SPT SPT7852SCT, SPT7852SCU, SPT7852SIT Datasheet

SPT7852

DUAL 10-BIT, 20 MSPS, 160 mW A/D CONVERTER

FEATURES

• Dual 10-Bit/20 MSPS Analog-to-Digital Converter

• Monolithic CMOS

• Internal Track-and-Hold

• Low Power Dissipation: 160 mW

• 4 Vp-p Analog Input Range for Each ADC

• Single +5 Volt Power Supply

with Option for 3.3 V Digital Outputs

• Tri-State, TTL-Compatible Outputs

• Overrange Bit

• Selectable Two’s Complement or Straight Binary Output

GENERAL DESCRIPTION

The SPT7852 has two 10-Bit CMOS analog-to-digital converters that can sample data at speeds up to 20 MSPS. It

has excellent low noise performance with a very low typical

power dissipation of only 160 mW—that’s the total power

for

both

converters. The SPT7852 uses a dual configuration

of the proprietary circuit design found in our 10-bit CMOS

single converter family, to achieve its high performance in a

CMOS process.

The SPT7852 is specifically designed for video decoding

applications and is ideal for S-video decoding and decoding

of multiple composite video sources. It is the ADC for the

APPLICATIONS

• SPT NTSC/PAL Video Chip Set

• Video Set-Top Boxes

• Cellular Base Stations

• QPSK/QAM RF Demodulation

• S-Video Digitizers

• Composite Video Digitizers

• Portable and Handheld Instrumentation

SPT NTSC/PAL video decoder chip set that includes the

SPT9210 analog video processor and the SPT2110 video

decoder. It also has excellent application in the area of

coherent I/Q demodulation in such applications as QAM

demodulation and TV set-top box converters.

Inputs and outputs are TTL/CMOS-compatible to interface

with TTL/CMOS-logic systems. Output data format is selectable for either straight binary or two’s complement. The

SPT7852 is available in a 44L TQFP package in commercial

and industrial temperature ranges. It is also available in die

form. For availability of extended temperature ranges,

please contact the factory.

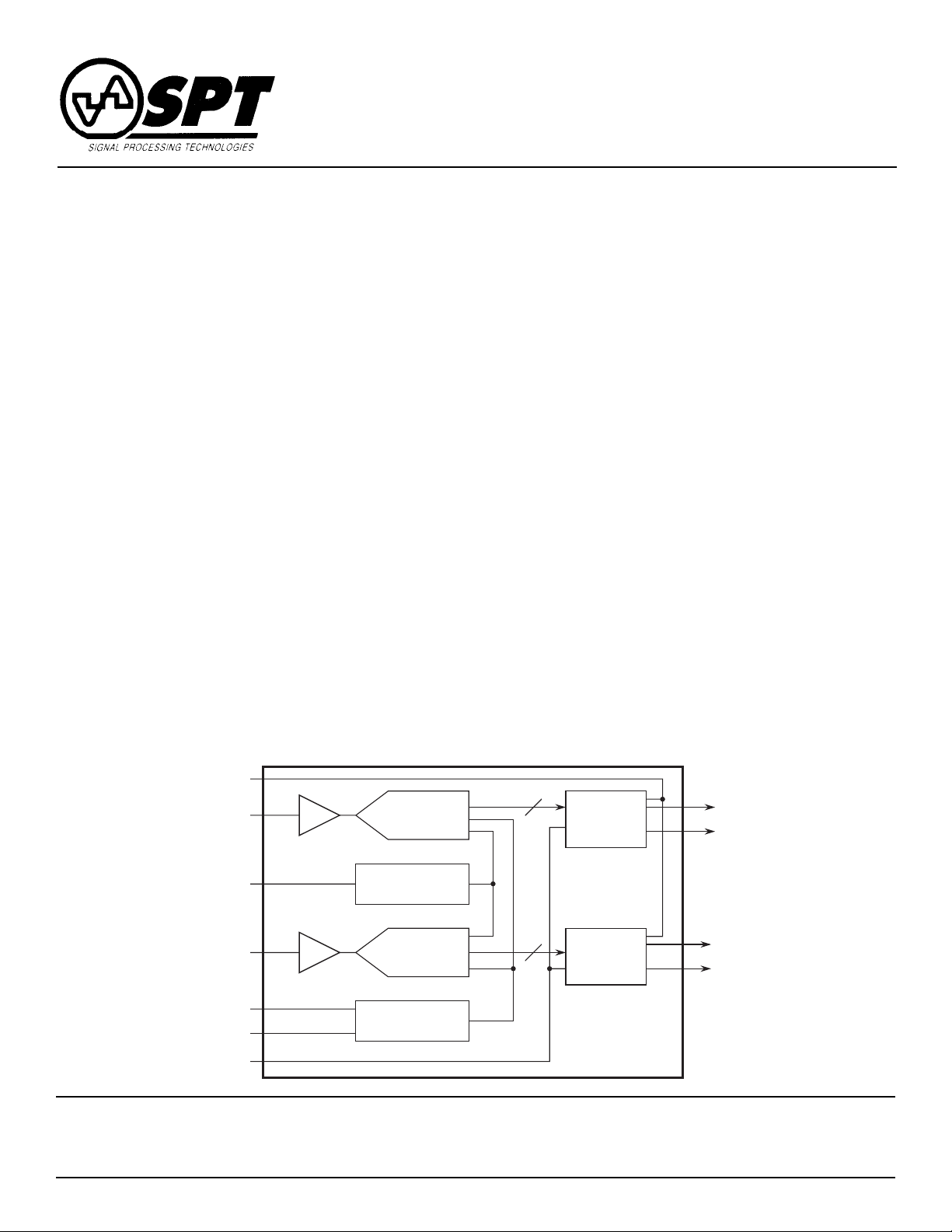

BLOCK DIAGRAM

Reference In

Signal Processing Technologies, Inc.

Phone: (719) 528-2300 FAX: (719) 528-2370 Website: http://www.spt.com E-Mail: sales@spt.com

MSB

Invert

V

INA

V

INB

Clock

Reset

Output

Enable

10

T/H

T/H

ADC

Reference

Ladder

ADC

Timing

Generation

A

B

10

Output

Buffer

Output

Buffer

4755 Forge Road, Colorado Springs, Colorado 80907, USA

Overrange

D

A0-9

Overrange

D

B0-9

ABSOLUTE MAXIMUM RATINGS (Beyond which damage may occur)1 25 °C

Supply Voltages

AVDD.........................................................................+6 V

Output

Digital Outputs .......................................................10 mA

DVDD.........................................................................+6 V

Temperature

Input Voltages

Analog Input................................. –0.5 V to AVDD +0.5 V

V

.............................................. –1.5 V to AVDD +0.8 V

Ref

CLK Input ...................................................................V

AV

– DVDD......................................................±100 mV

DD

DD

Operating Temperature ...................................0 to 70 °C

Junction Temperature ........................................... 175 °C

Lead Temperature, (soldering 10 seconds).......... 300 °C

Storage Temperature............................... –65 to +150 °C

Note: 1. Operation at any Absolute Maximum Rating is not implied. See Electrical Specifications for proper nominal

applied conditions in typical applications.

ELECTRICAL SPECIFICATIONS FOR EACH CHANNEL

TA = T

PARAMETERS CONDITIONS LEVEL MIN TYP MAX UNITS

Resolution 10 Bits

DC Accuracy

Analog Input

Reference Input

Conversion Characteristics

Dynamic Performance

MIN

to T

, AVDD = DVDD = +5.0 V, V

MAX

=0 to 4 V, ƒS =20 MSPS, ƒ

IN

=40 MHz, V

CLK

RHS

=4.0 V, V

=0.0 V, unless otherwise specified.

RLS

TEST TEST

Integral Nonlinearity IV ±1.0 LSB

Differential Nonlinearity IV ±1.0 LSB

Input Voltage Range V V

RLS

V

RHS

V

Input Resistance V 50 kΩ

Input Capacitance V 5.0 pF

Input Bandwidth Full Power V 35 MHz

Offset VI ±2.0 LSB

Gain Error VI ±2.0 LSB

Resistance V

RHS

– V

RLS

VI 350 425 500 Ω

Voltage Range

V

RLS

V

RHS

V

– V

∆(V

∆(V

RHS

RHF

RLS

RLS

– V

– V

) V 150 mV

RHS

) V 150 mV

RLF

Maximum Conversion Rate

Minimum Conversion Rate

1

1

IV 0 - 2.0 V

IV 3.0 - AV

DD

V

V 1.0 4.0 5.0 V

VI 20 MHz

IV 100 kHz

Pipeline Delay (Latency) IV 12 Clock Cycles

Aperture Delay Time V 5 ns

Aperture Jitter Time V 15 ps

Effective Number of Bits

ƒ

=3.58 MHz VI 8.4 8.9 Bits

IN

ƒIN= 10 MHz VI 7.9 8.4 Bits

1

2X Clock required.

SPT

SPT7852

2 1/12/00

ELECTRICAL SPECIFICATIONS

TA=T

MIN

to T

, AVDD = DVDD = +5.0 V, V

MAX

=0 to 4 V, ƒS =20 MSPS, ƒ

IN

=40 MHz, V

CLK

RHS

= 4.0 V, V

=0.0 V, unless otherwise specified.

RLS

TEST TEST

PARAMETERS CONDITIONS LEVEL MIN TYP MAX UNITS

Dynamic Performance

Signal-to-Noise Ratio

(without Harmonics)

=3.58 MHz VI 53 57 dB

ƒ

IN

ƒIN=10 MHz VI 52 56 dB

Harmonic Distortion

ƒIN=3.58 MHz VI 56 59 dB

ƒIN=10 MHz VI 52 54 dB

Signal-to-Noise and Distortion

(SINAD)

ƒIN=3.58 MHz VI 52 55 dB

ƒIN=10 MHz VI 49 52 dB

Channel-to-Channel Crosstalk ƒIN=3.58 MHz IV 70 dB

Channel-to-Channel Gain Matching Full Scale IV 0.04 dB

Spurious Free Dynamic Range ƒIN=3.58 MHz @ –3 dB FS V 66 dB

Differential Phase V 0.2 Degree

Differential Gain V 0.3 %

Digital Inputs

Logic "1" Voltage VI 2.0 V

Logic "0" Voltage VI 0.8 V

Maximum Input Current Low V

=0 V VI –10 +10 µA

IL

Maximum Input Current High VIH=5 V VI –10 +10 µA

Input Capacitance V 5 pF

Digital Outputs

Logic "1" Voltage IOH=0.5 mA VI OVDD–0.5 V

Logic "0" Voltage IOS=1.6 mA VI 0.4 V

t

RISE/tFALL

15 pF Load V 10 ns

Output Enable to Data Output Delay 20 pF Load, TA=+25 °C V 10 ns

50 pF Load Over Temp. V 22 ns

Power Supply Requirements

Voltages DV

AV

OV

Currents AI

DI

DD

DD

DD

DD

DD

Total for Both Converter VI 15 18 mA

Channels VI 17 20 mA

IV 4.75 5.0 5.25 V

IV 4.75 5.0 5.25 V

IV 2.7 5.0 5.25 V

Power Dissipation VI 160 190 mW

TEST LEVEL CODES

All electrical characteristics are subject to the following conditions:

All parameters having min/max specifications are

guaranteed. The Test Level column indicates the

specific device testing actually performed during

production and Quality Assurance inspection. Any

blank section in the data column indicates that the

specification is not tested at the specified condition.

SPT

TEST LEVEL

I

II

III

IV

V

VI

TEST PROCEDURE

100% production tested at the specified temperature.

100% production tested at T

=+25 °C, and sample tested at

A

the specified temperatures.

QA sample tested only at the specified temperatures.

Parameter is guaranteed (but not tested) by design and char-

acterization data.

Parameter is a typical value for information purposes only.

100% production tested at T

= +25 °C. Parameter is guaran-

A

teed over specified temperature range.

SPT7852

3 1/12/00

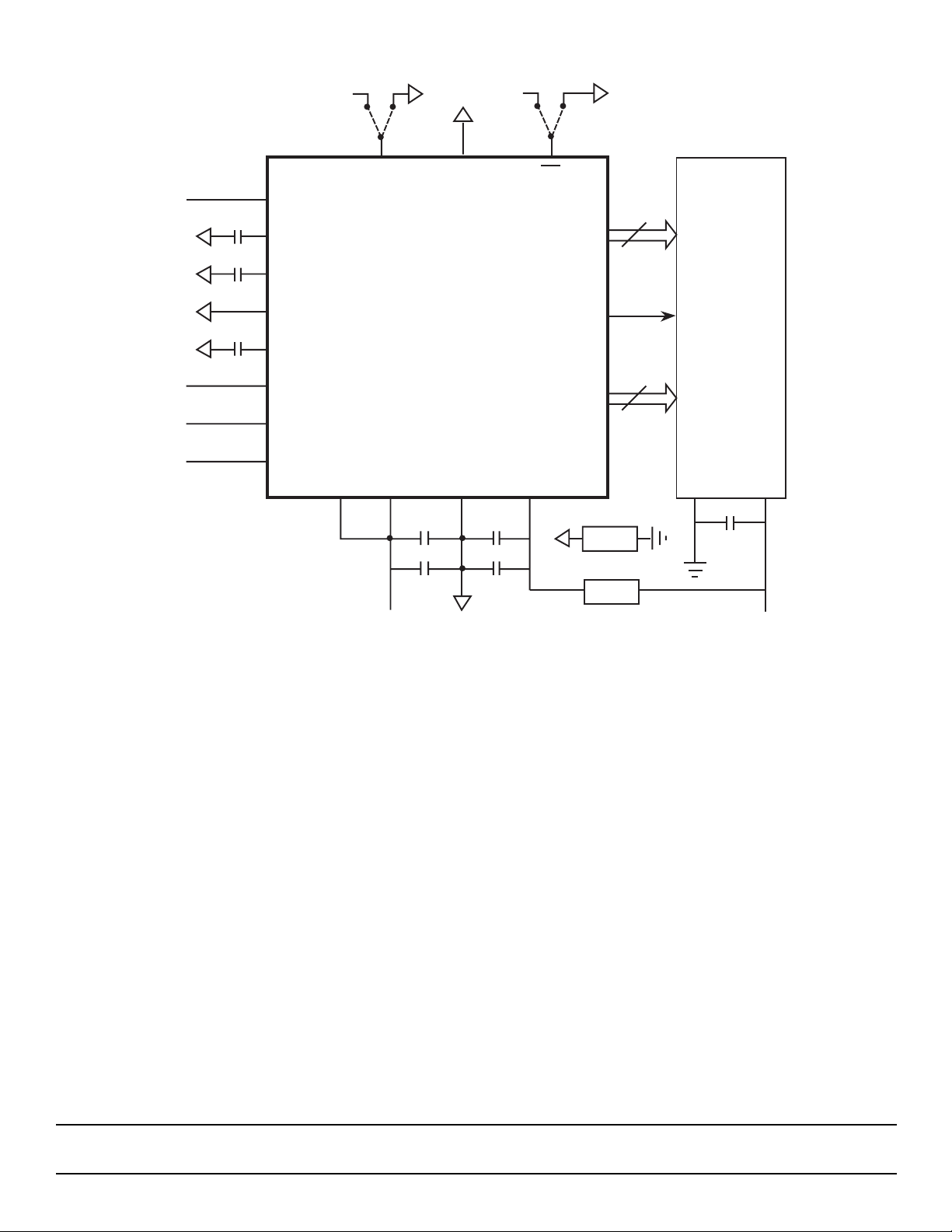

Figure 1 –Typical Interface Circuit

+A5

+A5

3-st

EN

Ref In

(+4 V)

V

IN1

V

IN2

Clock

V

RHF

V

RHS

V

RLS

V

RLF

V

CAL

V

INA

V

INB

CLK

MSBINV Reset

SPT7852

AV

DD

DV

DD

.1 µF .1 µF

4.7 µF 4.7 µF

+A5

GND OV

EN

Digital

Output A

DAV

Digital

Output B

DD

11

Interfacing

Logic

11

FB

*

FB

*

3.3 V/5 V

1. Place the ferrite bead (*) as close to the ADC as possible.

2. Place 0.1 µF decoupling capacitors as close to the ADC as possible.

3. All capacitors are 0.1 µF surface-mount unless otherwise specified.

4. All analog input pins (references, analog input, clock input) must

be protected. (See absolute maximum ratings.)

TYPICAL INTERFACE CIRCUIT

Very few external components are required to achieve the

stated device performance. Figure 1 shows the typical interface requirements when using the SPT7852 in normal

circuit operation. The following sections provide descriptions of the major functions and outline critical performance

criteria to consider for achieving the optimal device performance.

POWER SUPPLIES AND GROUNDING

SPT suggests that both the digital and the analog supply

voltages on the SPT7852 be derived from a single analog

supply as shown in figure 1. A separate digital supply must

be used for all interface circuitry. SPT suggests using this

power supply configuration to prevent a possible latch-up

condition on powerup.

SPT

SPT7852

4 1/12/00

Loading...

Loading...