SPT SPT7840SCT, SPT7840SIS Datasheet

SPT7840

10-BIT, 10 MSPS, 100 mW A/D CONVERTER

TECHNICAL DATA

JUNE 27, 2001

FEATURES

• Monolithic 10 MSPS converter

• 100 mW power dissipation

• On-chip track-and-hold

• Single +5 V power supply

• TTL/CMOS outputs

• 5 pF input capacitance

• Low cost

• Tr i-state output buffers

• High ESD protection: 3,500 V minimum

• Selectable +3 V or +5 V logic I/O

GENERAL DESCRIPTION

The SPT7840 is a 10-bit monolithic, low-cost, ultralowpower analog-to-digital converter capable of minimum

word rates of 10 MSPS. The on-chip track-and-hold function assures very good dynamic performance without the

need for external components. The input drive requirements are minimized due to the SPT7840’s low input

capacitance of only 5 pF.

Po wer dissipation is e xtremely lo w at only 100 mW typical

(120 mW maximum) at 10 MSPS with a power supply of

+5.0 V. The digital outputs are +3 V or +5 V, and are user

APPLICATIONS

• All high-speed applications where low power

dissipation is required

• Video imaging

• Medical imaging

• IR imaging

• Scanners

• Digital communications

selectable. The SPT7840 is pin-compatible with the entire

family of SPT 10-bit, CMOS conver ters (SPT7835/40/50/

55/60/61), which simplifies upgrades. The SPT7840 has

incorporated proprietar y circuit design* and CMOS processing technologies to achieve its advanced performance. Inputs and outputs are TTL/CMOS-compatible to

interface with TTL/CMOS logic systems. Output data format is straight binary.

The SPT7840 is available in a 28-lead SOIC pac kage over

the industrial temperature range, and a 32-lead small

(7 mm square) TQFP package over the commercial

temperature range.

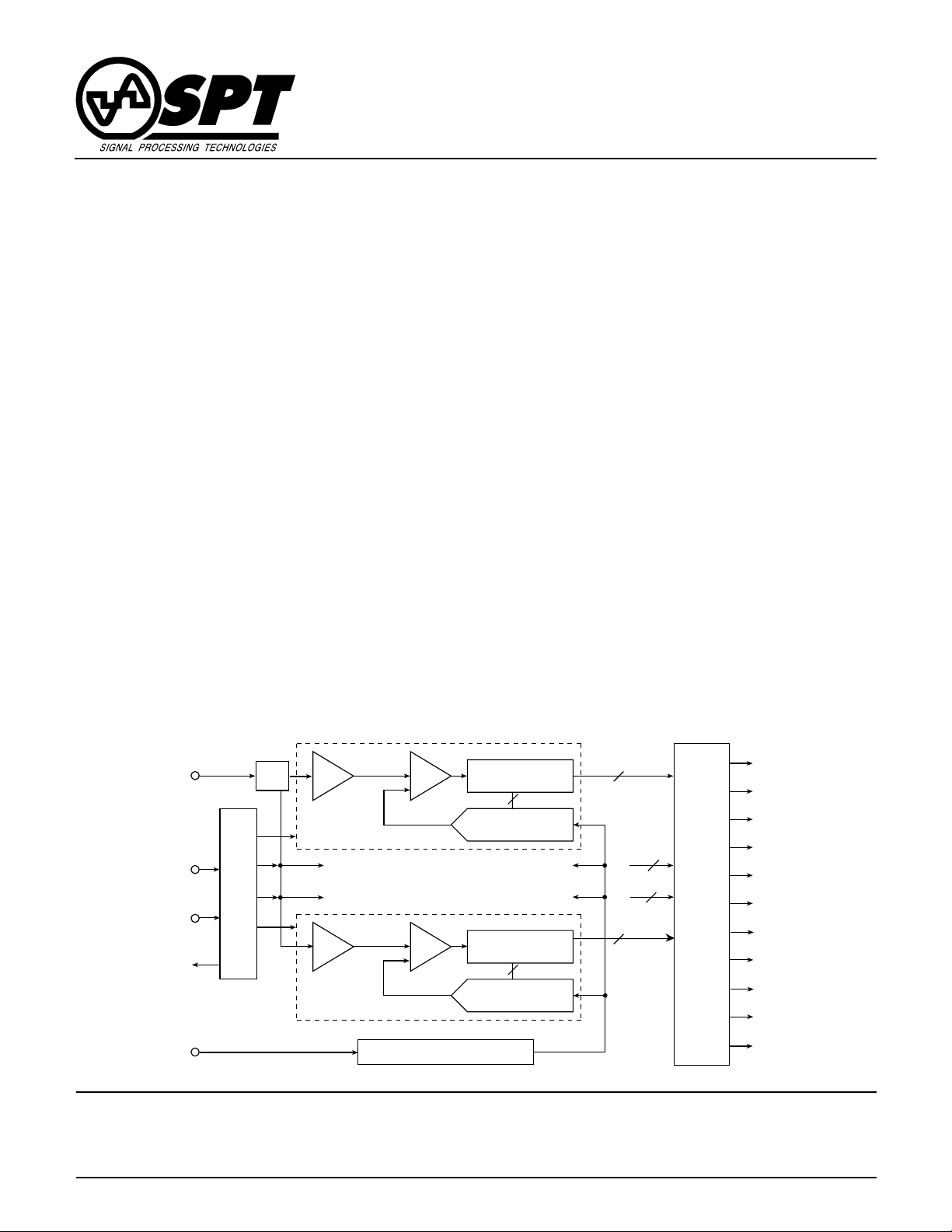

BLOCK DIAGRAM

A

IN

CLK In

Enable

Data

Valid

Ref

In

Timing

and

Control

Mux

P1

P2

P7

P8

ADC Section 1

1:8

.

.

.

T/H

ADC Section 2

ADC Section 7

ADC Section 8

T/H

.

.

.

Auto-

Zero

CMP

Auto-

Zero

CMP

Reference Ladder

*Patent pending

11-Bit

SAR

11

DAC

11-Bit

SAR

11

DAC

V

REF

11

11

.

.

.

.

.

.

11

11

11-Bit

8:1

Mux/

Error

Correction

Signal Processing Technologies, Inc.

4755 Forge Road, Colorado Springs, Colorado 80907, USA

Phone: 719-528-2300 Fax: 719-528-2370 Web Site: http://www .spt.com e-mail: sales@spt.com

D10 Overrange

D9 (MSB)

D8

D7

D6

D5

D4

D3

D2

D1

D0 (LSB)

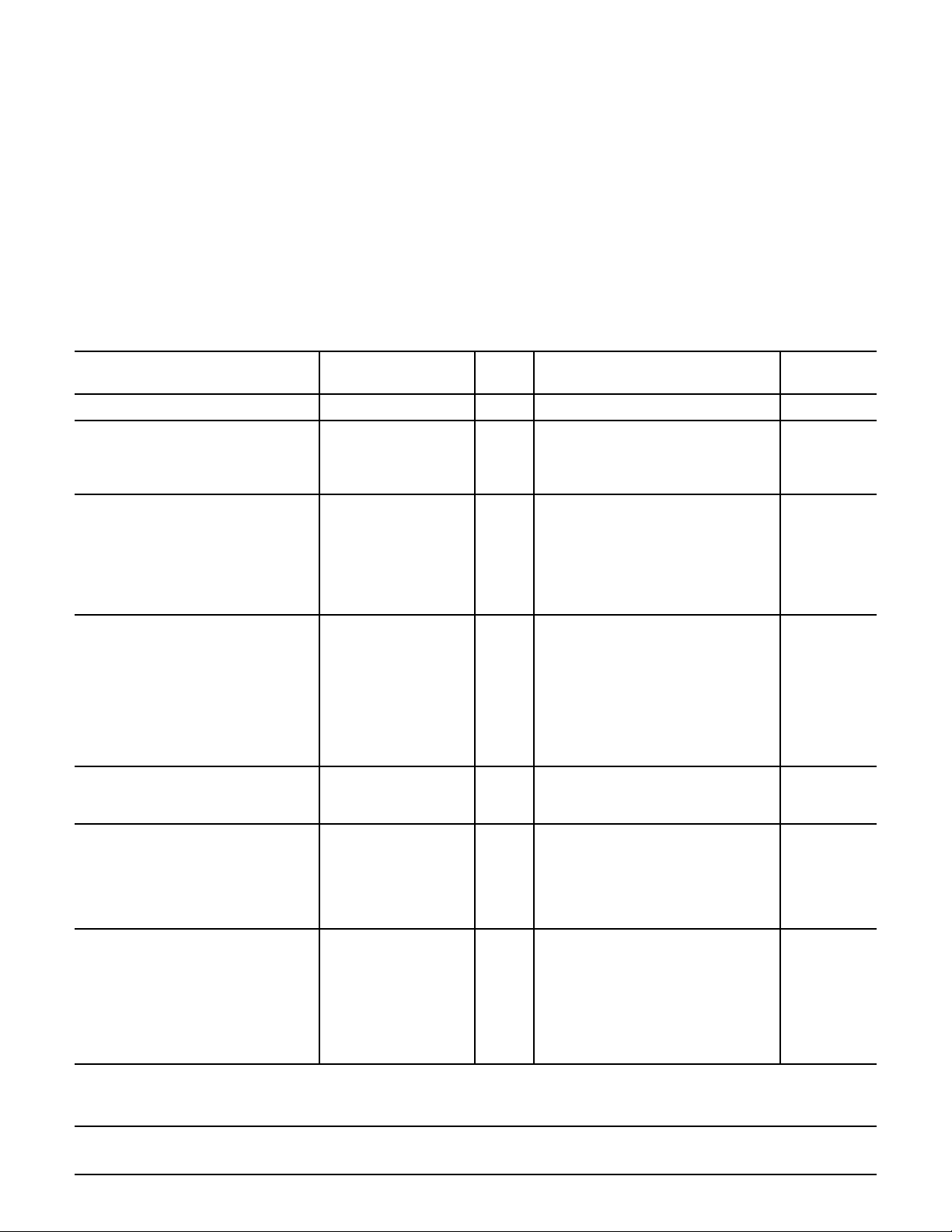

ABSOLUTE MAXIMUM RATINGS (Beyond which damage may occur)1 25 °C

Supply Voltages

AVDD......................................................................+6 V

Output

Digital Outputs ...................................................10 mA

DVDD.....................................................................+6 V

Temperature

Input Voltages

Analog Input .............................. –0.5 V to AVDD +0.5 V

..............................................................0 to AV

V

REF

CLK Input ............................................................... V

AVDD – DVDD..................................................±100 mV

AGND – DGND ..............................................±100 mV

DD

DD

Operating T emper ature ............................ –40 to 85 °C

Junction Temperature ........................................ 175 °C

Lead Temperature, (soldering 10 seconds) ....... 300 °C

Storage Temperature............................ –65 to +150 °C

Note: 1. Operation at any Absolute Maximum Rating is not implied. See

Electrical Specifications for proper nominal applied conditions

in typical applications.

ELECTRICAL SPECIFICATIONS

TA=T

to T

MIN

, AVDD=DVDD=OVDD=+5.0 V , VIN=0 to 4 V, ƒ

MAX

TEST TEST SPT7840

PARAMETERS CONDITIONS LEVEL MIN TYP MAX UNITS

Resolution 10 Bits

DC Accuracy

Integral Linearity Error (ILE) VI ±1.0 LSB

Differential Linearity Error (DLE) VI ±0.5 LSB

No Missing Codes VI Guaranteed

Analog Input

Input Voltage Range VI V

Input Resistance IV 50 kΩ

Input Capacitance V 5.0 pF

Input Bandwidth (Small Signal) V 100 MHz

Offset V ±2.0 LSB

Gain Error V ±2.0 LSB

=20 MHz, ƒS=10MSPS, V

CLK

RHS

RLS

=4.0 V , V

=0.0 V, unless otherwise specified.

RLS

V

RHS

V

Reference Input

Resistance VI 400 500 600 Ω

Bandwidth V 100 150 MHz

Voltage Range

IV 0 2.0 V

IV 3.0 AV

DD

V 1.0 4.0 5.0 V

V

∆(V

∆(V

V

V

V

RLS

RHS

RHS

RHF

RLS

– V

RLS

– V

)V90mV

RHS

– V

)V75mV

RLF

Reference Settling Time

V

RHS

V

RLS

V 15 Clock Cycles

V 20 Clock Cycles

Conversion Characteristics

Maximum Conversion Rate VI 10 MHz

Minimum Conversion Rate IV 2 MHz

Pipeline Delay (Latency) IV 12 Clock Cycles

Aperture Delay Time V 5 ns

Aperture Jitter Time V 10 ps (p-p)

Dynamic Performance

Effective Number of Bits (ENOB)

= 1 MHz VI 9.1 Bits

ƒ

IN

= 5 MHz VI 9.0 Bits

ƒ

IN

Signal-to-Noise Ratio (SNR)

(without Harmonics)

= 1 MHz VI 53 58 dB

ƒ

IN

ƒIN = 5 MHz VI 52 57 dB

SPT

SPT7840

2 6/27/01

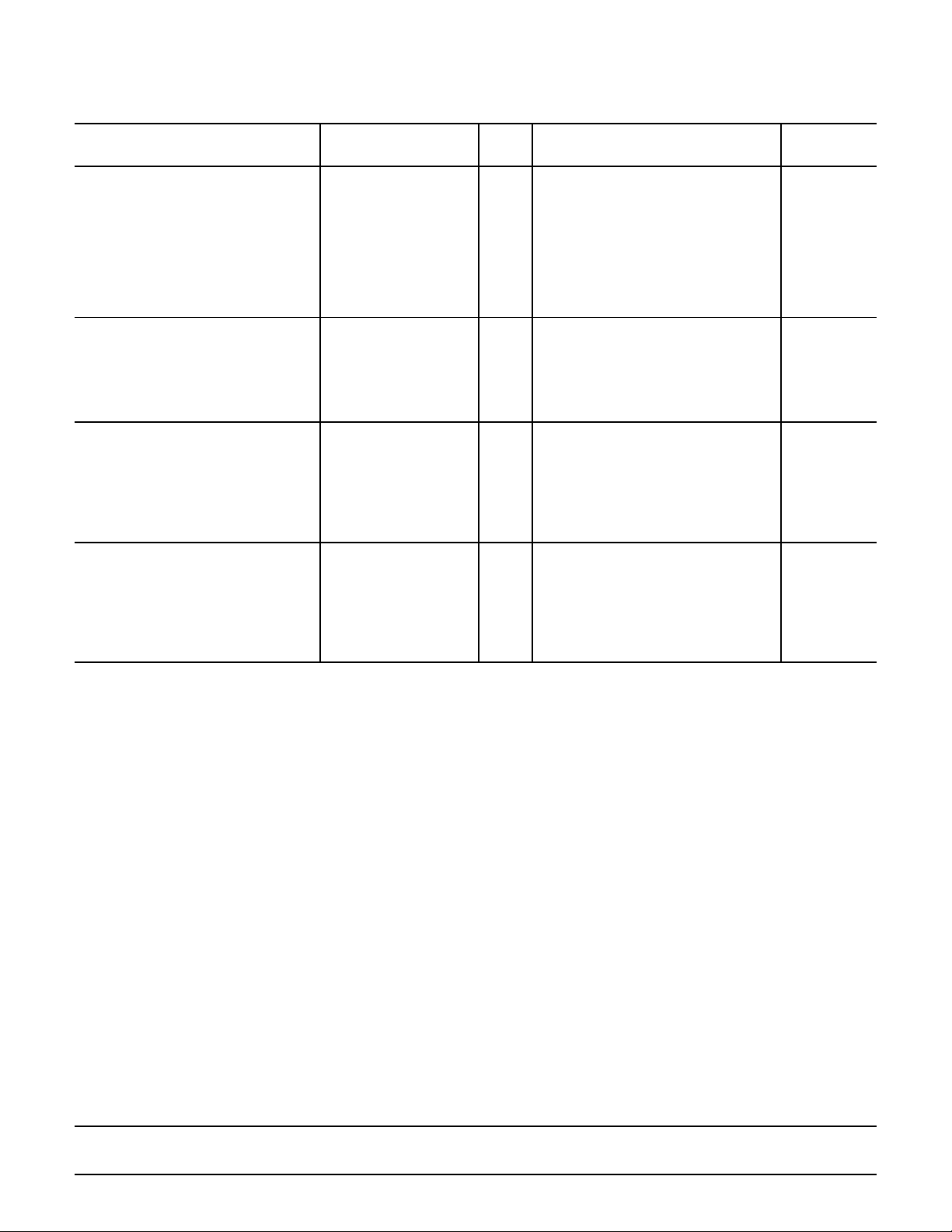

ELECTRICAL SPECIFICATIONS

TA=T

to T

MIN

, AVDD=DVDD=OVDD=+5.0 V , VIN=0 to 4 V, ƒ

MAX

TEST TEST SPT7840

PARAMETERS CONDITIONS LEVEL MIN TYP MAX UNITS

Dynamic Performance

Total Harmonic Distortion (THD)

= 1 MHz VI 59 63 dB

ƒ

IN

= 5 MHz VI 56 59 dB

ƒ

IN

Signal-to-Noise and Distortion

(SINAD)

= 1 MHz VI 52 57 dB

ƒ

IN

ƒ

= 5 MHz VI 51 56 dB

IN

Spurious Free Dynamic Range V 63 dB

Digital Inputs

Logic 1 Voltage VI 2 .0 V

Logic 0 Voltage VI 0.8 V

Maximum Input Current Low VI –10 +10 µA

Maximum Input Current High VI –10 +10 µA

Input Capacitance V 5 pF

=20 MHz, ƒS=10 MSPS, V

CLK

RHS

=4.0 V , V

=0.0 V, unless otherwise specified.

RLS

Digital Outputs

Logic 1 Voltage I

Logic 0 Voltage I

t

RISE

t

FALL

Output Enable to Data Output Delay 20 pF load, T

= 0.5 mA VI 3. 5 V

OH

= 1.6 mA VI 0 .4 V

OL

15 pF load V 10 ns

15 pF load V 10 ns

= +25 °CV 10 ns

A

50 pF load over temp. V 22 ns

Power Supply Requirements

Voltages OV

DV

AV

Currents AI

DI

DD

DD

DD

DD

DD

IV 3.0 5.0 V

IV 4.75 5.0 5.25 V

IV 4.75 5.0 5.25 V

VI 9 12 mA

VI 11 12 mA

Power Dissipation ƒIN = 1 MHz VI 100 120 mW

TEST LEVEL CODES

All electrical characteristics are subject to the

following conditions:

All parameters having min/max specifications

are guaranteed. The Test Level column indicates the specific device testing actually performed during production and Quality Assurance inspection. Any blank section in the data

column indicates that the specification is not

tested at the specified condition.

LEVEL TEST PROCEDURE

I 100% production tested at the specified temperature.

II 100% production tested at TA = +25 °C, and sample tested at the

specified temperatures.

III QA sample tested only at the specified temperatures.

IV Parameter is guaranteed (but not tested) by design and characteri-

zation data.

V Parameter is a typical value for information pur poses only.

VI 100% production tested at TA = +25 °C. Parameter is guaranteed

over specified temperature range.

SPT

SPT7840

3 6/27/01

SPECIFICATION DEFINITIONS

APERTURE DELAY

Aperture delay represents the point in time, relative to the

rising edge of the CLOCK input, that the analog input is

sampled.

APERTURE JITTER

The variations in aperture delay for successive samples.

DIFFERENTIAL GAIN (DG)

A signal consisting of a sine wave superimposed on various DC levels is applied to the input. Diff erential gain is the

maximum variation in the sampled sine wave amplitudes

at these DC levels.

DIFFERENTIAL PHASE (DP)

A signal consisting of a sine wave superimposed on various DC levels is applied to the input. Differential phase is

the maximum variation in the sampled sine wave phases

at these DC levels .

EFFECTIVE NUMBER OF BITS (ENOB)

SINAD = 6.02N + 1.76, where N is equal to the effective

number of bits.

INPUT BANDWIDTH

SINAD – 1.76

N =

6.02

INTEGRAL LINEARITY ERROR (ILE)

Linearity error refers to the deviation of each individual

code (normalized) from a straight line drawn from –FS

through +FS. The deviation is measured from the edge of

each particular code to the true straight line.

OUTPUT DELAY

Time between the clock’s triggering edge and output data

valid.

OVERVOLTAGE RECOVERY TIME

The time required for the ADC to recover to full accuracy

after an analog input signal 125% of full scale is reduced

to 50% of the full-scale value.

SIGNAL-TO-NOISE RATIO (SNR)

The ratio of the fundamental sinusoid power to the total

noise power. Harmonics are excluded.

SIGNAL-TO-NOISE AND DISTORTION (SINAD)

The ratio of the fundamental sinusoid power to the total

noise and distortion power.

TOTAL HARMONIC DISTORTION (THD)

The ratio of the total power of the first 9 harmonics to the

power of the measured sinusoidal signal.

Small signal (50 mV) bandwidth (3 dB) of analog input

stage.

DIFFERENTIAL LINEARITY ERROR (DLE)

Error in the width of each code from its theoretical value.

(Theoretical = VFS/2N)

SPURIOUS FREE DYNAMIC RANGE (SFDR)

The ratio of the fundamental sinusoidal amplitude to the

single largest harmonic or spurious signal.

SPT

SPT7840

4 6/27/01

Loading...

Loading...