SPT SPT7820ACN, SPT7820ACS, SPT7820AIJ, SPT7820AMJ, SPT7820BCN Datasheet

...

SPT7820

10-BIT, 20 MSPS, TTL OUTPUT, A/D CONVERTER

FEATURES

• Monolithic 20 MSPS Converter

• On-Chip Track/Hold

• Bipolar ±2.0 V Analog Input

• 60 dB SNR @ 1 MHz Input

• Low Power (1.0 W Typical)

• 5 pF Input Capacitance

• TTL Outputs

GENERAL DESCRIPTION

The SPT7820 A/D converter is a 10-bit monolithic converter

capable of word rates of a minimum of 20 MSPS. On board

track/hold function assures excellent dynamic performance

without the need for external components. Drive requirement problems are minimized with an input capacitance of

only 5 pF.

Inputs and outputs are TTL compatible to interface with TTL

logic systems. An overrange output signal is provided to

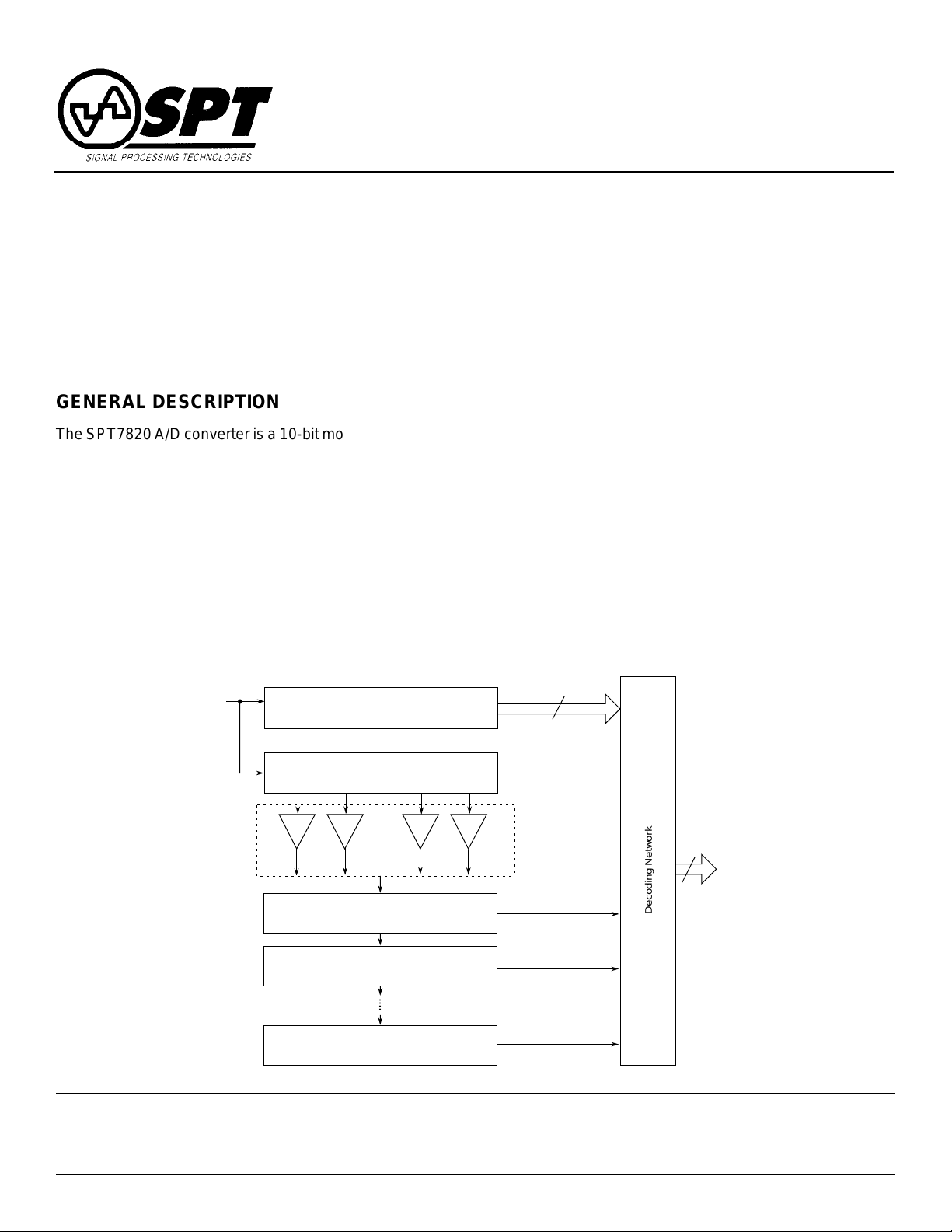

BLOCK DIAGRAM

APPLICATIONS

• Medical Imaging

• Professional Video

• Radar Receivers

• Instrumentation

• Electronic Warfare

• Digital Communications

indicate overflow conditions. Output data format is straight

binary. Power dissipation is very low at only 1.0 watt with

power supply voltages of +5.0 and -5.2 volts. The SPT7820

also provides a wide input voltage swing of ±2.0 volts.

The SPT7820 is available in 28-lead ceramic sidebrazed DIP,

PDIP and SOIC packages over the commercial, industrial

and military temperature ranges. Contact the factory for

availability of die and /883 versions.

Analog

Input

Coarse

A/D

Analog

Prescaler

T/H Amplifier

Bank

Successive Interpolation

Stage i

Successive Interpolation

Stage i+1

Successive Interpolation

Stage N

4

Digital

10

Decoding Network

Output

Signal Processing Technologies, Inc.

4755 Forge Road, Colorado Springs, Colorado 80907, USA

Phone: (719) 528-2300 FAX: (719) 528-2370

ABSOLUTE MAXIMUM RATINGS (Beyond which damage may occur)1 25 °C

Supply Voltages

VCC...........................................................................+6 V

Output

Digital Outputs ......................................... +30 to -30 mA

VEE........................................................................... -6 V

Temperature

Input Voltages

Analog Input............................................... VFB≤VIN≤V

VFT, V

..............................................................

FB

+3.0 V, -3.0 V

Reference Ladder Current .....................................12 mA

CLK Input.................................................................. V

FT

CC

Operating Temperature ............................-55 to +125 °C

1

Junction Temperature

..............................................

+175 °C

Lead Temperature, (soldering 10 seconds)........ +300 °C

Storage Temperature................................-65 to +150 °C

Note: 1. Operation at any Absolute Maximum Rating is not implied. See Electrical Specifications for proper nominal

applied conditions in typical applications.

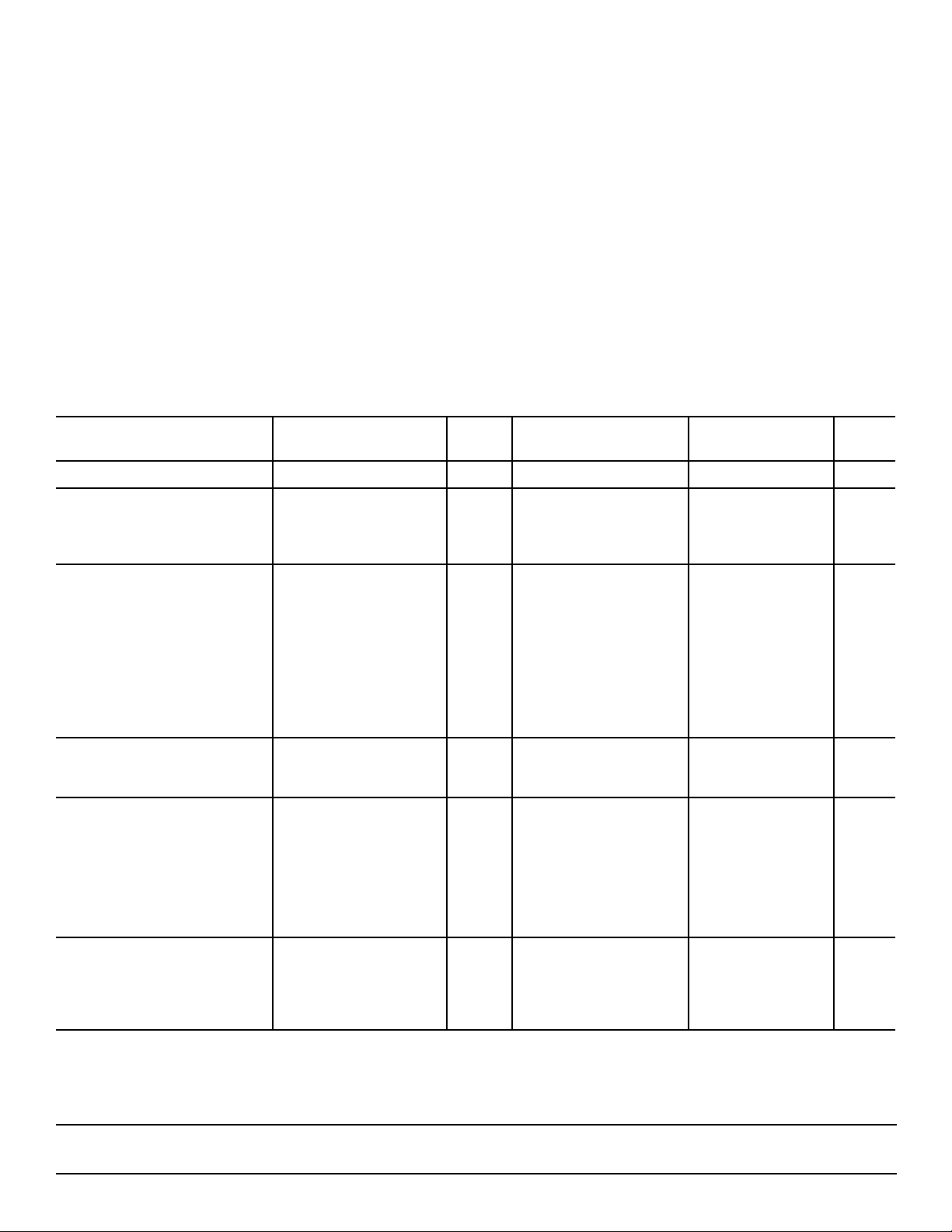

ELECTRICAL SPECIFICATIONS

TA=T

specified.

PARAMETERS CONDITIONS LEVEL MIN TYP MAX MIN TYP MAX UNITS

Resolution 10 10 Bits

DC Accuracy (+25 °C) ±Full Scale

- T

min

Integral Nonlinearity 100 kHz Sample Rate V ±1.0 ±1.5 LSB

Differential Nonlinearity V ±0.5 ±0.75 LSB

No Missing Codes VI Guaranteed Guaranteed

, VCC=+5.0 V, VEE=-5.2 V, DVCC=+5.0 V, VIN=±2.0 V, VSB=-2.0 V, VST=+2.0 V, f

max

TEST TEST SPT7820A SPT7820B

=20 MHz, 50% clock duty cycle, unless otherwise

CLK

Analog Input f

Input Voltage Range V ±2.0 ±2.0 V

Input Bias Current V

Input Bias Current T

Input Resistance VI 100 300 100 300 kΩ

Input Resistance T

Input Capacitance V 5 5 pF

Input Bandwidth 3 dB Small Signal V 120 120 MHz

+FS Error V ±2.0 ±2.0 LSB

-FS Error V ±2.0 ±2.0 LSB

Reference Input f

Reference Ladder Resistance VI 500 800 500 800 Ω

Reference Ladder Tempco V 0.8 0.8 Ω/°C

Timing Characteristics

Maximum Conversion Rate VI 20 20 MHz

Overvoltage Recovery Time V 20 20 ns

Pipeline Delay (Latency) IV 1 1

Output Delay TA=+25 °C V 14 18 14 18 ns

Aperture Delay Time T

Aperture Jitter Time T

Acquisition Time TA=+25 °C V 20 20 ns

Dynamic Performance

Effective Number of Bits

=1 MHz 9.2 8.7 Bits

f

IN

f

=3.58 MHz 8.8 8.3 Bits

IN

fIN=10.0 MHz 7.5 7.0 Bits

=1 MHz

CLK

=0 V VI 30 60 30 60 µA

IN

=-55 to +125 °CIV 75 75µA

A

=-55 to +125 °C IV 75 300 75 300 kΩ

A

=1 MHz

CLK

=+25 °CV1 1ns

A

=+25 °C V 5 5 ps-RMS

A

Clock Cycle

Typical thermal impedances (unsoldered, in free air): 28L sidebrazed DIP: θja = 50 °C/W, 28L plastic DIP: θja = 50 °C/W,

28L SOIC: θ

SPT

= 100 °C/W.

ja

2 3/11/97

SPT7820

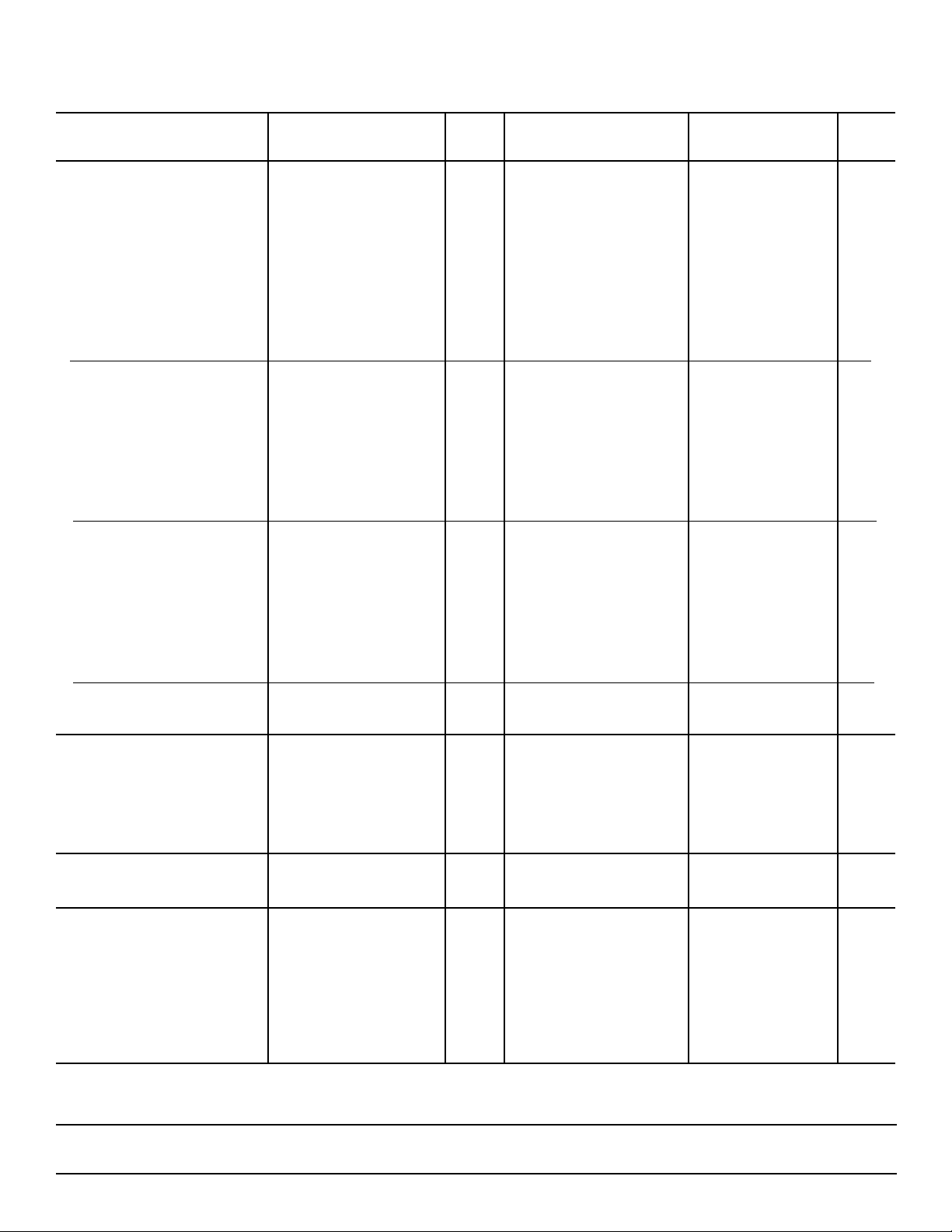

ELECTRICAL SPECIFICATIONS

TA=T

specified.

PARAMETERS CONDITIONS LEVEL MIN TYP MAX MIN TYP MAX UNITS

Dynamic Performance

Digital Inputs f

Digital Outputs f

Power Supply Requirements

- T

min

, VCC=+5.0 V, VEE=-5.2 V, DVCC=+5.0 V, VIN=±2.0 V, VSB=-2.0 V, VST=+2.0 V, f

max

=20 MHz, 50% clock duty cycle, unless otherwise

CLK

TEST TEST SPT7820A SPT7820B

Signal-To-Noise Ratio

(Without Harmonics)

=1 MHz TA=+25 °C I 57 60 54 57 dB

f

IN

f

=3.58 MHz TA=+25 °C I 56 58 53 55 dB

IN

=10.0 MHz TA=+25 °C I 50 53 47 49 dB

f

IN

=0-70, -25 to +85 °CIV 5558 5255 dB

T

A

=-55 to +125 °C* IV 52 55 49 52 dB

T

A

=0-70, -25 to +85 °CIV 5456 5153 dB

T

A

=-55 to +125 °C* IV 52 54 49 51 dB

T

A

=0-70, -25 to +85 °CIV 4750 4446 dB

T

A

T

=-55 to +125 °C* IV 43 46 40 42 dB

A

Harmonic Distortion

=1 MHz TA=+25 °C I 57 60 54 57 dB

f

IN

f

=3.58 MHz TA=+25 °C I 56 58 53 55 dB

IN

=10.0 MHz TA=+25 °C I 46 48 43 45 dB

f

IN

=0-70, -25 to +85 °CIV 5457 5154 dB

T

A

=-55 to +125 °C* IV 50 53 47 50 dB

T

A

=0-70, -25 to +85 °CIV 5355 5052 dB

T

A

=-55 to +125 °C* IV 50 52 47 49 dB

T

A

=0-70, -25 to +85 °)IV 4547 4244 dB

T

A

T

=-55 to +125 °C* IV 45 47 42 44 dB

A

Signal-to-Noise and Distortion

=1 MHz TA=+25 °C I 55 57 52 54 dB

f

IN

f

=3.58 MHz TA=+25 °C I 54 55 51 52 dB

IN

=10.0 MHz TA=+25 °C I 44 47 41 44 dB

f

IN

Spurious Free Dynamic Range T

Differential Phase

Differential Gain T

=0-70, -25 to +85 °CIV 52 49 dB

T

A

=-55 to +125 °C* IV 48 45 dB

T

A

=0-70, -25 to +85 °CIV 51 48 dB

T

A

=-55 to +125 °C* IV 48 45 dB

T

A

=0-70, -25 to +85 °CIV 43 40 dB

T

A

T

=-55 to +125 °C* IV 41 38 dB

A

=+25 °C, fIN=1 MHz V 67 67 dB

A

TA=+25 °C, fIN=3.58 & 4.35 MHz V 0.2 0.2 Degree

=+25 °C, fIN=3.58 & 4.35 MHz V 0.5 0.7 %

A

=1 MHz

CLK

Logic 1 Voltage VI 2.4 4.5 2.4 4.5 V

Logic 0 Voltage VI 0.8 0.8 V

Maximum Input Current Low T

Maximum Input Current High T

=+25 °C I 0 +5 +20 0 +5 +20 µA

A

=+25 °C I 0 +5 +20 0 +5 +20 µA

A

Pulse Width Low (CLK) IV 20 20 ns

Pulse Width High (CLK) IV 20 300 20 300 ns

=1 MHz

CLK

Logic 1 Voltage VI 2.4 2.4 V

Logic 0 Voltage VI 0.6 0.6 V

Voltages V

Currents I

DV

-V

CC

DI

-I

CC

CC

EE

CC

EE

Power Dissipation T

TA=+25 °C I 118 145 118 145 mA

TA=+25 °C I 40 55 40 55 mA

TA=+25 °C I 40 57 40 57 mA

=+25 °C I 1.0 1.3 1.0 1.3 W

A

IV 4.75 5.25 4.75 5.25 V

IV 4.75 5.0 5.25 4.75 5.0 5.25 V

IV -4.95 -5.2 -5.45 -4.95 -5.2 -5.45 V

Power Supply Rejection (5 V ±0.25 V, -5.2 ±0.25 V) V 1.0 1.0 LSB

*Temperature tested /883 only.

SPT

SPT7820

3 3/11/97

TEST LEVEL CODES

TEST LEVEL

TEST PROCEDURE

All electrical characteristics are subject to the

following conditions:

All parameters having min/max specifications

are guaranteed. The Test Level column indicates the specific device testing actually performed during production and Quality Assurance inspection. Any blank section in the data

column indicates that the specification is not

tested at the specified condition.

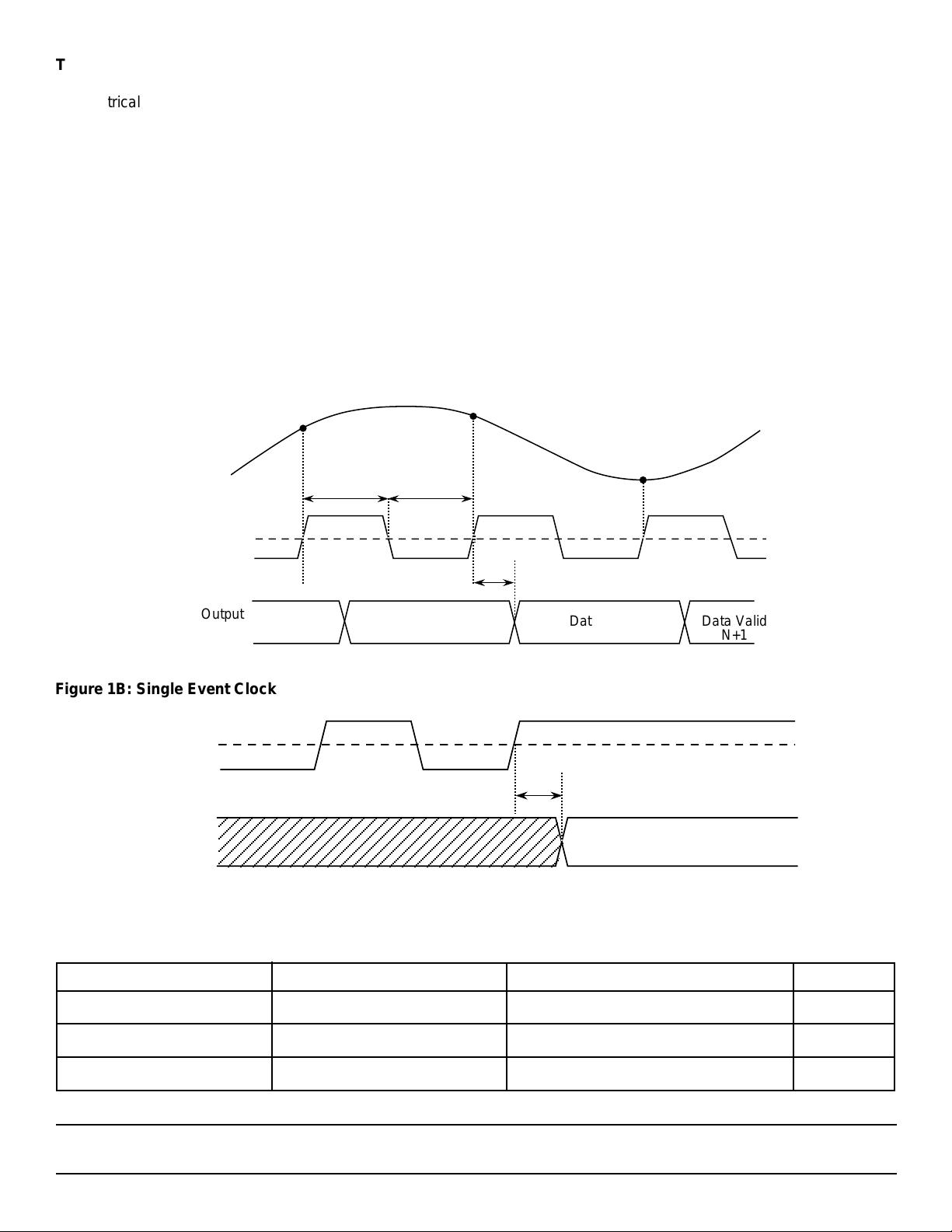

Figure 1A: Timing Diagram

N

t

pwH

CLK

t

pwL

II

III

IV

V

VI

I

100% production tested at the specified temperature.

100% production tested at TA = +25 °C, and sample

tested at the specified temperatures.

QA sample tested only at the specified temperatures.

Parameter is guaranteed (but not tested) by design

and characterization data.

Parameter is a typical value for information purposes

only.

100% production tested at TA = +25 °C. Parameter is

guaranteed over specified temperature range.

N+1

N+2

t

d

Output

Data

Figure 1B: Single Event Clock

CLK

Output

Data

Table I - Timing Parameters

PARAMETERS DESCRIPTION MIN TYP MAX UNITS

t

d

t

pwH

N-2 N-1

t

d

Data Valid

N

Data Valid

N+1

Data Valid

CLK to Data Valid Prop Delay - 14 18 ns

CLK High Pulse Width 20 - 300 ns

SPT

t

pwL

CLK Low Pulse Width 20 - - ns

SPT7820

4 3/11/97

Loading...

Loading...