SPT SPT561AIJ, SPT561AMJ Datasheet

Typical Distortion Performance

Output 20MHz 50MHz 100MHz

Power 2nd 3rd 2nd 3rd 2nd 3rd

10dBm -59 -62 -52 -60 -35 -49

18dBm -52 -48 -45 -46 -30 -36

24dBm -50 -41 -36 -32 -40 -30

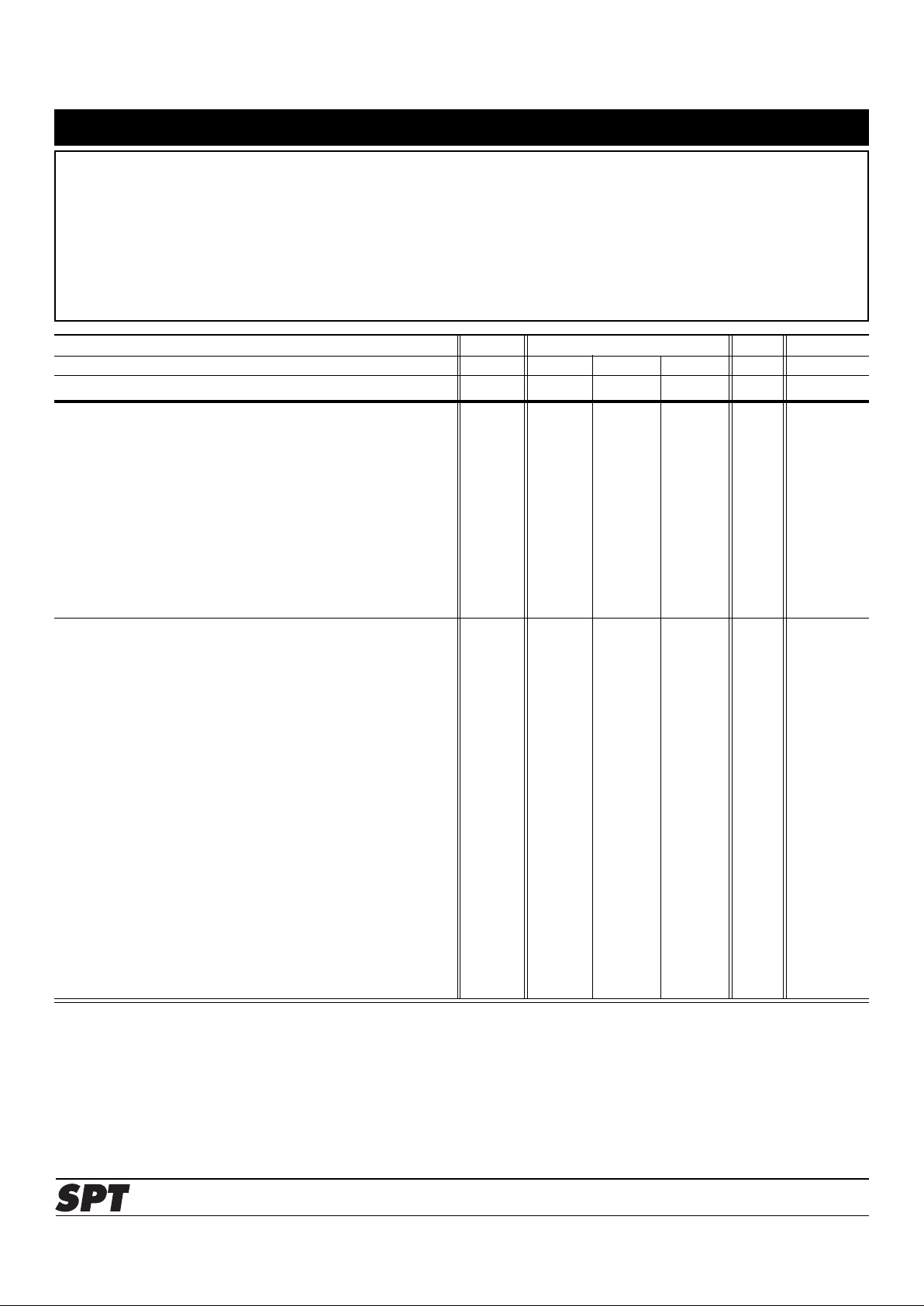

Frequency Response vs. Output Power

Gain (dB)

Frequency (MHz)

16

12

6

0 40 80 120 160 200

10

8

14

Po = 10dBm

V

o

= 2V

pp

Po = 24dBm

V

o

= 10V

pp

Po = 27.5dBm

V

o

= 15V

pp

Po = 18dBm

V

o

= 5V

pp

Features

■

150MHz bandwidth at +24dBm output

■

Low distortion (2nd/3rd:

-59/-62dBc @ 20MHz and 10dBm)

■

Output short circuit protection

■

User-definable output impedance, gain,

and compensation

■

Internal current limiting

■

Direct replacement for CLC561

Applications

■

Output amplification

■

Arbitrary waveform generation

■

ATE systems

■

Cable/line driving

■

Function generators

■

SAW drivers

■

Flash A/D driving and testing

4755 Forge Road, Colorado Springs, Colorado 80907, USA

Phone: (719) 528-2300 FAX: (719) 528-2370 Website: http://www.spt.com E-Mail: sales@spt.com

WIDEBAND, LOW DISTORTION DRIVER AMPLIFIER

General Description

The SPT561 is a wideband DC coupled, amplifier that combines high

output drive and low distortion. At an output of +24dBm (10Vpp into

50Ω), the -3dB bandwidth is 150MHz. As illustrated in the table

below, distortion performance remains excellent even when amplifying high-frequency signals to high output power levels.

With the output current internally limited to 250mA, the SPT561 is

fully protected against shorts to ground and can, with the addition of a

series limiting resistor at the output, withstand shorts to the ±15V

supplies.

The SPT561 has been designed for maximum flexibility in a wide

variety of demanding applications. The two resistors comprising the

feedback network set both the gain and the output impedance,

without requiring the series backmatch resistor needed by most op

amps. This allows driving into a matched load without dropping half

the voltage swing through a series matching resistor. External

compensation allows user adjustment of the frequency response.

The SPT561 is specified for both maximally flat frequency response

and 0% pulse overshoot compensations.

The combination of wide bandwidth, high output power, and low

distortion, coupled with gain, output impedance and frequency

response flexibility, makes the SPT561 ideal for waveform generator

applications. Excellent stability driving capacitive loads yields superior performance driving ADC’s, long transmission lines, and SAW

devices.

The SPT561 is constructed using thin film resistor/bipolar transistor

technology, and is available in the following versions:

SPT561AIJ -25°C to +85°C 24-pin Ceramic DIP

SPT561AMJ -55°C to +125°C 24-pin Ceramic DIP, features

burn-in and hermetic testing

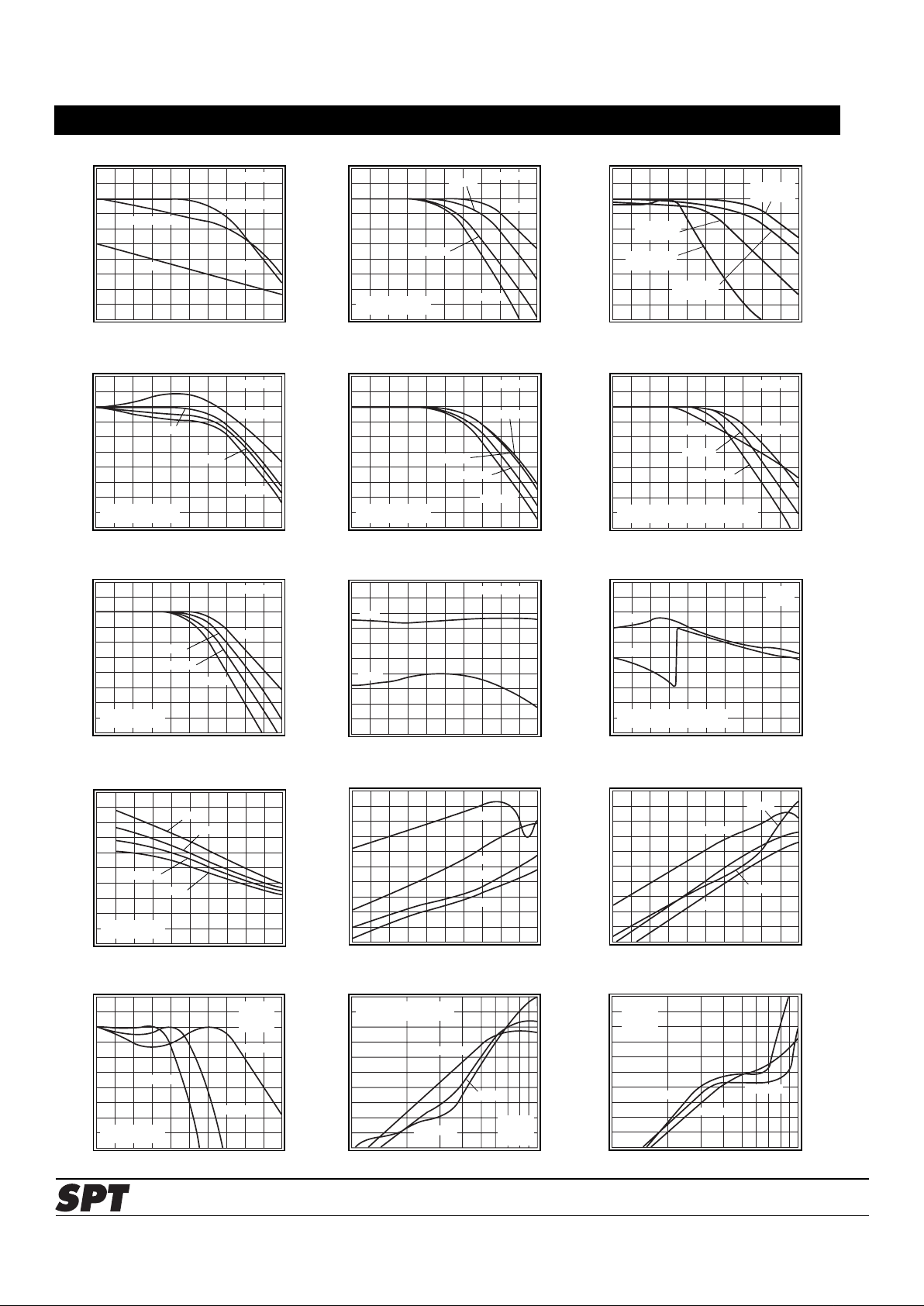

4

19

23

21

20

15

10

5

18

8

+

-

Compensation

V

o

-V

CC

All undesignated

pins are internally

unconnected. May

be grounded if

desired.

+V

CC

V+

V-

Block Diagram

2 10/9/98

SPT561

PARAMETERS CONDITIONS TYP MIN & MAX RATINGS UNITS SYM

Case Temperature SPT561AIJ +25°C -25°C +25°C +85°C

Case Temperature SPT561AMJ +25°C -55°C +25°C +125°C

FREQUENCY DOMAIN RESPONSE (Max. Flat Compensation)

✝ -3dB bandwidth

✝ maximally flat compensation V

o

<2Vpp (+10dBm) 215 >175 >185 >175 MHz SSBW

0% overshoot compensation V

o

<2Vpp (+10dBm) 210 >170 >180 >170 MHz

large signal bandwidth Vo <10Vpp (+24dBm) 150 >145 >135 >120 MHz FPBW

(see Frequency Response vs. Output Power plot)

gain flatness Vo <2Vpp (+10dBm)

✝ peaking 0.1 -50MHz 0 <0.50 <0.40 <0.50 dB GFPL

✝ peaking >50MHz 0 <1.75 <0.75 <1.00 dB GFPH

✝ rolloff at 100MHz 0.1 <1.00 <0.75 <1.00 dB GFR

group delay to 100MHz 2.9 – – – ns GD

linear phase deviation to 100MHz 0.6 <1.7 <1.2 <1.7 ° LPD

return loss (

see discussion of R

x

) to 100MHz -15 <-11 <-11 <-11 dB RL

DISTORTION (Max. Flat Compensation)

2nd harmonic distortion

✝ 24dBm (10V

pp

): 20MHz -50 <-38 <-40 <-38 dBc HD2HL

✝ 50MHz -36 <-29 <-29 <-22 dBc HD2HM

100MHz -40 <-25 <-25 <-25 dBc HD2HH

✝ 18dBm (5V

pp

): 20MHz -52 <-42 <-44 <-42 dBc HD2ML

✝ 50MHz -45 <-30 <-35 <-30 dBc HD2MM

✝ 100MHz -30 <-22 <-25 <-25 dBc HD2MH

✝ 10dBm (2V

pp

): 20MHz -59 <-48 <-52 <-48 dBc HD2LL

✝ 50MHz -52 <-36 <-40 <-40 dBc HD2LM

100MHz -35 <-27 <-28 <-28 dBc HD2LH

3rd harmonic distortion

✝ 24dBm (10V

pp

): 20MHz -41 <-34 <-34 <-30 dBc HD3HL

✝ 50MHz -32 <-26 <-26 <-21 dBc HD3HM

✝ 100MHz -30 <-24 <-24 <-24 dBc HD3HH

✝ 18dBm (5V

pp

): 20MHz -48 <-40 <-44 <-44 dBc HD3ML

✝ 50MHz -46 <-37 <-37 <-35 dBc HD3MM

100MHz -36 <-30 <-30 <-30 dBc HD3MH

✝ 10dBm (2V

pp

): 20MHz -62 <-54 <-57 <-57 dBc HD3LL

✝ 50MHz -60 <-49 <-52 <-49 dBc HD3LM

100MHz -49 <-45 <-45 <-45 dBc HD3LH

2-tone 3rd order

intermod intercept

2

20MHz 38 >36 >36 >36 dBm IM3L

50MHz 35 >32 >32 >32 dBm IM3M

100MHZ 29 >27 >27 >23 dBm IM3H

Min/max ratings are based on product characterization and simulation. Individual parameters are tested as noted. Outgoing quality levels are

determined from tested parameters.

SPT561 Electrical Characteristics

(Av = +10V, VCC = ±15V, RL = 50Ω, Rf = 410Ω, Rg = 40Ω, Ro = 50Ω; unless specified)

NOTES TO THE ELECTRICAL SPECIFICATIONS

The electrical characteristics shown here apply to the specific test conditions shown above (see also Figure 1 in

description of the operation). The SPT561 provides an equivalent, non-zero, output impedance determined by the

external resistors. The signal gain to the load is therefore load dependent. The signal gain shown above (Av = +10)

is the no load gain. The actual gain to the matching 50Ω load used in these specifications is half of this (+5).

The SPT561 requires an external compensation capacitor. Unless otherwise noted, this has been set to 10.5pF for

the frequency domain specifications (yielding a maximally flat frequency response) and 12.5pF for the time domain

specifications (yielding a 0% small signal pulse overshoot response).

3 10/9/98

SPT561

PARAMETERS CONDITIONS TYP MIN & MAX RATINGS UNITS SYM

Case Temperature SPT561AIJ +25°C -25°C +25°C +85°C

Case Temperature SPT561AMJ +25°C -55°C +25°C +125°C

TIME DOMAIN RESPONSE (0% Overshoot Compensation)

rise and fall time

2V step 1.5 <2.0 <1.9 <2.0 ns TRS

10V step 2.4 <2.8 <2.8 <3.4 ns TRL

settling time to 0.5% (time <1µs) 5V step 7 <12 <12 <15 ns TS

long term thermal tail (time >1µs) 5V step 1.5 <2.0 <2.0 <2.0 % SE

slew rate 10V

pp

, 175MHz 3300 >3000 >2900 >2500 V/µsSR

overshoot 2V step

maximally flat compensation 5 <13 <10 <13 % OSMF

0% overshoot compensation 0 <5 <3 <5 % OSZO

EQUIVALENT INPUT NOISE

voltage >100KHz 2.1 <2.5 <2.5 <2.5 nV/√Hz VN

inverting current >100KHz 34 <40 <40 <45 pA/√Hz ICN

non-inverting current >100KHz 2.8 <4.5 <4.5 <5.0 pA/√Hz NCN

noise floor >100KHz -159 <-157 <-157 <-157

dBm/(1Hz) SNF

integrated noise 1kHz to 200MHz 35 <45 <45 <45 µV INV

noise figure >100KHz 15 <17 <17 <17 dB NF

STATIC, DC PERFORMANCE

* input offset voltage 2.0 <14.0 <5.0 <15.0 mV VIO

average temperature coefficient 35 <100 – <100 µV/°C DVIO

* non-inverting bias current 5.0 <35 <20 <20 µA IBN

average temperature coefficient 20 <175 – <100 nA/°C DIBN

* inverting bias current 10.0 <50 <30 <50 µA IBI

average temperature coefficient 100 <200 – <200 nA/°C DIBI

* power supply rejection ratio (DC) 57 >54 >54 >52 dB PSRR

* supply current no load 50 <60 <60 <65 mA ICC

MISCELLANEOUS PERFORMANCE

open loop current gain (±2% tolerance) 10.0 – – – mA/mA G

average temperature coefficient +0.02 <+.03 – <+.02 %/°CDG

inverting input resistance (±5% tolerance) 14.0 – – – Ω RIN

average temperature coefficient +.02 <+.025 – <+.025 Ω/°C DRIN

non-inverting input resistance 700 >200 >400 >400 KΩ RNI

non-inverting input capacitance to 100MHz 2.7 <3.5 <3.5 <3.5 pF CNI

output voltage range 150mA load current ±10.5 – >±10.0 – V VO

output current limit 210 <250 <250 <250 mA OCL

Min/max ratings are based on product characterization and simulation. Individual parameters are tested as noted. Outgoing quality levels are

determined from tested parameters.

Absolute Maximum Ratings Recommended Operating Conditions

V

CC

(reversed supplies will destroy part) ±20V V

CC

±10V to ±15V

differential input voltage ±3V I

o

≤ ±200mA

common mode input voltage ±V

CC

common mode input voltage < ±(|VCC| -6)V

junction temperature (see thermal model) +175°C output impedance 25Ω to 200Ω

storage temperature -65°C to +150°C gain range (no-load voltage gain) +5 to +80

lead temperature (soldering 10s) +300°C case temperature: AIJ -25°C to +85°C

output current (internally limited) ±250mA AMJ -55°C to +125°C

Notes

1) * AIJ, AMJ 100% tested at +25°C

✝ AMJ 100% tested at at +25°C and sample tested

at -55°C and +125°C

✝ AIJ sample tested at +25°C

2) Test Tones are set ±100kHz of indicated frequency.

SPT561 Electrical Characteristics

(Av = +10V, VCC = ±15V, RL = 50Ω, Rf = 410Ω, Rg = 40Ω, Ro = 50Ω; unless specified)

4 10/9/98

SPT561

Small Signal Gain and Phase

Gain (dB)

Frequency (MHz)

6

8

10

12

14

16

0 50 100 150 200 250

Maximally Flat

Phase (degrees)

0

-90

-360

-180

-270

0% Overshoot

Gain

Phase

Po = 10dBm

Frequency Response vs. Gain

Normalized Magnitude (1dB/div)

Frequency (MHz)

0 50 100 150 200 250

Po = 10dBm

Av = 10

Av = 5

Av = 15

Av = 20

Re-compensated at

each gain (see text)

Frequency Response vs. Output Power

Gain (dB)

Frequency (MHz)

16

12

6

0 40 80 120 160 200

10

8

14

Po = 10dBm

V

o

= 2V

pp

Po = 24dBm

V

o

= 10V

pp

Po = 27.5dBm

V

o

= 15V

pp

Po = 18dBm

V

o

= 5V

pp

Frequency Response vs. R

L

Normalized Magnitude (1dB/div)

Frequency (MHz)

0 50 100 150 200 250

Pi = -4dBm

RL = 50Ω

RL = 25Ω

RL = 75Ω

RL = 100Ω

Fixed gain and

compensated vs. load

Frequency Response vs. Power Supply

Frequency (MHz)

0 50 100 150 200 250

Po = 10dBm

±VCC = 18

±VCC = 12

±VCC = 15

±VCC = 10

Gain (dB)

16

12

6

10

8

14

Re-compensated at

each supply voltage

Frequency Response vs. R

o

Frequency (MHz)

0 50 100 150 200 250

Pi = -4dBm

Normalized Magnitude (1dB/div)

Ro = 50Ω

Ro = 25Ω

Ro = 75Ω

Ro = 100Ω

Response measured with matched load

Re-compensated at each R

o

Frequency Response vs. Gain (R

o, RL

= 75Ω)

Frequency (MHz)

0 50 100 150 200 250

Vo = 2V

pp

Normalized Magnitude (1dB/div)

Av = 5

Av = 10

Av = 15

Av = 20

Re-compensated

at each gain

Gain Flatness/Deviation from Linear Phase

Gain (0.1dB/div)

Frequency (MHz)

0 20406080100

Phase (0.5°/div)

Gain

Phase

Po = 10dBm

Internal Current Gain and Phase

Gain (10dB/div)

Frequency (MHz)

-30

-20

0

20

30

10

0 100 200 300 400 500

Phase (90°/div)

180

90

-180

0

-90

Gain

Phase

-10

Cx = 0

R

L

= 0

Phase consistant with current

polarity connection of Figure 3

Two Tone, 3rd-Order Intermodulation

Intercept (2.5dB/div)

Frequency (MHz)

45

35

20

0 20406080100

30

25

40

Av = 15

Av = 5

Av = 10

Av = 20

Re-compensated

at each gain

2nd Harmonic Distortion vs. Frequency

Distortion (dBc)

Output Power (dB)

-25

-45

-75

4 8 12 16 20 24

-55

-65

-35

50MHz

10MHz

20MHz

100MHz

3rd Harmonic Distortion vs. Frequency

Distortion (dBc)

Output Power (dB)

-25

-45

-75

4 8 12 16 20 24

-55

-65

-35

50MHz

10MHz

20MHz

100MHz

Frequency Response Driving C

L

Frequency (MHz)

0 50 100 150 200 250

Gain (1dB/div)

Av = +5

R

o

= 25

V

o

= 2V

pp

CL = 100pF

CL = 20pF

CL = 50pF

Re-compensated

at each C

L

2nd Harmonic Distortion Driving C

L

Frequency (MHz)

10 20 30 40 50 100

Distortion (5dBc/div)

Av = +5

R

o

= 25

V

o

= 2V

pp

CL = 100pF

CL = 20pF

CL = 50pF

70

-80

-70

-60

-50

-40

-30

Compensation as shown in

Frequency Response plot

3rd Harmonic Distortion Driving C

L

Frequency (MHz)

10 20 30 40 50 100

Distortion (5dBc/div)

Av = +5

R

o

= 25

V

o

= 2V

pp

CL = 100pF

CL = 20pF

CL = 50pF

70

-80

-70

-60

-50

-40

-30

SPT561 Typical Performance Characteristics

(TA = +25°C, Circuit in Figure 1; unless specified)

Loading...

Loading...