SPT SPT5230SCT Datasheet

SPT5230

10-BIT, 36 MWPS TRIPLE VIDEO DAC

FEATURES

• 10-Bit Triple Video Digital-to-Analog Converter

• Output Full-Scale Voltage 0.5 to 2.0 Vp-p

• 36 MWPS Operation (typ)

• Low Power: 280 mW (1 Vp-p Output)

• 5 V Monolithic CMOS

• 52-pin QFP Package (10mm x 10mm, 0.65 mm pitch)

GENERAL DESCRIPTION

The SPT5230 is a 10-bit, 36 MWPS triple video digital-toanalog converter specifically designed for high performance,

high resolution color graphics monitor applications and video

processing applications. A single external resistor controls

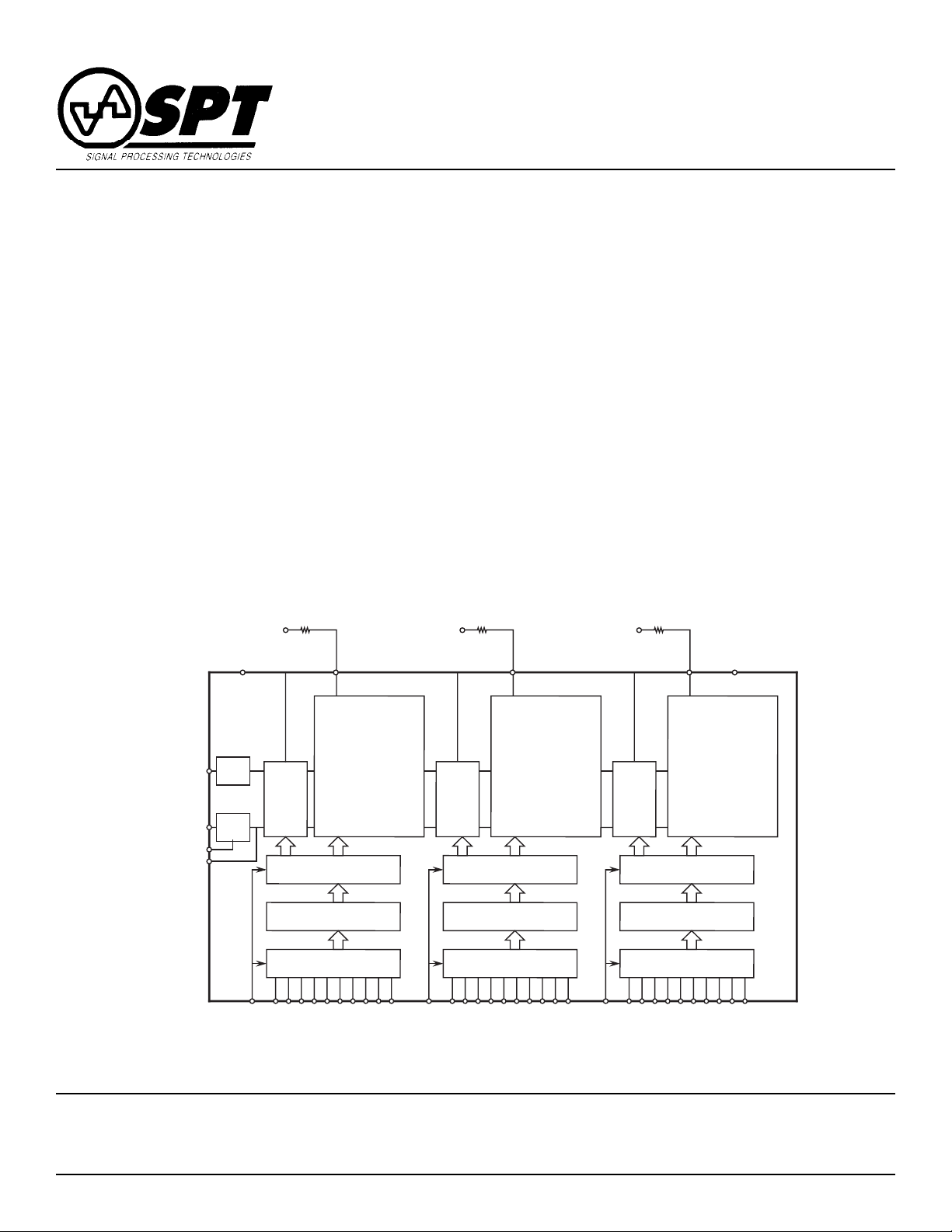

BLOCK DIAGRAM

R

OUT

AV

DD

AV

DD

I

OR

AV

DD

APPLICATIONS

• Desktop Video Processing

• CCIR-601 Video Signal Processing

• RGB Color Monitors

• Image Processing

• Direct Digital Synthesis

the full-scale output current. The differential linearity errors of

the DACs are guaranteed to be a maximum of ±1.0 LSB over

the full temperature range. The device is available in a 52lead QFP package over the commercial temperature range.

G

OUT

I

OG

B

DD

OUT

I

OB

V

SSA

AV

V

V

REF1

REF2

V

CS2

V

CS1

Current

V

REF

Current

Switch

Cell

Array

(Cell 4)

V

CS

Switch Cell

Array (Cell 255)

Current

Switch

Cell

Array

(Cell 4)

Latch

Decoder

Latch

DR6

DR7

CLKR

DR8

(MSB) DR9

DR5

DR4

DR3

DR2

DR1

(LSB) DRØ

CLKG

DG8

(MSB) DG9

Current

Switch Cell

Array (Cell 255)

Latch

Decoder

Latch

DG3

DG4

DG5

DG6

DG7

DG2

DG1

(LSB) DGØ

Current

Switch

Array

(Cell 4)

CLKB

Cell

DB8

(MSB) DB9

Current

Switch Cell

Array (Cell 255)

Latch

Decoder

Latch

DB6

DB7

DB5

DB4

DB3

DB2

DB1

(LSB) DBØ

Signal Processing Technologies, Inc.

4755 Forge Road, Colorado Springs, Colorado 80907, USA

Phone: (719) 528-2300 FAX: (719) 528-2370 Website: http://www.spt.com E-Mail: sales@spt.com

ABSOLUTE MAXIMUM RATINGS (Beyond which damage may occur)

Supply Voltages

AV

(measured to AVSS)...........................–0.3 to 7.0 V

DD

Output Current

I

...........................................................................

OUT

1

0 to 14 mA

Input Voltage

Clock and Data ......................................... AVSS to AV

DD

Temperature

Operating, ambient ........................................ 0 to +70 °C

Storage ...................................................–55 to + 125 °C

Note: 1. Operation at any Absolute Maximum Rating is not implied. See Electrical Specifications for proper nominal applied

conditions in typical applications.

ELECTRICAL SPECIFICATIONS

f

= 27 MWPS, AVDD = 5.0 V, Output Pull-Up Load = 75 Ω, TA = 25 °C, AVSS = 0.0 V

CLK

TEST TEST

PARAMETERS CONDITIONS LEVEL MIN TYP MAX UNITS

DC Performance

Resolution 10.0 Bits

Differential Linearity T

Integral Linearity I –2.5 2.0 LSB

Analog Outputs

Output Voltage Range V

Conversion Rate I 27 36 MWPS

Output Offset Voltage I 2.4 14 mV

Signal-to-Noise Ratio I 46 52 dB

Settling Time

Propagation Delay (t

Crosstalk I –49 –54 dB

FS Control Voltage (V

Digital Inputs and Timing

Input Current, Logic High V

Set-Up Time, Data and Controls (t

Hold Time, Data and Controls (t

Clock Duty Cycle V 40 60 %

Power Supply Requirements

Supply Voltage I 4.75 5.25 V

Supply Current 1 Vp-p Output IV 56 mA

Power Dissipation 1 Vp-p Output IV 280 mW

1

Full-scale settling time to within ±2% of full scale.

1

) V 10 12 ns

pd

) V 2.0 4.0 V

CS2

Logic Low V

)I5ns

S

) I 10 ns

h

= T

A

CS2

IH

= 0 V I –5 µA

IL

2 Vp-p Output I 100 mA

2 Vp-p Output I 485 500 mW

to T

MIN

= +2.1 V I 3.0 5.0 V

= 5 V I 5 µA

MAX

I –1.0 1.0 LSB

I1623ns

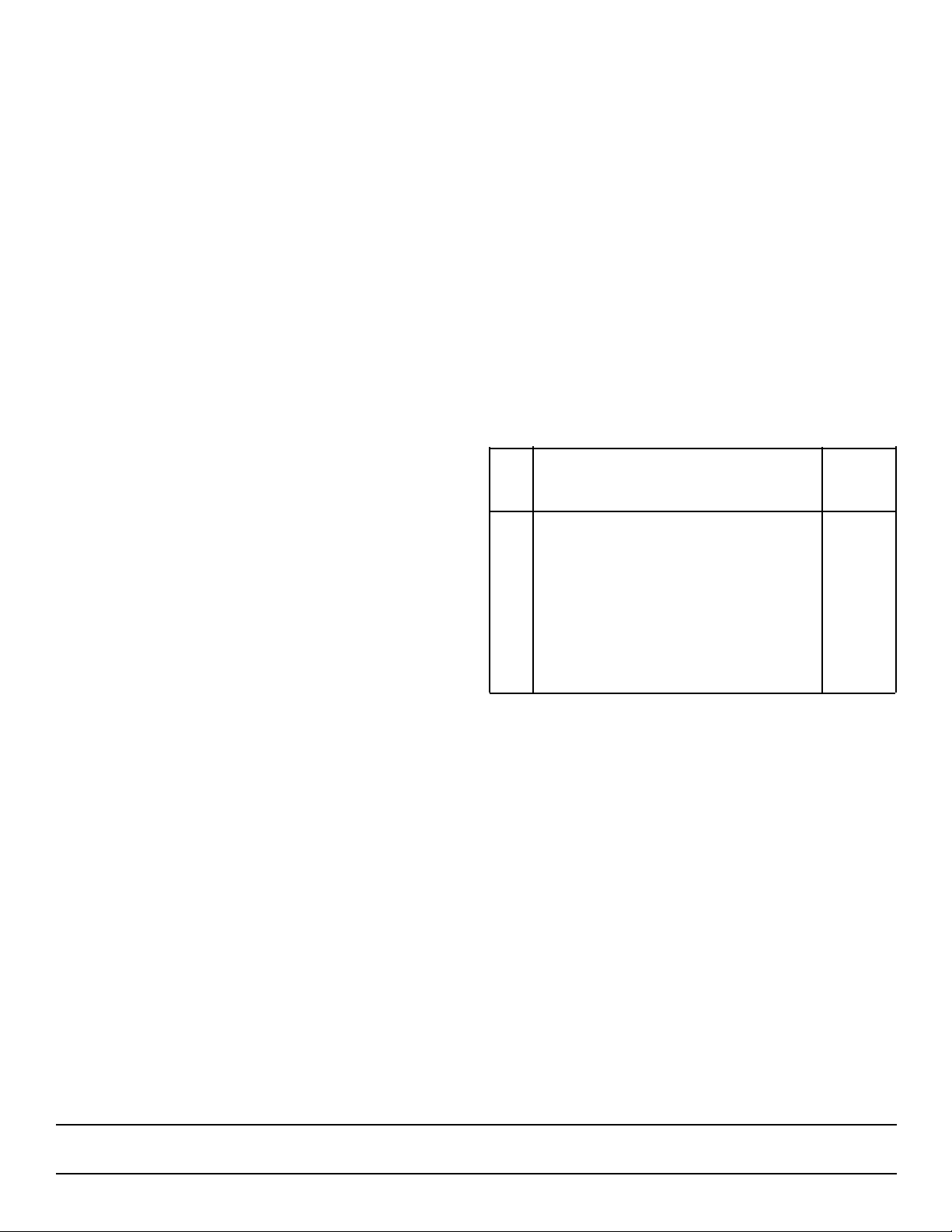

TEST LEVEL CODES

All electrical characteristics are subject to the

following conditions:

All parameters having min/max specifications

are guaranteed. The Test Level column indicates the specific device testing actually performed during production and Quality Assurance inspection. Any blank section in the data

column indicates that the specification is not

tested at the specified condition.

SPT

TEST LEVEL

I

II

III

IV

V

VI

2 5/1/00

TEST PROCEDURE

100% production tested at the specified temperature.

100% production tested at TA=25 °C, and sample

tested at the specified temperatures.

QA sample tested only at the specified temperatures.

Parameter is guaranteed (but not tested) by design

and characterization data.

Parameter is a typical value for information purposes

only.

100% production tested at TA = 25 °C. Parameter is

guaranteed over specified temperature range.

SPT5230

INTERFACE CONSIDERATIONS

Figure 4 shows a typical interface circuit of the SPT5230 in

normal circuit operation.

SUPPLY AND GROUND CONSIDERATIONS

SPT suggests that all power supply pins (AVDD) be tied

together and decoupled using a 0.1 µF ceramic capacitor in

parallel with a 10 µF tantalum capacitor.

EXTERNAL REFERENCE VOLTAGE (V

A +3 V (±10%) voltage reference should be externally generated for the V

pin using the simple voltage divider shown

REF1

in figure 4. Connect a 0.1 µF bypass capacitor between

V

and AVSS as close to the pin as possible.

REF1

EXTERNAL REFERENCE VOLTAGE (V

V

needs to be externally connected to AVDD through a

REF2

1.2 kΩ (5%) resistor. Connect a 0.1 µF bypass capacitor

between V

and AVSS as close to the pin as possible.

REF2

CONTROL VOLTAGE DECOUPLING (V

This is a decoupling pin for the control voltage internal

circuitry. An external 0.1 µF capacitor should be connected

between V

FULL-SCALE ADJUST CONTROL (V

V

is an external control voltage input that controls the

CS2

and AVSS as close to the pin as possible.

CS1

CS2

peak-to-peak full scale output voltage. This is the only external voltage that has direct control over the SPT5230 output

voltage. The voltage output swings between AVDD (+5 V) and

a value controlled by V

CS2

.

REF1

REF2

CS1

)

)

)

)

CURRENT OUTPUTS

Each red, green and blue current output should have a load

resistor connected to AVDD. The resistors are typically 75 Ω

and should be kept in the 72 Ω to 85 Ω range. The outputs

should drive a high impedance load such as a voltage

follower.

OUTPUT LEVEL SHIFTING CIRCUIT

The SPT5230 voltage output will swing from +3.0 V to +4.99

V for V

= 2.1 V as shown in table I. If level shifting of the

CS2

output is desired, SPT recommends use of the circuit shown

in figure 5. The desired –FS voltage is fed into the collector of

the emitter to achieve the desired level shift. (Note the phase

inversion that will occur due to the common emitter.) Choose

any appropriate video op amp with adequate power supply

head room.

Table I – Binary Codes

1 LSB = 1.953 mV, V

CS2

≈ 2.1 V

Digital Input Analog

Step A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 Out (V)

(MSB) (LSB)

0 00000000003.000000

1 00000000013.001953

2 00000000103.003906

3 00000000113.005859

. . .

. . .

. . .

1022 11111111104.996094

1023 11111111114.998047

Assuming that an output load resistor of 75 Ω is connected

between the output and AVDD, figure 2 shows what the output

voltage will be for the digital inputs all equal to logic 0, as V

CS2

is varied from 2 V to 4 V. Figure 3 shows the peak-to-peak

output voltage versus V

which V

is equal to 2.1 V.

CS2

and table I shows an example in

CS2

SPT

SPT5230

3 5/1/00

Loading...

Loading...