SPT SPT5220SCN Datasheet

SPT5220

10-BIT, 80 MWPS VIDEO DAC

FEATURES

• 80 MWPS Pipelined Operation

• +5 V CMOS Monolithic Construction

• ±0.4 LSB Differential Linearity Error

• ±0.6 LSB Integral Linearity Error

• TTL-Compatible Inputs

• RS-343A/RS-170 Compatible Outputs

• Binary or Two's Complement Input Data Format

• Low Power Dissipation of 260 mW

• Internal/External Voltage Reference

GENERAL DESCRIPTION

The SPT5220 is a monolithic 10-bit, 80 MWPS CMOS D/A

converter for high-resolution color graphics and video

system applications. The device operates from a single

+5 V power supply and all digital inputs are TTL/CMOS

compatible.

The SPT5220 generates RS343A-compatible video outputs

(capable of driving a doubly-terminated 75 Ω load) and

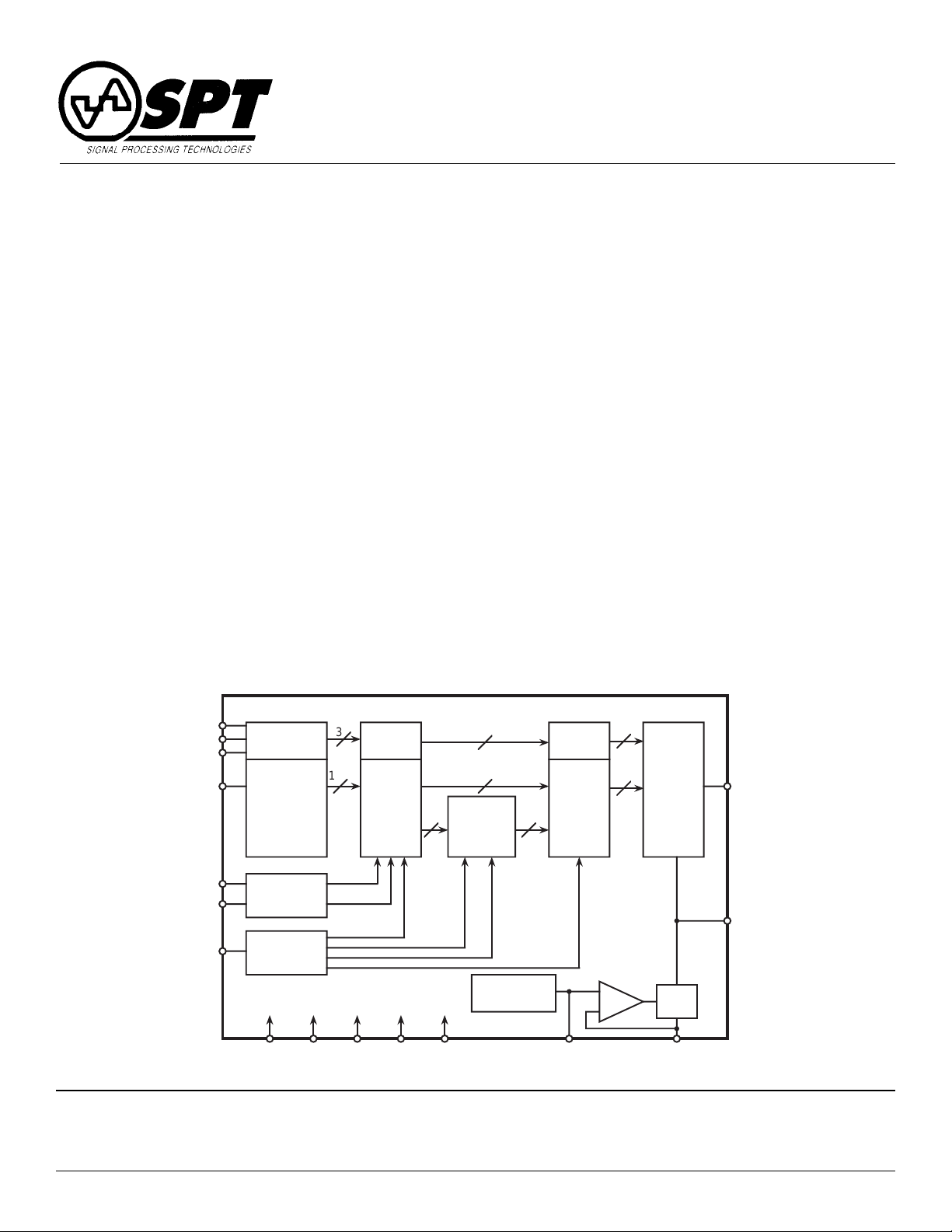

BLOCK DIAGRAM

APPLICATIONS

• High Resolution Color Graphics

• Medical Electronics: CAT, PET, MR Imaging Displays

• CAD/CAE Workstations

• General Purpose High-Speed D/A Conversion

• Direct Digital Synthesis (DDS)

• Digital Radio Transmitters/Modulators

• High Definition Television (HDTV)

RS170-compatible video outputs (capable of driving a singlyterminated 75 Ω load) without the need for external buffers.

The data latches minimize the data time skew and reduce the

glitches that can adversely affect many applications.

The device is available in a 28-lead plastic DIP package over

the commercial temperature range.

Sync

Blank

Bright

DØ-D9

N2C

Inverse

Clock

3

Digital

Input

Buffer

Code

Clock

Generator

DVDDDVSSV

10

BB

First

Latch

AVDDAV

3

5

5 31

Decoder

BGR

SS

Second

Latch

V

REF

36

Amp

3

DAC

CM

R

SET

Signal Processing Technologies, Inc.

4755 Forge Road, Colorado Springs, Colorado 80907, USA

Phone: (719) 528-2300 FAX: (719) 528-2370

I

OUT

Comp

ABSOLUTE MAXIMUM RATINGS (Beyond which damage may occur)

1,2,3

Supply Voltages

ESD Susceptibility ..............................................±2,000 V

AVDD.......................................................... -0.5 to +7.0 V

DVDD......................................................... -0.5 to +7.0 V

Temperature

Operating Temperature Range (Ambient) .....0 to +70 °C

Input Voltages

Storage Temperature................................-55 to +150 °C

Any Digital Pin .................... DVSS-3.0 V to DVDD+3.0 V

Notes: 1. Operation at any absolute maximum rating is not implied. See Electrical Specifications for proper nominal

applied conditions in typical applications.

2. Absolute maximum ratings are limiting values applied individually while all other parameters are within

specified operating conditions. Functional operation under any of these conditions is not implied.

3. Applied voltage must be current limited to the specified range.

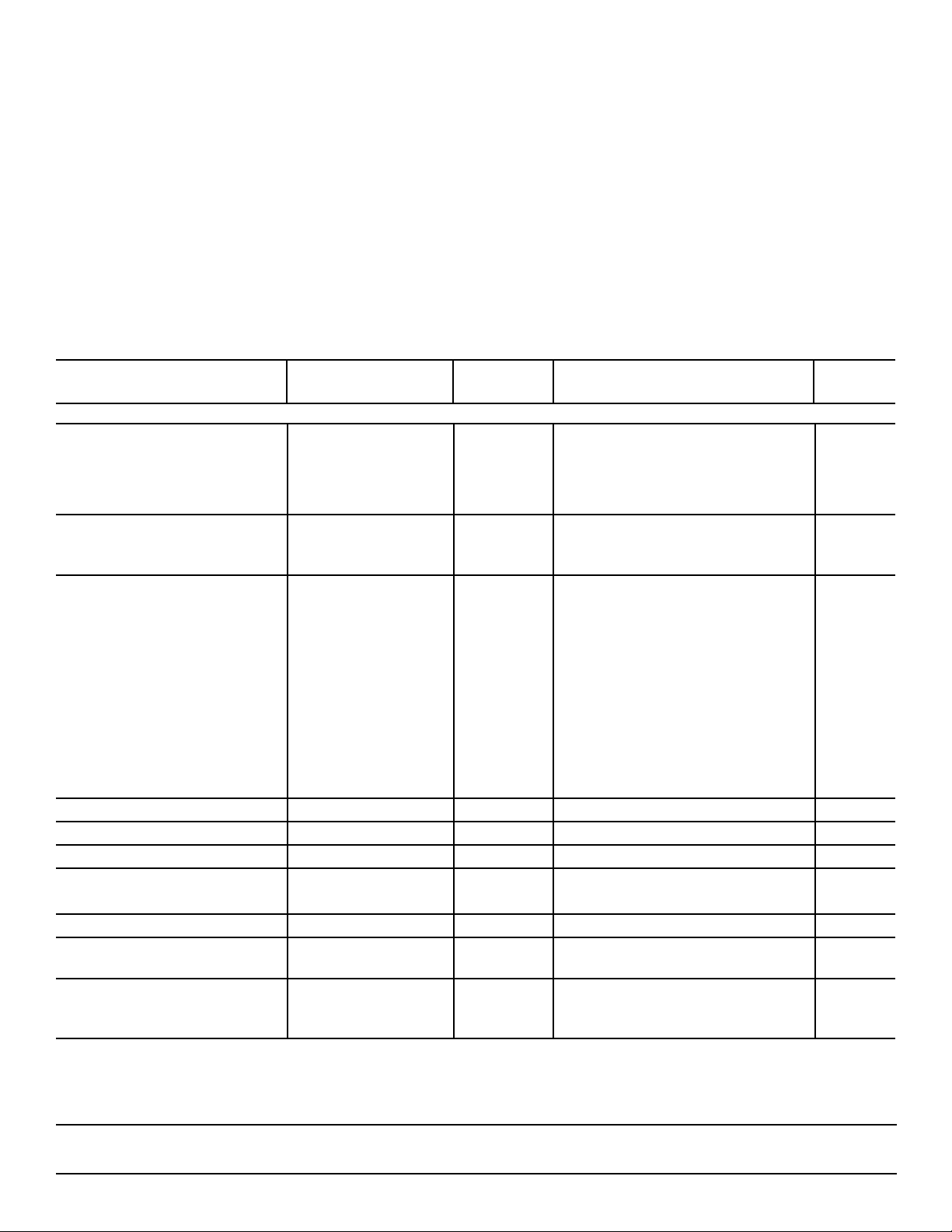

ELECTRICAL SPECIFICATIONS

TA=T

PARAMETERS CONDITIONS LEVEL MIN TYP MAX UNITS

DC CHARACTERISTICS

Resolution 10 Bits

Differential Linearity Error VI ±0.4 ±1.0 LSB

Integral Linearity Error VI ±0.6 ±1.0 LSB

Gray Scale Error VI ±5.0 % Gray

Monotonicity VI Guaranteed

Digital Input High Current V

Digital Input Low Current V

Digitial Input Capacitance fIN=1 MHz IV 20 40 pF

Analog Outputs

Internal Reference Voltage VI 1.16 1.235 1.36 V

Power Supply Rejection Ratio fIN=1 kHz, comp=0.1 µF V -30 dB

Operating Supply Voltage VI 4.75 5.00 5.25 V

Digital Input Voltage High VI 2.0 V

Effective Output Load V 37.5 Ω

Data Input Setup Time IV 2.0 ns

Data Input Hold Time IV 2.0 ns

Clock Cycle Time IV 12.5 ns

Clock Pulse Width High IV 5 ns

Clock Pulse Width Low IV 5 ns

to T

MIN

Gray Scale Current VI 22 mA

Output Current

Output Compliance VI -1.0 +1.5 V

Output Impedence V 11 kΩ

Output Capacitance fIN=1 MHz IV 14 30 pF

, AVDD=DVDD=VBB=+5.0 V, AVSS=DVSS=0.0 V, V

MAX

4

=1.235 V, R

REF

TEST TEST SPT5220

=2.4 V VI 1.0 µA

IN

=0.4 V VI -1.0 µA

IN

Bright to White VI 1.0 1.90 3.0 mA

White to Black VI 18.1 19.05 20.0 mA

Black to Blank VI 0.5 1.43 2.5 mA

Blank to Sync VI 6.5 7.62 8.5 mA

Sync Level VI 0 5 50 µA

LSB Size V 18.62 µA

Low VI VSS-0.3 0.8 V

=165 Ω, unless otherwise specified.

SET

DD

+0.3 V

Note: 4. To avoid power latch-up, drive all supply pins (AVDD, DVDD, and VBB) from the same source.

SPT

2 12/30/98

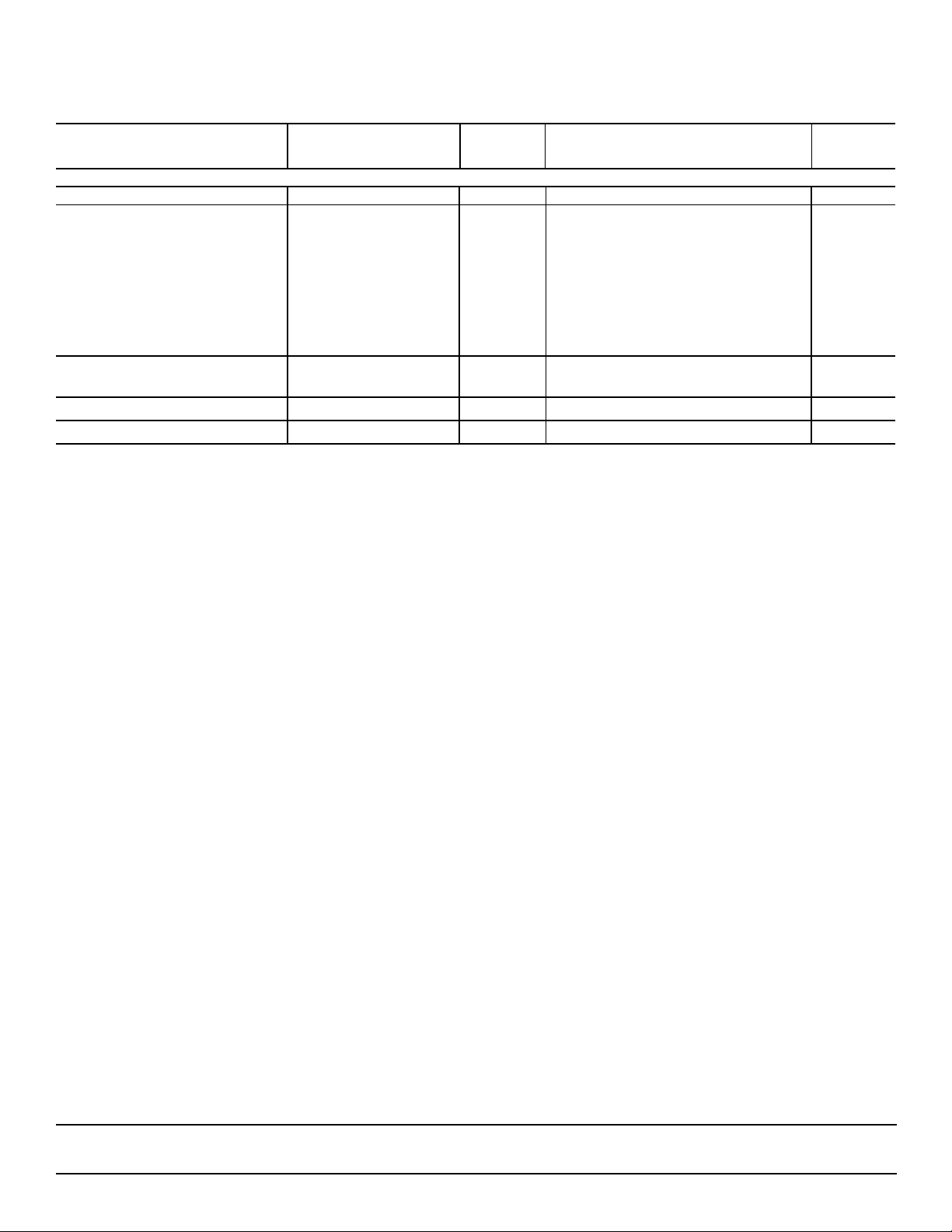

SPT5220

ELECTRICAL SPECIFICATIONS

TA=T

PARAMETERS CONDITIONS LEVEL MIN TYP MAX UNITS

AC CHARACTERISTICS

Clock Rate 80 MWPS

Analog Output Delay V 7 ns

Analog Output Rise Time V 4 ns

Analog Output Fall Time V 4 ns

Analog Output Settling Time

Clock and Data Feedthrough

Glitch Impulse

Differential Gain Error V 0.8 %

Differential Phase Error V 0.9 Degree

Pipeline Delay (Clock Latency) IV 1 Clock Cycles

VDD Supply Current

to T

MIN

to ±1 LSB IV 100 150 ns

to ±2 LSB IV 70 100 ns

, AVDD=DVDD=VBB=+5.0 V, AVSS=DVSS=0.0 V, V

MAX

TEST TEST SPT5220

5

5

5

6

=1.235 V, R

REF

V -34 dB

IV 30 pv-sec

VI 50 70 mA

=165 Ω, unless otherwise specified.

SET

Note: 5. Clock and data feedthrough are functions of the amount of overshoot and undershoot on the digital inputs.

For this test, the digital inputs have a 1 kΩ resistor to ground driven by 74HC logic. Settling time does not

include clock and data feedthrough. Glitch impulse includes clock and data feedthrough.

6. At f

, IDD (typ) at AVDD=DVDD=5.25 V, CLK=0 V to 3 V (80 MWPS), NC2=High, Data (DØ-D9)=0 V to 3 V

MAX

(40 MWPS), Inverse=Sync=Blank=Bright=Low.

TEST LEVEL CODES

All electrical characteristics are subject to the

following conditions:

All parameters having min/max specifications

are guaranteed. The Test Level column indicates the specific device testing actually performed during production and Quality Assurance inspection. Any blank section in the data

column indicates that the specification is not

tested at the specified condition.

TEST LEVEL

I

II

III

IV

V

VI

TEST PROCEDURE

100% production tested at the specified temperature.

100% production tested at TA=+25 °C, and sample

tested at the specified temperatures.

QA sample tested only at the specified temperatures.

Parameter is guaranteed (but not tested) by design

and characterization data.

Parameter is a typical value for information purposes

only.

100% production tested at TA = 25 °C. Parameter is

guaranteed over specified temperature range.

SPT

SPT5220

3 12/30/98

Loading...

Loading...