SPT SPT5110SCT Datasheet

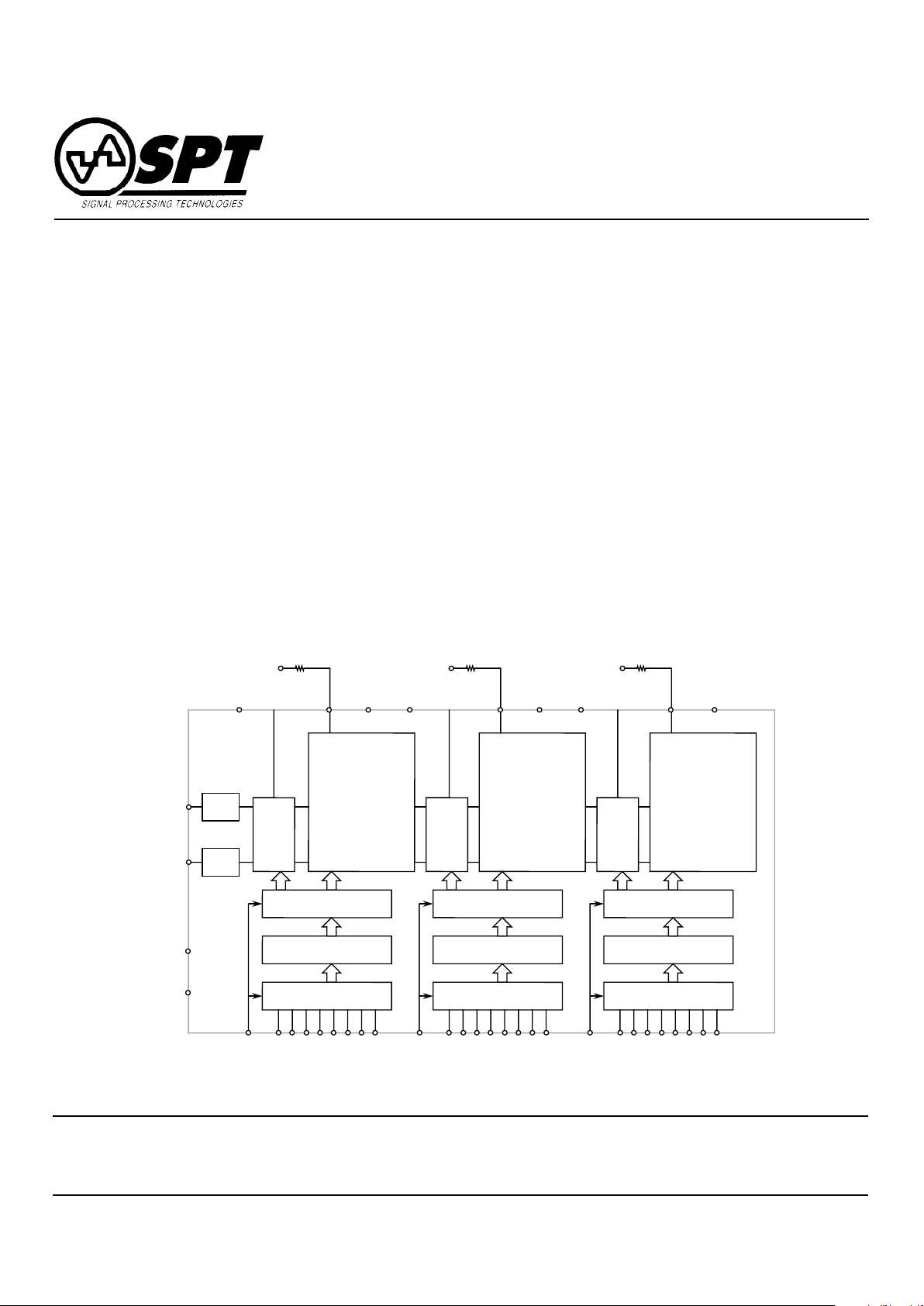

SPT5110

8-BIT, 30 MWPS TRIPLE VIDEO DAC

FEATURES

• 8-Bit Triple Video Digital-to-Analog Converter

• 30 MWPS Operation (typ)

• Low Power: 135 mW

• Internal Voltage Reference

• 5 V Monolithic CMOS

• 48-Pin QFP Package (7 mm x 7 mm, 0.5 mm Pitch)

Current

Switch

Cell

Array

(Cell 4)

Current

Switch Cell

Array (Cell 63)

Latch

Decoder

Latch

AV

DD

I

OR

(LSB) DRØ

DR1

DR2

DR3

DR4

DR5

DR6

(MSB) DR7

CLKR

V

CS

V

REF

Current

Switch Cell

Array (Cell 63)

Latch

Decoder

Latch

I

OB

(LSB) DBØ

DB1

DB2

DB3

DB4

DB5

DB6

(MSB) DB7

CLKB

Current

Switch Cell

Array (Cell 63)

Latch

Decoder

Latch

R

OUT

B

OUT

G

OUT

I

OG

(LSB) DGØ

DG1

DG2

DG3

DG4

DG5

DG6

(MSB) DG7

CLKG

V

CS

V

REF

AV

DD

AV

DD

Current

Switch

Cell

Array

(Cell 4)

Current

Switch

Cell

Array

(Cell 4)

AV

DD

AV

DD

AV

SS

AV

DD

AV

DD

AV

SS

AV

SS

AV

DD

GENERAL DESCRIPTION

The SPT5110 is an 8-bit, 30 MWPS triple video digital-toanalog converter specifically designed for high performance,

high resolution color graphics monitor and video processing

applications. A single external resistor controls the fullscale output current. The differential linearity errors of the

DACs are guaranteed to be a maximum of ±0.5 LSB over the

full temperature range. The device is available in a 48-lead

QFP package in the commercial temperature range.

APPLICATIONS

• Desktop Video Processing of S-Video and CCIR-601

Video Signals

• VGA Color Graphics Monitors

• Professional Video Equipment

• Digital Television

Signal Processing Technologies, Inc.

4755 Forge Road, Colorado Springs, Colorado 80907, USA

Phone: (719) 528-2300 FAX: (719) 528-2370

BLOCK DIAGRAM

SPT

2 3/14/97

SPT5110

ELECTRICAL SPECIFICATIONS

f

CLK

= 27 MWPS, AVDD = 5.0 V, Output Pull-Up Load = 240 Ω, TA = 25 °C, AVSS = 0.0 V, unless otherwise specified.

TEST TEST

PARAMETERS CONDITIONS LEVEL MIN TYP MAX UNITS

DC ELECTRICAL CHARACTERISTICS

DC Performance

Resolution 8.0 Bits

Differential Linearity I ±0.25 ±0.3 LSB

Differential Linearity T

A

= T

MIN

to T

MAX

I ±0.5 LSB

Integral Linearity I ±0.5 ±1.0 LSB

Analog Outputs

Output Voltage Range V

CS

= +1.27 V I 3.6 5.0 V

Conversion Rate I 27 30 MWPS

Output Offset Voltage I 17 25 mV

Signal-to-Noise Ratio I 41 47 dB

Differential Phase V 1 Degrees

Differential Gain V 2 %

Glitch Energy V 100 pV-s

Settling Time I 31 27 ns

Propagation Delay (t

pd

) V 10 12 ns

Crosstalk I -47 dB

FS Control Voltage (VCS) V 1.0 1.4 V

Digital Inputs and Timing

Input Current, Logic High VIH = 5 V I 5 µA

Logic Low V

IL

= 0 V I -5 µA

Set-Up Time, Data and Controls (t

S

)I5 ns

Hold Time, Data and Controls (t

h

) I 10 ns

Clock Pulse Width (Low) I 18.5 ns

Clock Pulse Width (High) I 18.5 ns

Power Supply Requirements

Supply Voltage I 4.75 5.25 V

Supply Current I 27 mA

Power Dissipation I 135 mW

ABSOLUTE MAXIMUM RATING (Beyond which damage may occur)

1

Supply Voltages

AV

DD

(measured to AVSS)........................... -0.3 to 7.0 V

Input Voltage

Clock and Data .........................................AVSS to AV

DD

Output Current

I

OUT

.............................................................................

0 to 7 mA

Temperature

Operating, ambient ........................................0 to +70 °C

Storage .....................................................-55 to +125 °C

Note: 1. Operation at any Absolute Maximum Ratings is not implied. See Electrical Specifications for proper nominal applied

conditions in typical applications.

Loading...

Loading...