Page 1

Monaco

Quad 'C6x VME64 Board

Technical Reference

Document Number 500-00191

Revision 2.00

September 1999

Page 2

Copyright © 1999 Spectrum Signal Processing Inc.

All rights reserved, including those to reproduce this document or parts thereof in any form without permission in writing from

Spectrum Signal Processing Inc.

All trademarks are registered trademarks of their respective owners.

Spectrum Signal Processing reserves the right to change any of the information contained herein without notice.

ii

Part Number 500-00191

Revision 2.00

Page 3

Spectrum Signal Processing Monaco Technical Reference

Preface

Preface

About

Spectrum

Contacting

Spectrum

Spectrum Signal Processing offers a complete line of DSP hardware, software and I/O

products for the DSP Systems market based on the latest DSP microprocessors, bus

interface standards, I/O standards and software development environments. By delivering

quality products, and DSP expertise tailored to specific application requirements,

Spectrum can consistently exceed the expectations of our customers. We pride ourselves

in providing unrivaled pre- and post-sales support from our team of application

engineers. Spectrum’s excellent relationships with third party vendors provide customers

with a diverse and top quality product offering.

In 1994, Spectrum achieved ISO 9001 quality certification.

Spectrum’s Applications Engineers are available to provide technical support Monday to

Friday, 8:00 AM to 5:00 PM, Pacific Standard Time.

Telephone 1-800-663-8986 or (604) 421-5422

Fax (604) 421-1764

Email support@spectrumsignal.com

Internet http://www.spectrumsignal.com

To help us assist you better and faster, please have the following information ready:

• A concise description of the problem

• The names of all Spectrum hardware components

Customer

Feedback

• The names and version numbers of all Spectrum software components

• The minimum amount of code that demonstrates the problem

• The versions of all software packages, including compilers and operating systems

At Spectrum, we know that accurate and easy to use manuals are important to help you

develop your applications and products. If you wish to comment on this manual, please

e-mail us at documentation@spectrumsignal.com or fax us at (604) 421-1764. Please

include the following information:

• The full name, document number, and version of the manual

• A description of any inaccuracies you may have found

• Comments about what you liked or did not like about the manual

It may be helpful for us to call you to discuss your comments. If this would be acceptable

please include your name, organization, and telephone number with your comments.

Note: Spectrum board products are static sensitive and can be damaged by electrostatic

discharges if not properly handled. Use proper electrostatic precautions whenever

handling Spectrum board products.

Part Number 500-00191

Revision 2.00

iii

Page 4

Monaco Technical Reference Spectrum Signal Processing

Preface

Document

Change

History

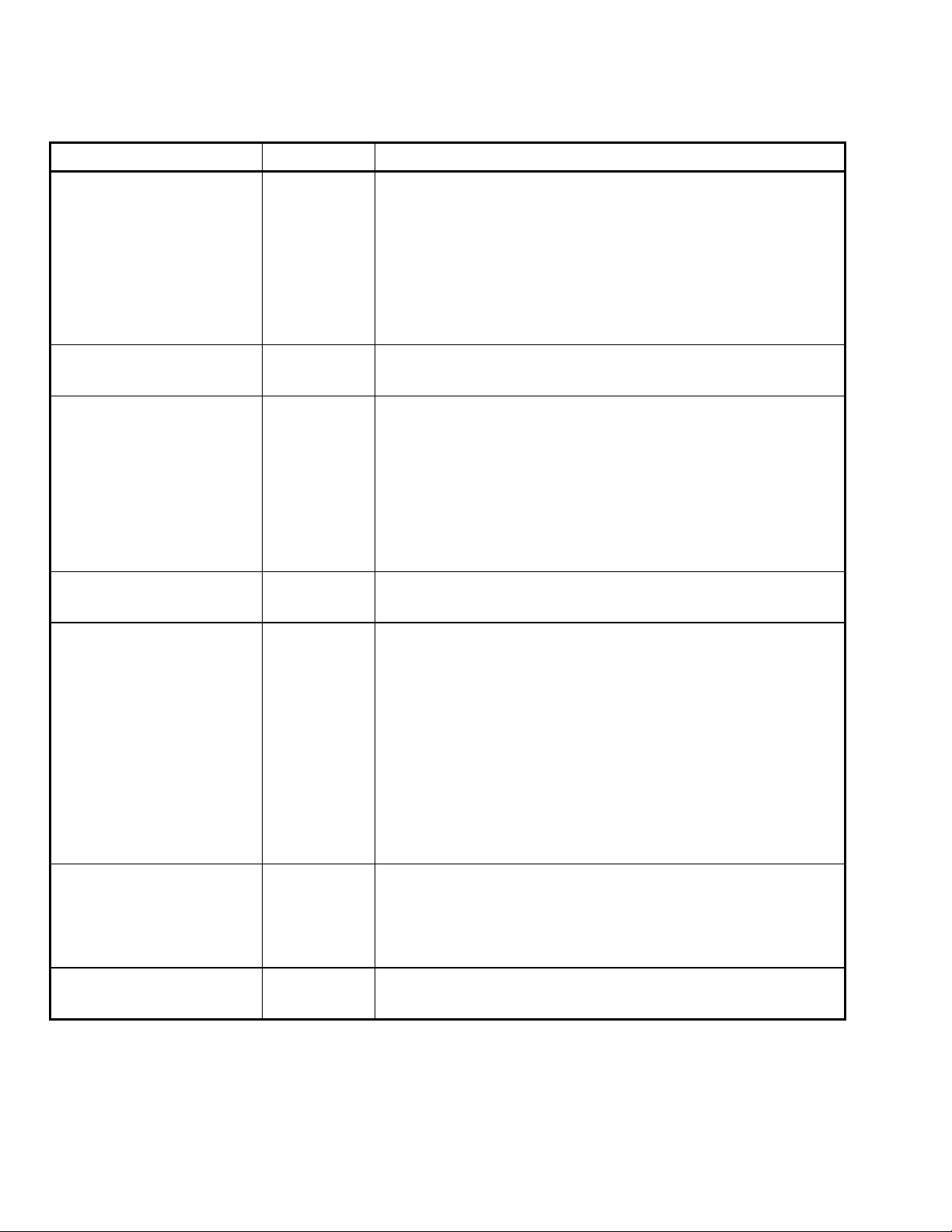

Rev. Date Changes Section

2.00 Sept 1999 Updated for TMS320C6201B and TMS320C6701

n.a.

DSPs

iv

Part Number 500-00191

Revision 2.00

Page 5

Spectrum Signal Processing Monaco Technical Reference

Table of Contents

Table of Contents

1 Introduction..............................................................................................................................1

1.1. Features....................................................................................................................................1

1.2. Interfaces ..................................................................................................................................2

1.2.1. VME.............................................................................................................................2

1.2.2. PMC ............................................................................................................................2

1.2.3. PEM.............................................................................................................................2

1.2.4. Serial Ports..................................................................................................................2

1.2.5. JTAG...........................................................................................................................2

1.3. Reference Documents..............................................................................................................3

1.4. General Bus Architecture..........................................................................................................4

1.5. On-Board Power Supply ...........................................................................................................4

1.6. Reset Conditions.......................................................................................................................5

1.6.1. VME SYSRESET ........................................................................................................5

1.6.2. VME A24 Slave Interface Reset..................................................................................5

1.6.3. JTAG Reset.................................................................................................................5

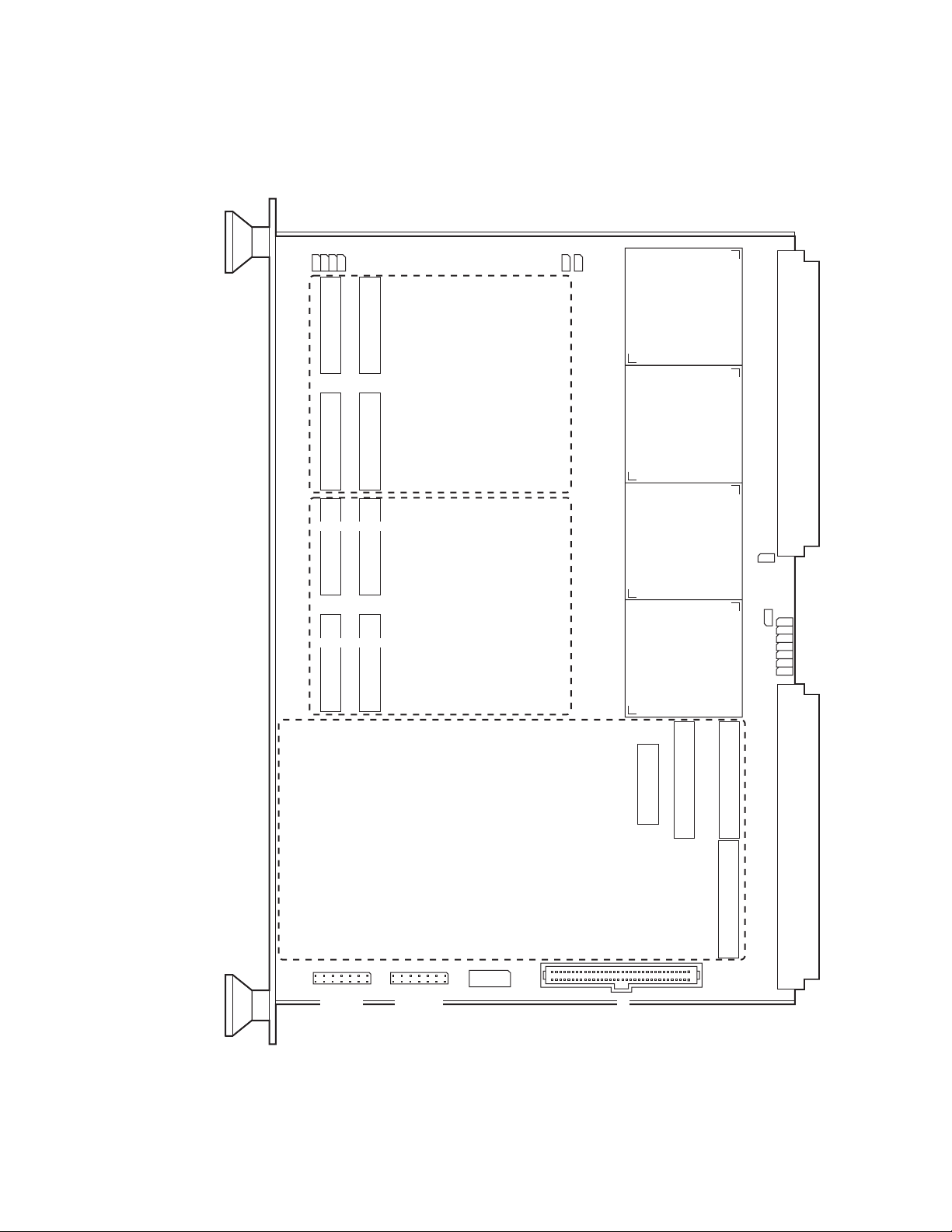

1.7. Board Layout.............................................................................................................................6

1.8. Jumper settings.........................................................................................................................7

2 Processor Nodes.....................................................................................................................9

2.1. Processor Memory Configuration ...........................................................................................11

2.1.1. Internal Memory ........................................................................................................11

2.1.2. External Memory.......................................................................................................11

2.2. Synchronous Burst SRAM......................................................................................................15

2.3. Synchronous DRAM ...............................................................................................................15

2.4. Processor Expansion Module.................................................................................................15

2.5. Host Port.................................................................................................................................15

2.6. Interrupt Lines.........................................................................................................................15

2.7. Processor Booting...................................................................................................................16

2.8. Serial Port Routing..................................................................................................................17

3 Global Shared Bus................................................................................................................19

3.1. Memory...................................................................................................................................19

3.2. Arbitration................................................................................................................................19

3.2.1. Single Cycle Bus Access ..........................................................................................20

3.2.2. Burst Cycle Bus Access............................................................................................20

Part Number 500-00191

Revision 2.00

v

Page 6

Monaco Technical Reference Spectrum Signal Processing

Table of Contents

3.2.3. Locked Cycles...........................................................................................................21

4 VME64 Bus Interface............................................................................................................23

4.1. VME Operation........................................................................................................................23

4.2. SCV64 Primary Slave A32/A24 Interface................................................................................23

4.3. A24 Secondary Slave Interface...............................................................................................24

4.4. Master A32/A24/A16 SCV64 Interface....................................................................................27

5 DSP~LINK3 Interface............................................................................................................29

5.1. DSP~LINK3 Data Transfer Operating Modes.........................................................................29

5.2. Address Strobe Control Mode.................................................................................................30

5.3. Interface Signals .....................................................................................................................31

5.4. DSP~LINK3 Reset ..................................................................................................................31

6 PCI Interface.........................................................................................................................33

6.1. Hurricane Configuration..........................................................................................................33

6.2. Hurricane Implementation.......................................................................................................36

7 JTAG Debugging...................................................................................................................37

8 Interrupt Handling..................................................................................................................39

8.1. Overview.................................................................................................................................39

8.2. DSP~LINK3 Interrupts to Node A ...........................................................................................40

8.3. PEM Interrupts........................................................................................................................41

8.4. PCI Bus Interrupts...................................................................................................................41

8.5. Hurricane Interrupt..................................................................................................................41

8.6. SCV64 Interrupt ......................................................................................................................41

8.7. Bus Error Interrupts.................................................................................................................43

8.8. Inter-processor Interrupts........................................................................................................44

8.9. VME Host Interrupts To Any Node..........................................................................................44

9 Registers...............................................................................................................................45

VPAGE Register..................................................................................................................46

VSTATUS Register .............................................................................................................47

VINTA Register ...................................................................................................................49

VINTB Register ...................................................................................................................50

VINTC Register...................................................................................................................51

VINTD Register...................................................................................................................52

KIPL Enable Register.........................................................................................................53

vi

Part Number 500-00191

Revision 2.00

Page 7

Spectrum Signal Processing Monaco Technical Reference

Table of Contents

DSP~LINK3 Register ..........................................................................................................54

ID Register ..........................................................................................................................55

VME A24 Status Register....................................................................................................56

VME A24 Control Register..................................................................................................57

10 Specifications......................................................................................................................59

10.1. Board Identification ...............................................................................................................59

10.2. General .................................................................................................................................60

10.3. Performance and Data Throughput ......................................................................................61

11 Connector Pinouts...............................................................................................................63

11.1. VME Connectors...................................................................................................................64

11.2. PMC Connectors...................................................................................................................67

11.3. PEM Connectors...................................................................................................................71

11.4. JTAG Connectors .................................................................................................................73

Part Number 500-00191

Revision 2.00

vii

Page 8

Monaco Technical Reference Spectrum Signal Processing

Table of Contents

viii

Part Number 500-00191

Revision 2.00

Page 9

Spectrum Signal Processing Monaco Technical Reference

Table of Contents

List of Figures

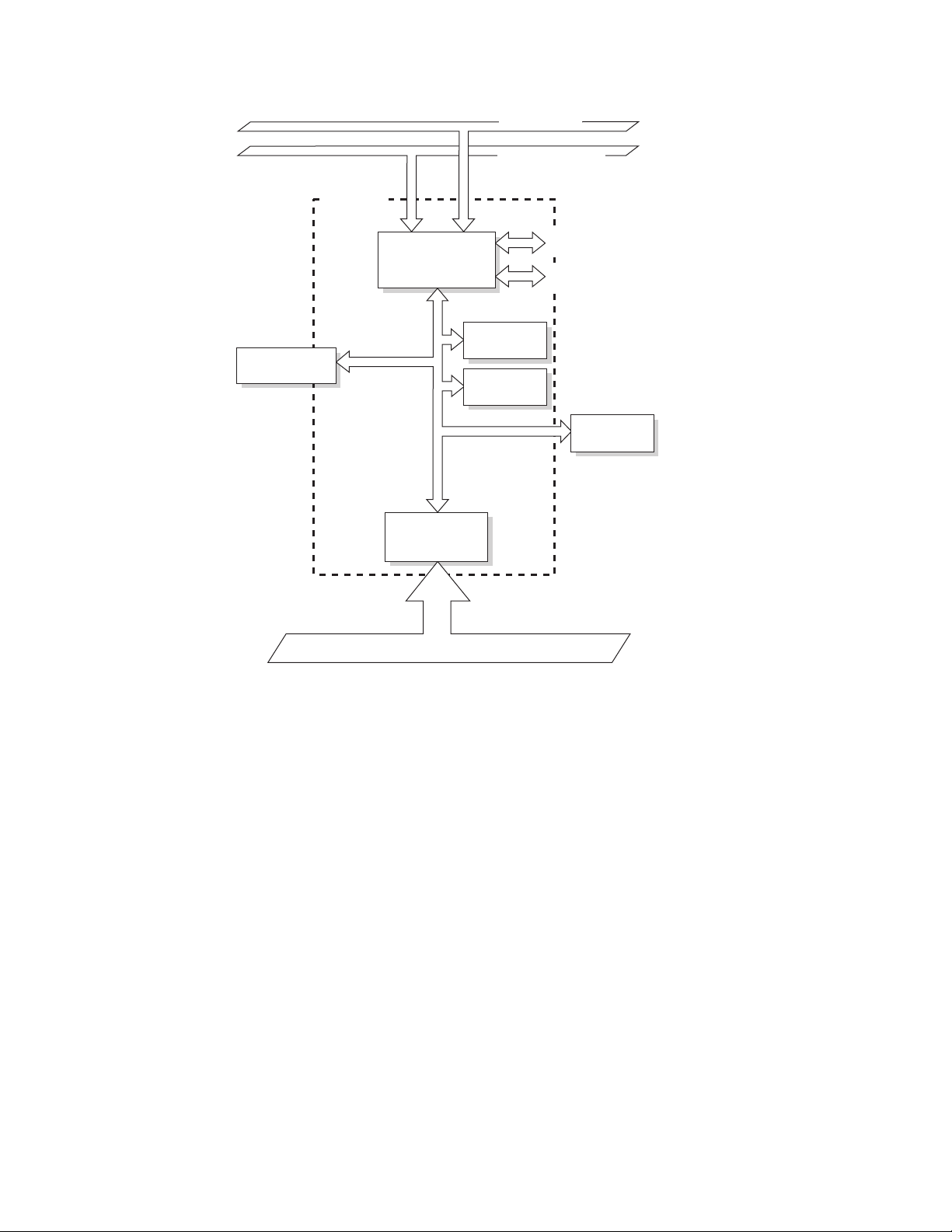

Figure 1 Block Diagram...................................................................................................................4

Figure 2 Board Layout.....................................................................................................................6

Figure 3 Processor Node Block Diagram......................................................................................10

Figure 4 DSP Memory Map...........................................................................................................13

Figure 5 DSP Memory Map for External-Memory Space CE1......................................................14

Figure 6 Serial Port Routing ..........................................................................................................17

Figure 7 Global Bus Arbitration .....................................................................................................20

Figure 8 Primary VME A24/A32 Memory Map ..............................................................................24

Figure 9 A24 Secondary Interface Memory Map...........................................................................25

Figure 10 PCI Memory Map ..........................................................................................................33

Figure 11 JTAG Chain...................................................................................................................37

Figure 12 Interrupt Routing............................................................................................................40

Figure 13 Connector Layout..........................................................................................................63

Part Number 500-00191

Revision 2.00

ix

Page 10

Monaco Technical Reference Spectrum Signal Processing

Table of Contents

x

Part Number 500-00191

Revision 2.00

Page 11

Spectrum Signal Processing Monaco Technical Reference

Table of Contents

List of Tables

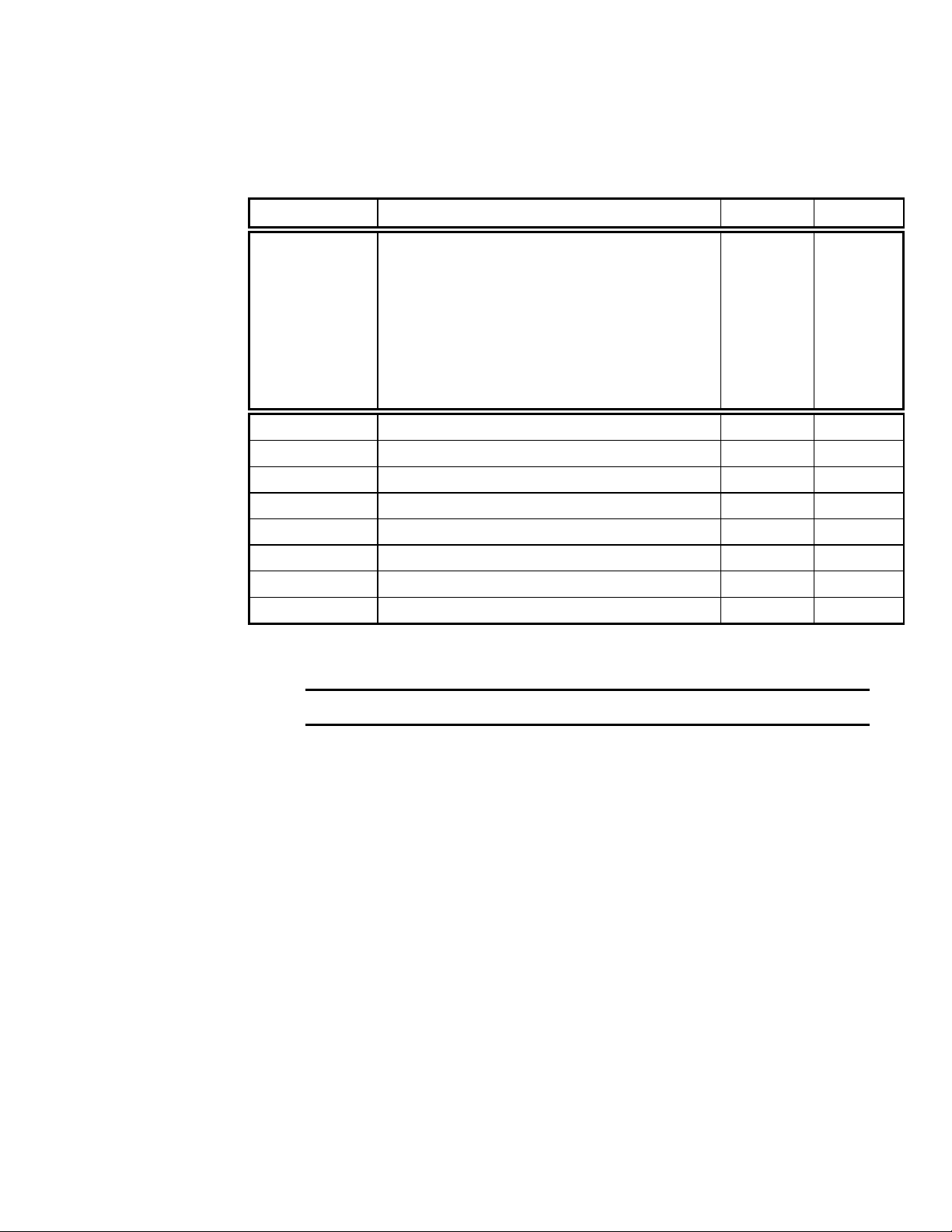

Table 1 Reset Summary..................................................................................................................5

Table 2 Jumper Settings..................................................................................................................7

Table 3 Processor Configurations...................................................................................................9

Table 4 'C6x Internal Peripheral Register Values..........................................................................12

Table 5 Processor Boot Source Jumpers......................................................................................16

Table 6 PEM Connections for Serial Port 0 and 1.........................................................................18

Table 7 VME and PMC Connections for Serial Port 1....................................................................18

Table 8 Global Shared Bus Access...............................................................................................19

Table 9 HPI Register Addresses...................................................................................................26

Table 10 DSP~LINK3 Data Transfer Operating Modes ................................................................30

Table 11 Hurricane Register Set...................................................................................................34

Table 12 KIPL Status Bits and the IACK Cycle.............................................................................42

Table 13 Register Address Summary............................................................................................45

Table 14 Specifications .................................................................................................................60

Table 15 Data Access/Transfer Performance...............................................................................61

Table 16 VME P1 Connector Pinout..............................................................................................64

Table 17 VME P2 Connector Pinout (PMC to VME P2)................................................................65

Table 18 VME P2 Connector (DSP~LINK3 to VME P2)................................................................66

Table 19 PMC Connector JN1 Pinout ...........................................................................................67

Table 20 PMC Connector JN2.......................................................................................................68

Table 21 PMC Connector JN4.......................................................................................................69

Table 22 Non-standard PMC Connector JN5................................................................................70

Table 23 PEM 1 Connector Pinout................................................................................................71

Table 24 PEM 2 Connector Pinout................................................................................................72

Table 25 JTAG IN Connector Pinout.............................................................................................73

Table 26 JTAG OUT Connector....................................................................................................73

Table 27 SCV64 Register Initialization..........................................................................................75

Part Number 500-00191

Revision 2.00

xi

Page 12

Monaco Technical Reference Spectrum Signal Processing

Table of Contents

xii

Part Number 500-00191

Revision 2.00

Page 13

Spectrum Signal Processing Monaco Technical Reference

Introduction

1 Introduction

This manual describes the features, architecture, and specifications of the Monaco Quad

'C6x VME64 Board. You can use this information to program the board at a driver level,

extend the standard hardware functionality, or develop custom configurations.

1.1. Features

Spectrum’s Monaco VME64 board consists of four TMS320C6x processing nodes. It is

available with either fixed-point or floating-point TMS320C6x processors.

Product Operation Processors Processor Clock Speed

Monaco Fixed-point TMS320C6201 200 MHz

Monaco67 Floating-point TMS320C6701 167 MHz

Both the Monaco and the Monaco67 are referred to as “Monaco” in this manual unless

otherwise noted.

Monaco has the following features:

• Up to four TMS320C6201 or TMS320C6701 processing nodes

• 128K x 32-bit of SBSRAM per processing node

• 4M x 32-bit of SDRAM per processing node

• Shared access to a 132 MBytes/s PMC module site via the Spectrum Hurricane chip

• 512K x 32-bit of fast, globally shared SRAM accessible to the processor nodes, PCI

interface, and VME64 interface.

• VME64 master/slave interface provided by Tundra Semiconductor’s SCV64 chip

• VME A24 slave interface access to the ‘C6x Host Port Interfaces (HPIs)

• JTAG debugging support

• Two PEM (Processor Expansion Module) sites

• DSP~LINK3 I/O interface supporting IndustryPack™ modules

Part Number 500-00191

Revision 2.00

1

Page 14

Monaco Technical Reference Spectrum Signal Processing

Introduction

1.2. Interfaces

In addition to the VME bus which provides the primary interface to the host computer,

the Monaco board features PMC, PEM, serial port, DSP~LINK3 and JTAG interfaces.

1.2.1. VME

Two VMEbus interfaces are provided on the Monaco board. The primary dataflow

interface supports VME64 master and slave modes for fast data transfer through the

SCV64 interface chip.

A secondary interface gives the VME A24 bus direct access to the Host Port Interface

(HPI) of each ‘C6x. This provides direct control and data transfer to and from the DSP

without interfering with dataflow on the Monaco’s Global Shared Bus.

1.2.2. PMC

The Spectrum Hurricane PCI bridge chip supports high-speed data transfer from an onboard PMC site to the shared memory. The industry-standard IEEE-1386 PMC module

site allows developers to select from a wide variety of third-party modules.

1.2.3. PEM

Four independent high-speed, full-bandwidth, bi-directional, dataflow channels between

standard mezzanine boards (Processor Expansion Modules, or PEMs) and the ‘C6x

processors are supported. Application-specific interfaces, mounted to the PEM, are

available for computer telephony, digital radio as well as customer-specified interfaces.

1.2.4. Serial Ports

Two serial ports from each ‘C6x are available at each PEM site for on-board I/O

expansion. For each ‘C6x, one of the serial ports is always routed to the PEM site, the

second can be routed to either the PEM site or the VME P2 connector.

1.2.5. JTAG

The secondary VME interface allows access to the on-board JTAG Test Bus Controller

(TBC) from a host single-board computer for diagnostic purposes.

2

Part Number 500-00191

Revision 2.00

Page 15

Spectrum Signal Processing Monaco Technical Reference

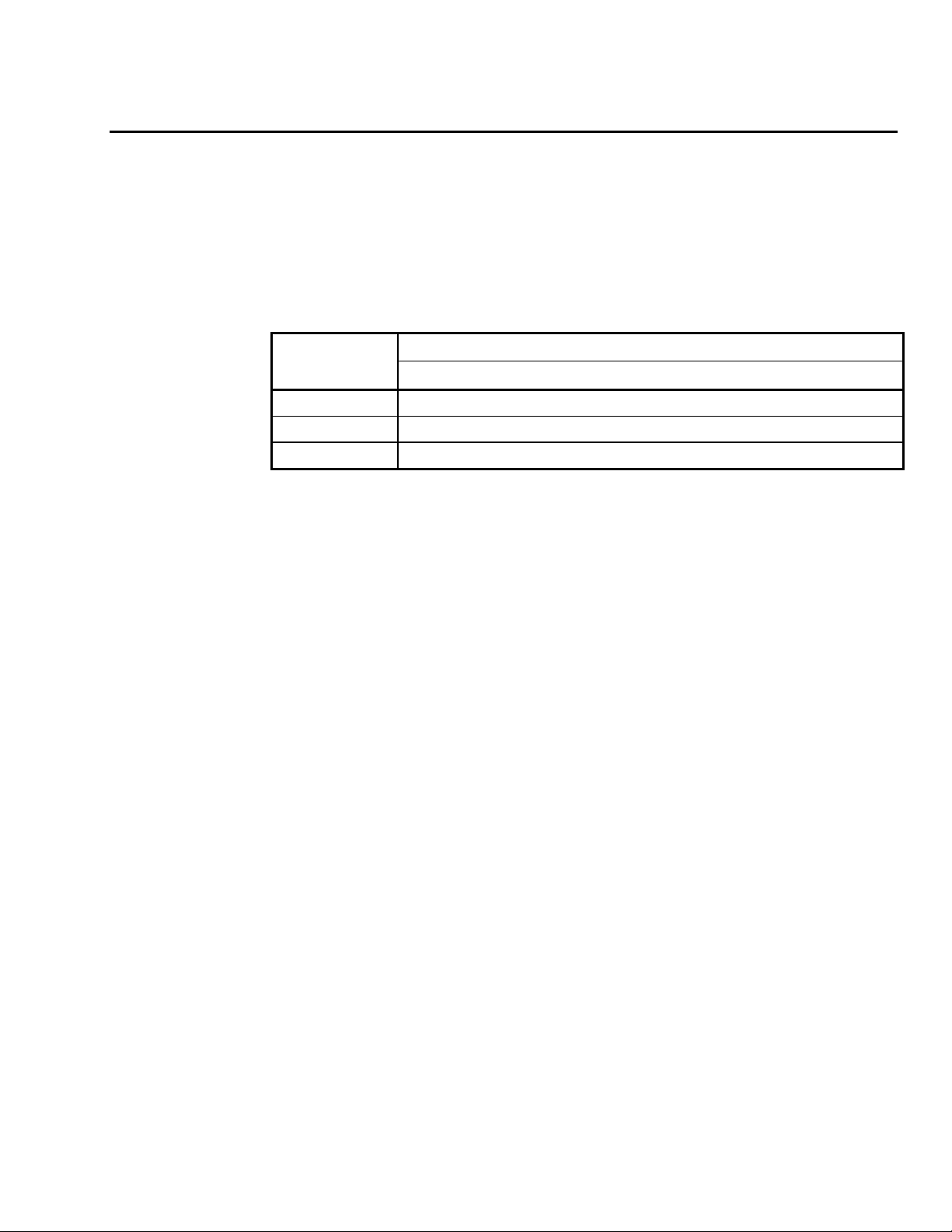

Introduction

1.3. Reference Documents

Monaco Installation Guide from Spectrum

Monaco Programming Guide from Spectrum

DSP~LINK3 Specification from Spectrum

PEM Specification from Spectrum

TMS320C6000 Peripherals Reference Guide from Texas Instruments

SCV64 User Manual from Tundra Semiconductor Corporation

Hurricane Data Sheet from Spectrum

Draft Standard Physical and Environmental Layers for PCI Mezzanine Cards: PMC

IEEE P1386.1/Draft 2.0 available from IEEE

VME64 ANSI/VITA 1-1994 available from ANSI

Part Number 500-00191

Revision 2.00

3

Page 16

Monaco Technical Reference Spectrum Signal Processing

Introduction

1.4. General Bus Architecture

The following block diagram shows the main components of the Monaco board.

'C6x Host Port Inteface (HPI)

DSP~LINK3 Interface

SBSRAM

128K x 32

PMC

Site

PCI

Bus

Hurricane

Node A

'C6x

PEM Site

Address Buffer

and

Data Latches

Global Shared

SRAM

512K x 32

VME P2 Connector

SDRAM

4M x 32

Node B

'C6x

Address Buffer

and

Data Latches

SBSRAM

128K x 32

SDRAM

4M x 32

SBSRAM

128K x 32

SDRAM

4M x 32

Global Shared Bus

Node C

'C6x

Address Buffer

and

Data Latches

Node D

PEM Site

Address Buffer

Data Latches

SCV64

VME64

Interface

VME P1 Connector

'C6x

and

JT A G

SBSRAM

128K x 32

SDRAM

4M x 32

Test Bus

Controller

A24 VME

Slave

Interface

Figure 1 Block Diagram

1.5. On-Board Power Supply

There is an on-board high-efficiency DC-DC power converter that supplies +2.5V and

+3.3V power to the board from the VME 5V supply. The circuit efficiency is

approximately 90%. The +3.3V supply is available to the PEM and PMC sites, as well as

+5V and ±12V. Up to 16.5 Watts is available from the +3.3V supply for the PEM and

PMC sites. The combined +3.3V current consumption of modules on these sites must not

exceed 5 Amps.

When adding modules to the Monaco board, ensure that the power requirements for the

modules are within the specified limits, and that the system power supply and cooling are

sufficient to meet the added requirements.

4

Part Number 500-00191

Revision 2.00

Page 17

Spectrum Signal Processing Monaco Technical Reference

Introduction

1.6. Reset Conditions

The Monaco board responds to three types of reset conditions:

• VME SYSRESET (VME bus /SYSRESET line)

• VME A24 Slave Interface Reset (VME A24 Control Register bit D0)

• JTAG reset (JTAG chain /TRST line)

The following table indicates which hardware components are reset by the specific reset

condition.

Table 1 Reset Summary

Reset Condition (Y = Component is Reset)

Hardware SYSRESET Slave Interface Reset JTAG Reset

Processor Nodes Y Y

SCV64 VME Interface chip Y

HPI registers Y Y

Global Shared Bus registers Y Y

VME A24 slave interface registers Y Y

JTAG (within DSPs) Y Y Y

PEM interface Y Y

PMC interface Y Y

DSP~LINK3 interface Y Y

Part Number 500-00191

Revision 2.00

1.6.1. VME SYSRESET

A VME SYSRESET is initiated when the /SYSRESET line on the VME bus is driven

low. All devices and registers on the Monaco board are reset to their default conditions.

1.6.2. VME A24 Slave Interface Reset

The VME A24 slave interface reset is initiated from the VME bus by setting bit D0 of

the VME A24 Control Register to “0”. All devices and registers on the Monaco board

are reset to their default conditions except for the SCV64 VME interface chip. The

VME A24 Control Register is located at VME A24 Base Address + 1004h. The base

address for the VME A24 slave interface is set by jumper block JP1.

1.6.3. JTAG Reset

The JTAG path can be reset by asserting the /TRST line of the JTAG chain by an

EMURST from the XDS or TBC. Only the JTAG path of the DSPs is reset by this

action; no other devices or registers on the board are affected.

5

Page 18

Monaco Technical Reference Spectrum Signal Processing

Introduction

1.7. Board Layout

The following diagram shows the board layout of the Monaco board.

JP10 JP8JP9 JP7

JN6

JN8 JN9

JN10 JN11

JN12

JN7

JN13

PEM Site

Nodes C and D

PEM Site

Nodes A and B

JP4 JP5

Node D

‘C6x

Node C

‘C6x

Node B

‘C6x

Node A

‘C6x

JP3

JP2

JP1

12

34

56

78

89

10 11

12 13

VME

P1

JN1 JN2

JN5

VME

P2

J1

JTAG IN

Connector

J2

JTAG OUT

Connector

PMC Site

J3

DSP~LINK3 Ribbon Cable Connector

J8

JN4

Figure 2 Board Layout

6

Part Number 500-00191

Revision 2.00

Page 19

Spectrum Signal Processing Monaco Technical Reference

Introduction

1.8. Jumper settings

Table 2 Jumper Settings

Jumper Description IN OUT

JP1 Pins 1-2 VME A24 slave interface base address bit A23 0 1*

JP1 Pins 3-4 VME A24 slave interface base address bit A22 0* 1

JP1 Pins 5-6 VME A24 slave interface base address bit A21 0* 1

JP1 Pins 7-8 VME A24 slave interface base address bit A20 0* 1

JP1 Pins 9-10 VME A24 slave interface base address bit A19 0* 1

JP1 Pins 11-12 VME A24 slave interface base address bit A18 0* 1

JP1 Pins 13-14 VME A24 slave interface base address bit A17 0* 1

JP2 Node A boot mode PEM HPI*

JP3 Node B boot mode PEM HPI*

JP4 Node C boot mode PEM HPI*

JP5 Node D boot mode PEM HPI*

JP7 Node A Serial Port 1 Routing VME P2 PEM*

JP8 Node B Serial Port 1 Routing VME P2 PEM*

JP9 Node C Serial Port 1 Routing VME P2 PEM*

JP10 Node D Serial Port 1 Routing VME P2 PEM*

* Default position

Note:

The default VME A24 slave interface base address is set to 80 0000h.

Part Number 500-00191

Revision 2.00

7

Page 20

Monaco Technical Reference Spectrum Signal Processing

Introduction

8

Part Number 500-00191

Revision 2.00

Page 21

Spectrum Signal Processing Monaco Technical Reference

Processor Nodes

2 Processor Nodes

The Monaco board supports one, two or four embedded ‘C6X processor nodes shared

across the Global Shared Bus. The three possible processor configurations are described

in the following figure.

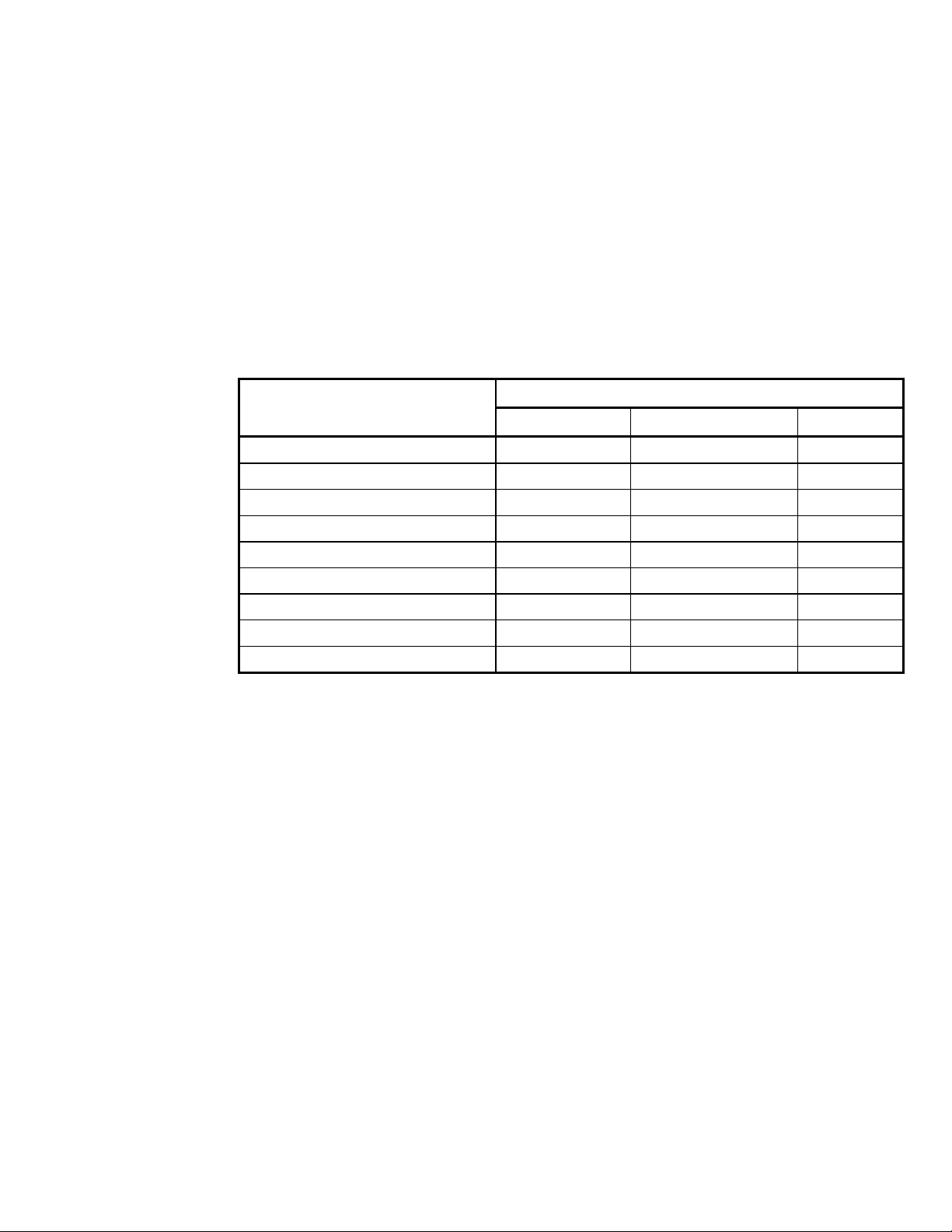

Table 3 Processor Configurations

Populated

Configuration Node A Node B Node C Node D

One Node Y

Two Nodes Y Y

Four Nodes YYYY

Each DSP node consists of:

• One TMS320C6201 DSP operating at 200 MHz for Monaco, or one TMS320C6701

DSP operating at 167 MHz for Monaco67

• 128K of 32-bit Synchronous burst SRAM (SBSRAM)

• 4M of 32-bit Synchronous DRAM (SDRAM)

• Processor Expansion Module (PEM) interface

• A slave Host Port Interface to VME A24 bus

• Two serial ports

• A DSP~LINK3 interface (DSP node A only)

Part Number 500-00191

Revision 2.00

9

Page 22

Monaco Technical Reference Spectrum Signal Processing

Processor Nodes

JT A G Test Bus

‘C6x Host Port

Interface (HPI) Bus

Node Local

Resources

Serial

Port 0

Serial

Port 1

DSP-LINK3

Interface

Node A

Only

PEM Site

Shared with

Node Pair

DSP

DSP

Local

Bus

‘C6x

128K x 32

SBSRAM

4M x 32

SDRAM

Address Buffer

and

Data Latches

Global Shared Bus

Figure 3 Processor Node Block Diagram

10

Part Number 500-00191

Revision 2.00

Page 23

Spectrum Signal Processing Monaco Technical Reference

Processor Nodes

2.1. Processor Memory Configurati on

Each ‘C6X DSP processor implements a 4 Gigabyte (full 32-bit) address space. This

address space is partitioned into internal memory space and external memory space.

External memory space is accessed through four memory select lines (CE0, CE1, CE2

and CE3).

2.1.1. Internal Memory

Internal memory space is further separated into three distinct regions:

• internal program RAM (64Kbytes)

• internal peripheral registers (2 Mbytes)

• internal data RAM (64 Kbytes)

These three regions define memory space which is implemented in the DSP processor.

2.1.2. External Memory

External memory is segmented into 4 regions:

• external memory interface CE0 (16 Mbytes)

• external memory interface CE1 (4 Mbytes)

• external memory interface CE2 (16 Mbytes)

• external memory interface CE3 (16 Mbytes)

External memory (CE0, CE1, CE2 and CE3) consists of node local memory resources

which are accessed on the DSP Local Bus, but are external to the DSP processor. The

type of memory in each of the four CE regions is determined by settings in the internal

peripheral registers. All remaining memory in the 4 GB address space is reserved.

The internal peripheral registers for Monaco must be initialized to the values in the

following table upon reset for the board to operate.

Part Number 500-00191

Revision 2.00

11

Page 24

Monaco Technical Reference Spectrum Signal Processing

Processor Nodes

Table 4 'C6x Internal Peripheral Register Values

Register

Global Control Register

Address

0x0180 0000

EMIF CE0 Control Register

0x0180 0008

EMIF CE1 Control Register

0x0180 0004

EMIF CE2 Control Register

0x0180 0010

EMIF CE3 Control Register

(Used for PEM. Must be

reconfigured for individual

PEM)

0x0180 0014

EMIF SDRAM Control

0x0180 0018

EMIF SDRAM Timing

0x0180 001C

Value Comments

0x0000 3078 NOHOLD (External HOLD disable) off

SDCEN (SDRAM clock enable) on

SSCEN (SBSRAM clock enable) on

CLK1EN (CLKOUT1 enable) on

CLK2EN (CLKOUT2 enable) on

SSCRT (SBSRAM clock rate select) 1/2x CPU clock

RBTR8 off (requester controls EMIF until a high priority request

occurs..

0xFFFF 3F43 MTYPE = 32 bit wide SBSRAM

No other bits are used.

0x30E4 0421 MTYPE = 32 bit wide asynchronous interface

write setup = 3 cycles

write strobe = 3 cycles

write hold = 2 cycles

read setup = 4 cycles

read strobe = 4 cycles

read hold = 1 cycle

all cycles are clockout1 cycles

0xFFFF 3F33 MTYPE = 32 bit wide SDRAM

No other bits are used.

0x72B7 0A23 MTYPE = 32 bit wide asynchronous interface

address = 0x01800004

value = 0x30E40421

MTYPE = 32 bit wide asynchronous interface

write setup = 7 cycles

write strobe = 10 cycles

write hold = 3 cycles

read setup = 7 cycles

read strobe = 10 cycles

read hold = 3 cycle

all cycles are clockout1 cycles

0x0544 A000 RFEN = 0 internal refresh enable OFF. Only external SDRAM

refresh can be used.

SDWID = 1 (SDRAM width select) two 16 bit SDRAMs

Other timing parameters are SDRAM specific and should not be

modified by the user.

0x0000 061A Refresh timer implemented in external hardware. This register is

not used.

12

Part Number 500-00191

Revision 2.00

Page 25

Spectrum Signal Processing Monaco Technical Reference

Processor Nodes

‘C6x Addr Memory Contents Memory Size

0000 0000 Internal-Program RAM 64 KB

0000 1000

Reserved 4 MB - 64KB

0040 0000 Local SBSRAM 512 KB

0048 0000

0140 0000

0180 0000

01A0 0000

0200 0000

0300 0000

External-Memory Space

Upon Reset

PEM EEPROM

Boot Mode

Internal-Peripheral Space 2 MB

Local SDRAM

Processor Expansion Module (PEM)

Reserved

CE1

CE0

External-Memory Space

After TOUT0 is toggled

DSP~LINK3

Shared SRAM

SCV64 Registers

(see the following CE1

memory map)

Reserved 6 MB

CE2

CE3

CE1

16 M - 512 KB

4 MB

16 MB

16 MB

Part Number 500-00191

Revision 2.00

0400 0000

Reserved 2 GB - 64 MB

8000 0000 Internal-Data RAM 64 KB

8001 0000

Reserved 2GB -

(2GB - 64 KB)

FFFF FFFF

Figure 4 DSP Memory Map

13

Page 26

Monaco Technical Reference Spectrum Signal Processing

Processor Nodes

External Memory Space CE1 is dedicated to accessing registers, global shared RAM and

DSP~LINK3 (Node A only). Node A differs from nodes B, C and D since it is the only

node with access to the DSP~LINK3. The following figure shows the memory map for

this region.

Address Node A Nodes B, C, and D

0140 0000

Global Shared SRAM

512K x 32

015F FFFC

0160 0000

DSP~LINK3 Standard Access

0163 FFFC

0164 0000

DSP~LINK3 Standard Fast Access Reserved

0167 FFFC

0168 0000

DSP~LINK3 RDY Controlled Access

016B FFFC

016C 0000

Hurricane Registers Hurricane Registers

016C 1FFC

016D 0000

Global Shared SRAM

512K x 32

016D 7FFC

016D 8000

016D FFFC

016E 0000

016E 7FFC

016E 8000

016E FFFC

016F 0000

016F FFFC

0170 0000

017F FFFC

Node A VPAGE Register Node B, C, or D VPAGE Register

Shared Bus Registers Shared Bus Registers

SCV64 Register Set (R/W) SCV64 Register Set (R/W)

Reserved Reserved

IACK Cycle Space (Read Only) IACK Cycle Space (Read Only)

One Mbyte window to the

VME Address Space

VME base address set by VPAGE register

DSP as VME Master (R/W)

VME base address set by VPAGE register

One Mbyte window to the

VME Address Space

DSP as VME Master (R/W)

14

Figure 5 DSP Memory Map for External-Memory Space CE1

Part Number 500-00191

Revision 2.00

Page 27

Spectrum Signal Processing Monaco Technical Reference

Processor Nodes

2.2. Synchronous Burst SRAM

The board provides 128K of 32-bit synchronous burst SRAM (SBSRAM) on each ‘C6x

local bus. The Monaco board supports 1 wait state operation.

2.3. Synchronous DRAM

The board provides 4M of 32-bit synchronous DRAM on each ‘C6x bus. The Monaco

board supports 1 wait state operation. An additional 4M of 32-bit synchronous DRAM

per DSP can also be supported on a PEM module.

Burst data transfer rates from CPU to SDRAM are 400 Mbytes/s on a Monaco with

200 MHz TMS320C6201 chips.

2.4. Processor Expansion Module

The Processor Expansion Module (PEM) provides a simple and flexible interface from

the DSP to I/O. It is similar to a PMC module, although physically narrower.

The Monaco board is designed to support two DSPs per PEM site, with a pair of

connectors for each DSP. While both DSP devices share the same PEM, the two DSP

buses are kept separate to allow very fast PEM data transfer rates.

The PEM is capable of booting the DSPs from local ROM, with up to 4 MBytes of

addressable boot space available to each DSP.

Refer to the PEM Specification for mechanical and functional details of the PEM

interface.

2.5. Host Port

A separate A24 VMEbus Slave interface is used for direct access to the DSP’s Host Port

Interface. This interface can be used for downloading code and as a control path from the

host to the DSP. Data transfer rates depend upon both the code executing in the DSP and

the VMEbus Master performing the transfers, but can be as high as 30 Mbytes/second.

Jumper block JP1 selects the VME A24 base address for this slave interface.

2.6. Interrupt Lines

There are four external interrupt inputs on each ‘C6x. They are INT4, INT5, INT6, and

INT7. All four must be configured as rising-edge triggered interrupts upon initialization.

See the Interrupt Handling chapter for further information.

Part Number 500-00191

Revision 2.00

15

Page 28

Monaco Technical Reference Spectrum Signal Processing

Processor Nodes

2.7. Processor Booting

The ‘C6x can boot from either the VME bus (via its Host Port Interface (HPI) port) or

from an 8-bit EEPROM on an installed PEM module. The jumpers listed in the following

table select the booting method for each node.

Table 5 Processor Boot Source Jumpers

Jumper Node PEM Boot HPI Boot

JP2 Node A IN OUT

JP3 Node B IN OUT

JP4 Node C IN OUT

JP5 Node D IN OUT

The Monaco board uses the CE1 memory space of the ‘C6x memory map 1 for the boot

space upon power up or reset. Immediately after booting, the ‘C6x cannot access the

resources in its CE1 space such as the Hurricane registers, Global Shared SRAM, and

SCV64 Registers. In order to access these CE1 resources, the ‘C6x must toggle the state

of its Timer 0 pin (TOUT0). The state of this pin is controlled by the DataOut bit of the

‘C6x Timer 0 Control Register. Once TOUT has been toggled, the CE1 resources are

available to the ‘C6x until the ‘C6x is reset.

16

Part Number 500-00191

Revision 2.00

Page 29

Spectrum Signal Processing Monaco Technical Reference

Processor Nodes

2.8. Serial Port Routing

Each ‘C6x has two serial ports. Serial Port 0 of each DSP is routed to the PEM connector

associated with the DSP node.

Routing for Serial Port 1 on nodes A, B, C and D is determined by jumpers J7 to J10 as

shown in the figure and following tables. The jumper setting selects routing either to the

PMC JN5 and VME P2 connectors, or to the PEM connector associated with the DSP

node.

Serial Port routing for the Monaco board is shown the figure. Complete pinouts for the

connectors are given in the Connector Pinouts chapter.

Serial

Port 0

Serial

Port 1

Serial

Port 0

Serial

Port 1

Serial

Port 0

Serial

Port 1

Serial

Port 0

Serial

Port 1

Node D

C6x

Node C

C6x

Node B

C6x

Node A

C6x

VME

P1

Node

D

PEM

1

Node

C

PEM

1

Node

B

PEM

1

Node

A

PEM

1

Node

D

PEM

2

Node

C

PEM

2

Node

B

PEM

2

Node

A

PEM

2

OUT

OUT

JP7

IN

OUT

JP8

IN

OUT

JP9

IN

JP10

IN

Part Number 500-00191

Revision 2.00

Figure 6 Serial Port Routing

Node D Serial Port 0

Node C Serial Port 0

Node B Serial Port 0

Node A Serial Port 0

PMC

Connector

JN5

Node D

Node C

Node B

Node A

VME

P2

17

Page 30

Monaco Technical Reference Spectrum Signal Processing

Processor Nodes

Pin assignments for the serial ports are given in the following tables.

Table 6 PEM Connections for Serial Port 0 and 1

Signal PEM 1 Port 0 PEM 2 Port 1*

CLKS External clock 56 17

CLKR Receive clock 52 13

CLKX Transmit clock 42 3

DR Received serial data 48 9

DX Transmitted serial data 46 7

FSR Receive frame synchronization 50 11

FSX Transmit frame synchronization 44 5

*The serial port routing jumper corresponding to the node (J7, J8, J9, or J10) must be

OUT for port 1 to be routed to the node’s PEM 2 connector.

Table 7 VME and PMC Connections for Serial Port 1

Node A (J7 IN) Node B (J8 IN) Node C (J9 IN) Node D (J10 IN)

Signal PMC JN5 VME-P2 PMC JN5 VME-P2 PMC JN5 VME-P2 PMC JN5 VME-P2

CLKS External clock 1 D-4 21 D-18 2 Z-3 22 Z-17

CLKR Receive clock 5 D-6 25 D-20 6 Z-5 26 Z-19

CLKX Transmit clock 9 D-8 29 D-22 10 Z-7 30 Z-21

DR Received serial data 11 D-10 31 D-24 12 Z-9 32 Z-23

DX Transmitted serial data 13 D-12 33 D-26 14 Z-11 34 Z-25

FSR Receive frame synchronization 15 D-14 35 D-28 16 Z-13 36 Z-27

FSX Transmit frame synchronization 17 D-16 37 D-30 18 Z-15 38 Z-29

18

Part Number 500-00191

Revision 2.00

Page 31

Spectrum Signal Processing Monaco Technical Reference

Global Shared Bus

3 Global Shared Bus

The Global Shared Bus provides access between devices on the Monaco board as shown

in the following table.

Table 8 Global Shared Bus Access

Source

3.1. Memory

Target ‘C6x

Nodes

Internal program & data RAM R/W own node No Access No Access

Local SDRAM R/W own node No Access No Access

Local SBSRAM R/W own node No Access No Access

Global Shared RAM R/W (32-bit only) R/W R/W

Hurricane Registers R/W R/W R/W

PMC Site Hurricane DMA

access only

SCV64 Registers R/W No Access No Access

Global Shared Bus Registers R/W No Access No Access

VMEbus as master R/W No Access -

PMC

Site

- No Access

VME Bus

via SCV64

512K of 32-bit Asynchronous RAM, implemented in four 512K x 8-bit Asynchronous

RAM devices, is provided on the Global Shared Bus. The ‘C6x DSPs can only perform

32-bit accesses to the Global Shared RAM. Byte accesses are not supported.

3.2. Arbitration

Part Number 500-00191

Revision 2.00

Arbitration of the Global Shared Bus is implemented using a next bus owner token that is

passed serially from one device to the next. Token passing follows a strict hierarchical

sequence, ordered by bus servicing priority. There are six devices participating in the

process. These are, in decreasing priority:

• SCV64

• Hurricane

• DSP Node A

• DSP Node B

• DSP Node C

• DSP Node D

19

Page 32

Monaco Technical Reference Spectrum Signal Processing

Global Shared Bus

Bus ownership is cycled between the two highest priority devices (SCV64 and

Hurricane) until neither device requires the bus. Then the DSP Nodes are processed

round robin. After one pass through the DSP chain, the cycle loops back to include the

SCV64 and Hurricane. This eliminates any arbitration latency as bus ownership is

transferred between devices, and grants the highest priority to those devices interfacing

to external buses (VME and PCI), which require the fastest response. The arbitration

cycle is shown in the following figure.

Note:

Because there is no ownership timer for either Hurricane or SCV64 chip

the system designer must ensure that processors are not held off from the shared

resources for unreasonable lengths of time.

Highest Priority Lowest priority

Node AHurricaneSCV64 Node DNode CNode B

Round Robin

DSPVME & PCI Bus

Round Robin

Figure 7 Global Bus Arbitration

Access to the Global Shared Bus can use single, burst, or locked cycles.

20

3.2.1. Single Cycle Bus Access

For single cycle accesses a device requests the global shared bus by simply initiating a

read or write access to the bus. When the bus is free, the device acquires it and performs

the single cycle access. The bus is then released.

3.2.2. Burst Cycle Bus Access

Burst cycles are used during DMA transfers from a ‘C6x processor to the Global Shared

Bus. A 6-bit bus ownership timer on each node prevents a ‘C6x from owning the bus for

more than 640 ns when another device is requesting the bus. When the burst cycles are

begun, the timer is started. If another device requests the bus when the timer expires, the

bus is released; otherwise ownership is maintained and the timer is reset and started

again.

If multiple DSPs request the bus, this scheme allocates time to them fairly so that none

are locked out.

Part Number 500-00191

Revision 2.00

Page 33

Spectrum Signal Processing Monaco Technical Reference

Global Shared Bus

Although this is a non-prioritized scheme, the back-off function of the SCV64 interface

resolves collisions between a bus master and the VMEbus if there is contention for the

VMEbus.

Note:

There are no ownership timers for the Hurricane or SCV64. If the

Hurricane holds the bus too long the VME bus could timeout.

3.2.3. Locked Cycles

A ‘C6x can lock the Global Shared Bus in order to perform Read-Modify-Write (RMW)

or other atomic accesses to it, by driving its Timer 0 (TOUT0) low. After the TOUT0 is

driven low, the next access to the Global Shared Bus acquires the bus. The bus is not

released until the ‘C6x drives the Timer 0 (TOUT0) pin high.

Caution:

be used carefully because other devices will not acquire the bus once it is locked.

This capability is intended for read-modify-write accesses to the Global Shared

RAM and registers. It is highly recommended that Bus locking not be used. It

can lead to a deadlock condition, and in particular, result in debugger timeouts.

The following precautions should be observed when locking the Global Shared Bus:

1. VME bus timeouts can occur because the SCV64 cannot access the board while a

‘C6x has locked the bus.

The capability of locking the Global Shared Bus from a ‘C6x should

2. If node A accesses the DSP~LINK3 interface while it has locked the Global Shared

Bus by asserting TOUT0, the bus will be released. Node A’s next access to the bus

will re-lock it to node A, providing that TOUT0 is still asserted.

3. Some SCV64 inbound cycles can occur while the bus is locked. If a ‘C6x has locked

the bus and is performing a VME outbound cycle while a VME inbound cycle is in

progress, the ‘C6x will be temporarily backed off and the SCV64 cycle will proceed.

The Global Shared Bus will be returned to that ‘C6x node after the SCV64 cycle

finishes. No other ‘C6x will get ownership of the bus.

4. If a debugger is being used when one processor has the bus locked for an extended

time while another processor is trying to get the bus, the debugger may timeout.

Part Number 500-00191

Revision 2.00

21

Page 34

Monaco Technical Reference Spectrum Signal Processing

Global Shared Bus

22

Part Number 500-00191

Revision 2.00

Page 35

Spectrum Signal Processing Monaco Technical Reference

VME64 Bus Interface

4 VME64 Bus Interface

There are two separate VMEbus slave interfaces on the Monaco board. One is

implemented by the SCV64 and provides A32 and A24 VMEbus masters access to the

global shared bus. The second slave interface provides direct access to the Test Bus

Controller for debugging, and to the Host Port Interfaces (HPIs) of each ‘C6x. The HPI

provides support for code download, control, and data transfers from the VME64 bus.

4.1. VME Operation

The Monaco board requires a VME chassis (6U) with power supply. The board

automatically becomes VMEbus system controller (Syscon) if it resides at the top of the

VMEbus grant daisy chain. This capability is provided by the Tundra SCV64 interface

chip. Refer to the SCV64 User Manual for details.

The Monaco board has two VME backplane connectors: a 3 row P1 connector and a 5

row P2 connector.

The board may be installed in either a 5 row VME backplane or a 3 row backplane. The

two additional rows on the VME P2 connector (Z and D) only serve to route serial port

signals from DSP processor nodes A, B, C and D to the VME backplane, if the board is

configured for that option.

Note:

routing will be restricted to the PEM and PMC sites only.

If the Monaco board is installed in a 3 row VME chassis, serial port

4.2. SCV64 Primary Slave A32/A24 Interface

The primary interface to the VME64 bus is based on Tundra Semiconductor

Corporation’s SCV64 VME64 Interface chip. This chip enables the Monaco board to act

as a master or a slave on the VME64 bus, and also provides VME interrupt capabilities.

Transfer rates of 40 MBytes/sec are supported between the SCV64 and the Global

Shared Bus SRAM once the bus has been acquired. The SCV64 cannot be pre-empted

from the Global Shared Bus and it does not have a bus ownership timer.

A host on the VME64 bus can access both the lower half (1 Mbyte) of Global SRAM

and the Hurricane control registers on a Monaco board in either A24 or A32 addressing

modes as shown in the following memory map.

Part Number 500-00191

Revision 2.00

23

Page 36

Monaco Technical Reference Spectrum Signal Processing

VME64 Bus Interface

VME Offset Address Access

0000 0000h

Global Shared SRAM

(lower 1Mbyte)

000F FFFFh

0010 0000h

Global Shared SRAM

(Upper 1 Mbyte)

001F FFFFh

0020 0000h

Hurricane Control Registers

002F FFFFh

0030 0000h

Reserved

003F FFFFh

Host

VME DSP

accessible and

Figure 8 Primary VME A24/A32 Memory Map

Note:

The full A24 memory map occupies one-quarter of the available A24

space. This can be reduced to the standard 512K (16M ÷ 32) of the available

A24 space by mapping only the lower 512 Kbytes (128k x 32) of the global

shared SRAM. This is entirely programmable in the SCV64 base address

registers. Only SCV64 A21 and A20 are used for decode on SCV64 VME slave

accesses to the board. D16 and D08E0 writes are not supported on the primary

A32/A24 interface.

Hurricane

accessible

4.3. A24 Secondary Slave Interface

Jumper block JP1 sets address bits A23..A17 of the VME A24 slave interface. This base

address defines a 128K byte addressed memory space accessed by the VME bus. Access

to this space from the VME bus bypasses the SCV64 VME bus interface chip.

All A24 VME transfer types are accepted except for LOCK, and MBLT types.

As shown in the following memory map, the A24 slave interface provides the VME bus

direct access to:

• The Host Port Interface (HPI) registers of each ‘C6x processor

• The Test Bus Controller (TBC) for JTAG debugging operation

• Control and Status registers of the Monaco board

D16 and D08E0 accesses are not supported on the slave A24 secondary interface.

24

Part Number 500-00191

Revision 2.00

Page 37

Spectrum Signal Processing Monaco Technical Reference

VME64 Bus Interface

VME Offset Address

00 0000h

Test Bus Controller Registers (JTAG)

00 0FFFh

00 1000h

FPGA

‘C6x

‘C6x

00 1003h

00 1004h

00 1007h

00 1008h

00 1FFFh

00 2000h

00 2FFFh

00 3000h

00 3FFFh

00 4000h

00 4FFFh

00 5000h

00 5FFFh

00 6000h

00 FFFFh

01 0000h

01 3FFCh

01 4000h

01 3FFCh

01 B000h

01 3FFCh

01 C000h

01 FFFCh

VME A24 Status Register (Read Only)

VME A24 Control Register (Read/Write)

Reserved

Node A HPI Registers

Node B HPI Registers

Node C HPI Registers

Node D HPI Registers

Reserved

Node A HPID DMA Space (HPIA incremented)

all addresses mapped to 00 2008h

Node B HPID DMA Space (HPIA incremented)

all addresses mapped to 00 3008h

Node C HPID DMA Space (HPIA incremented)

all addresses mapped to 00 4008h

Node D HPID DMA Space (HPIA incremented)

all addresses mapped to 00 5008h

16 KB

16 KB

16 KB

16 KB

Part Number 500-00191

Revision 2.00

Figure 9 A24 Secondary Interface Memory Map

Refer to the JTAG Debugging chapter for information on using the Test Bus Controller

for JTAG operation. The VME A24 Status Register and the

VME A24 Control Register are described in the Registers chapter.

25

Page 38

Monaco Technical Reference Spectrum Signal Processing

VME64 Bus Interface

The Host Port Interface (HPI) allows a VME host to access the memory map of any

‘C6X. The board transfers 32-bit VME accesses automatically through the 16-bit Host

Port Interface as two 16-bit words. The interface consists of three read/write, 32-bit

registers that are accessed through the VME A24 slave interface:

• HPI Address register (HPIA)

• HPI Control register (HPIC). A ‘C6x can also read and write to its HPI Control

register (HPIC) at address 0188 0000h.

• HPI Data register (HPID)

VME address bits A[3:2] select which register is being accessed in each node’s HPI

register address space. These bits are mapped to the HCNTRL[1:0] control pins of the

‘C6x. The following table shows how the HPI interface is addressed.

Table 9 HPI Register Addresses

VME address

‘C6x

Register

HPIC 00 2000h 00 3000h 00 4000h 00 5000h State for reading/setting the Control Register value.

HPIA 00 2004h 00 3004h 00 4004h 00 5004h Used to read/set the HPI address pointer. The HPIA

HPID 00 2008h 00 3008h 00 4008h 00 5008h A VME host reads and writes data to this address for

HPID 00 200Ch 00 300Ch 00 400Ch 00 500Ch A VME host reads and writes data to this address for

HPID

DMA

Space

Node

A

01 0000h 01 4000h 01 8000h 01 C0000h VME hosts which increment their target address can use

Node

B

Node

C

Node

D Description

points into the C6x memory space.

DMA transfers to the HPID register. The HPIA register

automatically increments by 4 bytes as each word is

transferred through the HPID register.

single cycle transfers to the HPID register. The HPIA is

not incremented for this HPI access mode.

this address space for DMA transfers to the HPID

register. Up to 4K of 32-bit data can be transferred in this

space. Data written to this space is automatically

transferred to the HPID register, and the HPIA register

automatically increments by 4 bytes as each word is

transferred.

26

Part Number 500-00191

Revision 2.00

Page 39

Spectrum Signal Processing Monaco Technical Reference

VME64 Bus Interface

Before a host can transfer data through a node’s HPI, the VME host must set the HWOB

bit of the node’s HPIC register to “1”. This only has to be done once after the Monaco

board is reset. To access an address within a ‘C6x’s memory space, the VME host loads

the address into the HPIA register. Data is then transferred through the HPID register.

• The HPID at offset “8h” auto-increments four bytes after every cycle, allowing it to

be used for burst DMA data transfers.

• The HPID at offset “Ch” does not auto-increment, and is therefore intended for

single cycle accesses only.

• The HPID DMA Space offers a 16K address space to VME hosts which increment

their target address during DMA transfers. This allows them to transfer data in

blocks of 16K 32-bit words to the HPID register used for DMA transfers.

4.4. Master A32/A24/A16 SCV64 Interface

As a VME master, the Monaco board supports A16, A24, or A32 transactions from any

node to the VME64 bus through the SCV64 chip. Any node can program the SCV64’s

DMA Controller for VME Master Accesses, and can directly master the VMEbus. Each

node has its own VPAGE Register to support the KFC, KSIZE, and upper 12 and

lower 2 address bits to the SCV64. The upper 11 bits extend the 20-bit address space of

the ‘C6x to the full 32-bit address space of the VME bus. Any node can monitor the

status of the /KIPL interrupt lines, BUSERRORs for each node, and KAVEC line by

reading the VSTATUS Register.

The Monaco board supports Auto-Syscon capabilities allowing it to become the System

Controller board when placed in the leftmost slot of the VME backplane. If it is to be the

System Controller it should typically be booted from a PEM module equipped with a

boot PROM.

Upon reset, the SCV64 is in Bus-Isolation Mode (BI-Mode) which isolates the SCV64

from the VME64 bus. The SCV64 is released from BI-Mode by a write to the SCV64

Location Monitor from any node of the Monaco board.

Part Number 500-00191

Revision 2.00

27

Page 40

Monaco Technical Reference Spectrum Signal Processing

VME64 Bus Interface

28

Part Number 500-00191

Revision 2.00

Page 41

Spectrum Signal Processing Monaco Technical Reference

DSP~LINK3 Interface

5 DSP~LINK3 Interface

The Monaco board provides a DSP~LINK3 interface through a ribbon cable connector.

The interface supports up to 4 slave DSP~LINK3 devices. The ribbon cable can be up to

12 inches (30 cm) long.

The DSP~LINK3 interface is accessed from node A’s local bus only; it is not accessible

from any other node nor from the VME bus. Accesses to the DSP~LINK3 interface do

not require the Global Shared Bus. As a result, DSP~LINK3 accesses can happen

concurrently with Global Shared Bus access by other devices (such as the other

processors or the SCV64 chip).

If a DSP~LINK3 access is interleaved within global shared SRAM accesses, node A

acquires the Global Shared Bus, performs the SRAM access, releases the Global Shared

Bus, performs the DSP~LINK3 access, acquires the Global Shared Bus, and then

performs the next Global Shared Bus SRAM access using a control register.

5.1. DSP~LINK3 Data Transfer Operating Modes

The Monaco board supports four data transfer operating modes.

• Standard Access

• Standard Fast Access

• Address Strobe Control

• Ready Control Access

The three “access” data transfer operating modes (Standard, Standard Fast and Ready

Control) of the DSP~LINK3 interface use three 64K address spaces accessed from node

A. Each of the three “access” modes is assigned its own 64K memory space. Address

Strobe Control cycles are multiplexed with the Standard Fast Access mode space.

The following table shows how the DSP~LINK3 data transfer operating modes are

supported.

Part Number 500-00191

Revision 2.00

29

Page 42

Monaco Technical Reference Spectrum Signal Processing

DSP~LINK3 Interface

Table 10 DSP~LINK3 Data Transfer Operating Modes

Mode

Standard

Access

Standard

Fast

Access

Address

Strobe

Control

Ready

Control

Access

Base

Address

0160 0000h

0164 0000h 0 For DSP~LINK3 slave boards that have fast,

0164 0000h 1 For slave boards that require more than the

0168 0000h

ASTRB_EN

Bit Description

x

x

For slave boards that are similar to DSP~LINK1

slave boards and operate with a fixed access

time.

fixed access time. This memory space is

shared with the Address Strobe Control

operating mode.

16 KWords of addressing provided by the

standard DSP~LINK3 address lines. The bus

master uses the /ASTRB cycle to place the

page address onto the DSP~LINK3 data lines.

It determines which address page is accessed

on the slave board. This allows access to up to

14

address pages with each address page

2

having an address depth of 2

Cycle has the same timing as the Standard

Fast transfer cycle.

For DSP~LINK3 slave boards that require

variable length access times. /DSTRB is active

until the slave asserts the DSP~LINK3 ready

signal (/RDY) to end the cycle.

14

. The /ASTRB

5.2. Address Strobe Control Mode

The Address Strobe Control mode uses the same node A 64K address space as the

Standard Fast Access mode. The Address Strobe Control mode is enabled for this space

by setting bit D1, the ASTRB_EN bit, of the DSP~LINK3 register to “1”. This register is

located at address 016D 8018h of node A. Standard Fast Access mode writes will now

generate /ASTRB cycles. The DSP~LINK3 slave attached to the Monaco board should

then latch the lower addresses.

30

Part Number 500-00191

Revision 2.00

Page 43

Spectrum Signal Processing Monaco Technical Reference

DSP~LINK3 Interface

5.3. Interface Signals

The DSP~LINK3 interface consists of two 16-bit bi-directional buffers for data, a 16-bit

address latch, and a control signal buffer. The control signals are terminated via a SCSI

terminator. The DSP~LINK3 interface signals are:

• 32 data I/O lines: D[31..0]

• 16 address outputs: A[15..0] A15 and A14 are used for slave device (board)

selection.

• /DSTRB, /ASTRB, R/W and /RST outputs

• Tri-state ready (/RDY) input

• 4 open-collector interrupt inputs (IRQ0 to IRQ3). These interrupt are logically

OR’ed and routed to the INT7 line of node A’s ‘C6x.

Refer to DSP~LINK3 specification for details (available from Spectrum’s internet web

site at http://www.spectrumsignal.com)

5.4. DSP~LINK3 Reset

Bit D0 of the DSP~LINK3 register controls the DSP~LINK3 reset line. This register is

located at address 016D 8018h of node A. Setting bit D0 to “1” asserts the DSP~LINK3

reset line; setting it to “0” releases the reset. DSP~LINK3 resets must be at least 1 µs

long. This reset is entirely under software control.

The DSP~LINK3 reset line will also be asserted during /SYSRESET or secondary

control register board reset conditions.

Part Number 500-00191

Revision 2.00

31

Page 44

Monaco Technical Reference Spectrum Signal Processing

DSP~LINK3 Interface

32

Part Number 500-00191

Revision 2.00

Page 45

Spectrum Signal Processing Monaco Technical Reference

PCI Interface

6 PCI Interface

The Hurricane chip provides the interface between the Global Shared SRAM on the

Global Shared Bus and the PMC site which supports a 32 bit, 33 MHz PCI bus. Although

the DSPs cannot directly master the PCI bus, the Hurricane’s DMA controller provides

flexible data transfer between the Global Shared Bus SRAM and the PMC.

Embedded PCI buses require Hurricane PCI configuration cycle generation.

Pre-emptive arbitration is not used. If a node requests the Global Shared bus when the

bus is not currently in use, then it will be granted the bus. It is up to the bus ownership

timers of the Hurricane and PMC devices to prevent bus hogging.

PMC modules can directly master the Global Shared SRAM.

The memory map of the Monaco seen by a PMC module is shown in the following

figure.

PCI Offset Address Access

0000 0000h

001F FFFFh

0020 0000h

002F FFFFh

0030 0000h

003F FFFFh

Figure 10 PCI Memory Map

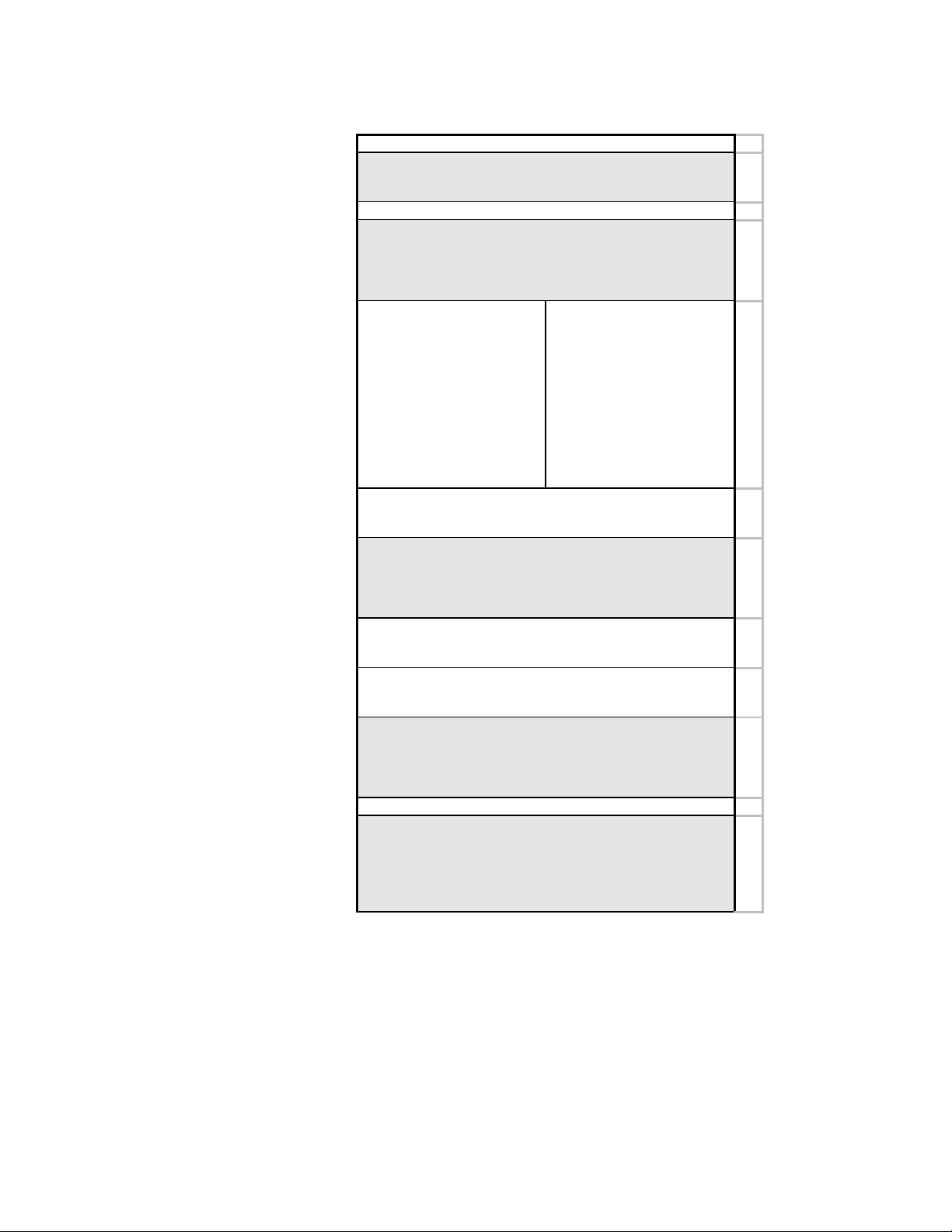

6.1. Hurricane Configuration

Before the PMC site can be accessed, the Monaco initialization software must configure

the Hurricane registers with the values shown in the following table. Only the indicated

values should be initialized, all other values should be left alone. As can be seen, these

registers can be accessed from a ‘C6x, the PMC’s PCI bus, and a host on the VME bus.

Global Shared SRAM

Hurricane Control Registers

Reserved

Part Number 500-00191

Revision 2.00

33

Page 46

Monaco Technical Reference Spectrum Signal Processing

PCI Interface

Table 11 Hurricane Register Set

Hurricane

DSP Offset

0x00 0x016C 0000 0x0020 0000 0x0020 0000 DCSR DMA Control / Status Register 0x0000 0000

0x01 0x016C 0004 0x0020 0004 0x0020 0004 IFSC Interrupt Flag, Set, Clr 0x0000 0000 Y

0x02 0x016C 0008 0x0020 0008 0x0020 0008 IED Interrupt Enable to DSP 0x0000 0000 Y

0x03 0x016C 000C 0x0020 000C 0x0020 000C IEP Interrupt Enable to PCI 0x0000 0000

0x04 0x016C 0010 0x0020 0010 0x0020 0010 IT Interrupt type 0x0000 0006 Y

0x05 0x016C 0014 0x0020 0014 0x0020 0014 GCSR General control and status register 0x1F00 0011

0x06 0x016C 0018 0x0020 0018 0x0020 0018 TTP Timer trigger point 0x0000 0001

0x07 0x016C 001C 0x0020 001C 0x0020 001C TV Timer value 0x0000 0000

0x08 0x016C 0020 0x0020 0020 0x0020 0020 SCR Serial EEPROM control 0x0000 302C

0x09 0x016C 0024 0x0020 0024 0x0020 0024 SEA Serial EEPROM address 0x0000 0000

0x0A 0x016C 0028 0x0020 0028 0x0020 0028 SED Serial EEPROM data 0x0000 0000

0x0B 0x016C 002C 0x0020 002C 0x0020 002C PFR Pin Function Register 0x0000 0000

0x0C 0x016C 0030 0x0020 0030 0x0020 0030 reserved 0x0000 0000

0x0D 0x016C 0034 0x0020 0034 0x0020 0034 reserved 0x0000 0000

0x0E 0x016C 0038 0x0020 0038 0x0020 0038 REV Chip Rev Code 0x0000 0010

0x0F 0x016C 003C 0x0020 003C 0x0020 003C RAC Register access control 0x0000 0100

0x10 0x016C 0040 0x0020 0040 0x0020 0040 DDA DSP Address 0x0000 0000

0x11 0x016C 0044 0x0020 0044 0x0020 0044 DPA PCI Address 0x0000 0000

0x12 0x016C 0048 0x0020 0048 0x0020 0048 DLNGTH Length 0x0000 0000

0x13 0x016C 004C 0x0020 004C 0x0020 004C DINTP Interrupt Point 0x0000 0000 Y

0x14 0x016C 0050 0x0020 0050 0x0020 0050 DSTRD DSP Stride 0x0000 0000

0x15 0x016C 0054 0x0020 0054 0x0020 0054 DPC Packet Control 0x0000 00F6 Y

0x16 0x016C 0058 0x0020 0058 0x0020 0058 DCAR DMA Chain Address Register 0x0000 0000

0x17 0x016C 005C 0x0020 005C 0x0020 005C reserved 0x0000 0000

0x18 0x016C 0060 0x0020 0060 0x0020 0060 DCDA Current DSP Address 0x0000 0000

0x19 0x016C 0064 0x0020 0064 0x0020 0064 DCPA Current PCI Address 0x0000 0000

0x1A 0x016C 0068 0x0020 0068 0x0020 0068 DCLNTGH Current Length 0x0000 0000

0x1B 0x016C 006C 0x0020 006C 0x0020 006C DBC PCI DMA burst control 0x0020 0020

0x1C 0x016C 0070 0x0020 0070 0x0020 0070 DFC DMA FIFO Control 0x0000 0620

0x1D 0x016C 0074 0x0020 0074 0x0020 0074 DBE PCI byte enable and command register 0x0000 0000

0x1E 0x016C 0078 0x0020 0078 0x0020 0078 0x0000 0000

0x1F 0x016C 007C 0x0020 007C 0x0020 007C 0x0000 0000

0x20 0x016C 0080 0x0020 0080 0x0020 0080 BCC0A DSP Cycle control 0A 0x0010 0021 Y

0x21 0x016C 0084 0x0020 0084 0x0020 0084 BCC0B DSP Cycle control 0B 0x0000 0140 Y

0x22 0x016C 0088 0x0020 0088 0x0020 0088 BCC0C DSP Cycle control 0C 0xB401 6820 Y

0x23 0x016C 008C 0x0020 008C 0x0020 008C BCC0D DSP Cycle control 0D 0x2800 2800 Y

0x24 0x016C 0090 0x0020 0090 0x0020 0090 BCC1A DSP Cycle control 1A 0x0000 0000

0x25 0x016C 0094 0x0020 0094 0x0020 0094 BCC1B DSP Cycle control 1B 0x0000 0000

0x26 0x016C 0098 0x0020 0098 0x0020 0098 BCC1C DSP Cycle control 1C 0x0000 0000

0x27 0x016C 009C 0x0020 009C 0x0020 009C BCC1D DSP Cycle control 1D 0x0000 0000

'C6x

Address

PCI Bus

Offset

Slave A32/A24

SCV64 Offset

Register Description Value Initialize

34

Part Number 500-00191

Revision 2.00

Page 47

Spectrum Signal Processing Monaco Technical Reference

PCI Interface

Hurricane

DSP Offset

0x28 0x016C 00A0 0x0020 00A0 0x0020 00A0 BCC2A DSP Cycle control 2A 0x0000 0000

0x29 0x016C 00A4 0x0020 00A4 0x0020 00A4 BCC2B DSP Cycle control 2B 0x0000 0000

0x2A 0x016C 00A8 0x0020 00A8 0x0020 00A8 BCC2C DSP Cycle control 2C 0x0000 0000

0x2B 0x016C 00AC 0x0020 00AC 0x0020 00AC BCC2D DSP Cycle control 2D 0x0000 0000

0x2C 0x016C 00B0 0x0020 00B0 0x0020 00B0 BCC3A DSP Cycle control 3A 0x00D6 1DE0

0x2D 0x016C 00B4 0x0020 00B4 0x0020 00B4 BCC3B DSP Cycle control 3B 0x0000 0000

0x2E 0x016C 00B8 0x0020 00B8 0x0020 00B8 BCC3C DSP Cycle control 3C 0xA9E0 69A0

0x2F 0x016C 00BC 0x0020 00BC 0x0020 00BC BCC3D DSP Cycle control 3D 0x0000 0000

0x30 0x016C 00C0 0x0020 00C0 0x0020 00C0 BMI0 Bank 0 Mapping Information 0x1000 0003 Y

0x31 0x016C 00C4 0x0020 00C4 0x0020 00C4 BMI1 Bank 1 Mapping Information 0x0000 0000

0x32 0x016C 00C8 0x0020 00C8 0x0020 00C8 BMI2 Bank 2 Mapping Information 0x0000 0000

0x33 0x016C 00CC 0x0020 00CC 0x0020 00CC BMI3 Bank 3 Mapping Information 0x0000 0000

0x34 0x016C 00D0 0x0020 00D0 0x0020 00D0 BMI4 Bank 4 Mapping Information 0x0000 0000

0x35 0x016C 00D4 0x0020 00D4 0x0020 00D4 BMI5 Bank 5 Mapping Information 0x0000 0000

0x36 0x016C 00D8 0x0020 00D8 0x0020 00D8 BMI6 Bank 6 Mapping Information 0x0000 0000

0x37 0x016C 00DC 0x0020 00DC 0x0020 00DC BMI7 Bank 7 Mapping Information 0x0000 0000

0x38 0x016C 00E0 0x0020 00E0 0x0020 00E0 BMI8 Bank 8 Mapping Information 0x0000 0000

0x39 0x016C 00E4 0x0020 00E4 0x0020 00E4 CSCR Cycle select (all banks) 0x0000 0000 Y

0x3A 0x016C 00E8 0x0020 00E8 0x0020 00E8 MABE

0x3B 0x016C 00EC 0x0020 00EC 0x0020 00EC IRBAR Internal Register Base Address Register 0x0020 0000 Y

0x3C 0x016C 00F0 0x0020 00F0 0x0020 00F0 PCS Programmable Chip Select 0x0000 0000 Y

0x3D 0x016C 00F4 0x0020 00F4 0x0020 00F4 DSPBT DSP bus timer control register 0x0000 0000

0x3E 0x016C 00F8 0x0020 00F8 0x0020 00F8 DBIC DSP bus interface control 0x0000 0000

0x3F 0x016C 00FC 0x0020 00FC 0x0020 00FC reserved 0x0000 0000

0x40 0x016C 0100 0x0020 0100 0x0020 0100 0xFFFF12FB

0x41 0x016C 0104 0x0020 0104 0x0020 0104 0x0280 0006

0x42 0x016C 0108 0x0020 0108 0x0020 0108 0x0680 0000

0x43 0x016C 010C 0x0020 010C 0x0020 010C 0x0000 0000

0x44 0x016C 0110 0x0020 0110 0x0020 0110 0x0000 0000

0x45 0x016C 0114 0x0020 0114 0x0020 0114 0x0000 0000

0x46 0x016C 0118 0x0020 0118 0x0020 0118 PCI Configuration Registers 0x0000 0000

0x47 0x016C 011C 0x0020 011C 0x0020 011C 0x0000 0000

0x48 0x016C 0120 0x0020 0120 0x0020 0120 0x0000 0000

0x49 0x016C 0124 0x0020 0124 0x0020 0124 0x0000 0000

0x4A 0x016C 0128 0x0020 0128 0x0020 0128 0x0000 0000

0x4B 0x016C 012C 0x0020 012C 0x0020 012C 0xFFFF FFFF

0x4C 0x016C 0130 0x0020 0130 0x0020 0130 0x0000 0000

0x4D 0x016C 0134 0x0020 0134 0x0020 0134 0x0000 0000

0x4E 0x016C 0138 0x0020 0138 0x0020 0138 0x0000 0000

'C6x

Address

PCI Bus

Offset

Slave A32/A24

SCV64 Offset

Register Description Value Initialize

CSER

BER

Map Bank Enable

Chip Select Enable

Mask Broadcast

0x0001 0100 Y

Part Number 500-00191

Revision 2.00

35

Page 48

Monaco Technical Reference Spectrum Signal Processing

PCI Interface

Hurricane

DSP Offset

0x4F 0x016C 013C 0x0020 013C 0x0020 013C 0x0120 0100

0x50 0x016C 0140 0x0020 0140 0x0020 0140 BAR0 Shadow Register 0xFF00 0000 Y

'C6x

Address

PCI Bus

Offset

Slave A32/A24

SCV64 Offset

Register Description Value Initialize

6.2. Hurricane Implementation

The Hurricane PCI-to-DSP Bridge Data Sheet should be read in order to understand

how it is used with the Monaco board.

On the DSP port of the Hurricane, only bank 0 is used to access the Global Shared Bus.

All other Hurricane DSP banks are unused.

There are two devices on the PMC site’s PCI bus: the Hurricane chip and the PMC

device. The IDSEL line from each of the two PCI devices is connected to the following

Address/Data lines:

PCI Device IDSEL Connection

Hurricane AD16

PMC Module AD17

36

Part Number 500-00191

Revision 2.00

Page 49

Spectrum Signal Processing Monaco Technical Reference

r

d

l

o

JTAG Debugging

7 JTAG Debugging

The Monaco board supports JTAG in-circuit emulation from a built in 74ACT8990 Test

Bus Controller. The 74ACT8990 Test Bus Controller permits the VME interface to

operate the JTAG chain. There are also two JTAG connectors for an XDS510 or White

Mountain debugger, JTAG IN (J1) and JTAG OUT (J2), which can route the JTAG

chain off-board.

JTAG in-circuit emulation is fed to the Test Bus Controller from the VME A24

secondary interface. C source debugging using an emulator board running a debug

monitor on an adjacent computer is supported through the JTAG IN connector. If a

JTAG IN connection with a clock signal is present the Test Bus Controller is

automatically disconnected.

JTAG data lines are routed to each available ‘C6x node. The full JTAG chain is shown

in the following diagram. Unpopulated processor nodes are bypassed.

TDO

JTAG OUT

TDI

The Test Bus Controlle

(TBC) is disable

(bypassed) if an externa

debugger is connected t

the JTAG IN connector.

Figure 11 JTAG Chain