ICX432DQ

2

8

V

H

Pin 1

Pin 11

48

4

Diagonal 6.67mm (Type 1/2.7) Frame Readout CCD Image Sensor with a Square Pixel for Color Cameras

Description

The ICX432DQ is a diagonal 6.67mm (Type 1/2.7)

interline CCD solid-state image sensor with a square

pixel array and 3.24M effective pixels. Adoption of a

3-field readout system ensures small size and high

performance. This chip features an electronic shutter

with variable charge-storage time.

R, G, B primary color mosaic filters are used as

the color filters, and at the same time high sensitivity

and low dark current are achieved through the

adoption of Super HAD CCD technology.

This chip is suitable for applications such as

electronic still cameras, etc.

Features

• Supports frame readout system

• High horizontal and vertical resolution

• Supports high frame rate readout mode : 30 frames/s,

AF mode : 60 frames/s, 50 frames/s

• Square pixel

• Horizontal drive frequency: 24.3MHz

• No voltage adjustments (reset gate and substrate bias are not adjusted.)

• R, G, B primary color mosaic filters on chip

• High sensitivity, low dark current

• Continuous variable-speed shutter

• Excellent anti-blooming characteristics

• 18-pin high-precision plastic package

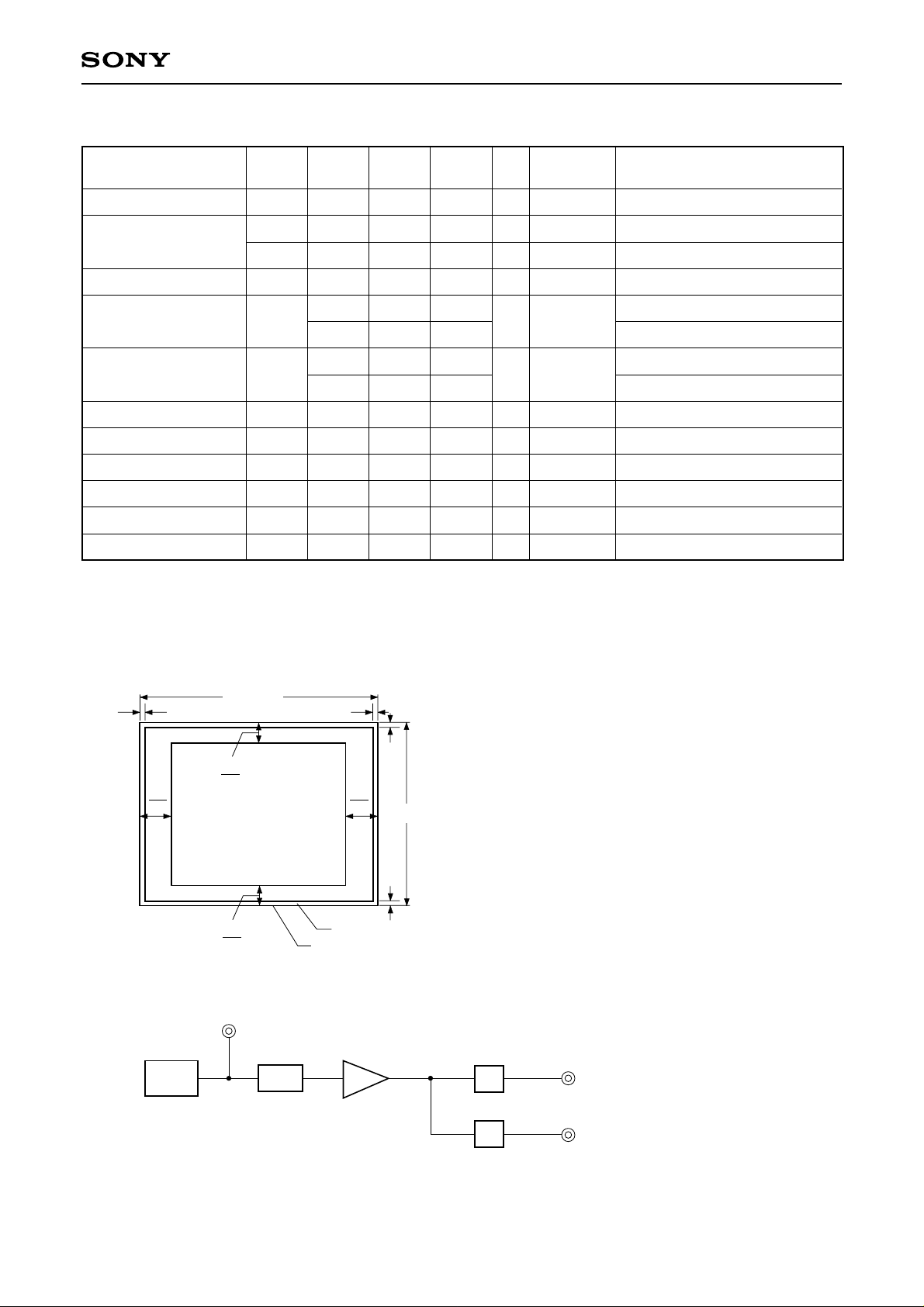

18 pin DIP (Plastic)

Optical black position

(T op View)

Device Structure

• Interline CCD image sensor

• Total number of pixels: 2140 (H) × 1560 (V) approx. 3.34M pixels

• Number of effective pixels: 2088 (H) × 1550 (V) approx. 3.24M pixels

• Number of active pixels: 2080 (H) × 1542 (V) approx. 3.21M pixels diagonal 6.667mm

• Number of recommended recording pixels:

2048 (H) × 1536 (V) approx. 3.15M pixels diagonal 6.592mm aspect ratio 4:3

• Chip size: 6.10mm (H) × 4.95mm (V)

• Unit cell size: 2.575µm (H) × 2.575µm (V)

• Optical black: Horizontal (H) direction: Front 4 pixels, rear 48 pixels

Vertical (V) direction: Front 8 pixels, rear 2 pixels

• Number of dummy bits: Horizontal 28

Vertical 1 (3rd field only)

• Substrate material: Silicon

∗

Super HAD CCD is a trademark of Sony Corporation. The Super HAD CCD is a version of Sony's high performance CCD HAD (Hole-

Accumulation Diode) sensor with sharply improved sensitivity by the incorporation of a new semiconductor technology developed by

Sony Corporation.

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

– 1 –

E02122A27

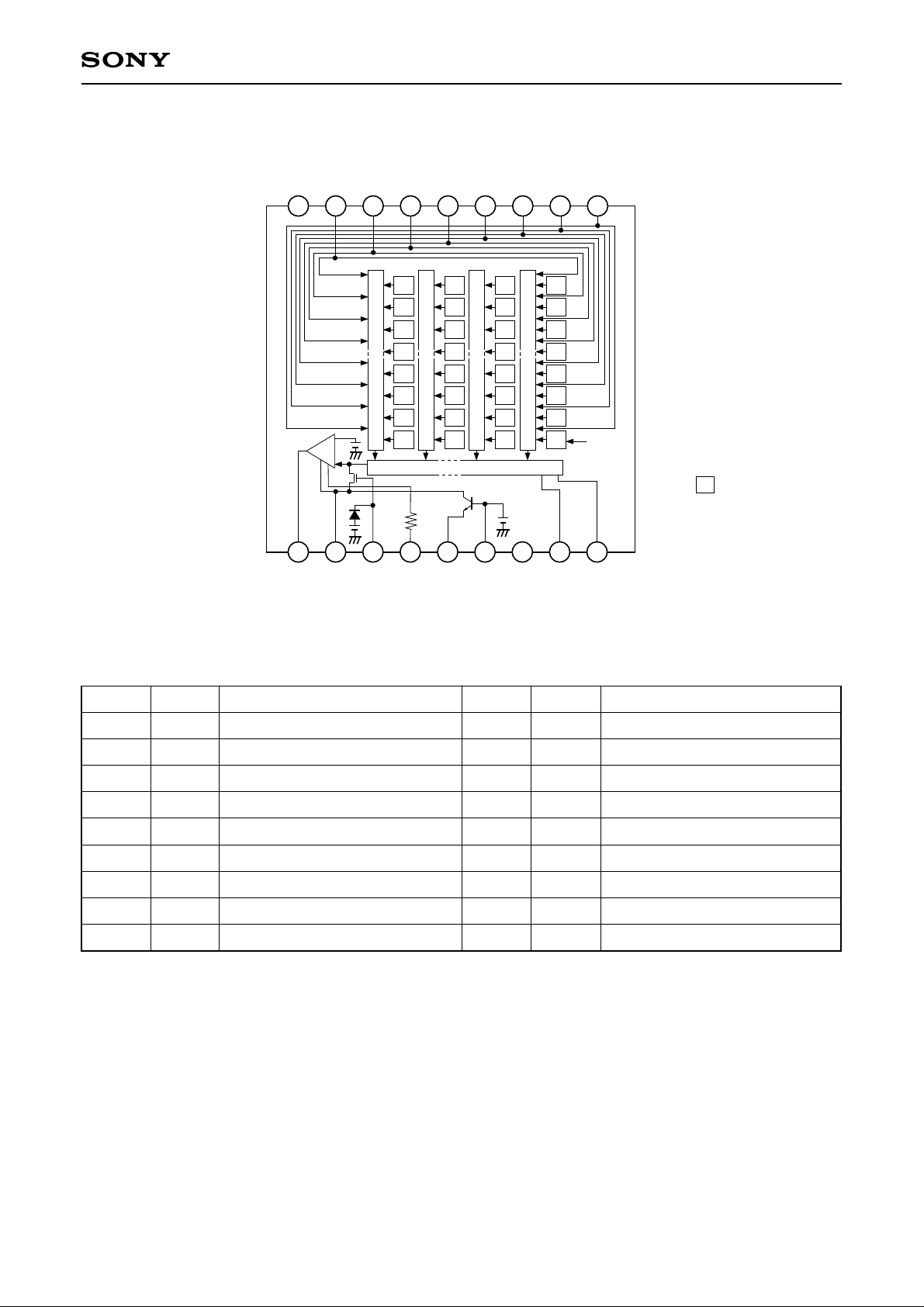

Block Diagram and Pin Configuration

(Top View)

GND

Vφ1Vφ2Vφ3AVφ3BVφ4Vφ5AVφ5BVφ

9 8 7 6 5 4 3 2 1

ICX432DQ

6

Gb

Gb

R

Gb

R

Gb

R

Vertical register

Gb

10 11 12 13 14 15 16 17 18

DD

OUT

V

V

φRG

B

SUB

C

R

Gb

R

Gb

R

Gb

Gr

B

Gr

B

Gr

B

Horizontal register

GND

φSUB

B

Gr

B

Gr

B

Gr

B

GrRGrR

Note)

Note) : Photo sensor

L

V

2

Hφ1Hφ

Pin Description

Pin No. Description Pin No. Symbol Description

1

Symbol

Vφ6

Vertical register transfer clock

10

VOUT

Signal output

2

3

4

5

6

7

8

9

1

∗

DC bias is generated within the CCD, so that this pin should be grounded externally through a

Vφ5B

Vφ5A

Vφ4

Vφ3B

Vφ3A

Vφ2

Vφ1

GND

Vertical register transfer clock

Vertical register transfer clock

Vertical register transfer clock

Vertical register transfer clock

Vertical register transfer clock

Vertical register transfer clock

Vertical register transfer clock

GND

11

12

13

14

15

16

17

18

VDD

φRG

GND

φSUB

CSUB

VL

Hφ1

Hφ2

Supply voltage

Reset gate clock

GND

Substrate clock

Substrate bias

Protective transistor bias

Horizontal register transfer clock

Horizontal register transfer clock

capacitance of 0.1µF.

– 2 –

∗1

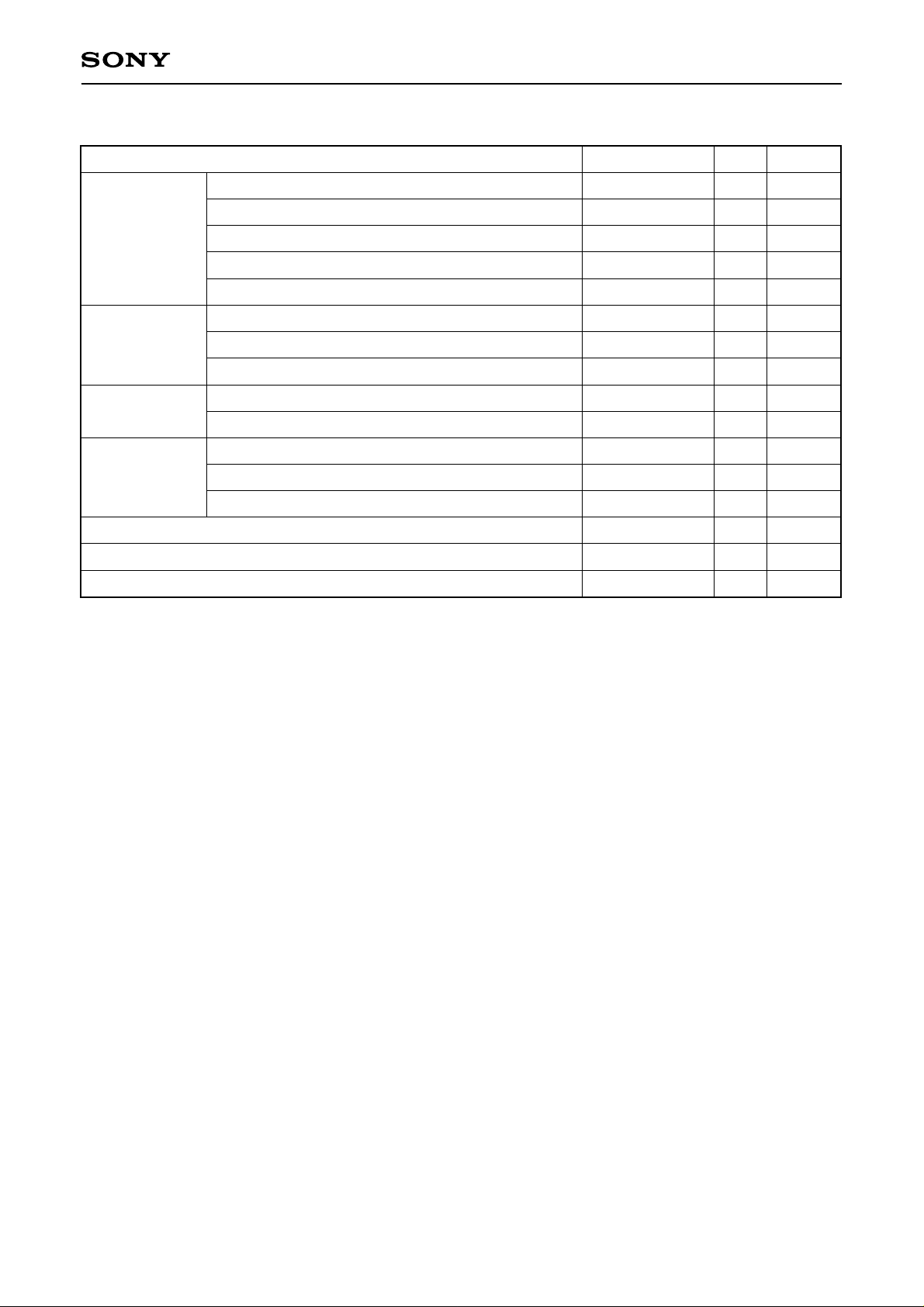

Absolute Maximum Ratings

ICX432DQ

Item

DD, VOUT, φRG – φSUB

V

Vφ

1, Vφ3A, Vφ3B, Vφ5A, Vφ5B – φSUB

Against φSUB

Vφ2, Vφ4, Vφ6, VL – φSUB

Hφ1, Hφ2, GND – φSUB

CSUB – φSUB

VDD, VOUT, φRG, CSUB – GND

Against φGND

Vφ1, Vφ2, Vφ3A, Vφ3B, Vφ4, Vφ5A, Vφ5B, Vφ6 – GND

Hφ1, Hφ2 – GND

Vφ1, Vφ3A, Vφ3B, Vφ5A, Vφ5B – VL

Against φVL

Vφ2, Vφ4, Vφ6, Hφ1, Hφ2, GND – VL

Voltage difference between vertical clock input pins

Between input

clock pins

Hφ1 – Hφ2

Hφ1, Hφ2 – Vφ6

Storage temperature

Guaranteed temperature of performance

Operating temperature

Ratings Unit Remarks

–40 to +12

–50 to +15

–50 to +0.3

–40 to +0.3

–25 to

–0.3 to +22

–10 to +18

–10 to +6.5

–0.3 to +28

–0.3 to +15

to +15

–6.5 to +6.5

–10 to +16

–30 to +80

–10 to +60

–10 to +75

V

V

V

V

V

V

V

V

V

V

V

V

V

°C

°C

°C

1

∗

1

∗

+24V (Max.) when clock width < 10µs, clock duty factor < 0.1%.

+16V (Max.) is guaranteed for turning on or off power supply.

– 3 –

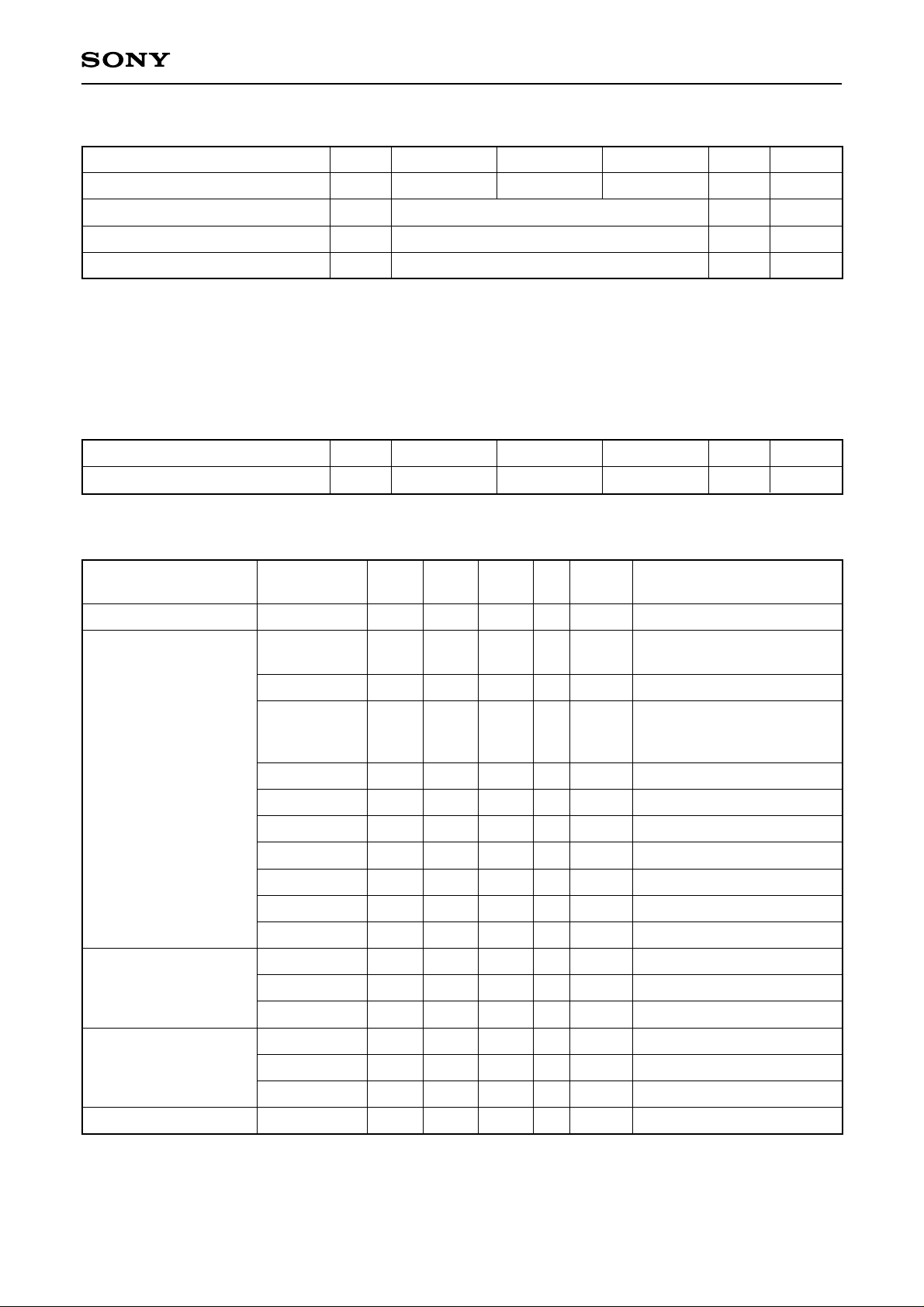

Bias Conditions

ICX432DQ

Item

Supply voltage

Protective transistor bias

Substrate clock

Reset gate clock

1

∗

VL setting is the VVL voltage of the vertical clock waveform, or the same voltage as the VL power supply for

Symbol

VDD

VL

φSUB

φRG

Min.

14.55 15.45

15.0

1

∗

2

∗

2

∗

Unit RemarksTyp. Max.

V

the V driver should be used.

2

∗

Do not apply a DC bias to the substrate clock and reset gate clock pins, because a DC bias is generated

within the CCD.

DC Characteristics

Item

Supply current

Symbol

IDD

Min. Unit RemarksTyp. Max.

7.0

mA9.05.0

Clock V olta ge Conditions

V

Waveform

Diagram

1

Remarks

Item

Readout clock voltage

VVT

Symbol

Min.

14.55

Typ.

15.0

Max. Unit

15.45

Vertical transfer clock

voltage

Horizontal transfer

clock voltage

Reset gate clock

voltage

VVH1, VVH2

VVH3, VVH4

VVH5, VVH6

VVL1, VVL2,

VVL3, VVL4,

VVL5, VVL6

VφV

VVH5 – VVH

VVH6 – VVH

VVHH

VVHL

VVLH

VVLL

VφH

VHL

VCR

VφRG

VRGLH – VRGLL

VRGL – VRGLm

–0.05

–0.2

–8.0

6.8

–0.25

–0.25

3.0

–0.05

0.5

3.0

0

0

–7.5

7.5

3.3

0

1.65

3.3

0.05

0.05

–7.0

8.05

0.1

0.1

0.8

0.9

0.9

0.8

3.6

0.05

3.6

0.4

0.5

VVH = (VVH1 + VVH2 + VVH3

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

2

+ VVH4)/2

2

2

VVL = (VVL5 + VVL6)/2

2

VφV = VVHn – VVLn (n = 1 to 6)

2

2

2

High-level coupling

2

High-level coupling

2

Low-level coupling

2

Low-level coupling

3

3

3

Cross-point voltage

4

4

Low-level coupling

4

Low-level coupling

Substrate clock voltage

VφSUB

21.5

22.5

– 4 –

23.5

V

5

Clock Equivalent Circuit Constants

ICX432DQ

Item Min. Typ. Max.

Capacitance between vertical transfer

clock and GND

Capacitance between vertical transfer

clocks

Capacitance between horizontal transfer

clock and GND

Capacitance between horizontal transfer

clocks

Capacitance between reset gate clock

and GND

Capacitance between substrate clock

and GND

Symbol

CφV1

CφV3A, CφV3B,

CφV5A, CφV5B

CφV2, CφV4,

V6

Cφ

CφV12

CφV23A, CφV23B,

CφV45A, CφV45B

CφV3A4, CφV3B4,

CφV5A6, CφV5B6

CφV61

CφH1, CφH2

CφHH

CφRG

CφSUB

1280

640

400

510

50

260

100

40

70

8

1000

Unit Remarks

pF

pF

pF

pF

pF

pF

pF

pF

pF

pF

pF

Vertical transfer clock series resistor

Vertical transfer clock ground resistor

Horizontal transfer clock series resistor

CφV12

CφV2

CφV5A

CφV45A

Vφ2

R2

CφV23A

CφV3A

CφV23B

CφV3B

RGND

CφV4

Cφ

CφV3A4

R4R5A

Vφ4Vφ5A

Vφ6

Vφ5B

R6

CφV5B6

R5B

Vφ1

R1

CφV61

CφV1

CφV6

CφV5A6

CφV5B

CφV45B

R1, R2, R4, R6

R3A, R5A

R3B, R5B

RGND

RφH

R3A

Vφ3A

R3B

Vφ3B

V3B4

Hφ

Cφ

Ω

Ω

Ω

Ω

Ω

Rφ

H

Hφ

2

H2

60

240

80

18

13

Rφ

H

1

Cφ

H1

Cφ

HH

Vertical transfer clock equivalent circuit Horizontal transfer clock equivalent circuit

– 5 –

Drive Clock Waveform Conditions

(1) Readout clock waveform

100%

90%

V

VT

10%

0%

tr tf

twh

(2) Vertical transfer clock waveform

Vφ1 Vφ2

V

VH1

V

VHH

V

VH

V

VHH

V

VHL

V

VHL

ICX432DQ

φM

φM

2

0V

V

VH2

V

V

VHH

V

VHL

VH

V

VHH

V

VHL

V

VHL

V

VHH

V

VL1

V

VLH

V

VLL

V

VL

Vφ3A, Vφ3B Vφ4

V

VH3

V

V

VHL

V

VLL

V

VL

VHH

V

VH

V

VHH

V

VHL

V

VHL

V

VL3

V

VLH

Vφ5A, Vφ5B Vφ6

V

V

VHH

V

VHL

V

VH5

VHH

V

VHL

V

VH

V

VL2

V

VLH

V

VLL

V

VL

V

VHH

V

V

VHH

V

VH4

V

VHL

V

VHL

V

VL

V

V

VHH

V

VH6

VHH

V

VHL

VH

V

VHL

V

VLH

V

VL4

V

VLL

V

VH

V

VL5

V

VL

VVH = (VVH1 + VVH2 + VVH3 + VVH4)/4

VVL = (VVL5 + VVL6)/2

VφV = VVHn – VVLn (n = 1 to 6)

V

V

V

VLH

V

VLL

VLH

V

V

VLL

VL

VL6

– 6 –

(3) Horizontal transfer clock waveform

ICX432DQ

tf

VCR

twl

VHL

Hφ

90%

10%

Hφ

tr

2

1

twh

Vφ

H

VφH

2

two

Cross-point voltage for the Hφ1 rising side of the horizontal transfer clocks Hφ1 and Hφ2 waveforms is VCR.

The overlap period for twh and twl of horizontal transfer clocks Hφ1 and Hφ2 is two.

(4) Reset gate clock waveform

RG waveform

tr twh

Vφ

RG

tf

V

RGH

twl

Point A

V

V

V

RGLH

RGLL

RGLm

V

RGL

VRGLH is the maximum value and VRGLL is the minimum value of the coupling waveform during the period from

Point A in the above diagram until the rising edge of RG.

In addition, VRGL is the average value of VRGLH and VRGLL.

VRGL = (VRGLH + VRGLL)/2

Assuming VRGH is the minimum value during the interval with twh, then:

VφRG = VRGH – VRGL

Negative overshoot level during the falling edge of RG is VRGLm.

(5) Substrate clock waveform

100%

90%

φM

Vφ

10%

V

(A bias generated within the CCD)

SUB

0%

SUB

tr tftwh

φM

2

– 7 –

Clock Switching Characteristics (Horizontal drive frequency: 24.3MHz)

ICX432DQ

Item

Readout clock

Symbol

VT

Vφ1, Vφ2,

Vertical transfer

clock

Vφ3A, Vφ3B,

Vφ4, Vφ5A,

Vφ5B, Vφ6

Horizontal

transfer clock

Reset gate clock

Substrate clock

Hφ1

Hφ2

φRG

φSUB

Horizontal transfer clock

Min.

2.63

11

11

6

2.5

Symbol

Hφ1, Hφ2

twh

twl tr tf

Typ. Max.Min. Typ. Max.Min. Typ. Max. Min. T yp . Max.

2.83

15

15

8

3.02

111115

15

28

0.5

6.0

6.0

3

9.5

9.5

0.5

15

0.5

6.0

6.0

3

350

9.5

9.5

0.5

two

UnitnsRemarksItem

Min.

Typ. Max.

10 15

Unit

µs

ns

ns

ns

µs

Remarks

During

readout

When using

CXD3400N

tf ≥ tr – 2ns

During drain

charge

Spectral Sensitivity Characteristics (excludes lens characteristics and light source characteristics)

1.0

0.9

0.8

0.7

0.6

0.5

0.4

Relative Response

0.3

0.2

0.1

0

400

B

450 500 550

G

R

600 650 700

Wave Length [nm]

– 8 –

ICX432DQ

Image Sensor Characteristics (horizontal drive frequency: 24.3MHz) (Ta = 25°C)

Item

G Sensitivity

Sensitivity

comparison

Saturation signal

Smear

Symbol

Sg

Rr

Rb

Vsat

Sm

Min.

165

0.46

0.33

420

Typ.

220

–87.5

–78

Max.

275

0.72

0.59

–80

–70.5

20

Video signal shading

SHg

25

Dark signal

Dark signal shading

Line crawl G

Line crawl R

Line crawl B

Lag

1

∗

After closing the mechanical shutter, the smear can be reduced to below the detection limit by performing

Vdt

∆Vdt

Lcg

Lcr

Lcb

Lag

10

8

3.8

3.8

3.8

0.5

Measurement

Unit

method

mV

mV

dB

%

mV

mV

%

%

%

%

Remarks

1

1/30s accumulation

1

1

2

Ta = 60°C

Frame readout mode

1

∗

3

High frame rate readout mode

Zone 0 and I

4

Zone 0 to II'

5

6

Ta = 60°C, 5.0 frame/s

Ta = 60°C, 5.0 frame/s,

7

7

7

8

vertical register sweep operation.

2

∗

Excludes vertical dark signal shading caused by vertical register high-speed transfer.

2

∗

Zone Definition of Video Signal Shading

2088 (H)

4

V

H

8

10

Zone 0, I

V

10

4

H

8

Zone II, II'

Ignored region

Effective pixel region

Measurement System

CCD signal output [∗A]

CCD C.D.S

AMP

4

1550 (V)

4

S/H

Gr/Gb channel signal output [∗B]

S/H

R/B channel signal output [∗C]

Note) Adjust the amplifier gain so that the gain between [∗A] and [∗B], and between [∗A] and [∗C] equals 1.

– 9 –

Loading...

Loading...