CMOS 16-bit Single Chip Microcomputer

Description

The CXP921000A is a CMOS 16-bit single chip

microcomputer of piggyback/evaluator combined

type, which is developed for evaluating the function

of the CXP921064A.

Features

• An efficient instruction set as a controller

– Direct addressing, numerous abbreviated forms,

multiplication and division instructions

• Instruction sets for C Ianguage and RTOS

– Highly quadratic instruction system,

general-purpose register of eight 16-bit × 16-bank configuration

• Minimum instruction cycle time 100ns at 20MHz operation (2.7 to 3.3V)

61µs at 32kHz operation (2.2 to 3.3V)

• Incorporated EPROM CXP27V1000K

• Incorporated RAM capacity 10K bytes

• Peripheral functions

— A/D converter 8-bit 12 analog input, 2 channels successive approximation system,

automatic scanning function, (Conversion time: 3.4µs at 20MHz)

— Serial interface 128 -byte buffer RAM, 3 channels

8-stage FIFO, 1 channel (supports special mode master/slave)

—I2C bus interface 64-byte buffer RAM , 2 channels

(supports master/slave and automatic transfer mode)

— Timers 8-bit timer/counter, 2 channels (with timing output)

16-bit timer, 3 channels

— Real-time pulse generator 5-bit output, 1 channel (2-stage FIFO)

— Clock prescaler

— Remote control receive circuit 8-bit pulse measurement counter, 8-stage FIFO

• Interruption 30 factors, 30 vectors, multi-interruption and priority selection possible

• Standby mode Sleep/stop

• Package 100-pin Ceramic PQFP

• Mask ROM CXP921064A

•

FLASH EEPROM incorporated type

CXP921F064A

Structure

Silicon gate CMOS IC

– 1 –

E99X11-PS

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

CXP921000A

100 pin PQFP (Ceramic)

Piggy/

evaluation type

(QFP supported)

(LQFP supported)

– 2 –

CXP921000A

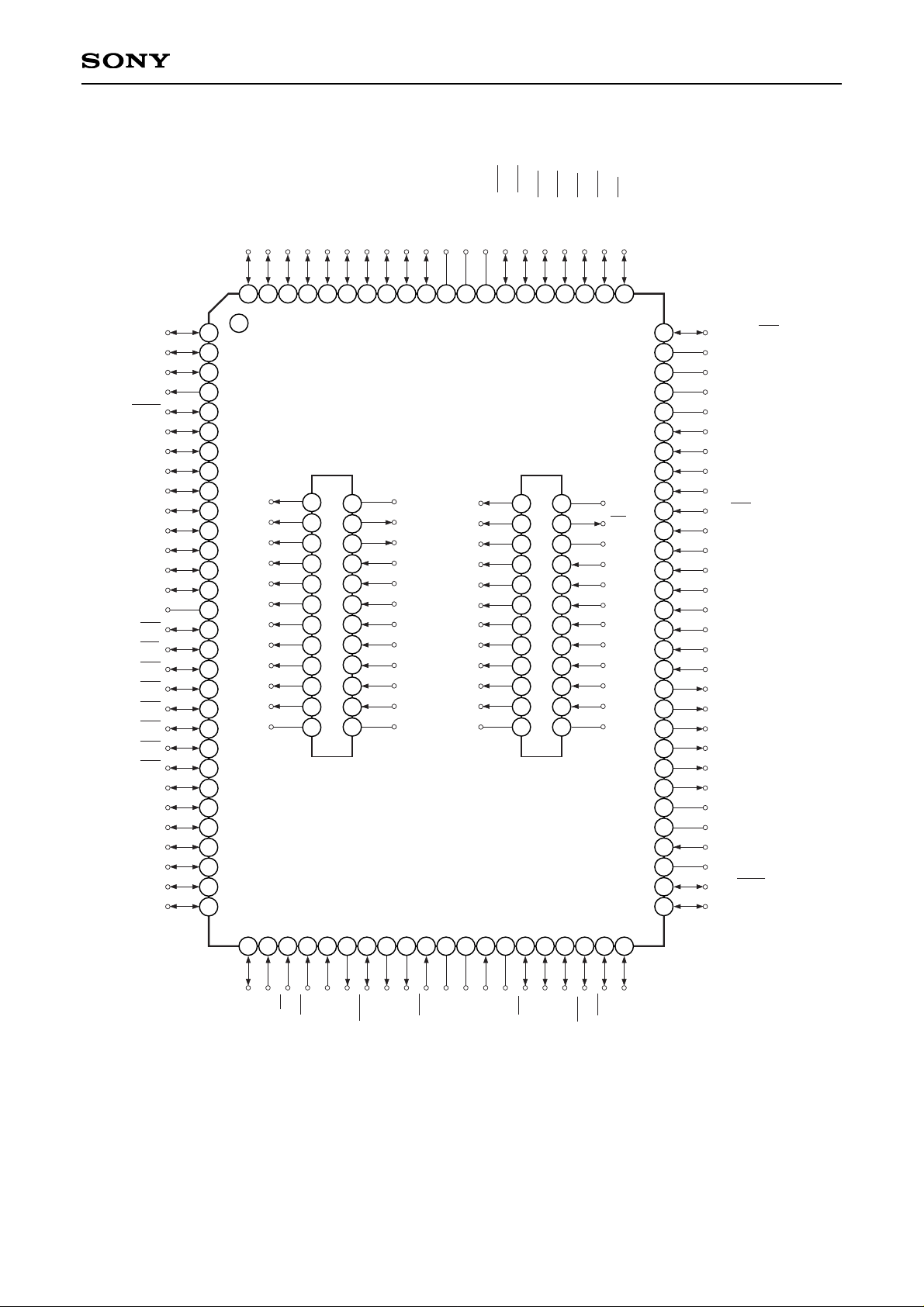

Pin Assignment in Piggyback Mode (Top View) 100-pin QFP package

31 32 33 34 35 36 37 38 39 40 41 42 43 44 454647 48 49 50

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81828384858687888990919293949596979899

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

PE7

PF0

PF1/EC

PF2/CS0

PF3/SI0

PF4/SO0

PF5/SCK0

PF6/TO

PF7/TMO

RST

V

SS

XTAL

EXTAL

V

DD

PG0/CS1

PG1/SI1

PG2/SO1

PG3/SCK1

PG4/CS2

PG5/SI2

PJ0/AN4/KS8

AV

DD

AVREF1

AVREF0

AVss

AN3

AN2

AN1

PI7/AN0

PI6/NMI

PI5/INT7

PI4/INT6

PI3/INT5

PI2/INT4

PI1/INT3

PI0/INT2

PH7/INT1

PH6/INT0

PH5/XOUT

PH4/RTO4

PH3/RTO3

PH2/RTO2

PH1/RTO1

PH0/RTO0

Vss

51

52

53

54

55

56

TX

TEX

V

DD

PG7/SCK2

PG6/SO2

PB2/AN22

PB3/AN23

PB4/SI3

PB5/SO3

PB6/SCK3

PB7/RMC

PC0/SDA0

PC1/SCL0

PC2/SDA1

PC3/SCL1

PC4

PC5

PC6

PC7

V

SS

PD0/KS0

PD1/KS1

PD2/KS2

PD3/KS3

PD4/KS4

PD5/KS5

PD6/KS6

PD7/KS7

PE0

25

26

27

28

29

PE1

PE2

PE3

PE4

PE5

30

PE6

PB1/AN21

PB0/AN20

PA7/AN19

PA6/AN18

PA5/AN17

PA4/AN16

PA3/AN15

PA2/AN14

PA1/AN13

PA0/AN12

VSSVDD

NC

PJ7/AN11/KS15

PJ6/AN10/KS14

PJ5/AN9/KS13

PJ4/AN8/KS12

PJ3/AN7/KS11

PJ2/AN6/KS10

PJ1/AN5/KS9

100

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

A10

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

Vss

VDD

A11

A12

D7

D6

D5

D4

D3

D2

D1

D0

Vss

25

26

27

28

29

30

31

32

33

34

35

36 37

38

39

40

41

42

43

44

45

46

47

48

A23

A22

A21

A20

A19

A18

A17

A16

A15

A14

A13

Vss

VDD

CE

NC

D15

D14

D13

D12

D11

D10

D9

D8

Vss

Note) 1. NC (Pin 88) must be left open. However, use this pin for FLASH EEPROM

incorporated version.

2. Vss (Pins 15, 41, 56 and 90) must be connected to GND.

3. VDD (Pins 44, 53 and 89) must be connected to VDD.

4. A20 to A23 are always high level output.

– 3 –

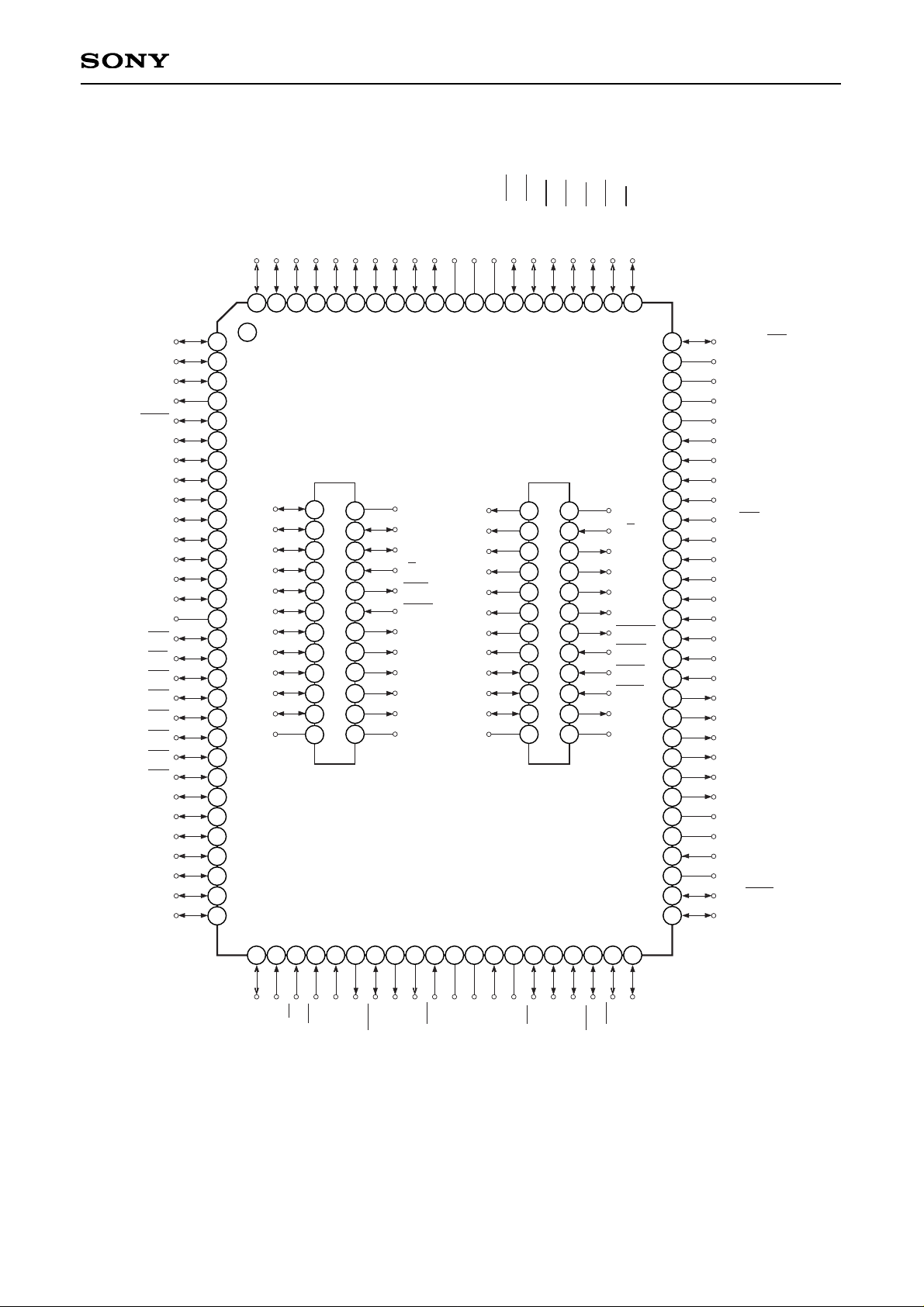

CXP921000A

31 32 33 34 35 36 37 38 39 40 41 42 43 44 454647 48 49 50

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81828384858687888990919293949596979899

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

PE7

PF0

PF1/EC

PF2/CS0

PF3/SI0

PF4/SO0

PF5/SCK0

PF6/TO

PF7/TMO

RST

V

SS

XTAL

EXTAL

V

DD

PG0/CS1

PG1/SI1

PG2/SO1

PG3/SCK1

PG4/CS2

PG5/SI2

PJ0/AN4/KS8

AV

DD

AVREF1

AVREF0

AVss

AN3

AN2

AN1

PI7/AN0

PI6/NMI

PI5/INT7

PI4/INT6

PI3/INT5

PI2/INT4

PI1/INT3

PI0/INT2

PH7/INT1

PH6/INT0

PH5/XOUT

PH4/RTO4

PH3/RTO3

PH2/RTO2

PH1/RTO1

PH0/RTO0

Vss

51

52

53

54

55

56

TX

TEX

V

DD

PG7/SCK2

PG6/SO2

PB2/AN22

PB3/AN23

PB4/SI3

PB5/SO3

PB6/SCK3

PB7/RMC

PC0/SDA0

PC1/SCL0

PC2/SDA1

PC3/SCL1

PC4

PC5

PC6

PC7

V

SS

PD0/KS0

PD1/KS1

PD2/KS2

PD3/KS3

PD4/KS4

PD5/KS5

PD6/KS6

PD7/KS7

PE0

25

26

27

28

29

PE1

PE2

PE3

PE4

PE5

30

PE6

PB1/AN21

PB0/AN20

PA7/AN19

PA6/AN18

PA5/AN17

PA4/AN16

PA3/AN15

PA2/AN14

PA1/AN13

PA0/AN12

VSSVDD

NC

PJ7/AN11/KS15

PJ6/AN10/KS14

PJ5/AN9/KS13

PJ4/AN8/KS12

PJ3/AN7/KS11

PJ2/AN6/KS10

PJ1/AN5/KS9

100

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

AD10

AD9

AD8

AD7

AD6

AD5

AD4

AD3

AD2

AD1

AD0

Vss

VDD

AD11

AD12

I/T

MON

ERST

C1

C2

QS0

QS1

QS2

Vss

25

26

27

28

29

30

31

32

33

34

35

36 37

38

39

40

41

42

43

44

45

46

47

48

A23

A22

A21

A20

A19

A18

A17

A16

AD15

AD14

AD13

Vss

VDD

E/P

ST0

ST1

ST2

ST3

WTACK

JRQH

JRQL

ENMI

MS

Vss

Pin Assignment in Evaluator Mode (Top View) 100-pin QFP package

Note) 1. NC (Pin 88) must be left open. However, use this pin for FLASH EEPROM

incorporated version.

2. Vss (Pins 15, 41, 56 and 90) must be connected to GND.

3. VDD (Pins 44, 53 and 89) must be connected to VDD.

– 4 –

Loading...

Loading...