Sony CXP88460, CXP88452 Datasheet

CXP88452/88460

CMOS 8-bit Single Chip Microcomputer

Description

The CXP88452/88460 is a CMOS 8-bit microcomputer

which consists of A/D converter, serial interface,

timer/counter, time-base timer, high precision timing

pattern generation circuit, PWM output, VISS/VASS

circuit, 32kHz timer/counter, remote control receiving

circuit, VSYNC separator and the measurement circuit

which measure signals of capstan FG and drum

FG/PG and other servo systems, as well as basic

configurations like 8-bit CPU, ROM, RAM and I/O

port. They are integrated into a single chip.

Also, the CXP88452/88460 provides sleep/stop

functions which enable to lower power consumption.

Features

• A wide instruction set (213 instructions) which covers various types of data

— 16-bit arithmetic/multiplication and division/boolean bit operation instructions

• Minimum instruction cycle 250ns at 16MHz operation

122µs at 32kHz operation

• Incorporated ROM capacity 52K bytes (CXP88452)

60K bytes (CXP88460)

• Incorporated RAM capacity 2048 bytes

• Peripheral functions

— A/D converter 8 bits, 12 channels, successive approximation system

(Conversion time of 20µs/16MHz)

— Serial interface Incorporated 8-bit, 8-stage FIFO

(Auto transfer for 1 to 8 bytes), 1 channel

Incorporated buffer RAM (Auto transfer for 1 to 32 bytes), 1 channnel

Incorporated two-wire 8-bit and 8-stage FIFO (Auto transfer for

1 to 8 bytes), 1 channel

— Timer 8-bit timer/counter, 2 channels

19-bit time-base timer

32kHz timer/counter

— High precision timing pattern generation PPG: Maximum of 19 pins 32 stages programmable

circuit RTG: 5 pins, 1 channel

7-bit, 10-satge FIFO (RECCTL control/ATC control),

1channel

— PWM/DA gate output PWM: 12 bits, 2 channels (Repetitive frequency 62.5kHz at 16MHz)

DA gate pulse output: 13 bits, 2 channels

— Analog signal input circuit PBCTL amplifier circuit

Reel FG comparator

— CTL write/rewrite circuit Recording current control circuit

— Servo input control Capstan FG, Drum FG/PG, CTL, Reel FG input

— VSYNC separator

— FRC capture unit Incorporated 26-bit and 8-stage FIFO

— PWM output 14 bits, 1 channel

— VISS/VASS circuit Pulse duty auto detection circuit

— Remote control receiving circuit 8-bit pulse measurement counter, 6-stage FIFO

— Tri-state output PPG output 2 pins

— High speed head switching circuit

• Interruption 22 factors, 15 vectors, multi-interruption possible

• Standby mode Sleep/stop

• Package 100-pin plastic QFP

• Piggy/evaluation chip CXP88400 100-pin ceramic PQFP

– 1 –

E98772-PS

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

100 pin QFP (Plastic)

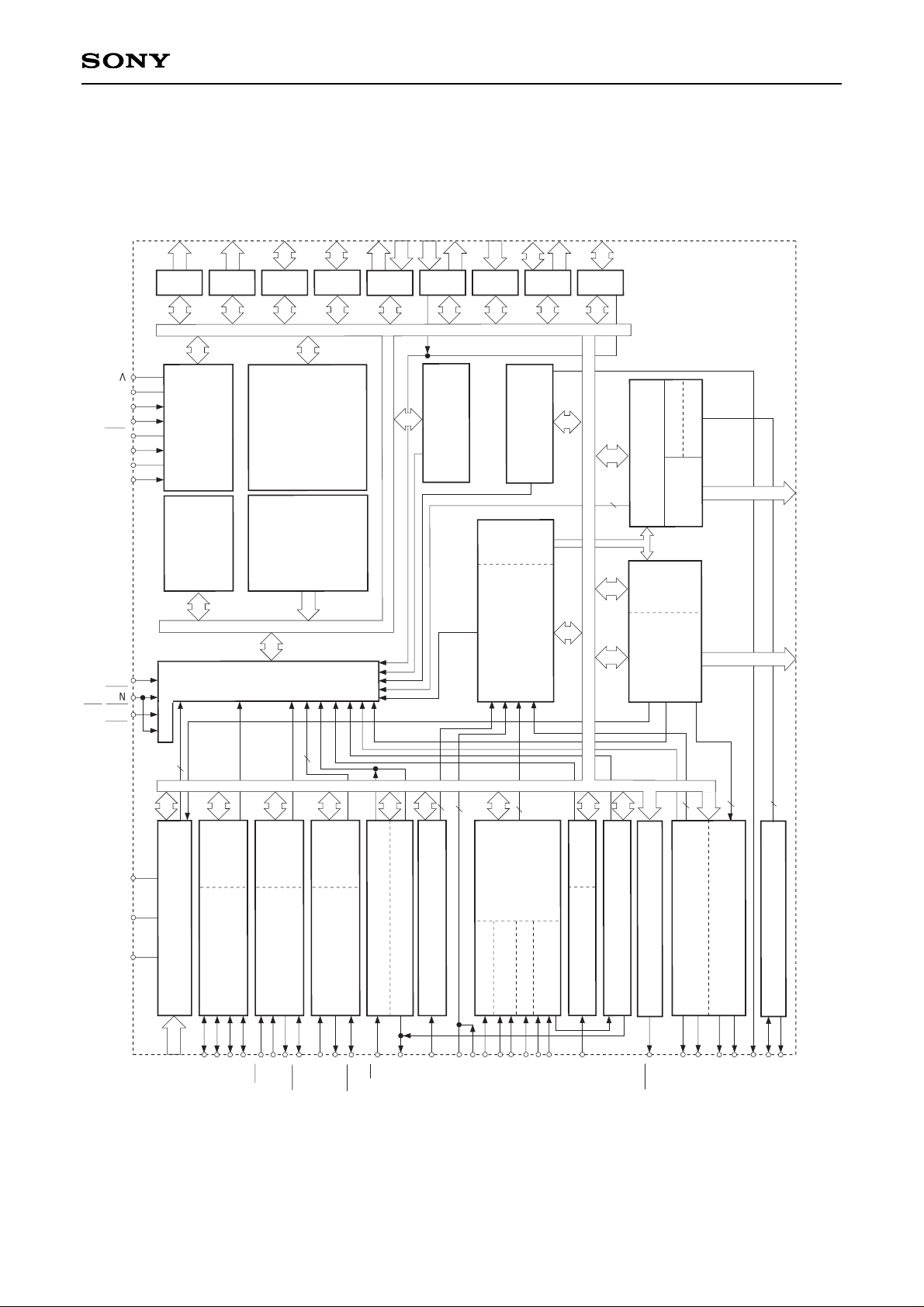

Structure

Silicon gate CMOS IC

– 2 –

CXP88452/88460

PA0 to PA7

PB0 to PB7

PC0 to PC7

PD0 to PD7

PE0, 1, 6, 7

PE2 to PE5

PF0 to PF3

PF4 to PF7

PG0 to PG3

PI0 to PI7

RST

EXTAL

CLOCK GENERATOR/

SYSTEM CONTROL

RAM

2048

BYTES

SPC700

CPU CORE

ROM

52K/60K

BYTES

INTERRUPT CONTROLLER

2

FIFO

FRC

CAPTURE UNIT

AVss

AV

REF

AV

DD

A/D CONVERTER

SERIAL

INTERFACE UNIT

(CH2)

FIFO

SCL0

AN0 to AN11

INT2

INT0

12

8

PORT A

8

PORT B

8

PORT C

PORT D

6

2

PORT E

4

4

PORT F

4

PORT G

4

PORT H

8

PORT I

PH4 to PH7

Vss

V

DD

MP

XTAL

TX

TEX

INT1/NMI

PRESCALER/

TIME-BASE TIMER

32kHz

TIMER/COUNTER

8

8-BIT TIMER/COUNTER 0

V SYNC SEPARATOR

8-BIT TIMER1

SO1

RMC

CTLFAMPI

SYNC

EC

SCK1

SI1

TO/DDO

NMI

2

2

2

5

2

5

SERIAL

INTERFACE UNIT

(CH0)

RAM

SERIAL

INTERFACE UNIT

(CH1)

FIFO

DAA1

DAA0

14-BIT PWM GENERATOR

12-BIT PWM GENERATOR CH0

SERVO INPUT

CONTROL

12-BIT PWM GENERATOR CH1

VISS/VASS

REMOCON INPUT

FIFO

CTL R/W CONTROL

PWM1

PWM0

PWM

DPG

DFG

CFG

EXI1

EXI0

HEADL

CTLHEAD

ADJ

CAPSTAIN

DRUM

PBCTL AMP

REEL

COMPARATOR

SCL1

SDA0

SDA1

CS0

SI0

SO0

SCK0

RFG0

RFG1

4

2

19

5

PROGRAMABLE

PATTERN

GENERATOR

RAM

REALTIME PULSE

GENERATOR

CH0

CH1

FIFO

PH0 to PH3

PPO0

to

PPO18

RTO3

to

RTO7

4

Block Diagram

– 3 –

CXP88452/88460

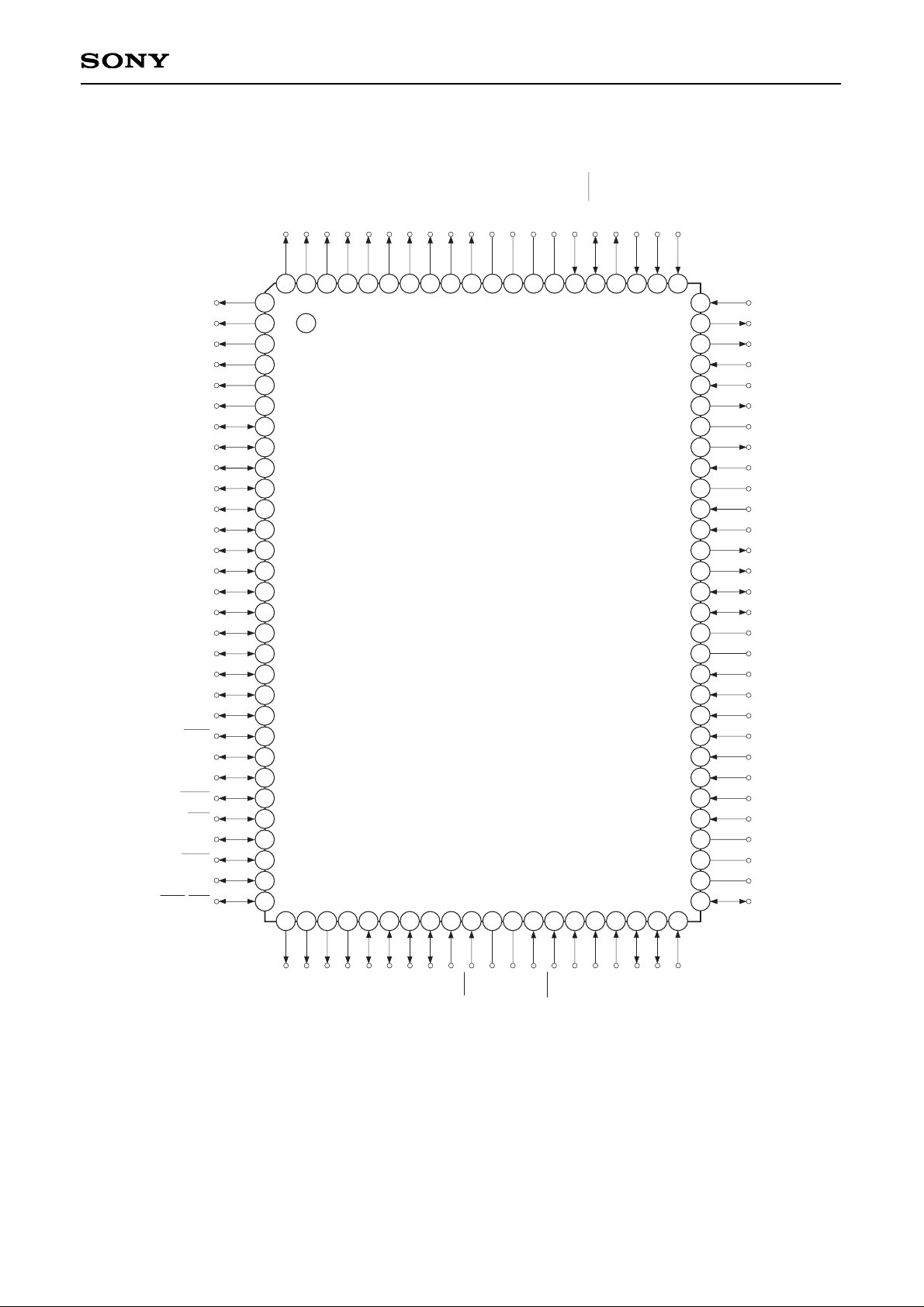

Pin Assignment (Top View)

PE5/EXI1

PH7

40

39

38

37

36

35

34

31

32

33

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

70

69

68

67

63

64

65

66

61

62

71

72

73

74

75

76

77

78

79

80

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

1

81

82

83

84

88

87

86

85

89

90

100

99

98

97

96

95

94

91

92

93

PE6/PWM0/DAA0

PE7/PWM1/DAA1

RFG0

RFG1

ANOUT

AMPV

DD

CTLFAMPO

CTLSAMPI

CTLAGND

CTLFAMPI (–)

CTLFAMPI (+)

HEADL (–)

HEADL (+)

CTLHEAD (+)

CTLHEAD (–)

AMPV

SS

VDD

AN0

AN1

AN2

AN3

PF0/AN4

PF1/AN5

PF2/AN6

PF3/AN7

AV

DD

AVREF

AVSS

PF4/AN8

PH6

PH5

PH4

PH3/SDA1

PH2/SDA0

PH1/SCL1

PH0/SCL0

MP

RST

V

SS

XTAL

EXTAL

PG3/EC/INT2

PG2/DPG

PG1/DFG

PG0/CFG

PF7/AN11

PF6/AN10

PF5/AN9

PB5/PPO13

PB4/PPO12

PB3/PPO11

PB2/PPO10

PB1/PPO9

PB0/PPO8

PC7/RTO7

PC6/RTO6

PC5/RTO5

PC4/RTO4

PC3/RTO3

PC2/PPO18

PC1/PPO17

PC0/PPO16

PI7

PI6

PI5

PI4

PI3

PI2

PI1

PI0/INT0

PD7/SI0

PD6/SO0

PD5/SCK0

PD4/CS0

PD3/SRVO/TO/DDO/ADJ

PD2/PWM

PD1/RMC

PD0/INT1/NMI

PB6/PPO14

PB7/PPO15

PA0/PPO0

PA1/PPO1

PA2/PPO2

PA3/PPO3

PA4/PPO4

PA5/PPO5

PA6/PPO6

PA7/PPO7

NC

V

DD

V

SS

TX

TEX

PE0/SCK1

PE1/SO1

PE2/SI1

PE3/SYNC

PE4/EXI0

Note) 1. NC (Pin 90) is always connected to VDD.

2. VDD (Pins 63 and 89) are both connected to VDD

3. Vss (Pins 41 and 88) are both connected to GND.

4. MP (Pin 39) is always connected to GND.

– 4 –

CXP88452/88460

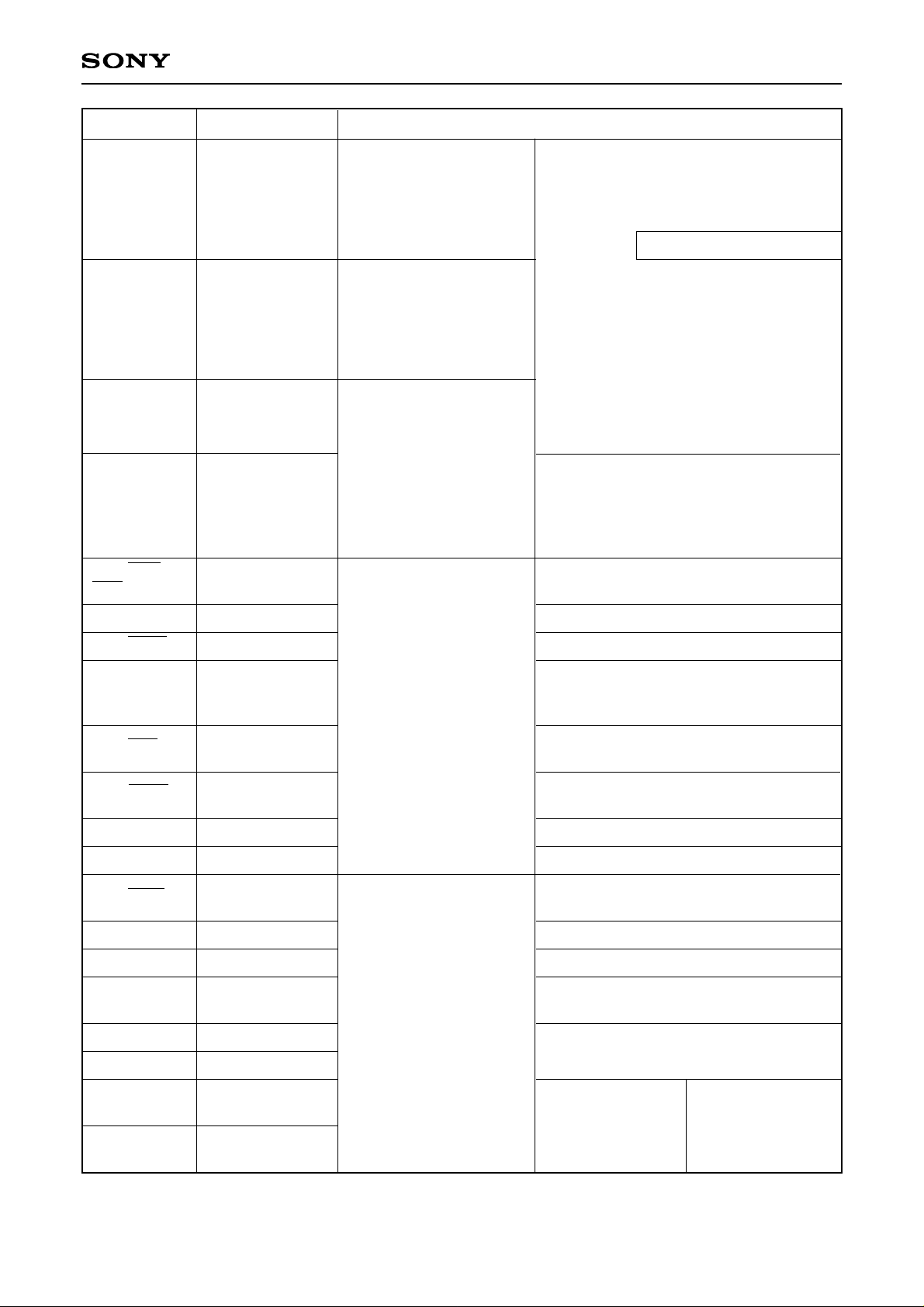

Pin Description

(Port A)

8-bit output port. Data is

gated with PPO contents

by OR-gate and they are

output.

(8 pins)

(Port B)

8-bit output port. Data is

gated with PPO contents

by OR-gate and they are

output.

(8 pins)

(Port C)

8-bit I/O port. I/O can be

set in a unit of single bits.

Data is gated with PPO or

RTO contents by OR-gate

and they are output.

(8 pins)

(Port D)

8-bit I/O port. I/O can be

set in a unit of single bits.

(8 pins)

(Port E)

8-bit port. Bits 2, 3, 4 and 5

are for inputs; bits 0, 1, 6

and 7 are for outputs.

(8 pins)

Programmable pattern generator (PPG)

output. Functions as high precision realtime pulse output port.

(19 pins)

PB0 and PB2 can be tri-state controlled

with PPG.

Real-time pulse generator (RTG) output.

Functions as high precision real-time

pulse output port. PC3 can be tri-state

controlled with RTG.

(5 pins)

Input pin to request external interruption

and non-maskable interruption.

Remote control receiving circuit input pin.

14-bit PWM output pin.

Timer/counter, CTL duty detector, 32kHz

oscillation adjustment and servo amplifier

output pin.

Serial chip select (CH0) input pin.

Serial clock (CH0) I/O pin.

Serial data (CH0) output pin.

Serial data (CH0) input pin.

Serial clock (CH1) I/O pin.

Serial data (CH1) output pin.

Serial data (CH1) input pin.

Composite sync signal input pin.

External input pin for FRC capture unit.

(2 pins)

Symbol I/O Description

PA0/PPO0

to

PA7/PPO7

PB0/PPO8

to

PB7/PPO15

PC0/PPO16

to

PC2/PPO18

PC3/RTO3

to

PC7/RTO7

PD0/INT1/

NMI

PD1/RMC

PD2/PWM

PD3/TO

DDO/ADJ

SRVO

PD4/CS0

PD5/SCK0

PD6/SO0

PD7/SI0

PE0/SCK1

PE1/SO1

PE2/SI1

PE3/SYNC

PE4/EXI0

PE5/EXI1

PE6/PWM0/

DAA0

PE7/PWM1/

DAA1

PWM output pin.

(2 pins)

DA gate pulse

output pin.

(2 pins)

Output/

Real-time output

Output/

Real-time output

I/O/

Real-time output

I/O/

Real-time output

I/O/Input/Input

I/O/Input

I/O/Output

I/O/Output/Output/

Output/Output

I/O/Input

I/O/I/O

I/O/Output

I/O/Input

Output/I/O

Output/Output

Input/Input

Input/Input

Input/Input

Input/Input

Output/Output

Output/Output

Head switching output.

– 5 –

CXP88452/88460

AN0 to AN3

PF0/AN4

to

PF3/AN7

PF4/AN8

to

PF7/AN11

PG0/CFG

PG1/DFG

PG2/DPG

PG3/EC/

INT2

PH0/SCL0

PH1/SCL1

PH2/SDA0

PH3/SDA1

PH4 to PH7

PI0/INT0

PI1 to PI7

RFG0, RFG1

ANOUT

CTLFAMPO

CTLSAMPI

CTLAGND

CTLFAMPI (–)

CTLFAMPI (+)

HEADL (–)

HEADL (+)

CTLHEAD (–)

CTLHEAD (+)

AMPVSS

AMPVDD

Input

Input/Input

Output/Input

Input/Input

Input/Input/Input

I/O/I/O

Output

I/O/Input

I/O

Input

Output

Output

Input

Output

Input

Output

I/O

Description I/O

Description

(Port F)

Lower 4 bits are for inputs; upper 4 bits are for

outputs. Lower 4 bits also serve as standby

release input pins.

(8 pins)

(Port H)

8-bit I/O port. Upper four

bits are for outputs. I/O

can be set in a unit of

single bits for lower four

bits.

Lower four bits are N-ch open drain outputs and which can drive 12mA

sink current.

Upper four bits are for outputs; N-ch open drain output of medium drive

voltage (12V) and large current (12mA).

(8 pins)

Input ports. (2 pins)

Output port. (1 pin)

Output port. (1 pin)

Input port. (1 pin)

Output port. (1 pin)

Input ports. (2 pins)

Output ports. (2 pins)

I/O ports. (2 pins)

Analog signal input circuit GND pin.

Analog signal input circuit power supply pin.

Input pin to request external interruption.

Active when falling edge.

(Port I)

8-bit I/O port. I/O can be

set in a unit of single bits.

Function as standby release input can be set in a unit of single bits.

(8 pins)

Analog input pin to

A/D converter.

(12 pins)

(Port G)

4-bit input port.

(4 pins)

Capstan FG input pin.

Drum FG input pin.

Drum PG input pin.

External event input

pin for

timer/counter.

Serial clock (CH2) I/O pin.

Serial data (CH2) I/O pin.

Input pin to request

external interruption.

Active when falling

edge.

Reel FG input pin.

Internal waveform output pin analog circuit.

PBCTL signal 1st amplifier output.

PBCTL signal 2nd amplifier input.

Smoothing capacitor connecting pin.

Input PBCTL signal with capacitor coupled.

During playback, connect to CTLHEAD (–)

and CTLHEAD (+) with internal signal.

During playback, input pin of PBCTL signal;

during recording, output pin of PBCTL signal.

– 6 –

CXP88452/88460

EXTAL

XTAL

TEX

TX

RST

NC

MP

AVDD

AVREF

AVSS

VDD

VSS

Input

Output

Input

Output

Input

Input

Input

Symbol I/O

Description

Connecting pin of crystal oscillator for system clock. When supplying

the external clock, input it to EXTAL pin and input the opposite phase

clock to XTAL pin.

Connecting pin of crystal oscillator for 32kHz timer clock. When used

as event counter, input to TEX pin and leave TX pin open.

(In this time, feedback resistor is not removed.)

System reset pin; active at low level.

NC pin. Connect this pin to VDD for normal operation.

Test mode input pin. Always connect to GND.

Positive power supply pin of A/D converter.

Reference voltage input pin of A/D converter.

GND pin of A/D converter.

Positive power supply pin.

GND pin. Connect both Vss pins to GND.

– 7 –

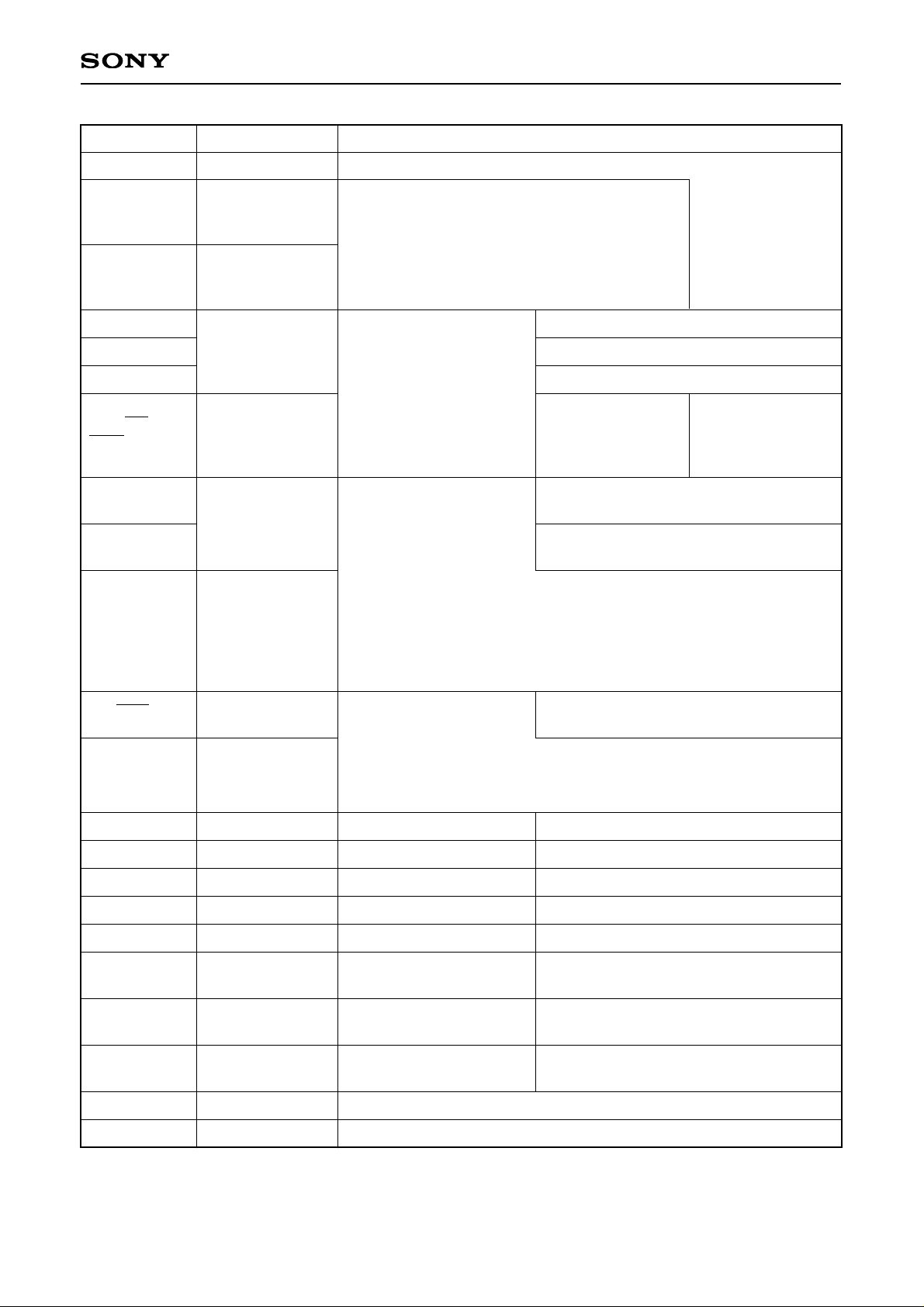

CXP88452/88460

Input/Output Circuit Formats for Pins

Port A

2 pins

2 pins

Hi-Z

Hi-Z

Hi-Z

After a reset

PB0/PPO8

PB2/PPO10

PB1/PPO9

PB3/PPO11

PA0/PPO0

to

PA7/PPO7

PB4/PPO12

to

PB7/PPO15

Port B

12 pins

Port B

Pin

Circuit format

Output becomes active from high

impedance by data writing to port

data register.

PPO9, PPO11 data

PB1, PB3 data

PPO9, PPO11 data

A

PPG control/status

register bit 0

Tri-state control

selection

RD (Port B)

Internal data bus

Output becomes active from high

impedance by data writing to port

data register.

Internal data bus

RD (Port B)

PB0, PB2 data

PPO8, PPO10 data

"0" after a reset

Internal data bus

PPO data

Ports A and B data

RD (Port A or Port B)

Output becomes active from

high impedance by data writing

to port data register.

AA

– 8 –

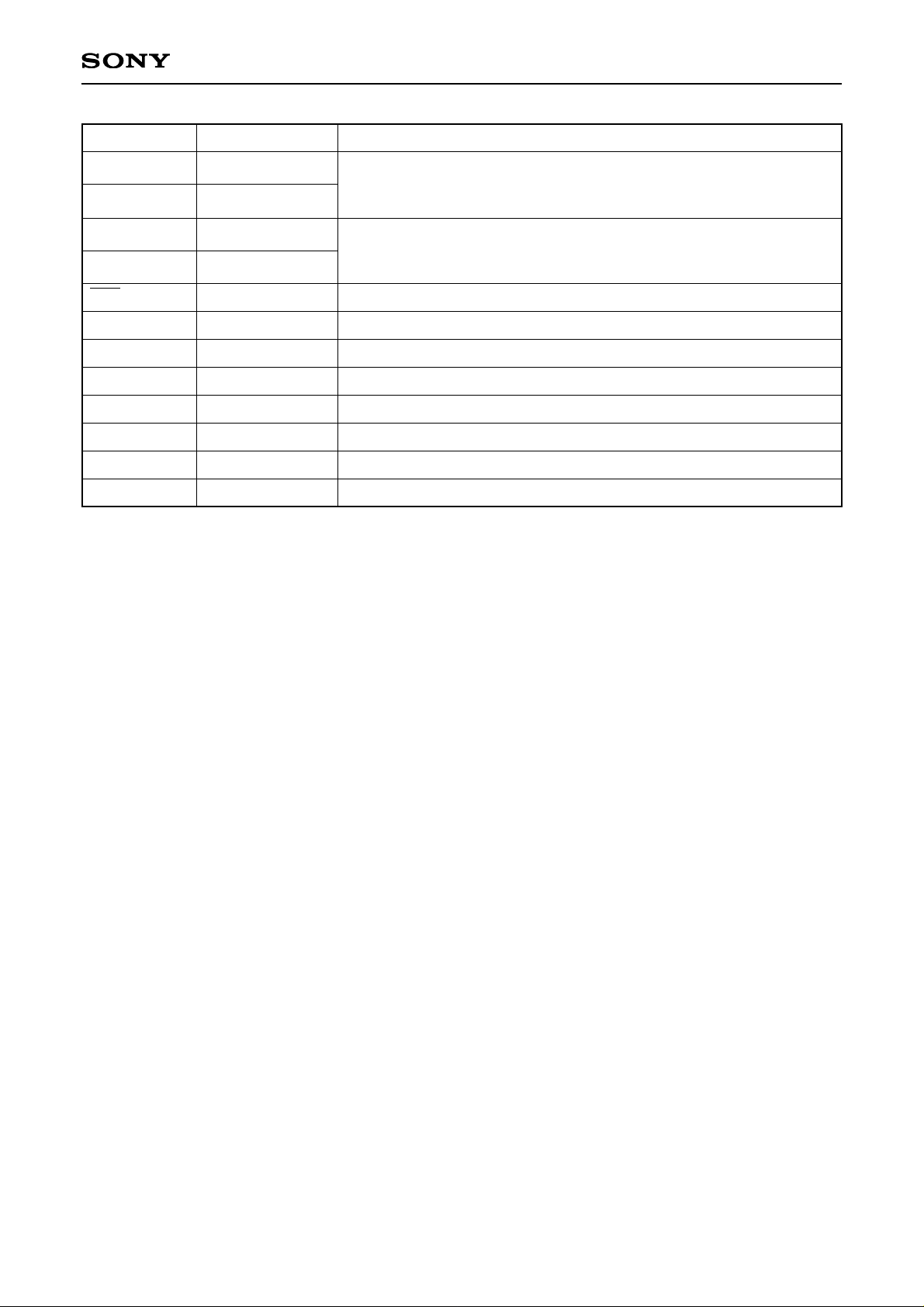

CXP88452/88460

6 pins

After a reset

PC0/PPO16

to

PC2/PPO18

PC5/RTO5

to

PC7/RTO7

Hi-Z

Pin

Circuit format

RTO3 data

Internal data bus

RD (Port C)

PC3 direction

PC3 data

IP

"0" after a reset

RTO4 data

A

RTG interruption

control register bit 7

Tri-state control

selection

RD (Port C)

PC4 direction

PC4 data

IP

RTO4 data

"0" after a reset

Internal data bus

Internal data bus

RD (Port C direction)

Internal data bus

RD (Port C direction)

"0" after a reset

Hi-Z

PC3/RTO3

Hi-Z

PC4/RTO4

1 pin

1 pin

Port C

Port C

Internal data bus

Internal data bus

PPO, RTO data

Port C data

Port C direction

"0" after a reset

RD (Port C)

RD (Port C direction)

Input protection

circuit

IP

AA

– 9 –

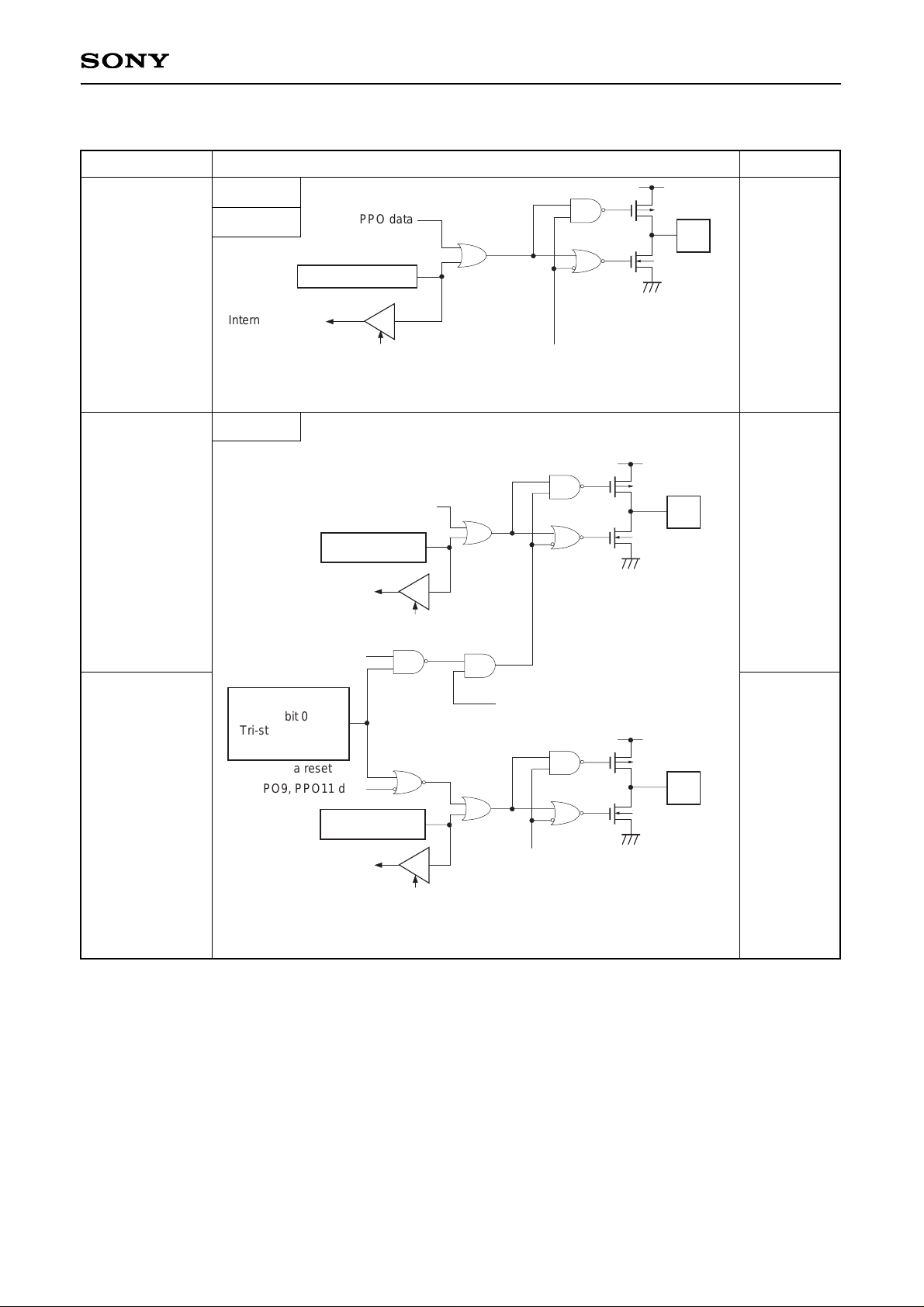

CXP88452/88460

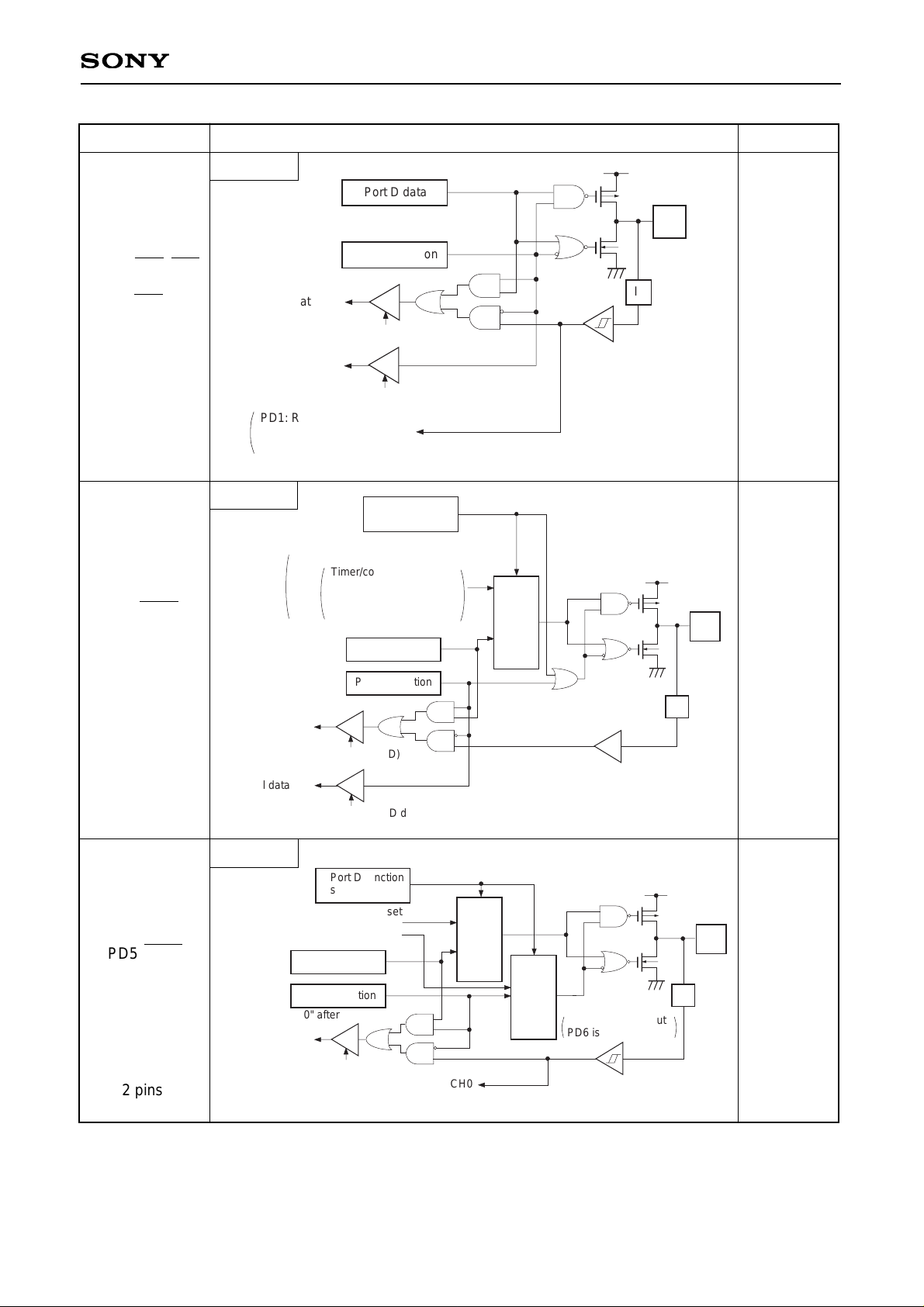

After a reset

Port D

Port D

Pin

Circuit format

Port D data

IP

Internal data bus

RD (Port D)

Port D direction

PD1: Remote control circuit

PD0: Interruption circuit

PD4, PD7: Serial CH0

Schmitt input

Internal data bus

RD (Port D direction)

"0" after a reset

A

A

PD2: 14-bit PWM

Timer/counter,

CTL duty detection circuit,

32kHz timer,

amplifier circuit

MPX

Port D data

IP

Internal data bus

RD (Port D)

Port D direction

Port D function

select

RD (Port D direction)

Internal data bus

PD3:

"0" after a reset

"0" after a reset

Hi-Z

PD0/INT1/NMI

PD1/RMC

PD4/CS0

PD7/SI0

Hi-Z

PD2/PWM

PD3/SRVO/

TO/DDO/

ADJ

4 pins

2 pins

MPX

Port D data

IP

Internal data bus

RD (Port D)

Port D direction

Port D function

select

A

A

MPX

SIO CH0

SIO CH0

Note)

PD5 is schmitt input

PD6 is inverter input

"0" after a reset

"0" after a reset

2 pins

PD5/SCK0

PD6/SO0

Hi-Z

Port D

A

A

A

A

– 10 –

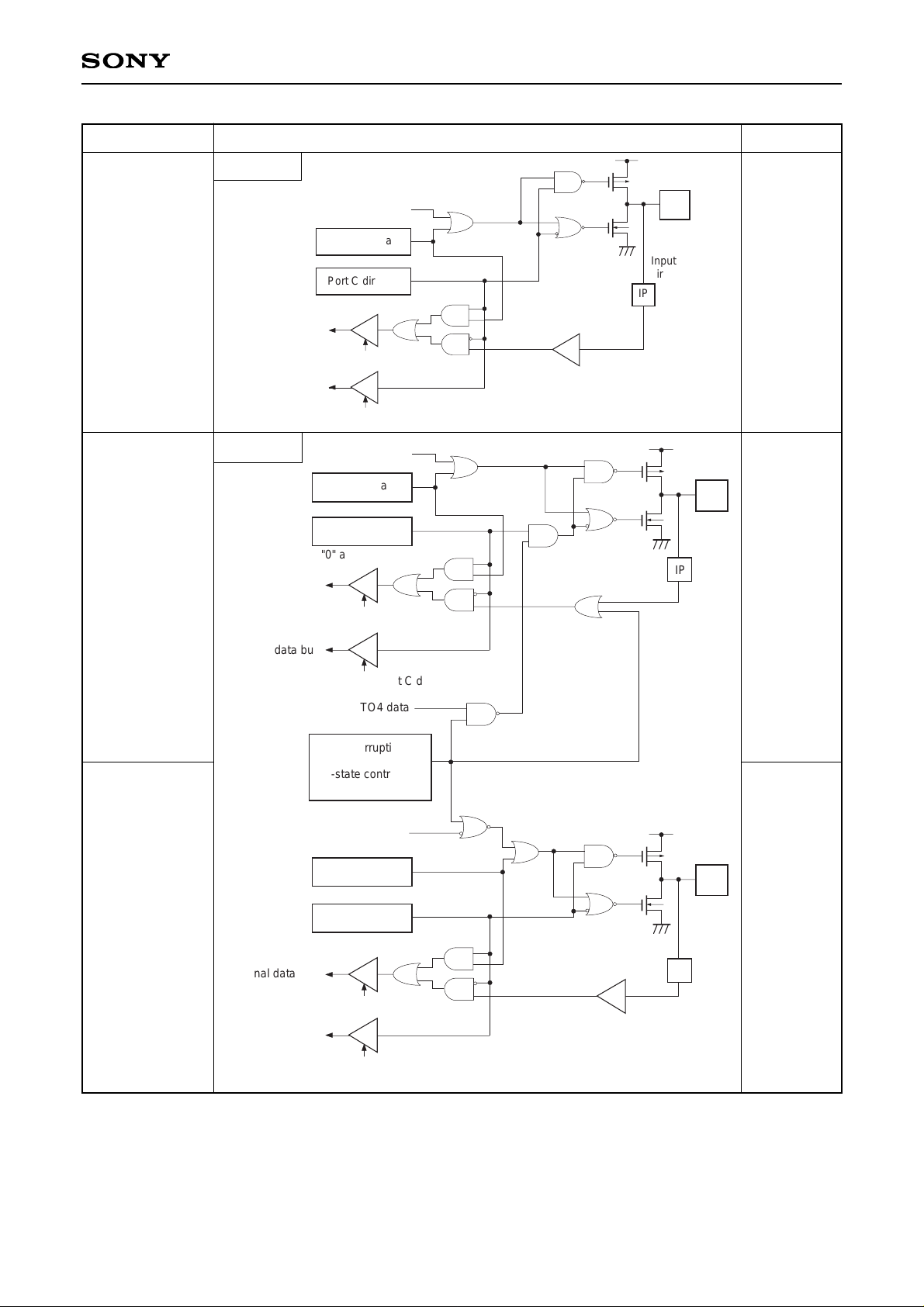

CXP88452/88460

Internal data bus

RD (Port E)

DA gate output or

PWM output

Hi-Z control

MPX

Port E data

Port/DA/PWM

select

"1" after a reset

2 pins

PE6/PWM0/

DAA0

PE7/PWM1/

DAA1

High level

Port E

Internal data bus

RD (Port E)

SIO CH1

Hi-Z control

MPX

Port E data

Port E function

select

"1" after a reset

Internal data bus

RD (Port E)

SIO CH1

Hi-Z control

MPX

Port E data

Port/SCK

output select

IP

SIO CH1

"1" after a reset

Port E

Hi-Z

Hi-Z

Hi-Z

After a reset

PE0/SCK1

Port E

Port E

1 pin

1 pin

4 pins

PE1/SO1

PE2/SI1

PE3/SYNC

PE4/EXI0

PE5/EXI1

Pin

Circuit format

IP

RD (Port E)

Internal data bus

Schmitt input

PE2: SIO CH1

PE3

PE4 : Servo input

PE5

Note) For PE3/SYNC, CMOS schmitt input or TTL schmitt input can be selected

with the mask option.

– 11 –

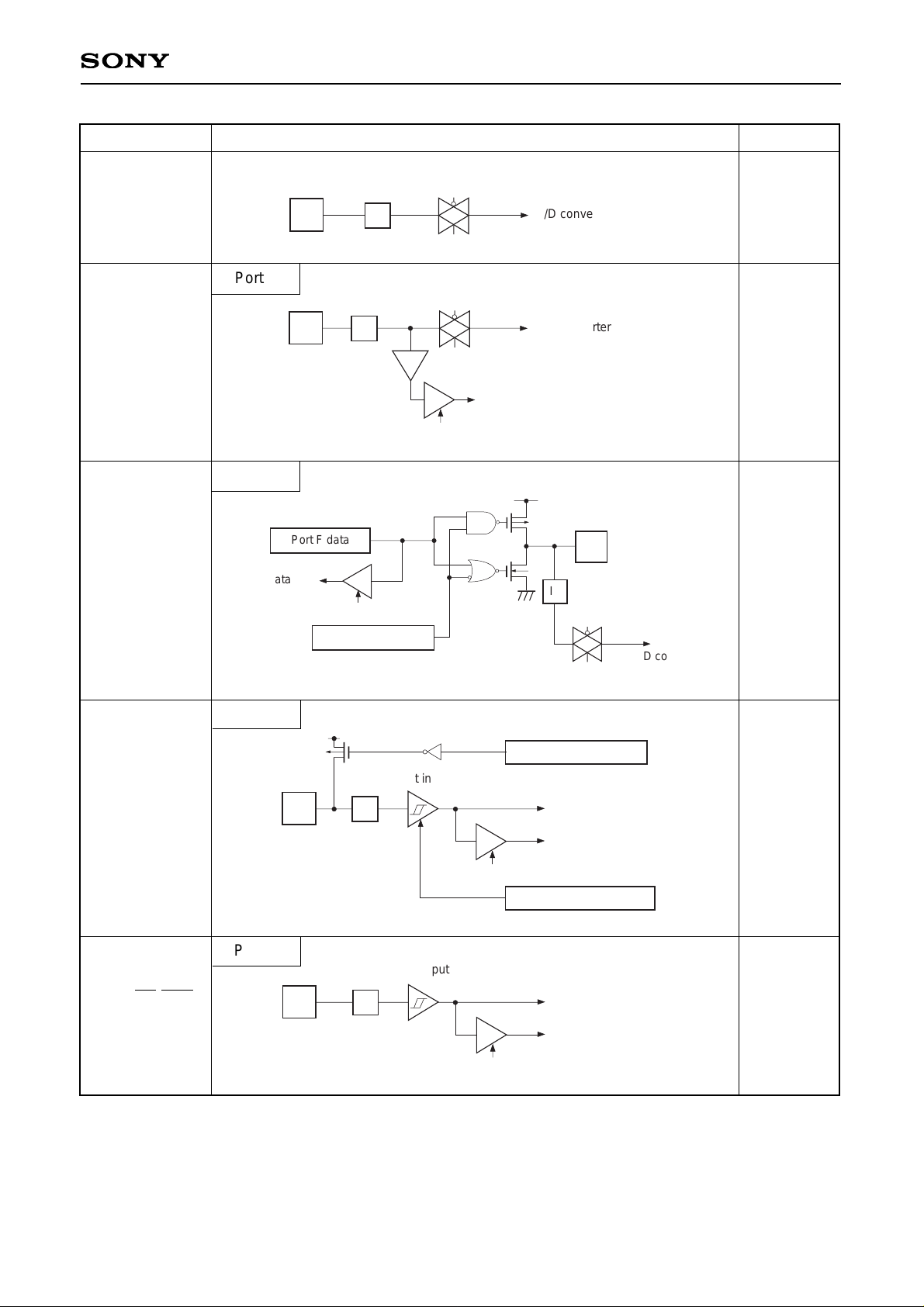

CXP88452/88460

4 pins

Hi-Z

Hi-Z

Hi-Z

After a reset

PF4/AN8

to

PF7/AN11

3 pins

AN0

to

AN3

4 pins

PF0/AN4

to

PF3/AN7

Pin

Circuit format

Port F data

IP

Internal data bus

RD (Port F)

Port/AD select

A/D converter

Input multiplexer

"1" after a reset

IP

Input multiplexer

A/D converter

Port F

RD (Port F)

Internal data bus

IP

Input multiplexer

A/D converter

Port F

Hi-Z

PG0/CFG

PG1/DFG

PG2/DPG

IP

RD (Port G)

Internal data bus

Schmitt input

Servo input

Schmitt width selection

Power ON/OFF control

Port G

3 pins

Hi-Z

PG3/EC/INT2

IP

RD (Port G)

Internal data bus

Schmitt input

Port G

1 pin

Loading...

Loading...