Sony CXL5505P, CXL5505M Datasheet

CMOS-CCD 1H Delay Line for PAL

Description

The CXL5505M/P are CMOS-CCD delay line ICs

that provide 1H delay time for PAL signals including

the external low-pass filter.

Features

• Single 5V power supply

• Low power consumption 100mW (Typ.)

• Built-in peripheral circuits

• Built-in quadruple PLL circuit

Functions

• 1130-bit CCD register

• Clock driver

• Auto-bias circuit

• Input clamp circuit

• Sample-and-hold circuit

• PLL circuit

Structure

CMOS-CCD

Absolute Maximum Ratings (Ta = 25°C)

• Supply voltage VDD 6V

•Operating temperature Topr –10 to +60 °C

• Storage temperature Tstg –55 to +150 °C

• Allowable power dissipation

PD

CXL5505M 400 mW

CXL5505P 800 mW

Recommended Operating Condition (Ta = 25°C)

Supply voltage VDD 5 ± 5% V

Recommended Clock Conditions (Ta = 25°C)

• Input clock amplitude VCLK 0.3 to 1.0 Vp-p

(0.5Vp-p typ.)

• Clock frequency fCLK 4.433619 MHz

• Input clock waveform Sine wave

Input Signal Amplitude

VSIG 575mVp-p (Max.) (at internal clamp condition)

– 1 –

E90731B7X-PS

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

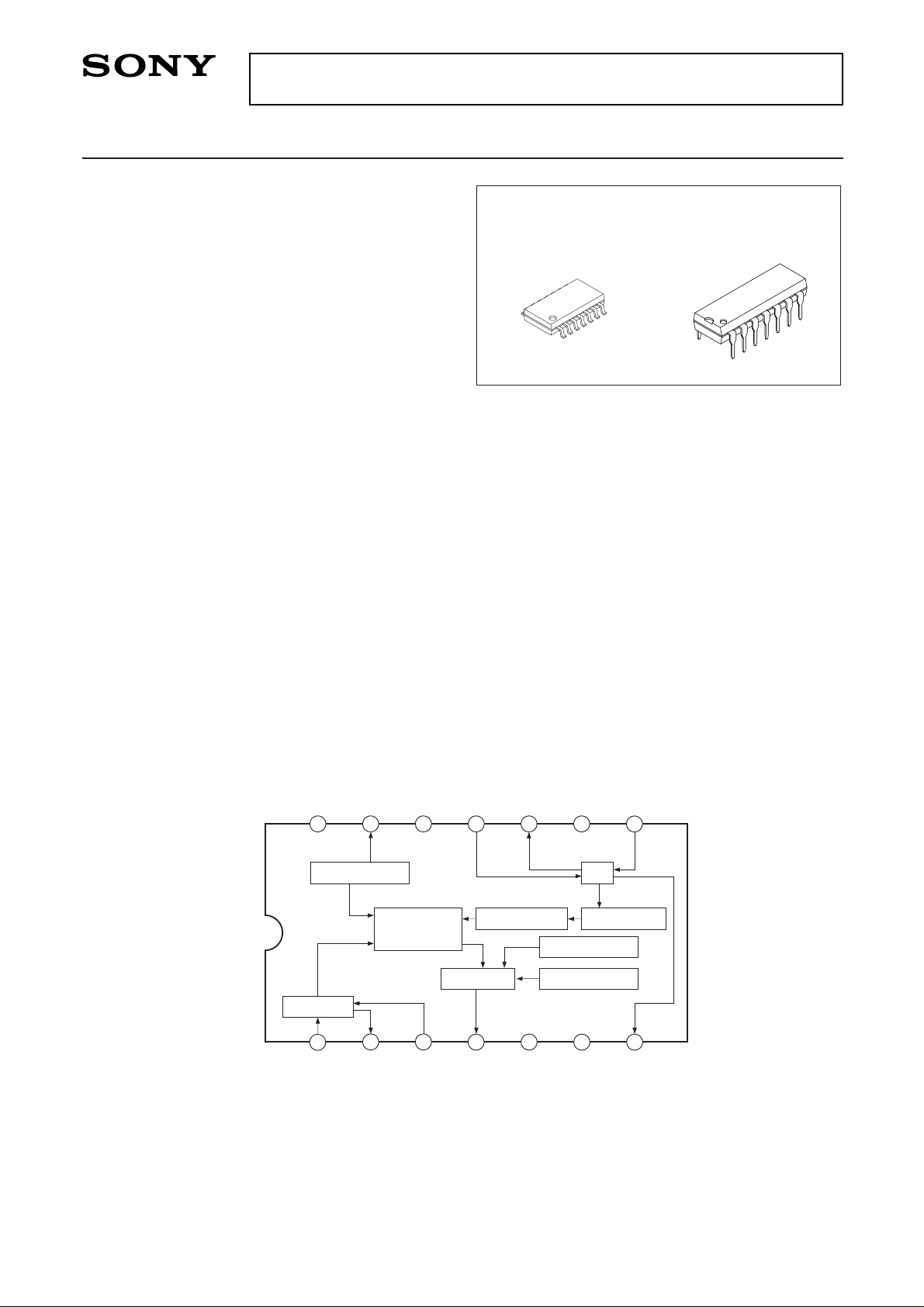

CXL5505M/P

CXL5505M

14 pin SOP (Plastic)

CXL5505P

14 pin DIP (Plastic)

Blook Diagram and Pin Configuration (Top View)

Output circuit

(S/H 1bit)

CLK

1

2

3

4

5

7

8

Auto-bias circuit

Timing circuit

CCD

(1130bit)

Clock driver

Bias circuit (A)

Bias circuit (B)

Clamp circuit

6

VCO IN

V

DD

AB

OUT

VG2

VG1

IN

9

10

11

12

13

14

V

SS

V

SS

VCO OUT

V

SS

V

DD

PC OUT

PLL

– 2 –

CXL5505M/P

∗

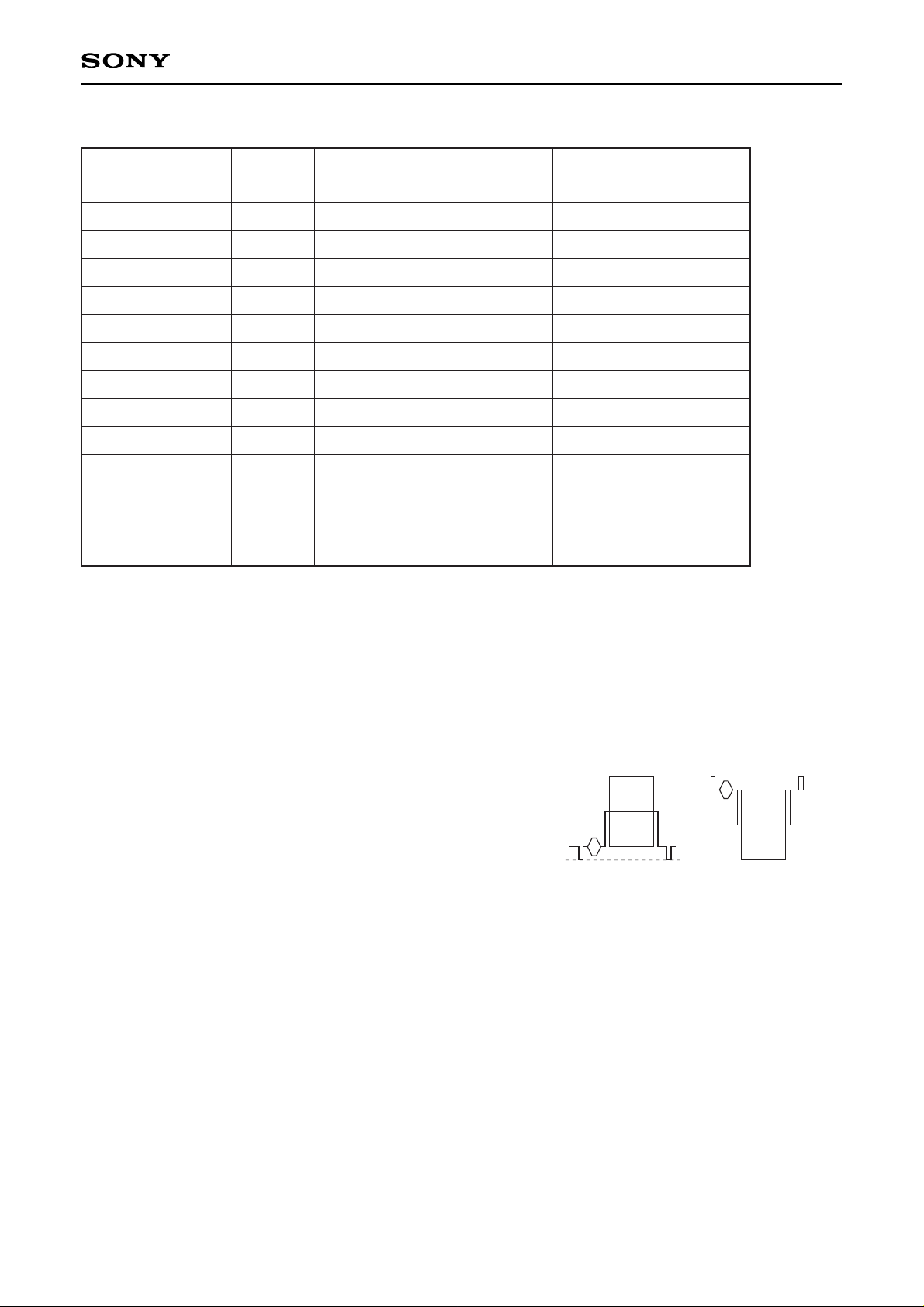

Description of Pin 3 (VG2)

Control of input signal clamp condition

0V ........ Sync tip clamp condition

5V ........ Center bias condition

Center biased to approx. 2.1V by means of the IC internal resistance (approx. 10kΩ).

In this mode, the input signal is limited to APL 50% and the maximum input signal amplitude is

200mVp-p.

Clamp

level

Input waveform Output waveform

Pin Description

Pin No. Symbol Description Impedance

1

2

3

∗

4

5

6

7

8

9

10

11

12

13

14

IN

VG1

VG2

OUT

VSS

VSS

VCO OUT

CLK

VDD

PC OUT

VCO IN

VDD

AB

VSS

Signal input

Gate bias 1 DC output

Gate bias 2 DC input

Signal output

GND

GND

VCO output

Clock input

Power supply (5V)

Phase comparator output

VCO input

Power supply (5V)

Auto-bias DC output

GND (SUB)

> 10kΩ at no clamp

40 to 500Ω

> 10kΩ

600 to 200kΩ

I

O

I

O

—

—

O

I

—

O

I

—

O

—

I/O

– 3 –

CXL5505M/P

Electrical Characteristics

(Ta = 25°C, VDD = 5V, fCLK = 4.433619MHz, VCLK = 500mVp-p, sine wave)

See "Electrical Characteristics Test Circuit"

Notes

(1) This is the IC supply current value during clock and signal input.

(2) GL is the output gain of OUT pin when a 500mVp-p, 200kHz sine wave is fed to IN pin.

GL = 20 log [dB]

(3) Indicates the dissipation at 4.43MHz in relation to 200kHz.

From the output voltage at OUT pin when a 150mVp-p, 200kHz sine wave is fed to IN pin, and from the

output voltage at OUT pin when a 150mVp-p, 4.43MHz sine wave is fed to same, calculation is made

according to the following formula.

fR = 20 log [dB]

←→

a

a

b

c

d

d

f

e

11

–2

–2

0

0

—

52

20

0

–1

3

3

—

56

29

2

0

5

5

350

—

mA

dB

dB

%

degree

mVp-p

dB

1

2

3

4

4

5

6

Unit

Note

Max.Min. Typ.

Item Symbol Test condition

SW condition

1

a

a

b

a

a

b

a

2

—

b

b

c

c

a

d

3

—

200kHz,

500mVp-p,

sine wave

200kHz ←→ 4.43MHz,

150mVp-p,

sine wave

5-staircase wave

(See Note 4)

5-staircase wave

(See Note 4)

No signal input

50% white

video signal

(See Note 6)

IDD

GL

fR

DG

DP

CP

SN

Supply current

Low frequency gain

Frequency response

Differential gain

Differential phase

S/H pulse coupling

S/N ratio

OUT pin output voltage [mVp-p]

500 [mVp-p]

OUT pin otuput voltage (4.43MHz) [mVp-p]

OUT pin output voltage (200kHz) [mVp-p]

Loading...

Loading...