Sony CXG1010N Datasheet

Power Amplifier for PHS

For the availability of this product, please contact the sales office.

Description

The CXG1010N is a power amplifier for PHS. This

IC is designed using the Sony’s GaAs J-FET process

and operates at a single power supply.

Features

• High output power 21.5 dBm

• Positive power supply drive VDD=3.4 V

• Low current consumption 200 mA

• High gain 40 dB Typ.

• Low distortion (ACP) –59 dBc Typ.

• Small mold package 16-pin SSOP

Structure

GaAs J-FET MMIC

CXG1010N

16 pin SSOP (Plastic)

Absolute Maximum Ratings (Ta=25 °C)

• Supply voltage VDD 6V

•Voltage between gate and source

Vgs0 1.5 V

• Drain current IDD 500 mA

• Power dissipation PD 3W

•Channel temperature Tch 175 °C

• Operating temperature Top –35 to +85 °C

• Storage temperature Tstg –65 to +150 °C

Electrical Characteristics

VDD=3.4 V, VCTL=2.0 V, f=1.90 GHz (Ta=25 °C)

Item Symbol Min. Typ. Max. Unit

∗1

Current consumption

∗1

Gate voltage adjustment value

Input VSWR

Output power (for –15.5 dBm input)

∗2

Power gain

∗2

Gain control

∗3

∗2

Average leak power level

(600 kHz±100 kHz)

∗

2

Average leak power level

(900 kHz±100 kHz)

∗1This value is adjusted by VGG1 and VGG2 set with Sony’s recommended current adjustment method when

21.5 dBm is output. In this time, the voltage ratio of VGG1 and VGG2 should match to the voltage ratio

generated by the resistance of the recommended gate bias circuit.

∗2When 21.5 dBm is output.

∗3GCTL=GP (VCTL 2.0 V)–GP (VCTL 0 V)

IDD 200 mA

VGG2 0 0.5 1.0 V

VSWRIN 1.5 2.0 —

POUT 21.5 dBm

GP 37 40 43 dB

GCTL 20 dB

PLEAK600 –59 –54 dBc

PLEAK900 –65 –59 dBc

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

—1—

E95836-TE

CXG1010N

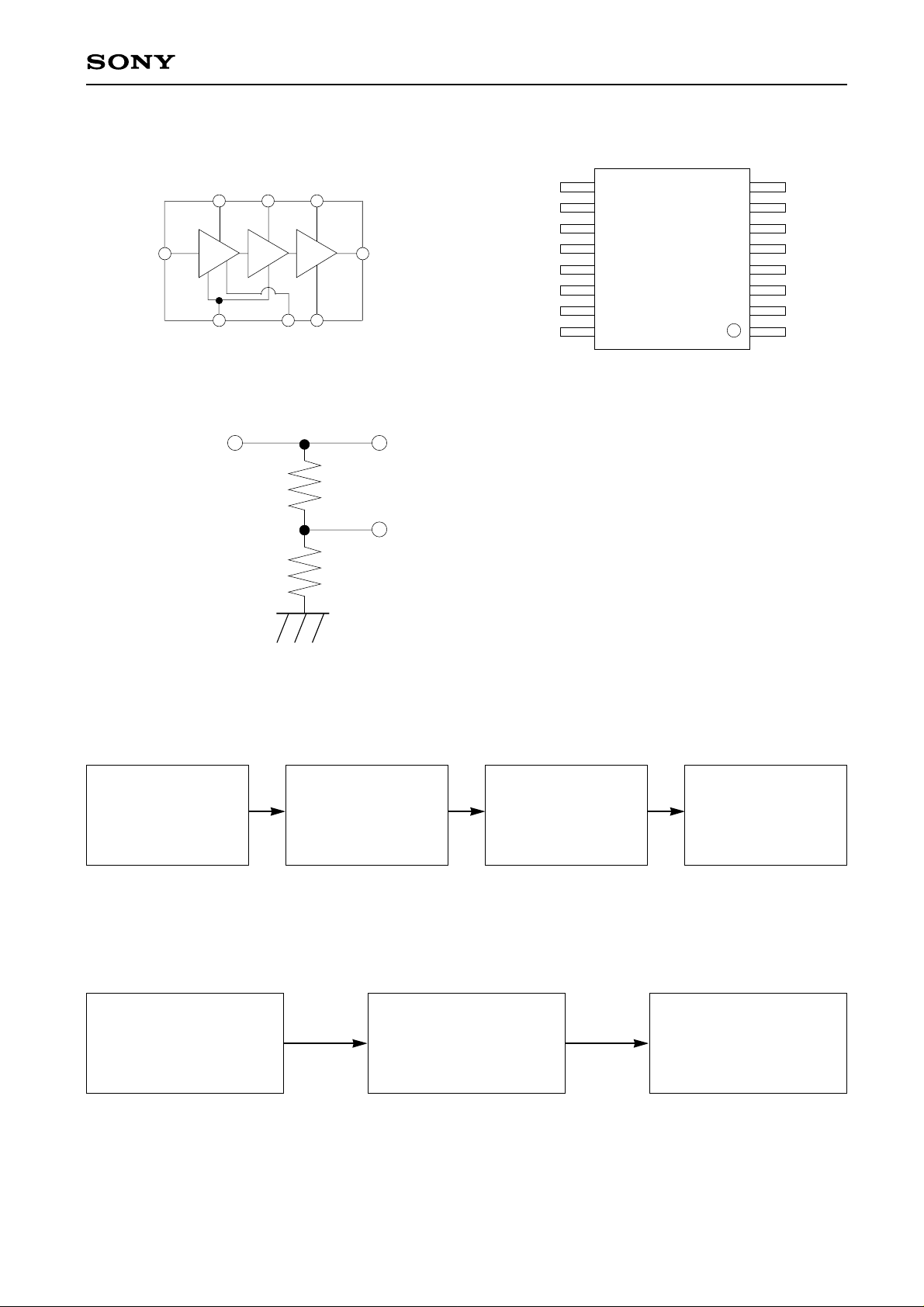

Block Diagram

VDD1VDD2VDD3

RFIN

VGG1VCTL VGG2

Gate adjustment pin

Gate adjustment pin

470Ω

680Ω

RF

OUT

V

V

GG2

GG1

Pin Configuration

GND

RF

OUT

GND

V

GG2

GND

VCTL

VGG1

GND

16

DD3

V

GND

DD2

V

GND

DD1

V

GND

IN

RF

GND

1

Recommended Current Adjustment Method

(1) VGG2/PIN separate adjustment

(VGG2 adjustment 1) (PIN adjustment 1) (VGG2 adjustment 2) (PIN adjustment 2)

When the RF input

(PIN) is off, the current

consumption (IDD) is

adjusted to 200 mA.

Variation of IDD and

POUT due to adjustment

The output power

(POUT) is adjusted

to 21.5 dBm.

IDD=200±20 mA

POUT=21.5 dBm

The current

consumption (IDD)

is finely adjusted to

200 mA.

IDD=200 mA

POUT=21.5±0.2 dBm

The output power

(POUT) is finely

adjusted to 21.5 dBm.

IDD=200±5 mA

POUT=21.5 dBm

(2) Simple adjustment

(IDD read) (VGG2 setting) (PIN adjustment)

When the RF input (PIN)

is off, the gate voltage

(VGG2) is set to 0.4 V

and it is read.

Variation of IDD and POUT

due to adjustment

The formula∗1where

VGG2=f (IDD: VGG2=0.4 V)

is used to set VGG2.

∗

1

e.g. VGG2=a-b x IDD IDD=200±5 mA

The output power (POUT)

is adjusted to 21.5 dBm.

POUT=21.5 dBm

—2—

Loading...

Loading...