Sony CXD3526GG Datasheet

Digital Signal Driver/Timing Generator

Description

The CXD3526GG incorporates digital signal

processor type RGB driver, color shading correction and

timing generator functions onto a single IC. Operation is

possible with a system clock up to 85 [MHz] (max.). This

IC can process video signals in bands up to XGA

standard, and can output the timing signals for driving

various Sony LCD panels such as XGA and SVGA.

CXD3526GG

144 pin BGA (Plastic)

Features

• Various picture quality adjustment functions such

as user adjustment, white balance adjustment and

gamma correction

• OSD MIX, black frame processing, mute and

limiter functions

• LCD panel color shading correction function

• Drives various Sony data projector LCD panels

such as XGA and SVGA

• Controls the CXA3562AR and CXA7000R sample-

and-hold drivers

• Line inversion and field inversion signal generation

• Supports AC drive of LCD panels during no signal

• On-chip serial interface

• The data of gamma correction and color shading

correction can be downloaded automatically from

the external EEPROM.

Applications

LCD projectors and other video equipment

Absolute Maximum Ratings (VSS = 0V)

• Supply voltage VDD1 VSS – 0.5 to +3.0 V

VDD2 VSS – 0.5 to +4.0 V

• Input voltage VI VSS – 0.5 to VDD2 + 0.5 V

• Output voltage VO VSS – 0.5 to VDD2 + 0.5 V

• Storage temperature

Tstg –55 to +125 °C

• Junction temperature

Tj 125 °C

Recommended Operating Conditions

• Supply voltage VDD1 2.3 to 2.7 V

VDD2 3.0 to 3.6 V

• Operating temperature

Topr –20 to +75 °C

Structure

Silicon gate CMOS IC

Note) Company names and product names indicated on this data sheet are the trademark or registered trademark of each company.

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

– 1 –

E01X09A26

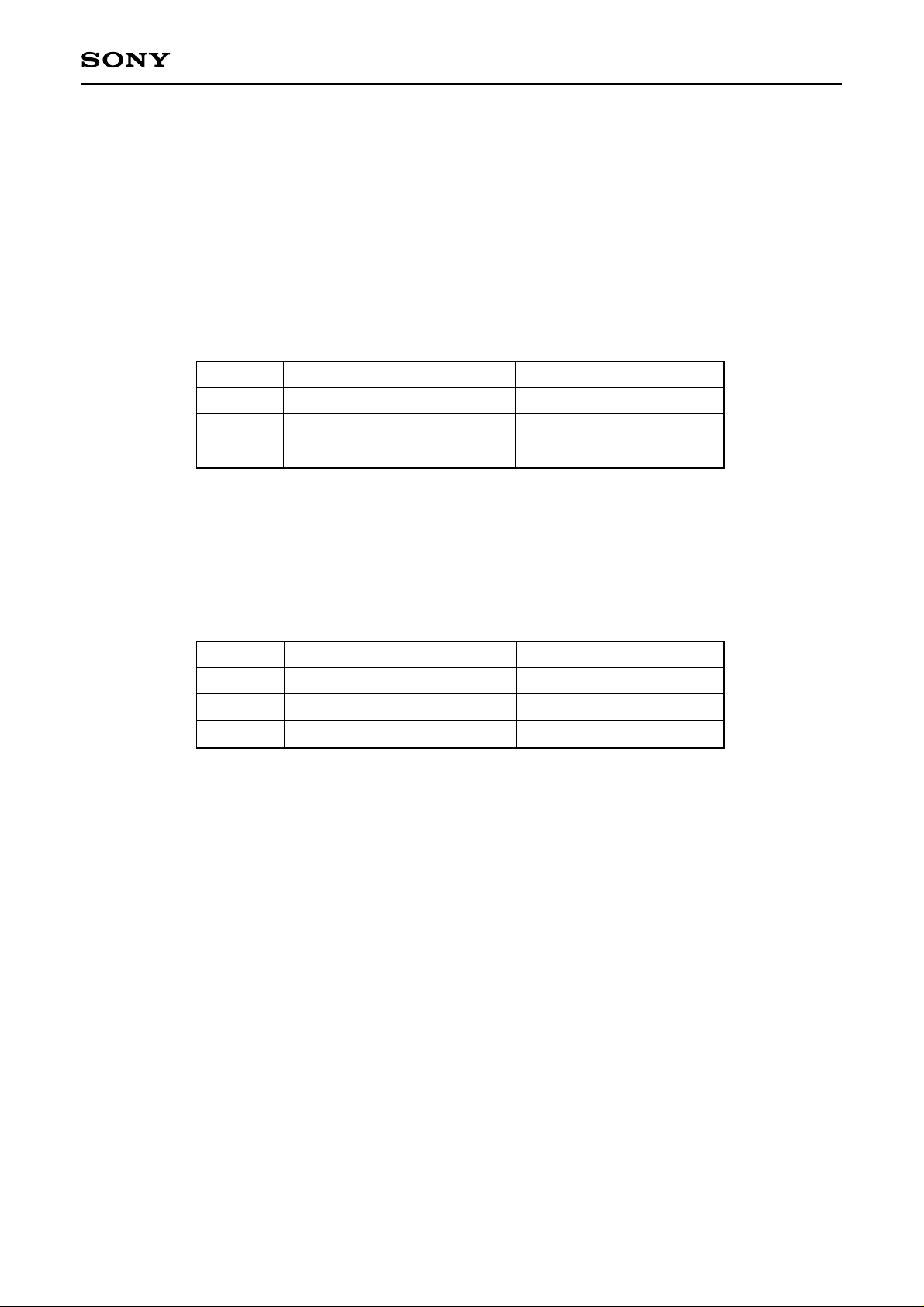

Block Diagram

CXD3526GG

EEPROM

Host

Controller

HSEL

HSCL

HSDA

R, G, BIN

R, G, BOSD

YM

YS

HDIN

VDIN

CLKC

CLKP

CLKN

CLKSEL

CLKPOL

PLLDIV

RSCL

External ROM I/F

Host I/F

10 × 3

2 × 3

RSDA

Register I/F

PLL

DSD

TG

10 × 3

Direct Clear

CLKOUT

R, G, BOUT

CTRL

RGT, DWN

HST, PST, HCK1, HCK2,

DCK1, DCK2, ENB, PCG,

PRG, SHST, HD2, HD3,

CLR, CLP, HD1, VST,

VCK, FRP, XFRP, XRGT,

PO1, PO2

XCLR1

XCLR2

XCLR3

– 2 –

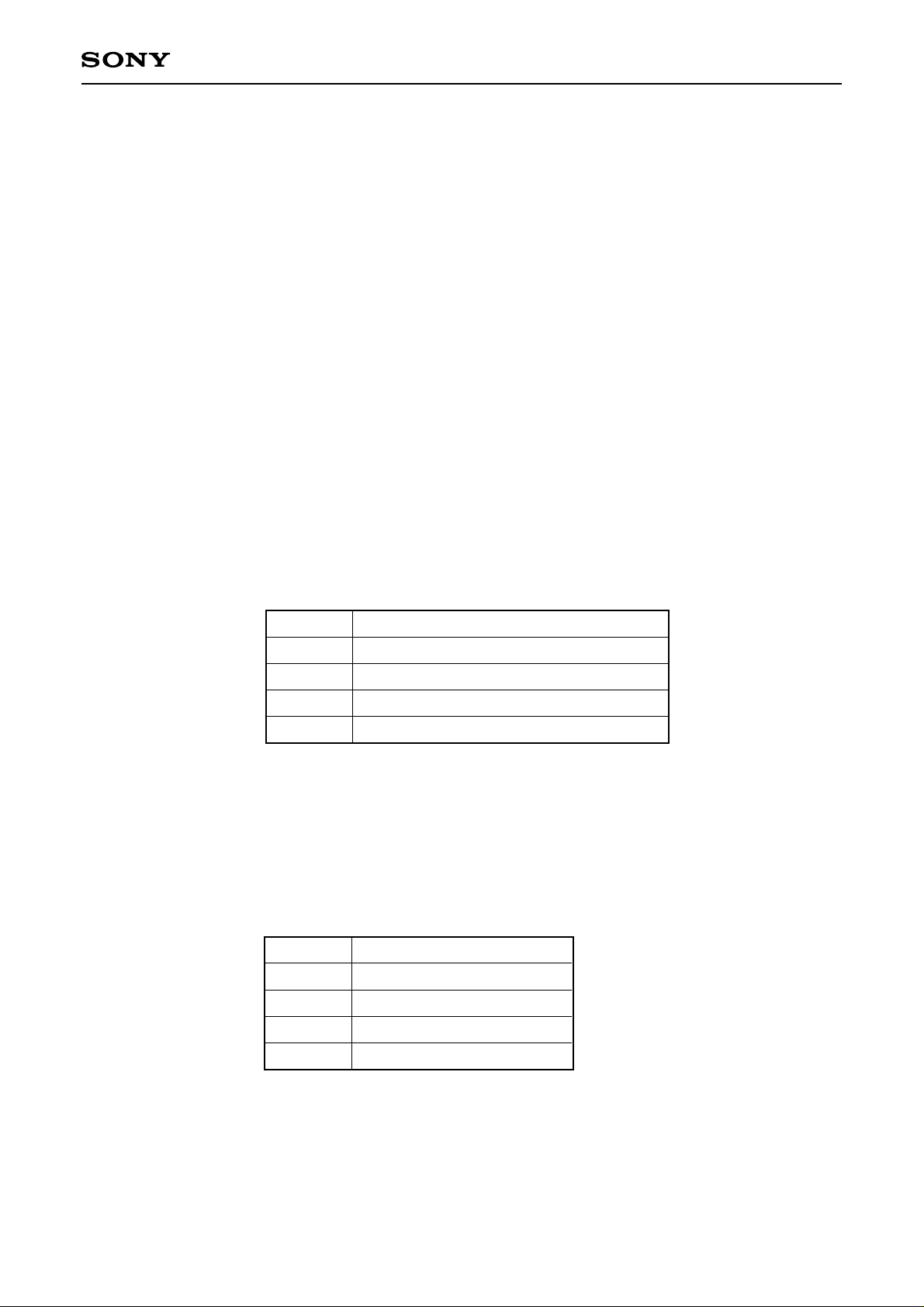

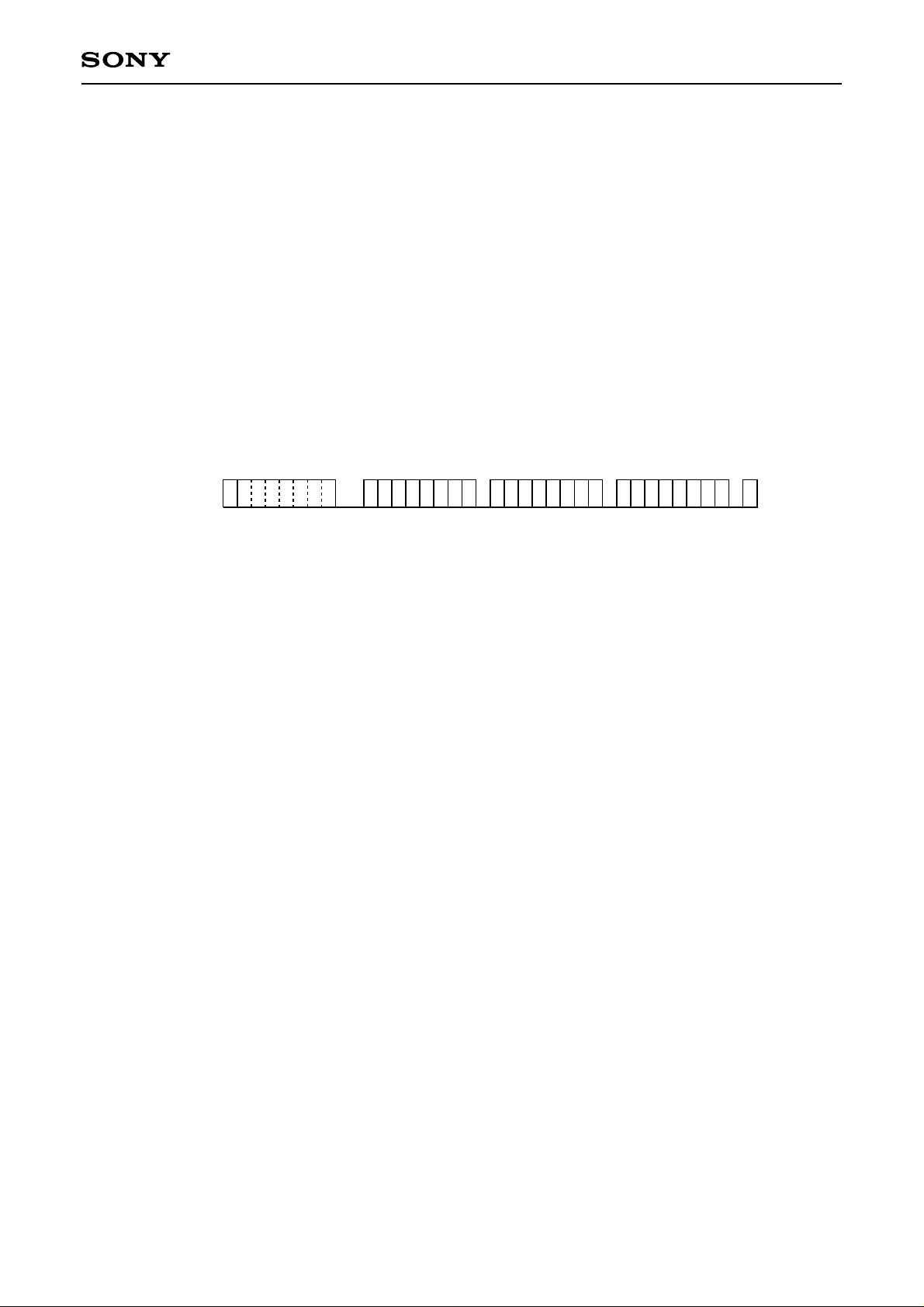

Pin Configuration

CXD3526GG

Index

12345678910111213

A

B

C

D

E

F

G

H

J

K

L

M

N 141516171819202122232425

1 484746454443424140393837

2 498887868584838281807936

3 50 89 120 119 118 117 116 115 114 113 78 35

4 51 90 121 144 143 142 141 140 139 112 77 34

5 52 91 122 138 111 76 33

6 53 92 123 137 110 75 32

7 54 93 124 136(T op Vie w) 109 74 31

8 55 94 125 135 108 73 30

9 56 95 126 134 107 72 29

10 57 96 127 128 129 130 131 132 133 106 71 28

11 58 97 98 99 100 101 102 103 104 105 70 27

12 59 60 61 62 63 64 65 66 67 68 69 26

13

– 3 –

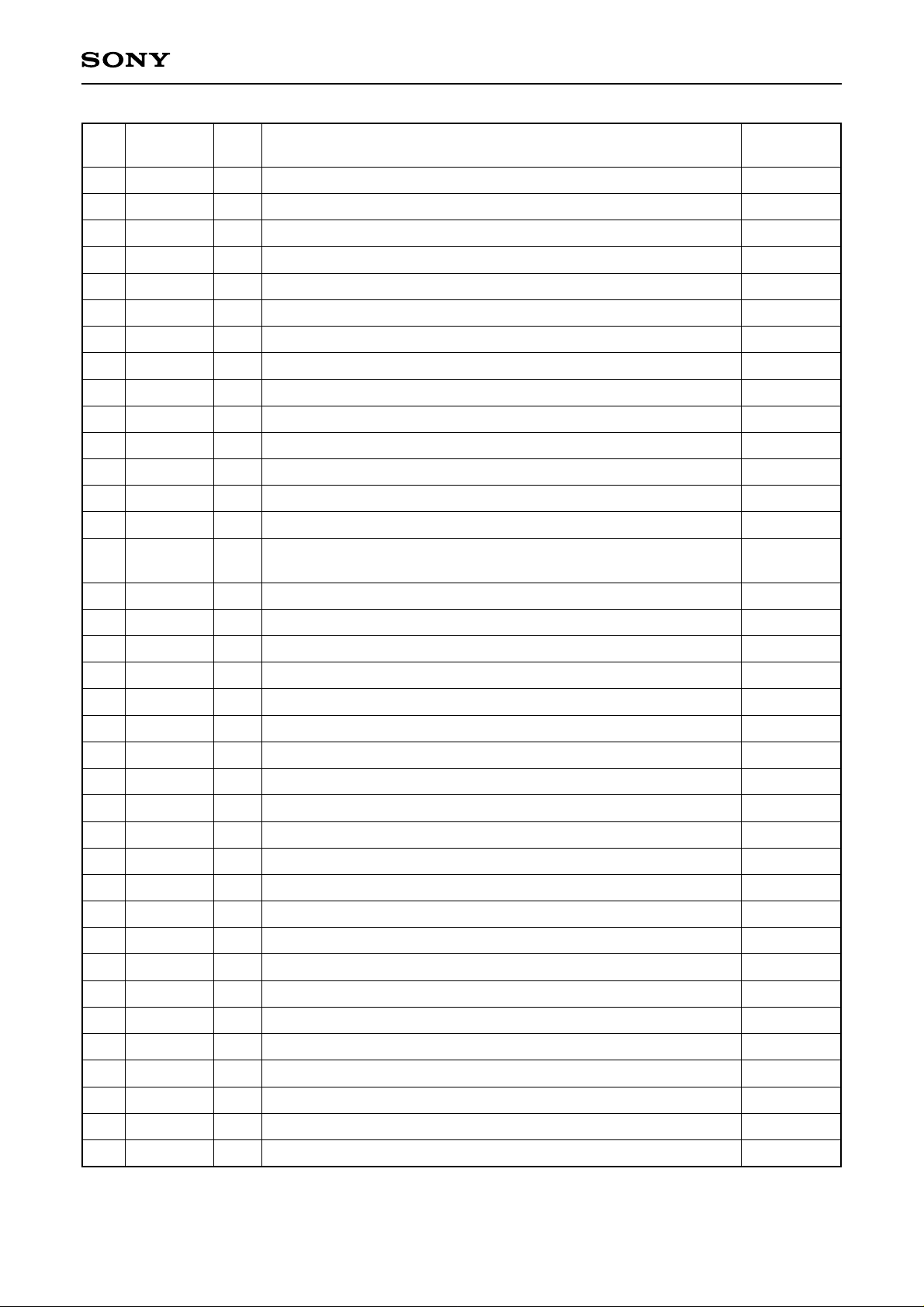

Pin Description

Pin

No.

Symbol

1

VSS

RGT

2

I/O

—

GND

I/O

Horizontal scan direction switching signal I/O

Description

CXD3526GG

Input pin

processing for

open status

—

—

10

11

12

13

14

15

16

17

18

19

3

4

5

6

7

8

9

XRGT

RIN5

RIN2

RIN0

GIN4

GIN0

BIN7

BIN4

BIN1

BIN0

V

SS

ROSD0

GOSD0

BOSD0

VDIN

TEST1

VSS

Horizontal scan direction switching signal output

O

(reversed polarity of RGT)

I

Red data input

I

Red data input

I

Red data input

I

Green data input

I

Green data input

I

Blue data input

I

Blue data input

I

Blue data input

I

Blue data input

—

GND

I

OSD red data input

I

OSD green data input

I

OSD blue data input

I

Vertical sync signal input

—

Test pin (Connect to GND.)

—

GND

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

VDD1

VSS

HSEL

RSCL

TEST2

VSS

TEST3

TEST4

CLKOUT

BOUT3

VDD2

VSS

GOUT3

GOUT6

GOUT9

ROUT2

ROUT6

—

Internal operation power supply

—

GND

I

Serial bus slave address selection signal input

I/O

Serial bus clock I/O (external ROM I/F)

—

Test pin (Connect to VDD2.)

—

GND

—

Test pin (Connect to VDD2.)

—

Test pin (Connect to VDD2.)

O

Internal clock output (inverted output)

O

Blue data output

—

I/O power supply

—

GND

O

Green data output

O

Green data output

O

Green data output

O

Red data output

O

Red data output

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

– 4 –

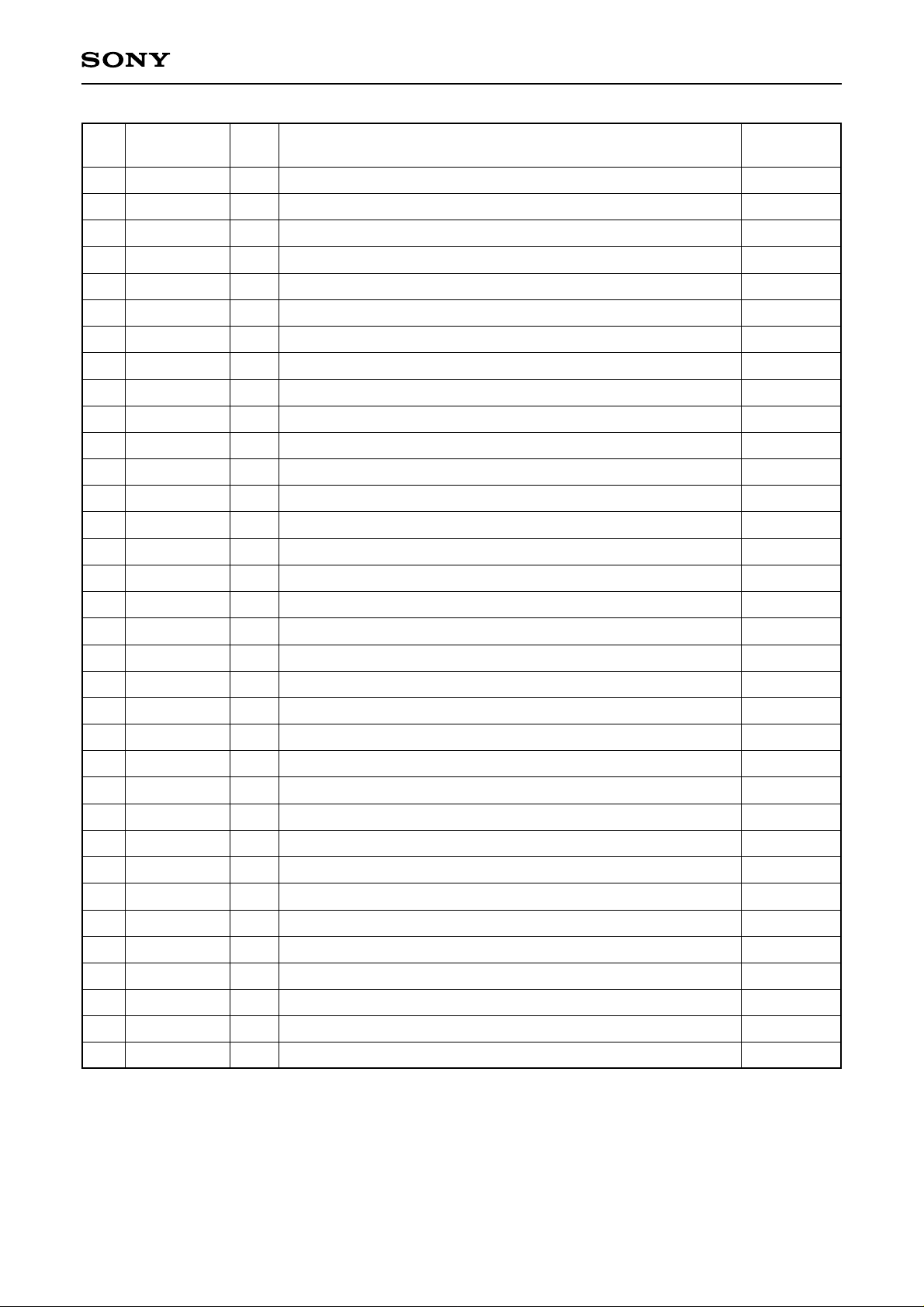

CXD3526GG

Pin

No.

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

Symbol

VSS

ROUT9

ROUT8

ROUT7

VST

HD2

HD3

VDD2

PRG

ENB

PO1

PO2

DWN

RIN8

RIN6

RIN3

I/O

—

GND

O

Red data output

O

Red data output

O

Red data output

O

Vertical display start timing pulse output

O

Horizontal auxiliary pulse output 2

O

Horizontal auxiliary pulse output 3

—

I/O power supply

O

2-step precharge timing pulse output

O

Gate enable pulse output

O

Parallel output 1

O

Parallel output 2

I/O

Vertical scan direction switching signal I/O

I

Red data input

I

Red data input

I

Red data input

Description

Input pin

processing for

open status

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

RIN1

GIN5

GIN1

BIN8

BIN5

BIN2

ROSD1

GOSD1

BOSD1

HDIN

CLKPOL

VSS

TEST5

XCLR2

TEST6

HSCL

RSDA

I

Red data input

I

Green data input

I

Green data input

I

Blue data input

I

Blue data input

I

Blue data input

I

OSD red data input

I

OSD green data input

I

OSD blue data input

I

Horizontal sync signal input

I

Internal clock polarity selection (High: inverted; Low: non-inverted)

—

GND

—

Test pin (Connect to VDD2.)

I

External clear (Low: reset)

—

Test pin (Connect to GND.)

I

Serial bus clock (host I/F)

I/O

Serial bus data I/O (external ROM I/F)

—

—

—

—

—

—

—

—

—

—

L

—

—

H

—

—

—

70

71

72

73

HSDA

VSS

BOUT2

BOUT6

I/O

Serial bus data I/O (host I/F)

—

GND

O

Blue data output

O

Blue data output

—

—

—

—

– 5 –

CXD3526GG

Pin

No.

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

Symbol

BOUT9

GOUT2

GOUT5

GOUT8

ROUT1

ROUT5

ROUT4

ROUT3

VCK

HD1

PCG

VSS

CLR

DCK1

CTRL

I/O

O

Blue data output

O

Green data output

O

Green data output

O

Green data output

O

Red data output

O

Red data output

O

Red data output

O

Red data output

O

Vertical display transfer clock output

O

Horizontal auxiliary pulse output 1

O

Collective precharge timing pulse output

—

GND

O

CLR pulse output

O

DCK1 pulse output

Scan direction control method switching

I

(Low: internal register ; High: external)

Description

Input pin

processing for

open status

—

—

—

—

—

—

—

—

—

—

—

—

—

—

L

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

105

RIN9

RIN7

RIN4

GIN8

GIN6

GIN2

BIN9

BIN6

BIN3

YM

YS

CLKSEL

CLKP

XCLR1

XCLR3

TEST7

VSS

I

Red data input

I

Red data input

I

Red data input

I

Green data input

I

Green data input

I

Green data input

I

Blue data input

I

Blue data input

I

Blue data input

I

OSD YM input

I

OSD YS input

I

Input clock selection (High: CLKC; Low: CLKP/N)

I

Clock input (small-amplitude differential input, positive polarity)

I

External clear (Low: reset)

I

External clear (Low: reset)

—

Test pin (Connect to GND.)

—

GND

—

—

—

—

—

—

—

—

—

L

L

L

—

H

H

—

—

106

107

108

109

110

BOUT0

BOUT1

BOUT5

BOUT8

GOUT1

O

Blue data output

O

Blue data output

O

Blue data output

O

Blue data output

O

Green data output

—

—

—

—

—

– 6 –

CXD3526GG

Pin

No.

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

Symbol

GOUT4

GOUT7

ROUT0

VDD2

CLP

HST

HCK1

FRP

SHST

DCK2

VSS

VDD1

GIN9

GIN7

GIN3

VDD2

I/O

O

Green data output

O

Green data output

O

Red data input

—

I/O power supply

O

CLP pulse output

O

Horizontal display start timing pulse output

O

Horizontal display transfer clock output 1

O

AC drive inversion timing pulse output

O

SHST pulse output

O

DCK2 pulse output

—

GND

—

Internal operation power supply

I

Green data input

I

Green data input

I

Green data input

—

I/O power supply

Description

Input pin

processing for

open status

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

127

128

129

130

131

132

133

134

135

136

137

138

139

140

141

142

143

Vss

VDD1

PLLDIV

CLKN

CLKC

VDD2

VSS

VDD1

BOUT4

BOUT7

GOUT0

VDD2

VSS

VDD1

PST

HCK2

XFRP

—

GND

—

Internal operation power supply

I

Internal PLL setting (High: 55MHz or less; Low: 55MHz or more)

I

Clock input (small-amplitude differential input, negative polarity)

I

Clock input (CMOS input)

—

I/O power supply

—

GND

—

Internal operation power supply

O

Blue data output

O

Blue data output

O

Green data output

—

I/O power supply

—

GND

—

Internal operation power supply

O

Dot sequential precharge start timing pulse output

O

Horizontal display transfer clock output 2

O

AC drive inversion timing pulse output (reversed polar ity of FRP)

—

—

L

—

—

—

—

—

—

—

—

—

—

—

—

—

—

144

VDD2

—

I/O power supply

—

– 7 –

CXD3526GG

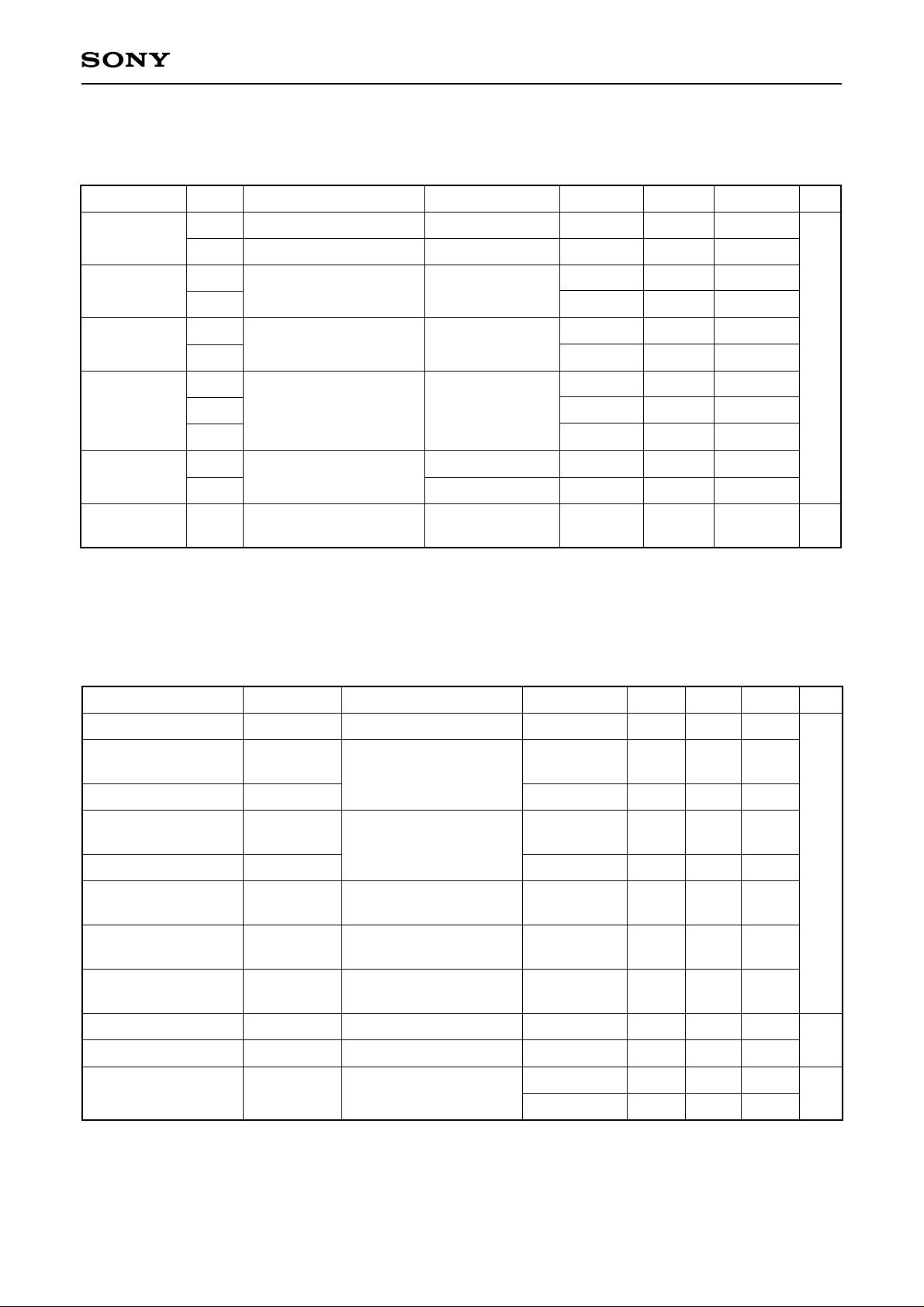

Electrical Characteristics

DC Characteristics (Topr = –20 to +75°C, VSS = 0V)

Item Symbol Applicable pins Conditions Min. Typ. Max.

Supply

voltage

Input

voltage 1

Input

voltage 2

Input

voltage 3

VDD1

VDD2

VIH1

VIL1

VIH2

VIL2

VC

VIH3

1

∗

HDIN, VDIN, HSCL

2

∗

CLKP, CLKN

VIL3

Output

voltage

Power

consumption

1

∗

Input pins other than those indicated in items Input voltage 2 and Input voltage 3.

2

∗

VIH3 > VC (max.) and VIL3 < VC (min.).

3

∗

Tj [°C] ≥ Toprmax [°C] + θja [°C/W] × PD [W].

VOH

VOL

PD

All output pins

3

∗

—

—

—

—

—

CMOS input cell

CMOS Schmitt

trigger input cell

Small-amplitude

differential input

—

—

CLKP = 85MHz

2.3

3.0

2.0

–0.3

0.8VDD2

–0.3

1.718

1.868

VSS

VDD2 – 0.2

VSS

—

2.5

3.3

—

—

—

—

2.0

VC + 0.4

VC – 0.4

—

—

950

2.7

3.6

DD2 + 0.3

V

0.8

V

DD2 + 0.3

0.2VDD2

2.281

VDD2

2.131

VDD2

0.2

1140

Unit

V

mW

AC Characteristics (Topr = –20 to +75°C, V DD1 = 2.5 ± 0.2V, VDD2 = 3.3 ± 0.3V, VSS = 0V)

Item Symbol Applicable pins Conditions Min. Typ. Max. Unit

Clock input period

Input setup time

—

tis

CLKP, CLKN, CLKC

RGB input, OSD input,

—

—

10.0

2.0

—

—

—

—

HDIN, VDIN

Input hold time

Input setup time

tih

tis

—

—

2.0

5.0

—

—

—

—

HSCL, HSDA, RSDA

Input hold time

Output rise/fall

delay time

Output rise/fall

delay time

Cross-point time

difference

HCK1 duty

tih

tor/tof

tor/tof

∆t

th/(th + tl)

4

∗

FRP, XFRP, SHST,

CLKOUT

HCK1, HCK2, DCK1,

DCK2

HCK1

—

CL = 20pF

CL = 50pF

CL = 20pF

CL = 20pF

5.0

2.5

2.5

–5.0

48

—

4.0

4.0

—

50

—

7.0

7.0

5.0

52

ns

%

HCK2 duty

Phase compensation

PLL operating

frequency

tl/(th + tl)

—

HCK2

—

CL = 20pF

PLLDIV = L

PLLDIV = H

48

55

27.5

50

—

—

52

100

MHz

55

4

∗

Output pins other than FRP, XFRP, SHST and CLKOUT.

– 8 –

CXD3526GG

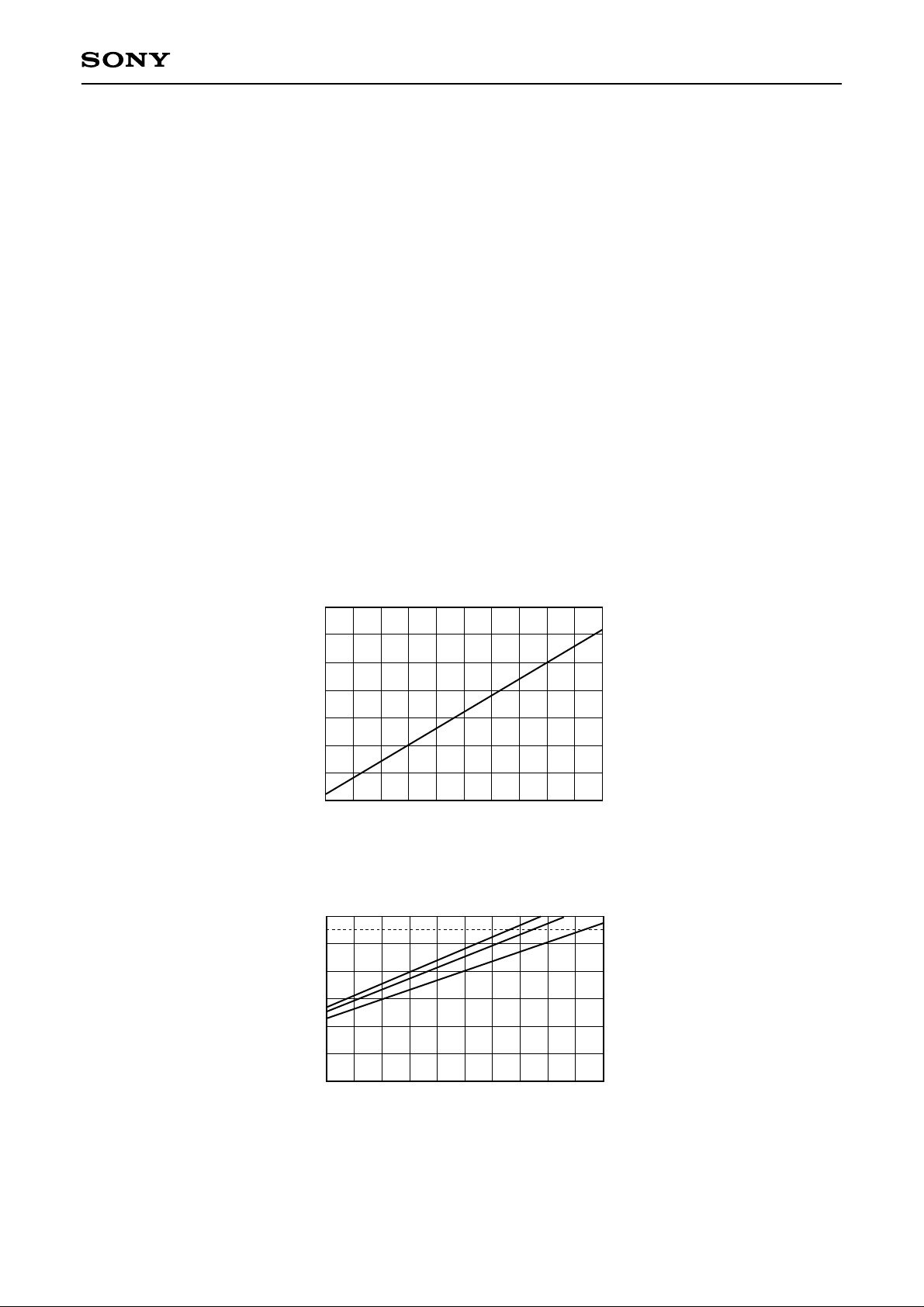

Power Consumption and Allowable Power Dissipation

The relationship between the power consumption and junction temperature of this IC must satisfy the following

formula.

Tj [°C] ≥ Toprmax [°C] + θja [°C/W] × PD [W]

In addition, specification values are as follows.

Tjmax = 125 [°C]

Toprmax = 75 [°C]

θja = 43 [°C/W] (When mounted on 4-layer substrate, wind speed 0m/s)

Under these conditions, PDmax, the maximum allowable power dissipation for the package, is as follows.

PDmax = (125 – 75)/43 = 1162 [mW]

Further more, if the operating frequency of this IC exceeds 85MHz, the junction temperature may exceed its

maximum value depending on conditions of use. Use this IC under conditions where the maximum value for

the junction temperature will not be exceeded by lowering the thermal resistance of the package as follows by

taking thermal countermeasures at this time.

Wind speed 1m/s: θja = 40 [°C/W] (When mounted on 4-layer substrate)

Wind speed 3m/s: θja = 35 [°C/W] (When mounted on 4-layer substrate)

1400

1300

1200

1100

1000

900

Power consumption [mW]

800

700

50

60 70

Operating frequency [MHz]

80 90 100

Operating Frequency vs. Power Consumption (Maximum Values)

130

120

110

43˚C/W

40˚C/W

35˚C/W

100

90

80

Junction temperature [˚C]

70

500

700 900

Power consumption [mW]

1100 1300 1500

Power Consumption vs. Junction Temperature (for Various Values of Thermal Resistance)

– 9 –

CXD3526GG

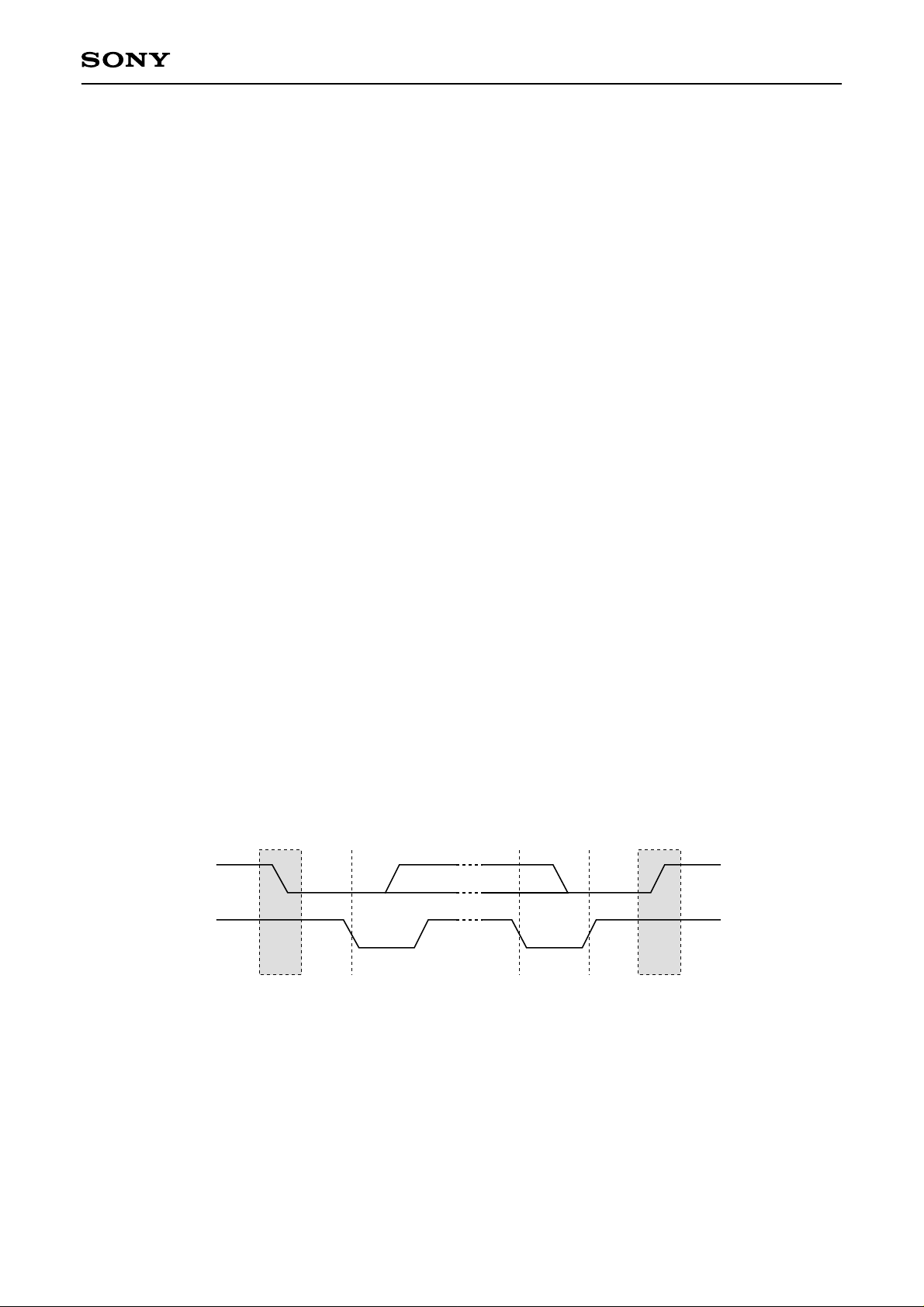

Power-on and Initialization of Internal Circuit

As for this IC, two systems of supply voltage should be turned on simultaneously. The initialization of the

internal circuit should be also performed by maintaining the system clear pin at low during the specified time

after setting the supply voltage in the range of recommended operating conditions and stabilizing as shown in

the figure below. Keep in mind that the internal circuit may not be initialized correctly if system clear

cancellation is performed before the supply voltage is set in the range of the recommended operating

conditions.

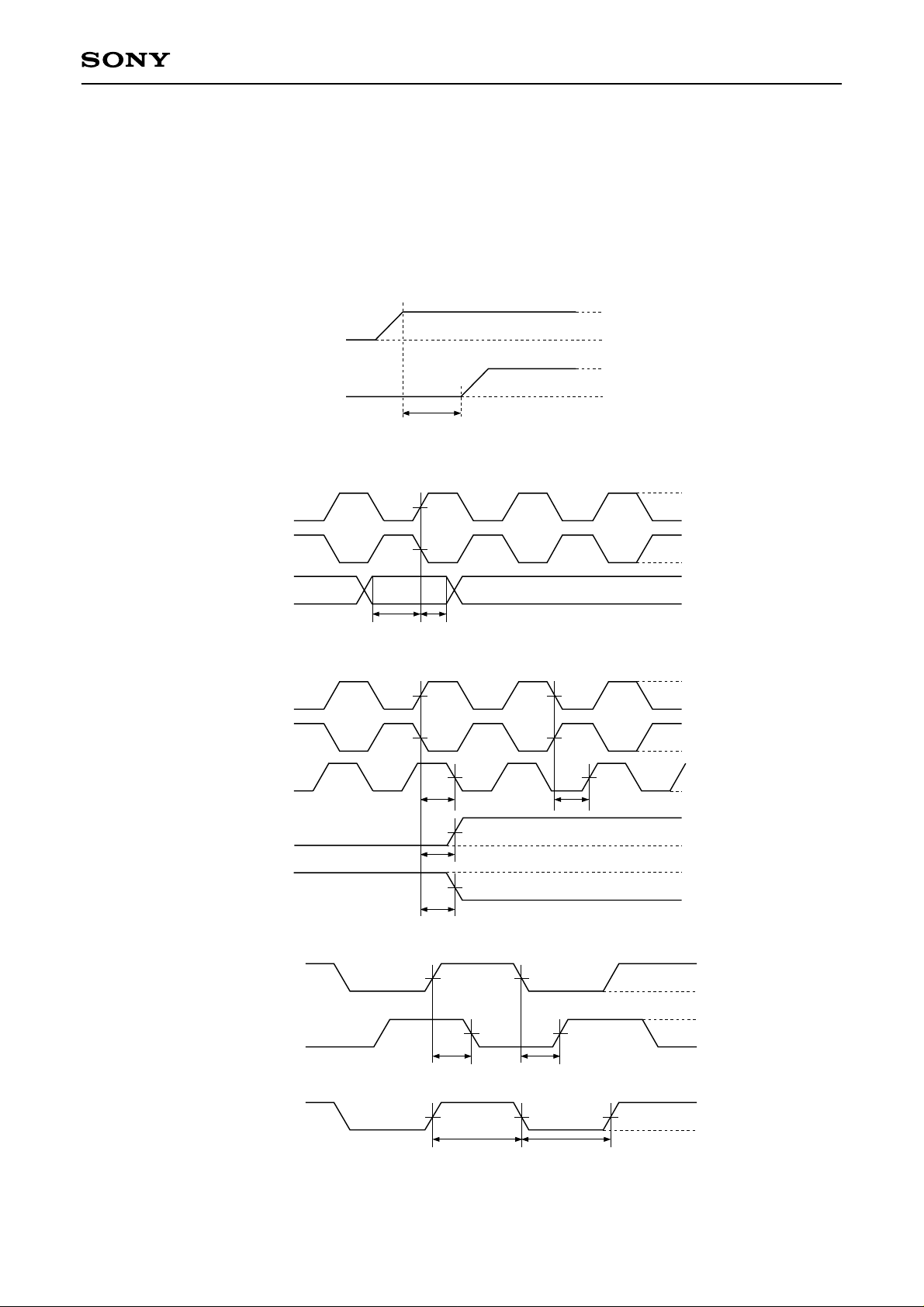

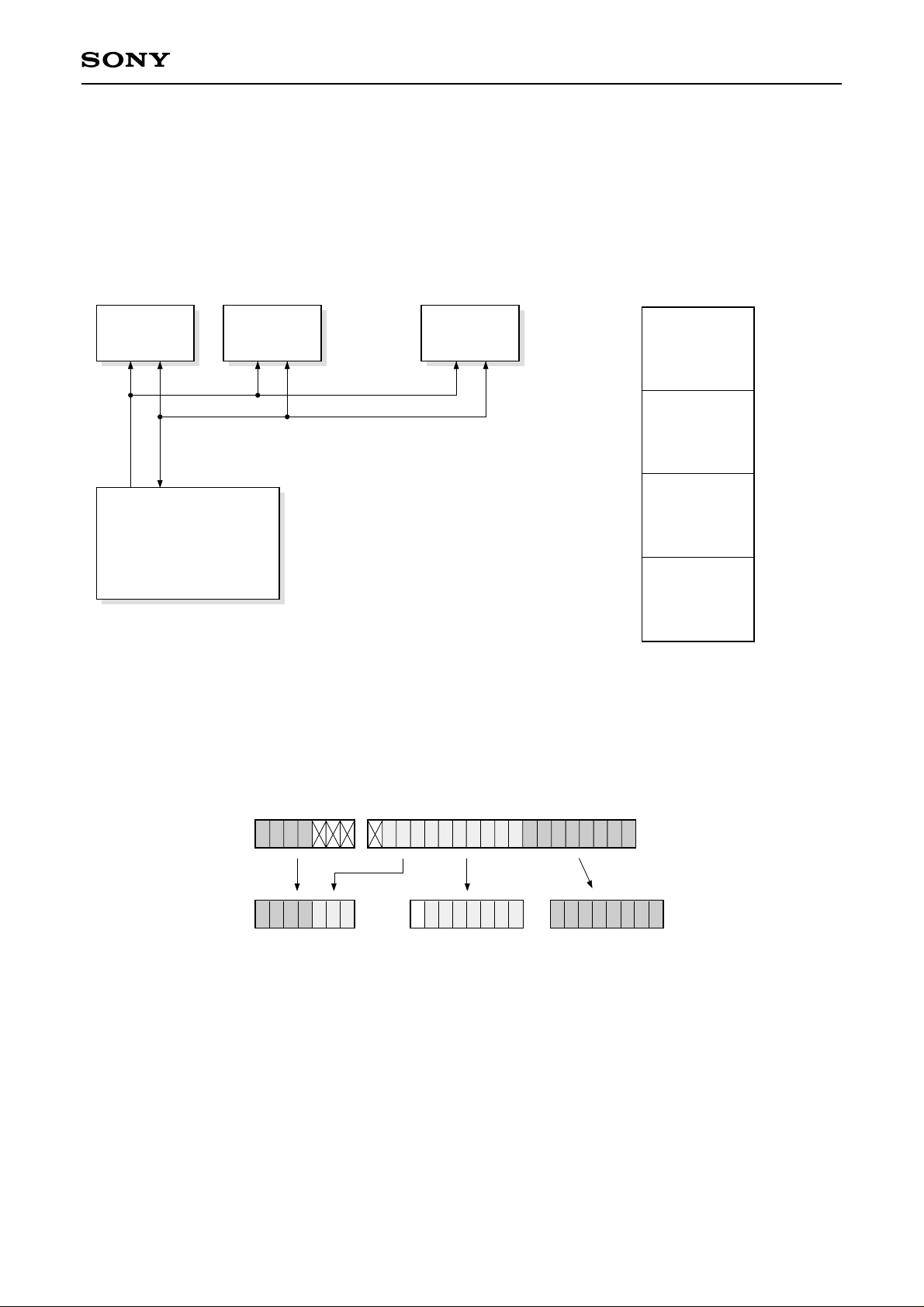

Timing Definition

HDIN, VDIN

RGB input, OSD input

XCLR1, XCLR2,

XCLR3

CLKP, CLKC

CLKN

CLKP, CLKC

CLKN

CLKOUT

Outputs other

than CLKOUT

Outputs other

than CLKOUT

V

DD1, VDD2

TR TR > 200ns

VC,

50%

VC

tis tih

VC,

50%

VC

VC

50%

50%

tof

tor

tof

VC,

50%

VC

VC

VDD1, VDD2

Vss

VDD2

Vss

tor

IH1, VIH3

V

V

IL1, VIL3

VIH3

VIL3

VIH1, VIH2

VIL1, VIL2

V

IH1, VIH3

V

SS, VIL3

VIH3

VIL3

VOH

VOL

VOH

VOL

VOH

VOL

HCK1, DCK1

HCK2, DCK2

HCK1, HCK2

50%50%

50%

∆t

50%

th tl

– 10 –

50%

VOH

VOL

VOH

∆t

50%50%

VOL

VOH

VOL

CXD3526GG

Description of Operation

1. Description of I/O Pins

(a) System clear pins (XCLR1, XCLR2 and XCLR3)

All internal circuits are initialized by setting XCLR1 (Pin 102) low. In addition, the internal PLL is initialized by

setting XCLR2 (Pin 66) low, and RGB output is initialized (preset) by setting XCLR3 (Pin 103) low.

Initialization should be performed when power is turned on.

(b) Sync signal input pins (HDIN and VDIN)

Horizontal and vertical separate sync signals are input to HDIN (Pin 62) and VDIN (Pin 17), respectively. The

CXD3526GG supports only non-interlace sync signals with a dot clock of 100MHz or less.

(c) Master clock input pins (CLKP/CLKN, CLKC, CLKSEL and CLKPOL)

Phase comparison is performed by an external circuit and a clock synchronized to the sync signal is input. The

master clock input pins have two systems consisting of CLKP/CLKN (Pins 101 and 130) for small-amplitude

differential input (center level: 2.0V, amplitude: ±0.4V), and CLKC (Pin 131) for CMOS level input. In addition,

the clock path selection is performed with CLKSEL (Pin 100) and CLKPOL (Pin 63). The setting values are as

follows.

CLKSEL: 0 = CLKP and CLKN input; 1 = CLKC input

CLKPOL: 0 = Input clock is non-inverted; 1 = Input clock is inverted

(d) PLL setting pin (PLLDIV)

PLLDIV (Pin 129) sets the divider setting of the internal phase compensation PLL circuit. The setting values for

master clock frequency are as follows.

PLLDIV: 0 = 55 to 100MHz; 1 = 27.5 to 55MHz

Note that the frequency of the clock input to the CXD3526GG must be within the phase compensation PLL

operating range, even during free running.

(e) RGB signal input pins (RIN, GIN and BIN)

These pins input RGB digital signals in 10 bits. The Red signal is input to RIN (Pins 4 to 6, 50 to 53 and 89 to

91), the Green signal to GIN (Pins 7, 8, 54, 55, 92, 93 and 123 to 125), and the Blue signal to BIN (Pins 9 to

12, 56 to 58 and 95 to 97) respectively.

(f) OSD signal input pins (ROSD, GOSD, BOSD, YS and Y M)

These pins input OSD signals. The Red signal is input to ROSD (Pins 14 and 59), the Green signal to GOSD

(Pins 15 and 60), and the Blue signal to BOSD (Pins 16 and 61) respectively. In addition, the YM signal is input

to YM (Pin 98), and the YS signal to YS (Pin 99).

– 11 –

CXD3526GG

(g) Host I/F serial clock input pin (HSCL)

HSCL (Pin 68) is the clock input pin used to set the I/O timing for serial data from the host. Data is taken from

the HSDA pin when the clock signal rises, and data is output to the HSDA pin when the clock signal falls.

(h) Host I/F serial I/O pin (HSDA)

This is the I/O pin for serial data from the host. It is necessar y to switch the input to the HSDA (Pin 70) while

the signal level of HSCL is low.

(i) Slave address input pin (HSEL)

With this IC, it is possible to select host I/F slave address. Since a slave address is used to identify each of

these devices, this pin should be connected to VDD or Vss externally. This VDD and Vss setting drives the device

which matches the slave address input from the HSDA pin. The slave addresses of this IC used for the HSEL

(Pin 22) setting are as follows.

HSEL: 0 = 74h; 1 = 76h

(j) External ROM I/F serial clock output pin (RSCL)

RSCL (Pin 23) is the clock output pin used to set the I/O timing of serial data sent to the external EEPROM.

Data is taken from the RSDA pin when the clock signal r ises, and data is output to the RSDA pin when the

clock signal falls.

(k) External ROM I/F serial I/O pin (RSDA)

This is the I/O pin for serial data sent to the external EEPROM. It is necessary to switch the input to the RSDA

(Pin 69) while the signal level of RSCL is low.

2. Pipeline Delay of the RGB and OSD Signals

The pipeline delay f or the I/O of the RGB signals is 32 clock cycles of the master clock. In addition, the pipeline

delay for the OSD, YS and YM signals is 25 clock cycles of the master clock.

– 12 –

CXD3526GG

3. Serial Bus

The serial bus of this IC consists of a host I/F, external ROM I/F and register I/F.

3-1. Host I/F

With this IC, each register setting and data set to built-in RAM are perfor med over a serial bus. Bus protocol

conforms to I2C bus specifications. Note that this IC does not suppor t multi-slave functions, and that the bus

should be independent from ICs having the other I2C bus specification. Also, when accessing gamma RAM,

always access memory address from odd addresses in 2-byte units. The following restrictions are placed on

the host I/F of this IC.

• Only I2C bus slave operations are performed.

• Standard mode and fast mode are supported. Hs mode is not supported.

• Multi-slave functions are not supported.

• The general call address and start byte of the slave address are not acknowledged.

• C bus compatibility is not supported.

• Acknowledgment is not performed for 10-bit slave addresses.

• Low is not asserted for HSCL. (Wait control is not performed.)

(1) "Start" conditions

Read and write operations enter "Start" status by switching HSDA input from high to low level while HSCL input

is high.

(2) "Stop" conditions

"Stop" results by switching HSDA input from low to high while HSCL input is high. Setting "Stop" status causes

read processing to terminate during read operations, and causes the input of write data to terminate dur ing

write operations.

HSDA

HSCL

"Start" "Stop"

"Start" Conditions and "Stop" Conditions

– 13 –

CXD3526GG

(3) Acknowledgment

Acknowledgment is used to indicate whether or not data has been sent/received normally. The

"Acknowledgment" of a data transfer is performed after that data transfer when the sender releases the bus on

the 9th clock of HSCL and the receiver drives low. If the host is the receiver, the IC is informed by the host that

data has ended by the fact that "Acknowledgment" is not generated for the last data sent from the IC.

HSDA in

HSDA out

HSCL

12 89

Not

acknowledged

Acknowledged

"

Acknowledgment

""Start"

Acknowledgment on the I2C Bus

(4) Slave address specification

After "Start" is sent, a 7-bit slave address and 1-bit read/write code is sent. Read/write operations with this IC

start if the input slave address matches the device address set using HSEL. If the device address does not

match, "Acknowledgment" is not generated and the system does nothing.

Slave Address Word (8 bits)

Device Code (fixed)

Device

Select

R/W

Code

011101HSEL R/W

∗

If R/W = 1, read results, if R/W = 0, write results.

Slave Address Specification

(5) Byte write operation

After "Start" is sent, the R/W code is set to low and an 8-bit device address word is input. The IC outputs

"Acknowledgment" on the 9th bit and enters write mode. After this, "Acknowledgment" is output every 8 bits

after each of the two 8-bit memory addresses are input. Next, "Acknowledgment" is output after 8 bits of write

data is input and written to the IC.

HSDA

1st memory address

1W01110

R/W

ACK

START

HSEL

A15

A14

A13

(n)

A12

A11

2nd memory address

A9A8A7A6A5A4A3A2A1

A10

ACK

(n) Write data (n)Slave address

A0

D7D6D5D4D3D2D1

ACK

D0

ACK

STOP

Byte Write Operation

– 14 –

CXD3526GG

(6) Continuous write operation

This IC possesses a function which can write data continuously. With the continuous write operation, write data

is written in a manner similar to the byte write operation. Continuous write is possible by sending write data

continuously before sending "Stop". The address used to write data during the continuous write operation is

automatically incremented when each separate write operation terminates.

There is no limit on the number of continuous transfers that are possible to write continuously with this IC.

HSDA

1st memory address

1W01110

R/W

ACK

START

HSEL

A15

(n)

A14

A13

• • • • • • • •

A12

A11

2nd memory address

A9A8A7A6A5A4A3A2A1

A10

ACK

(n) Write data (n)Slave address

D7D6D5D4D3D2D1D0D7D6D5D4D3D2D1

A0

D7D6D5D4D3D2D1

ACK

Write data (n + m)

ACK

D0

D0

ACK

ACK

STOP

Continuous Write Operation

(7) Byte read operation

After "Start" is sent, the R/W code is set to low and an 8-bit device address word is input. The IC outputs

"Acknowledgment" to the 9th bit and enters write mode. After this, "Acknowledgment" is output ever y 8 bits

after each of the two 8-bit memory addresses are input. Once the addresses are acknowledgment, "Restart" is

input, and the R/W code is set to high, an 8-bit device address word is input, and the IC outputs

"Acknowledgment" to the 9th bit and enters read mode. Next, 8 bits of read data are output using the address

used for the dummy write, and the read operation terminates if "Stop" is input without inputting

"Acknowledgment".

HSDA

1st memory address

1W01110

R/W

ACK

START

HSEL

(n)

A15

A14

A13

A12

Dummy write

A11

2nd memory address

A9A8A7A6A5A4A3A2A1

A10

ACK

Slave address Read data (n)

RESTART

(n)Slave address

A0

ACK

1R01110

Current address read

D7D6D5D4D3D2D1

R/W

ACK

HSEL

D0

STOP

No ACK

Byte Read Operation

– 15 –

CXD3526GG

(8) Continuous read operation

This IC possesses a function which can read data continuously. With the continuous read operation, data up to

the current address is read in a manner similar to the byte read operation. Continuous read is possible by

receiving continuous read data and perform "Acknowledgment" before sending "Stop". The address used for

reading data during the continuous read operation is automatically incremented when each separate read

operation terminates.

There is no limit on the number of continuous transfers that are possible to read continuously with this IC.

Slave address Read data (n) Read data (n + 1) Read data (n + m)

1R01110

START

or

RESTART

R/W

HSEL

D7

D6D5D4D3D2D1D0D7D6D5D4D3D2D1D0

ACK

ACK

• • • • • • • •

ACK

D7D6D5D4D3D2D1

D0

STOP

No ACK

Continuous Read Operation

– 16 –

CXD3526GG

3-2. Conditions for Accessing Gamma RAM and Color Shading RAM

With this IC, there are two way to access the internal RAM: by the host I/F using the serial bus and refresh/

write-back for sending/receiving data via external ROM I/F. In the case of Gamma RAM, internal RAM must be

accessed by the host I/F in 2-byte units, and memory address must be read from or written to odd memory

addresses. Color shading RAM can be accessed in 1-byte units and there is no restriction on which addresses

can be read or written.

It is possible to access internal RAM from each I/F when the conditions given in the following table are

established.

GAM_ON

0

1

1

∗

GAM_ON represents the setting value of the DSD register.

∗

Gamma correction is not performed when GAM_ON is "0", and is performed when

Vertical blanking period

—

Vertical blanking period

Outside vertical blanking period

Gamma RAM access

Yes

Yes

No

GAM_ON is "1".

Conditions for Accessing Gamma RAM

CSC_ON

0

1

1

∗

CSC_ON represents the setting value of the color shading register.

∗

Color shading correction is not performed when CSC_ON is "0", and is performed when

Vertical blanking period

—

Vertical blanking period

Outside vertical blanking period

Color shading RAM access

Yes

Yes

No

CSC_ON is "1".

Conditions for Accessing Color Shading RAM

GAM_ON must be set to "0" when performing a write-back or forced refresh operation for Gamma RAM.

Similarly, CSC_ON must be set to "0" when performing a write-back or forced refresh operation for color

shading RAM.

In the case of a self-refresh operation, the start of vertical blanking period is automatically detected and

operations start automatically at that time, regardless of how GAM_ON and CSC_ON are set. Therefore, be

sure to set the external EEPROM transfer count register ROM_TRAN to fit within the ver tical blanking period.

Furthermore, the vertical blanking period for gamma is set using GAM_H1, GAM_H2, GAM_V1 and GAM_V2,

while the vertical blanking period for color shading is set using CSC_HP, CSC_VP, CSC_HNUM, CSC_VNUM,

CSC_HINT and CSC_VINT. Make all settings in accordance with the specifications of the video signal

attempting to be displayed.

– 17 –

CXD3526GG

3-3. External ROM I/F

When operating the external ROM I/F, operations start by setting the serial bus register from the host I/F. The

serial bus on the ROM side is used to access the external EEPROM. Bus protocol conforms to I2C bus

specifications. Also, the following restrictions are placed on the external ROM I/F of this IC.

• Only master operations are performed.

• Standard mode and fast mode are supported. Hs mode is not supported.

• Multi-master functions are not supported.

• The general call address and start byte of the slave address are not generated.

• C bus compatibility is not supported.

• A memory address space of up to 512K bytes is supported.

• Wait control by RSCL is not supported.

• 10-bit slave addresses are not supported.

(1) External ROM I/F clock settings

The frequency of the clock signal supplied to the external EEPROM by the RSCL pin is set using RSCL_SEL

of the serial bus control registers. Set this value based on the operating frequency of the IC as given in the

table below so that the frequency output by the RSCL pin is appropriate for the specifications of the external

EEPROM.

RSCL_SEL

00

01

10

11

Operating frequency

35MHz or less

70MHz or less

94.5MHz or less

100MHz or less

(2) External EEPROM memory capacity setting

With this IC, slave addresses and memory addresses are generated in accordance with the memory capacity

set for the external EEPROM. The memory capacity of the external EEPROM is set using ROM_MAP of the

serial bus control registers.

ROM_MAP

Usable memory size

00

01

10

11

512K-bit (65,536 × 8-bit)

256K-bit (32,768 × 8-bit)

128K-bit (16,384 × 8-bit)

64K-bit (8,192 × 8-bit)

– 18 –

CXD3526GG

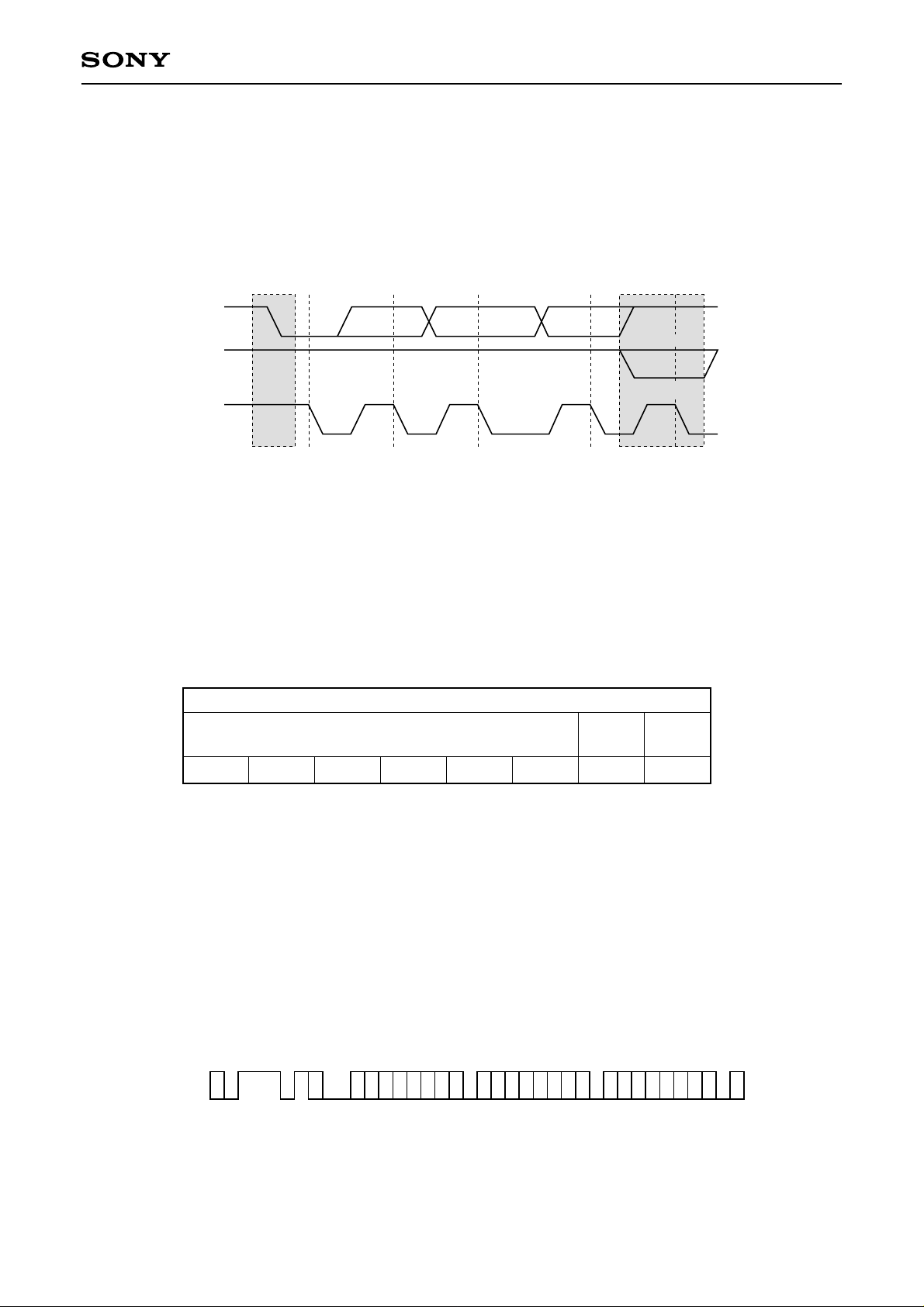

[Example] Address output when using eight 256K-byte EEPROMs (ROM_MAP = 01)

With this IC, the ROM slave address register setting [7:4] is set as is for the serial bus slave address [7:4], and

the memory address [17:15] is used for the slave address [3:1]. The memory address [14:0] is used as is for

the 1st and 2nd memory addresses. The 1st memor y address [7] is fixed to all "0". Furthermore, up to eight

external EEPROMs can be connected to this IC.

Bank 0

RSCL

EEPROM

256K-bit

CXD3526GG

Bank 1

X0h

RSDA

EEPROM

256K-bit

X1h X7h

• • • • • • •

System Configuration Diagram

Bank 7

EEPROM

256K-bit

0_0000h

0_7FFFh

0_8000h

0_FFFFh

1_0000h

3_7FFFh

3_8000h

3_FFFFh

Bank 0

32K-byte

Bank 1

32K-byte

•

•

•

Bank 7

32K-byte

Memory Map

256K-byte space

Slave address

X0h

X1h

X7h

Slave address register [7:4] Memory address [18:0]

74 0118

717

Slave address [7:1]

1st memory address [7:0] 2nd memory address [7:0]

0

0 70

– 19 –

CXD3526GG

(3) External ROM I/F slave address setting

The external ROM I/F of this IC transfers data into and out of memory using the serial bus as host I/F. Since

operations conform to I2C bus protocol just as with the host I/F, this section only describes the slave address.

To access the external EEPROM, when access conditions are established, "Start" is sent, and then 7 bits

representing the slave address are output, and the R/W code is output. "Acknowledgment" is received to the

9th bit from the external EEPROM, and the IC enters either read or write mode. The slave address is

determined based on ROM_MAP of the serial bus ROM I/F control register and RSLV_ADDR of the ser ial bus

ROM slave address register as previously described.

The user should set the upper 4 bits of the device address of the EEPR OM to be used in RSLV_ADDR and the

memory size in ROM_MAP. This allows memory to be used without awareness of memory boundaries of

actual memory used for the setting memory space.

RSDA

1st memory address

W

R/W

START

ACK

A15

A14

A13

(n)

A12

A11

2nd memory address

A9A8A7A6A5A4A3A2A1

A10

ACK

(n) Write data (n)Slave address

A0

D7D6D5D4D3D2D1

ACK

D0

ACK

STOP

Byte Write Operation

(4) Memory location and data size setting for the external EEPROM

Since this IC performs refresh and write-back operations, it is necessary to set which addresses of the

external EEPROM gamma data and color shading data have been located in.

The registers used to make these settings are the external EEPROM gamma data start address register and

the external EEPROM color shading data start address register. By specifying the star ting position of the data

area in these registers data access from the specified addresses is possible during refresh or write-back

operation.

Units of 1K-byte can be used to set the start addresses which can be set in these registers.

In addition, the size of data transferred during refresh and write-back operations is fixed at 2K bytes for each

color in the case of gamma data. The n umber of bytes transferred in the case of color shading data is the value

stored in the color shading data size register plus one.

– 20 –

CXD3526GG

(5) Refresh and write-back operations

This IC includes a function that allows an external EEPROM to automatically refresh the internal RAM. This

function has the four modes described below.

• Self-refresh mode

• Forced refresh mode

• Write-back mode

• Refresh stop mode

Each mode is started by writing the specified mode into REF_MODE of the refresh register.

In self-refresh mode, the IC detects that the vertical blanking period has been entered and, using the value

specified in the external EEPROM transfer count register, uses the continuous read operation to transfer data

of the size "transfer count plus 1" to the external ROM I/F. The data read using the continuous read transfer is

written into the internal RAM.

When the transfer of the all data for the data size is completed, the access area for the internal RAM is

changed, continuous read transfer is executed indefinitely until self-refresh mode is exited, and refresh

operations are automatically carried out on the internal RAM.

In forced refresh mode, continuous read transfer from the external EEPROM is performed for the RAM area

specified by REF_RSEL of the refresh RAM select register, and the read data is wr itten to the inter nal RAM.

When the transfer of all data for the specified RAM area is completed, REF_END of the refresh status register

set to a flag indicating the operation has ended, and operations stop.

If forced refresh operations are to be performed for the entire internal RAM, first set the refresh RAM select

register to gamma RAM (R) and perform the forced refresh operation. Since the refresh RAM select register is

automatically set to the next RAM area after all data is transferred, refresh for the entire RAM can be

completed by repeating the forced refresh operation five times.

In write-back mode, continuous write transfer is performed from the RAM area specified by REF_RSEL of the

refresh RAM select register to the external EEPROM. When the transfer of all data for the specified RAM area

is completed, REF_END of the refresh status register set to a flag indicating the operation has ended, and

operations stop.

If write-back operations are to be performed for the entire internal RAM, first set the refresh RAM select

register to gamma RAM (R) just as for forced refresh operation, and then perform the write-back operation.

Since the refresh RAM select register is automatically set to the next RAM area after all data is transferred,

write-back for the entire RAM can be completed by repeating the write-back operation five times.

In refresh stop mode, the external ROM I/F does not operate and nothing is output on the serial bus.

(6) Forced reset of the external ROM I/F control circuit

With this IC, forced reset is possible in case a problem occurs with the external ROM I/F and the internal

circuit becomes locked. Forced reset initializes only the external ROM I/F control circuit by writing "1" to

ROM_RST of the refresh register. Normal operations are allowed after initialization is complete.

3-4. Register I/F Control Circuit

The register I/F control circuit transfers data between the host I/F and the external ROM I/F. Register data

other than RAM data is stored here. Since registers have a double buffer configuration, data in the first buffer is

synchronized with the internal VD and reflected in the second buffer, while data in the second buffer is input to

each block. Note, however, that data in the serial bus control register has a single buffer configuration.

– 21 –

CXD3526GG

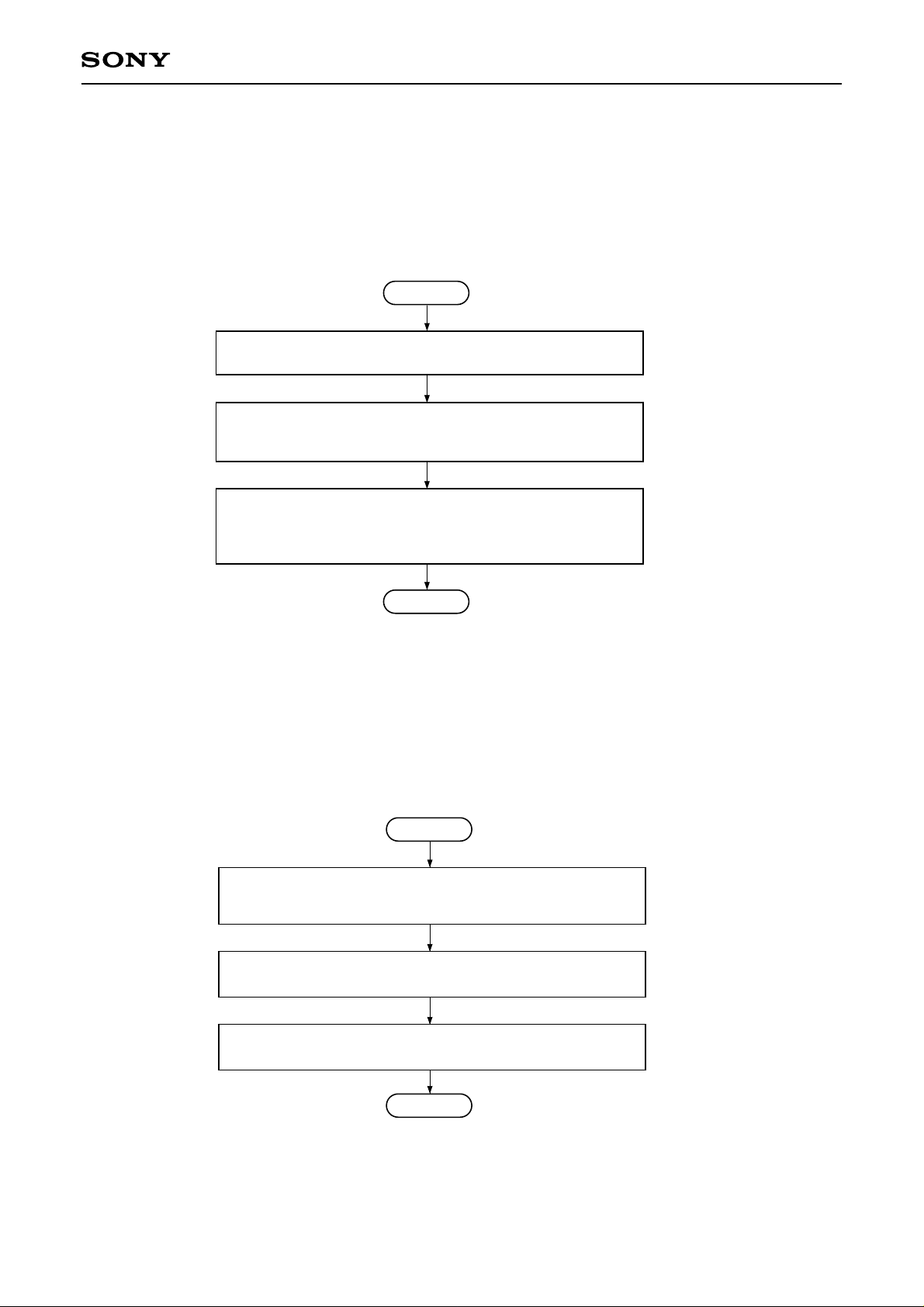

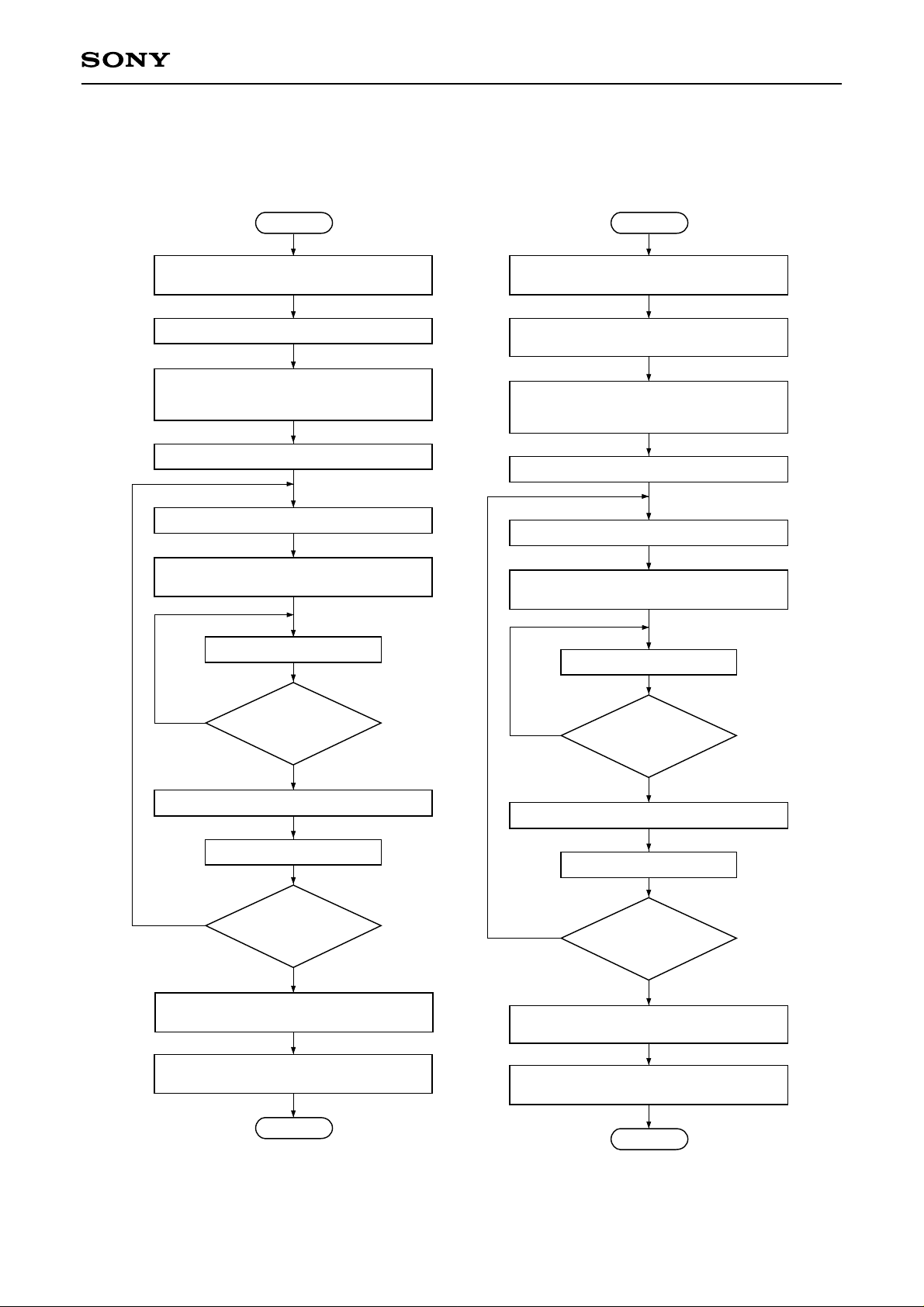

3-5. Software Flow

(1) Settings when power is turned on

The following procedure is the setting procedure first perfor med after power of the IC is turned on. If this

procedure is not executed, the internal VD will not be generated and register data cannot be set correctly.

Start

Perform settings such as for the timing of the corresponding LCD panel

using the TG register.

Since the TG register uses a double register configuration using a V latch,

set the FORCE_VD register of the serial bus control register to "1" only at

startup to transfer TG register setting values.

Perform setting for unset registers.

If TG is operating at this time, there is no need to write the FORCE_VD

register due to the fact that registers having a double register configuration

will be automatically written using VD from an external source.

End

(2) Setting procedure of the serial bus control register

The following procedure is the procedure for setting the serial bus control register in accordance with the external

EEPROM to which the IC is connected. Be sure to make settings according to the operating frequency of the IC

and the speed, capacity and number of external EEPROMs that are connected.

Start

Find the optimum clock frequency for the external ROM I/F based on the

frequency of the system clock and set the Bits 1 and 0 of the RSCL_SEL

register to this value.

Set the total capacity of the connected EEPROM devices and set Bits 5

and 4 of the ROM_MAP register to this value.

Set the slave addresses of the EEPROM devices connected into the

RSLV_ADDR register.

End

– 22 –

CXD3526GG

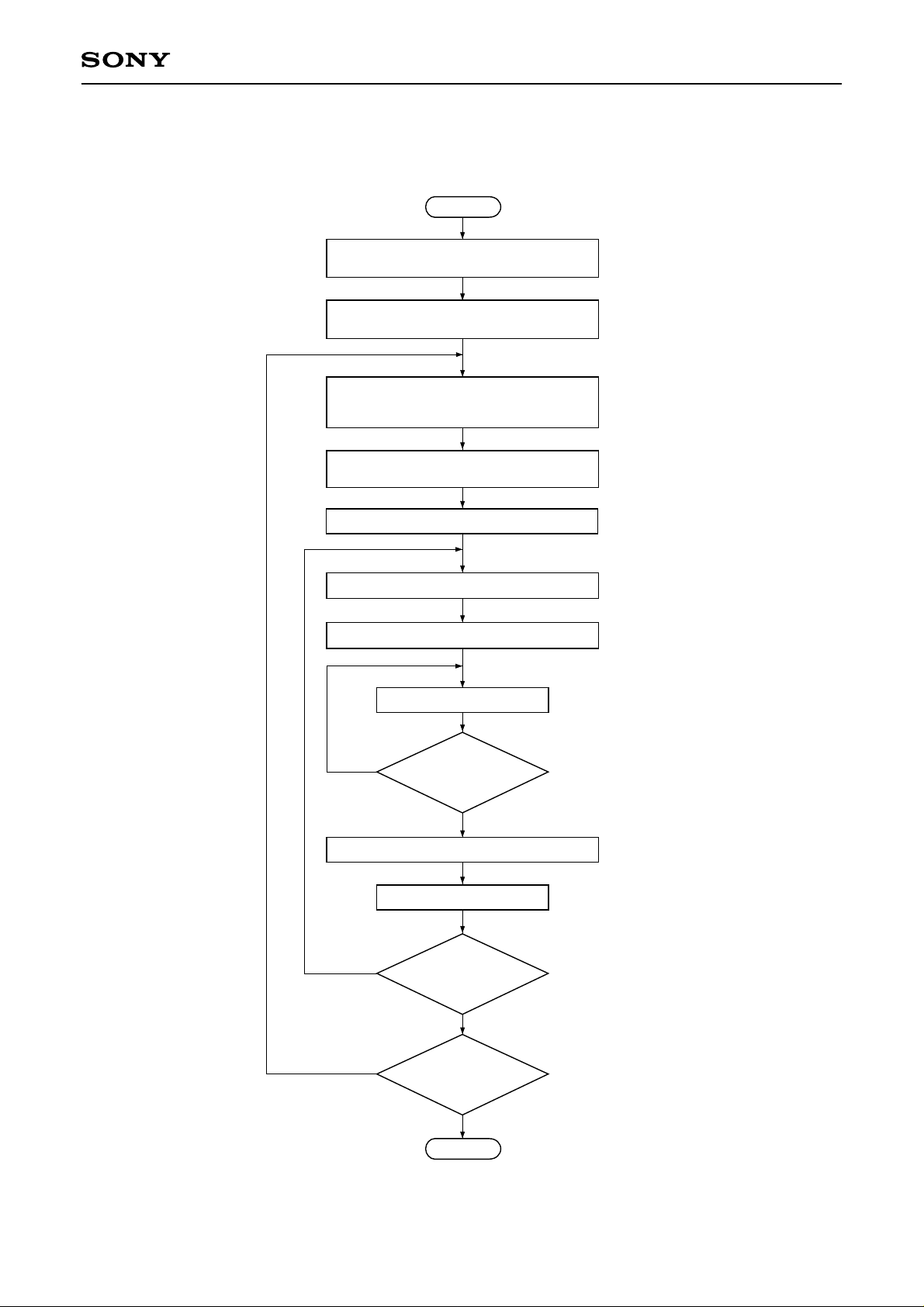

(3) Write-back procedure

The following procedure is the procedure for writing gamma correction and color shading correction data back

to the external EEPROM.

Start

During display, mute the video signal using the DSD

register.

Set GAM_ON = 0 and CSC_ON = 0 so that the

gamma RAMs and color shading RAMs are not used.

Set the GAM_ADDR, CSC_ADDR, CSC_SIZE and

ROM_TRAN registers to the addresses and transfer

count to be used to perform write-back.

Write data into the gamma RAMs (R, G, B) and color

shading RAMs (R, G, B).

Set the REF_RSEL register to gamma RAM (R).

Write "1" to the REF_END register and clear status.

Write 03h to the REF_MODE register to start write-back.

Read the REF_END register.

Is the status "1"?

0: Write-back currently

being performed

Write "1" to the REF_END register and clear status.

Read the REF_RSEL register.

No

Is write-back complete

for all RAMs?

1: Write-back complete

Write-back other data.

Yes

Is there other gamma

and color shading data

to be written back?

End

End

– 23 –

CXD3526GG

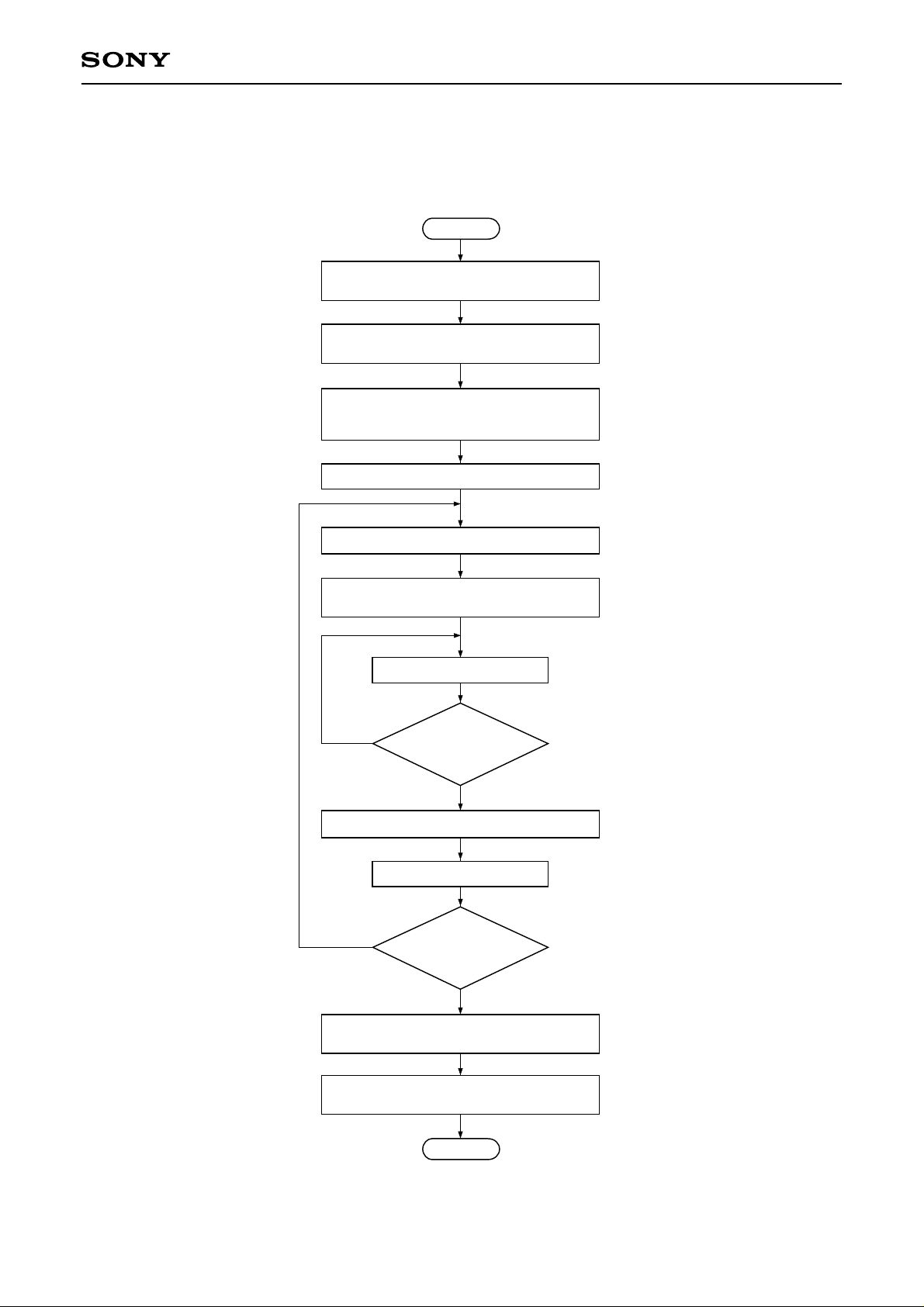

(4) Forced refresh procedure during power-on

The following procedure is the procedure for setting gamma correction and color shading correction data from

an external EEPROM for forced refresh when power is turned on.

Start

During display, mute the video signal using the DSD

register.

Set GAM_ON = 0 and CSC_ON = 0 so that the

gamma RAMs and color shading RAMs are not used.

Set the GAM_ADDR, CSC_ADDR, CSC_SIZE and

ROM_TRAN registers to the addresses and transfer

count to be used to perform forced refresh.

Set the REF_RSEL register to gamma RAM (R).

Write "1" to the REF_END register and clear status.

Write 02h to the REF_MODE register to start forced

refresh.

Read the REF_END register.

Is the status "1"?

0: Forced refresh

currently being performed

Write "1" to the REF_END register and clear status.

Read the REF_RSEL register.

No

Is forced refresh

complete for all RAMs?

1: Forced refresh complete

Yes

Set GAM_ON and CSC_ON so that the gamma RAMs

and color shading RAMs will be used by the video signal.

If a video signal is to be displayed, cancel muting of

the video signal using the DSD register.

End

– 24 –

CXD3526GG

(5) Procedure for forced refresh during normal operations

The following procedure is the procedure for selecting either gamma correction or color shading correction

data during normal operations.

Start

During display, mute the video signal using the DSD

register.

Set GAM_ON = 0 so that the gamma RAMs are not used.

Set the GAM_ADDR and ROM_TRAN registers to the

addresses and transfer count to be used to perform

forced refresh.

Set the REF_RSEL register to gamma RAM (R).

Write "1" to the REF_END register and clear status.

Write 02h to the REF_MODE register to start forced

refresh.

Read the REF_END register.

Start

During display, mute the video signal using the DSD

register.

Set CSC_ON = 0 so that the color shading RAMs are

not used.

Set the CSC_ADDR, CSC_SIZE and ROM_TRAN

registers to the addresses and transfer count to be

used to perform forced refresh.

Set the REF_RSEL register to color shading RAM (R).

Write "1" to the REF_END register and clear status.

Write 02h to the REF_MODE register to start forced

refresh.

Read the REF_END register.

Is the status "1"?

0:Forced refresh

currently being performed

Write "1" to the REF_END register and clear status.

Read the REF_RSEL register.

Is forced refresh of the

Perform forced

refresh for the other

gamma RAMs.

Set GAM_ON so that the gamma RAMs will be used

by the video signal.

If a video signal is to be displayed, cancel muting of

the video signal using the DSD register.

gamma RAMs (R, G, B)

complete?

1: Forced refresh complete

Forced refresh complete

for all gamma RAMs.

End

Is the status "1"?

0: Forced refresh

currently being performed

Write "1" to the REF_END register and clear status.

Read the REF_RSEL register.

Is forced refresh of

the color shading RAMs

Perform forced

refresh for the other

color shading RAMs.

Set GAM_ON so that the color shading RAMs will be

used by the video signal.

If a video signal is to be displayed, cancel muting of

the video signal using the DSD register.

(R, G, B) complete?

1: Forced refresh complete

Forced refresh complete

for all color shading RAMs.

End

– 25 –

CXD3526GG

(6) Procedure for self-refresh during normal operations

• Starting the refresh operation

The following procedure is the procedure used to set cyclic refreshing of the gamma correction and color

shading correction data stored in the built-in RAM during normal operations.

Start

Set the GAM_H1, GAM_H2, GAM_V1 and GAM_V2 registers of the DSD

register and the CSC_HNUM, CSC_VNUM, CSC_HINT and CSC_VINT

registers of the color shading register to the appropriate values.

Set GAM_ON and CSC_ON so that the gamma RAMs and color shading

RAMs are used by the video signal.

Set the GAM_ADDR, CSC_SIZE and ROM_TRAN registers to the

addresses and transfer count to be used to perform self-refresh.

Set the REF_RSEL register to gamma RAM (R).

Write "1" to the REF_END register and clear status.

Write 01h to the REF_MODE register and start self-refresh.

End

• Stopping the refresh operation

The following procedure is the procedure used to stop the self-refresh operation.

Start

Write 00h to the REF_MODE register to stop self-refresh.

End

– 26 –

CXD3526GG

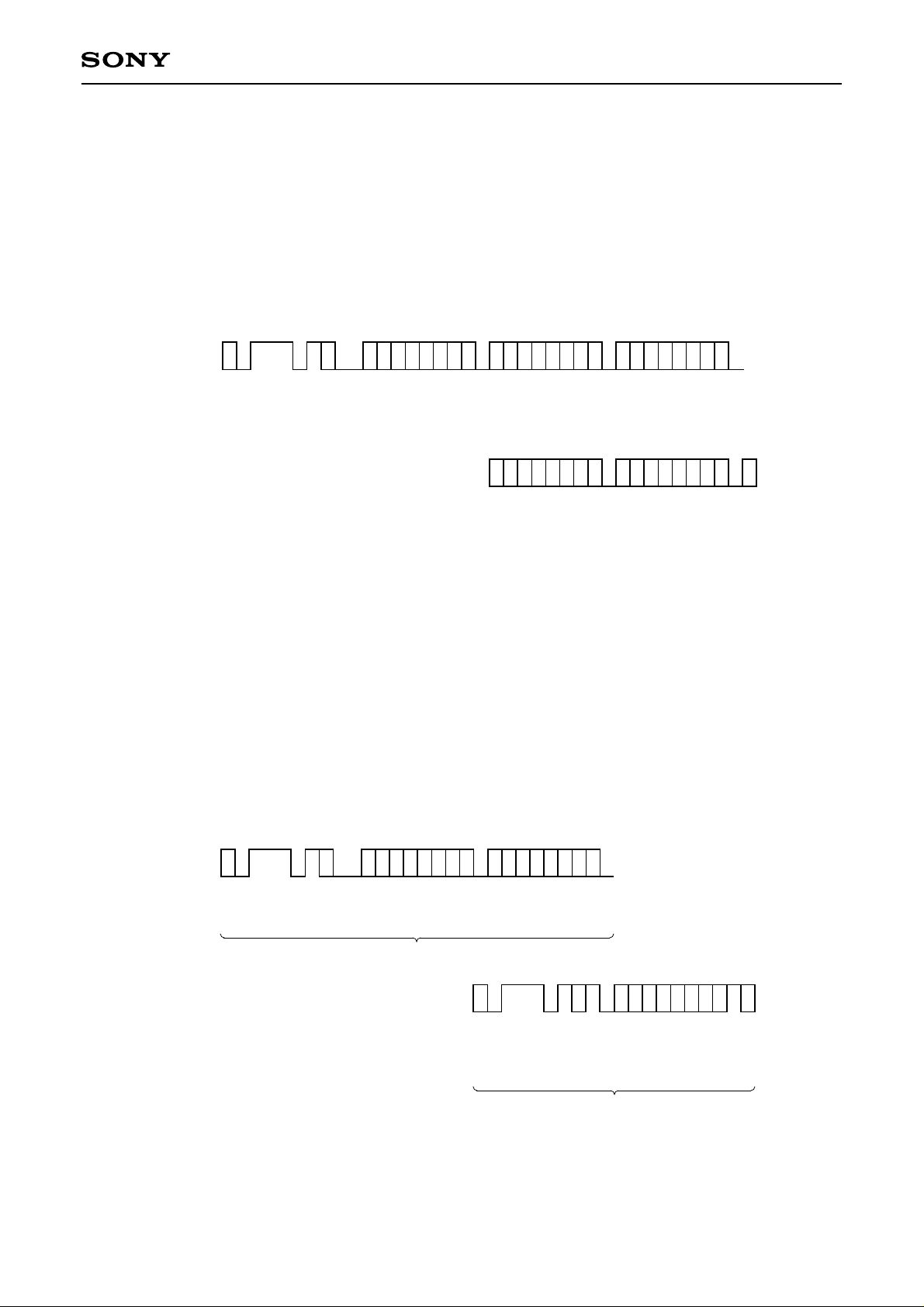

4. Timing Generator (TG) Block

This block generates the timing pulses required to drive Sony LCD panels. Of the output pulses, the required

pulses differ according to the LCD panel type, so be sure to also check the specifications of the panel used.

The output timing pulses are all set by the serial bus. For a detailed description, see the description of the TG

block register setting.

HSYNC

VSYNC

HSYNC

Detector

HPOL

Detector

VSYNC

Detector

VPOL

Detector

PLL Counter

N Detector

Register

Pic. PLS

HPOS. Counter

HPLS

Generator

VPLS GeneratorHPOS. Counter

HST, PST, HCK1, HCK2,

DCK1, DCK2, ENB, PCG,

PRG, SHST, HD2, HD3,

CLR

CLP, HD1

VST , VCK,

FRP, XFRP

CTRL

RGT, DWN

XRGT, PO1, PO2

– 27 –

Loading...

Loading...