Sony CXD3521GG Datasheet

Interface and Driver IC for LCD

Description

The CXD3521GG is an interface and driver IC for

the color LCD module ACX704AKM/BKM.

Features

• Generates the color LCD module ACX70 4AKM/BKM

drive pulse.

• Supports standby mode

• Built-in 9-channel reference voltage driver

• Built-in common voltage driver

Applications

PDA, compact LCD monitor, etc.

Structure

Silicon gate CMOS IC

CXD3521GG

128 pin TFBGA (Plastic)

Absolute Maximum Ratings (Ta = 25°C)

• Supply voltage 1 VDD1 VSS – 0.3 to +4.6 V

• Supply voltage 2 VDD2 VSS – 0.3 to +6.0 V

• Input voltage VI VSS – 0.3 to VDD + 0.3 V

• Output voltage VO VSS – 0.3 to VDD + 0.3 V

• Storage temperature

Tstg –55 to +125 °C

Recommended Operating Conditions

• Supply voltage 1 VDD1 3.0 to 3.6 V

• Supply voltage 2 VDD2 4.7 to 5.3 V

• Operating temperature

Topr –25 to +75 °C

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

– 1 –

E01408-PS

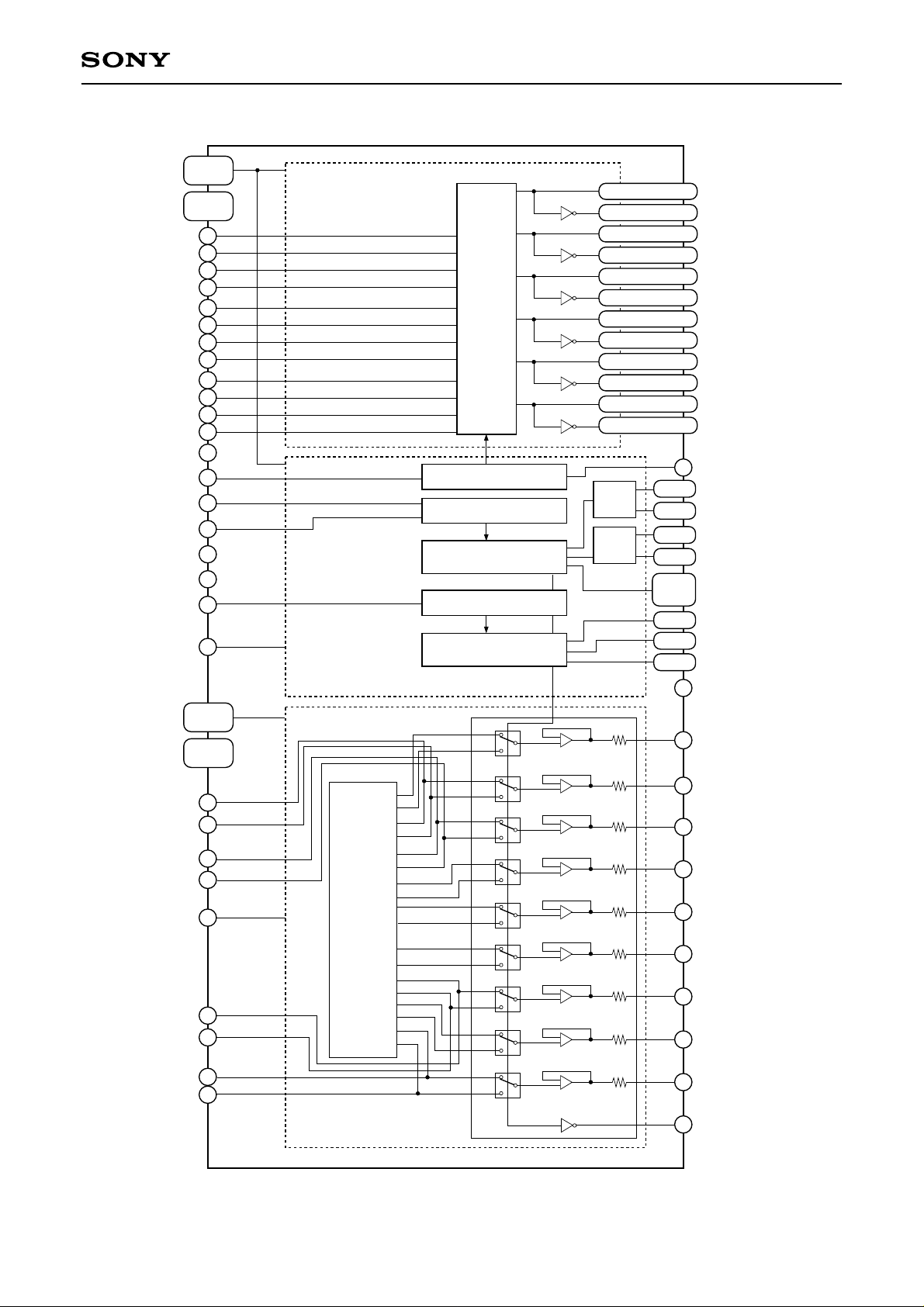

Block Diagram

CXD3521GG

V

DD1

(3.3V)

V

SS1

(GND)

Hsync/DENB

V

DD2

(5.0V)

SS1

(GND)

V

R3

R2

R1

R0

G3

G2

G1

G0

B3

B2

B1

B0

MCK

PCI

SLIN

TESTP

TEST

Vsync

CLR

C10, J6,

L11, M1

B11, G9,

L2

H12

H11

H10

H9

J12

J11

J10

J9

K12

K11

K10

K9

L12

G11

G12

E10

M12

A12

G11

F9

B2, D2,

D7

B4, D3,

F4

Serial/Parallel Transform Block

Timing Generator Block

Power CTR.

H Counter

H Timing Pulse GEN.

V Counter

V Timing Pulse GEN.

M11, L10, M10, M9

J7, M6, L6, K6

F12, F11, E12, E11

D10, A9, B9, C9

L9, M8, L8, K8

M5, L5, K5, J5

B12, C12, D12, A11

D9, A8, B8, C8

J8, M7, L7, K7

M4, L4, M3, L3

C11, D11, A10, B10

D8, A7, B7, C7

E9

Delay

Delay

H4, H3

H2, H1

K2, K1

J2, J1

G4, G3,

G2, G1

M2, L1

J4, J3

K4, K3

F10

F3

R31, R21, R11, R01

XR31, XR21, XR11, XR01

R32, R22, R12, R02

XR32, XR22, XR12, XR02

G31, G21, G11, G01

XG31, XG21, XG11, XG01

G32, G22, G12, G02

XG32, XG22, XG12, XG02

B31, B21, B11, B01

XB31, XB21, XB11, XB01

B32, B22, B12, B02

XB32, XB22, XB12, XB02

PCO

HST1, XHST1

HST2, XHST2

HCK1, XHCK1

HCK2, XHCK2

OE1, XOE1,

OE2, XOE2

VST, XVST

VCK, XVCK

ENB, XENB

TESTO

V0

VH1

VL1

VH2

VL2

VRFSTB

VH6

VL6

VH8

VL8

F2

F1

E1

E3

A1

C2

B1

A2

C4

Resistor

Array

Block

Reference Voltage Driver Block

– 2 –

E2

E4

D1

C1

D4

C3

B3

D5

A3

V1

V2

V3

V4

V5

V6

V7

V8

VCOM

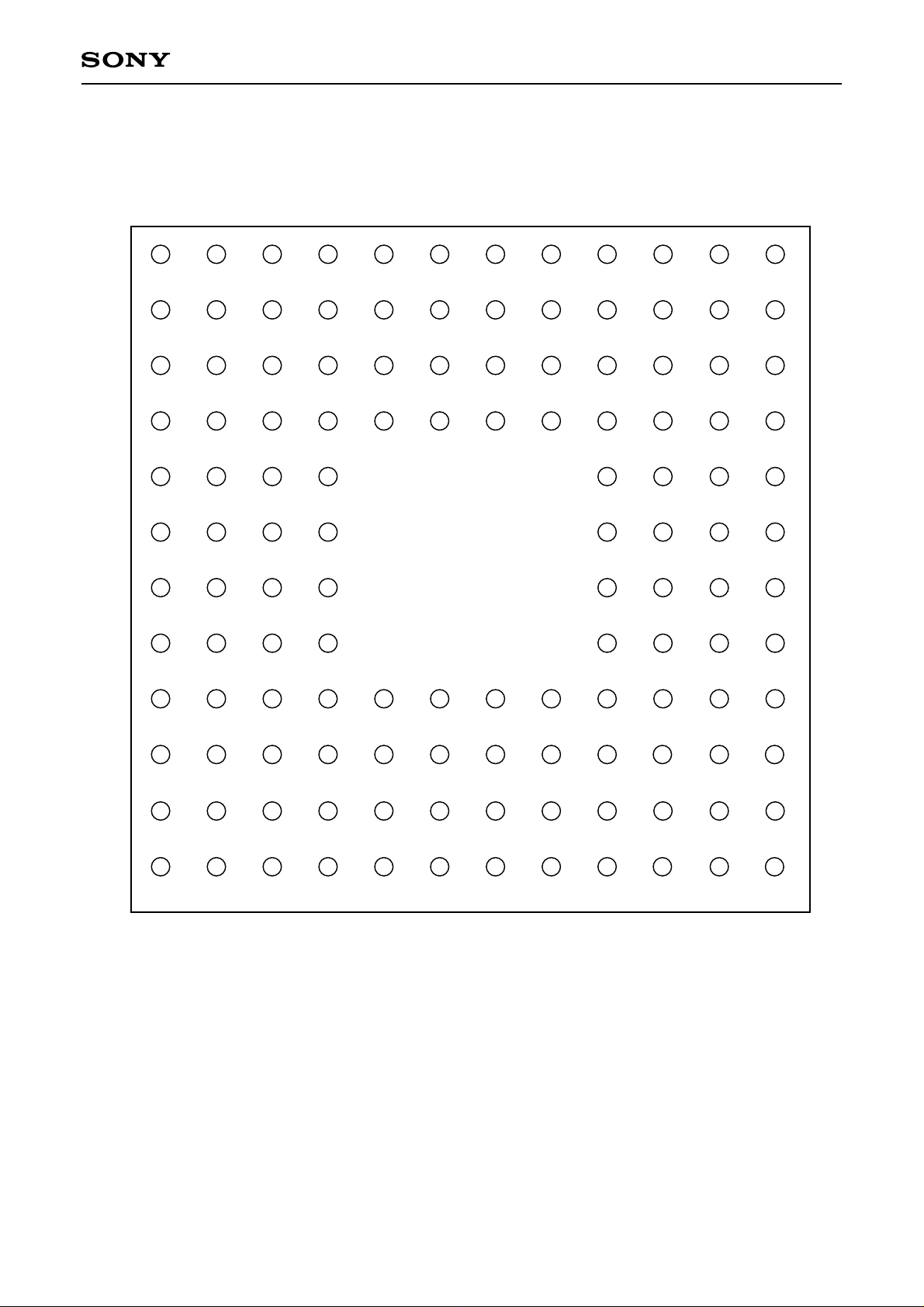

Pin Configuration (Top View)

CXD3521GG

1

234567

8

9

10

11

12

A

VRFSTB

VH8

VCOM

TESTL1

TESTL7

TESTL5

XB22

XG22

XR22

B12

G02

TEST1

B

VL6

DD2

V

V7

V

SS2

TESTL8

TESTL4

XB12

XG12

XR12

B02

SS1

V

G32

C

V4

VH6

V6

VL8

TESTL2

TESTL6

XB02

XG02

XR02

DD1

V

B32

G22

D

V3

DD2

V

V

SS2

V5

V8

TESTL3

V

DD2

XB32

XG32

XR32

B22

G12

E

VH2

V1

VL2

V2

PCO

SLIN

R02

R12

F

VL1

VH1

V0

SS2

V

CLR

TESTO

R22

R32

G

XOE2

OE2

XOE1

OE1

SS1

V

PCI

Vsync

Hsync/

DENB

H

XHST2

HST2

XHST1

HST1

R0

R1

R2

R3

J

XHCK2

HCK2

XVCK

VCK

XG01

DD1

V

XR31

B31

G0

G1

G2

G3

K

XHCK1

HCK1

XENB

ENB

XG11

XR01

B01

G01

B0

B1

B2

B3

L

XVST

SS1

V

XB01

XB21

XG21

XR11

B11

G11

G31

R21

DD1

V

MCK

M

DD1

V

VST

XB11

XB31

XG31

XR21

B21

G21

R01

R11

R31

TESTP

– 3 –

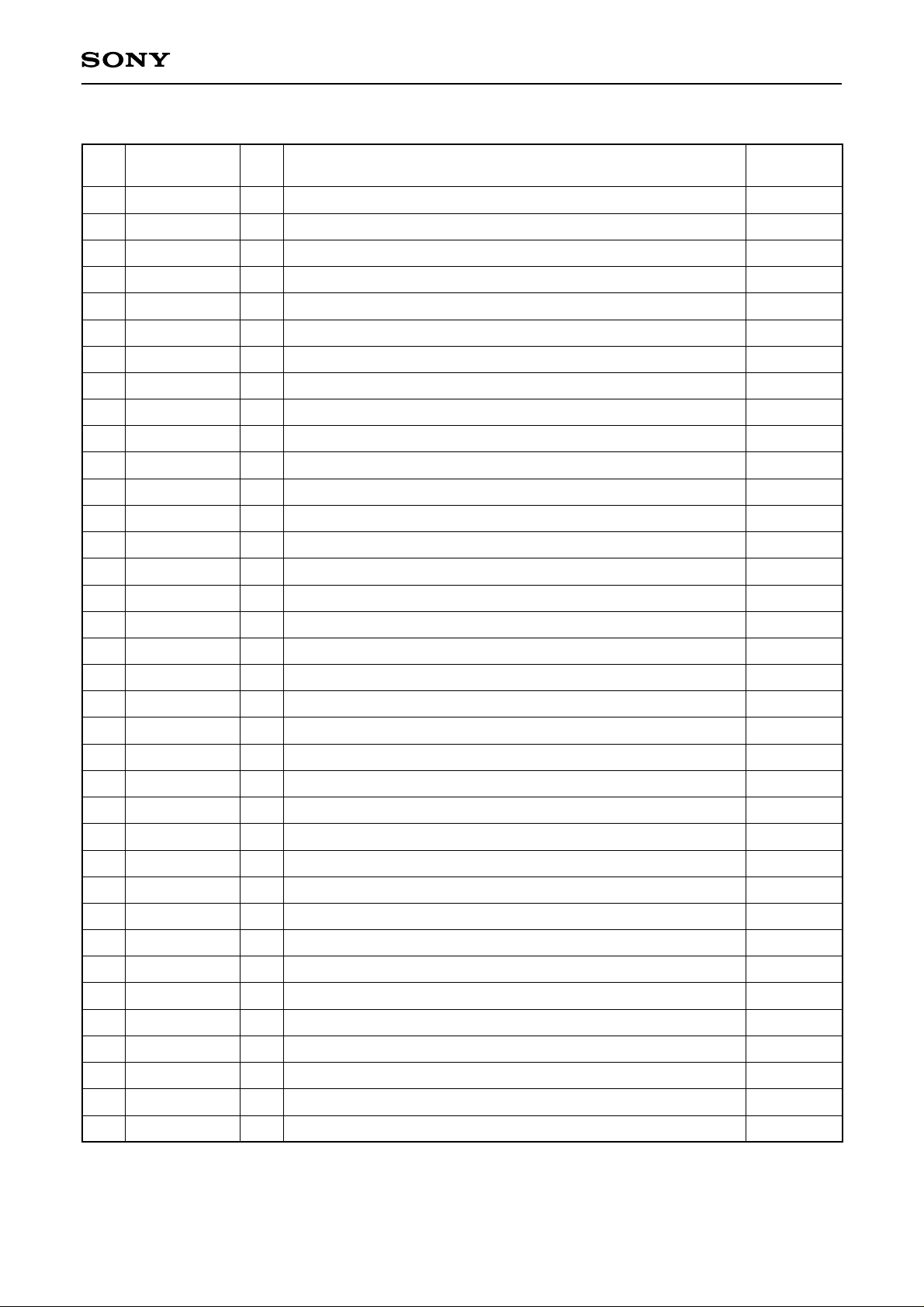

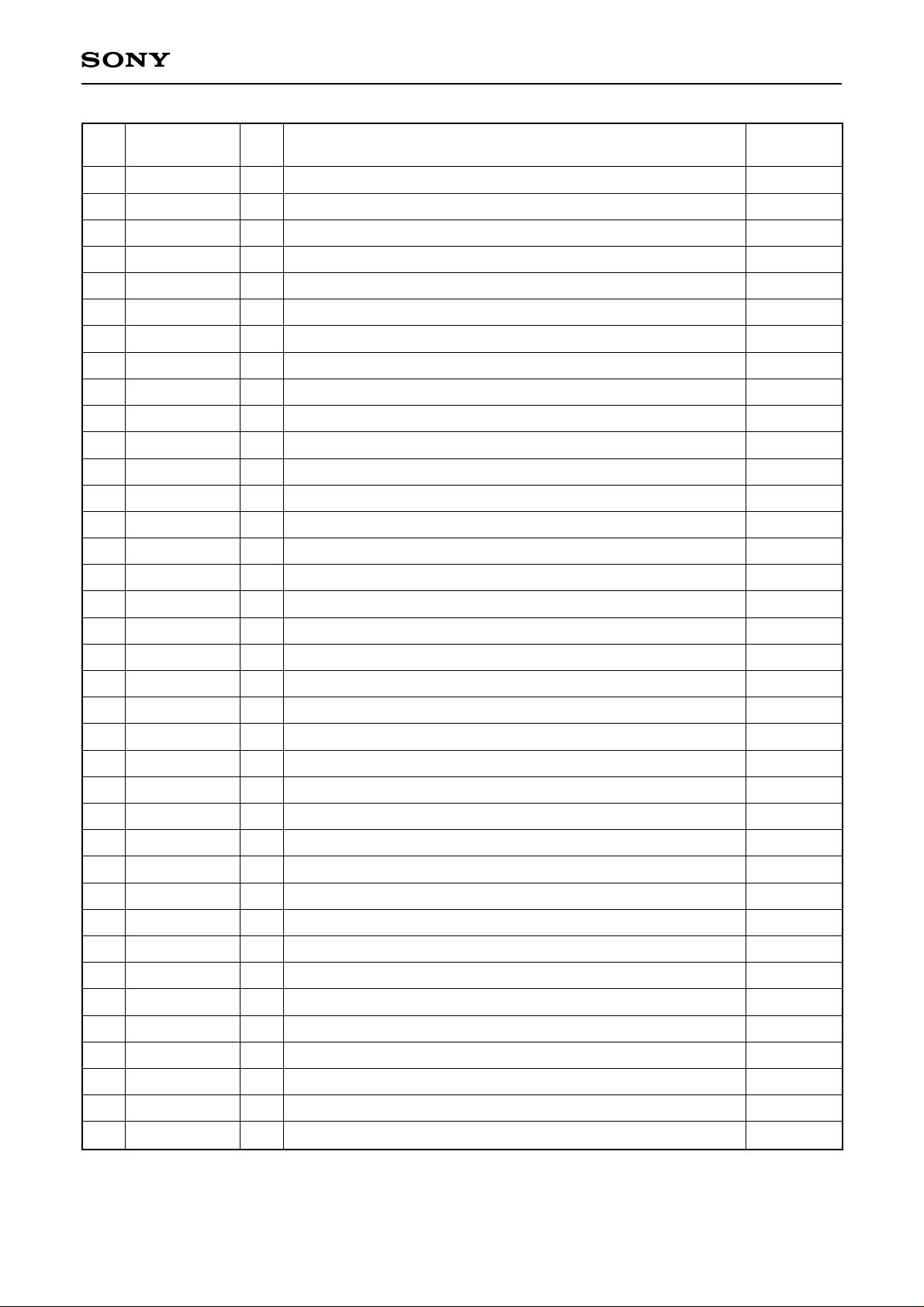

Pin Description

CXD3521GG

Pin

No.

B11

G9

L2

C10

J6

L11

M1

F9

H12

H11

H10

H9

J12

J11

J10

J9

SS1

V

VSS1

VSS1

VDD1

VDD1

VDD1

VDD1

CLR

R3

R2

R1

R0

G3

G2

G1

G0

Symbol

I/O

—

GND (Logic)

—

GND (Logic)

—

GND (Logic)

—

Power supply (3.3V)

—

Power supply (3.3V)

—

Power supply (3.3V)

—

Power supply (3.3V)

I

System reset (Cleared at 0V)

I

Red signal input (MSB)

I

Red signal input

I

Red signal input

I

Red signal input (LSB)

I

Green signal input (MSB)

I

Green signal input

I

Green signal input

I

Green signal input (LSB)

Description

Input pin for

open status

—

—

—

—

—

—

—

∗

UP

—

—

—

—

—

—

—

—

K12

K11

K10

K9

G12

G11

L12

G10

E10

F10

E9

M11

L10

M10

M9

L9

M8

B3

B2

B1

B0

Hsync/DENB

Vsync

MCK

PCI

SLIN

TESTO

PCO

R31

R21

R11

R01

G31

G21

I

Blue signal input (MSB)

I

Blue signal input

I

Blue signal input

I

Blue pulse input (LSB)

I

Hsync pulse input/Data enable signal input

I

Vsync pulse input

I

Dot clock input

I

Power control signal input

I

Sync input signal mode selector switch

O

Test output (Leave it open.)

O

Power control signal output

O

Red signal output

O

Red signal output

O

Red signal output

O

Red signal output

O

Green signal output

O

Green signal output

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

L8

G11

K8

G01

J8

B31

∗

UP: Pull-up (typ. 160kΩ)

O

Green signal output

O

Green signal output

O

Blue signal output

—

—

—

– 4 –

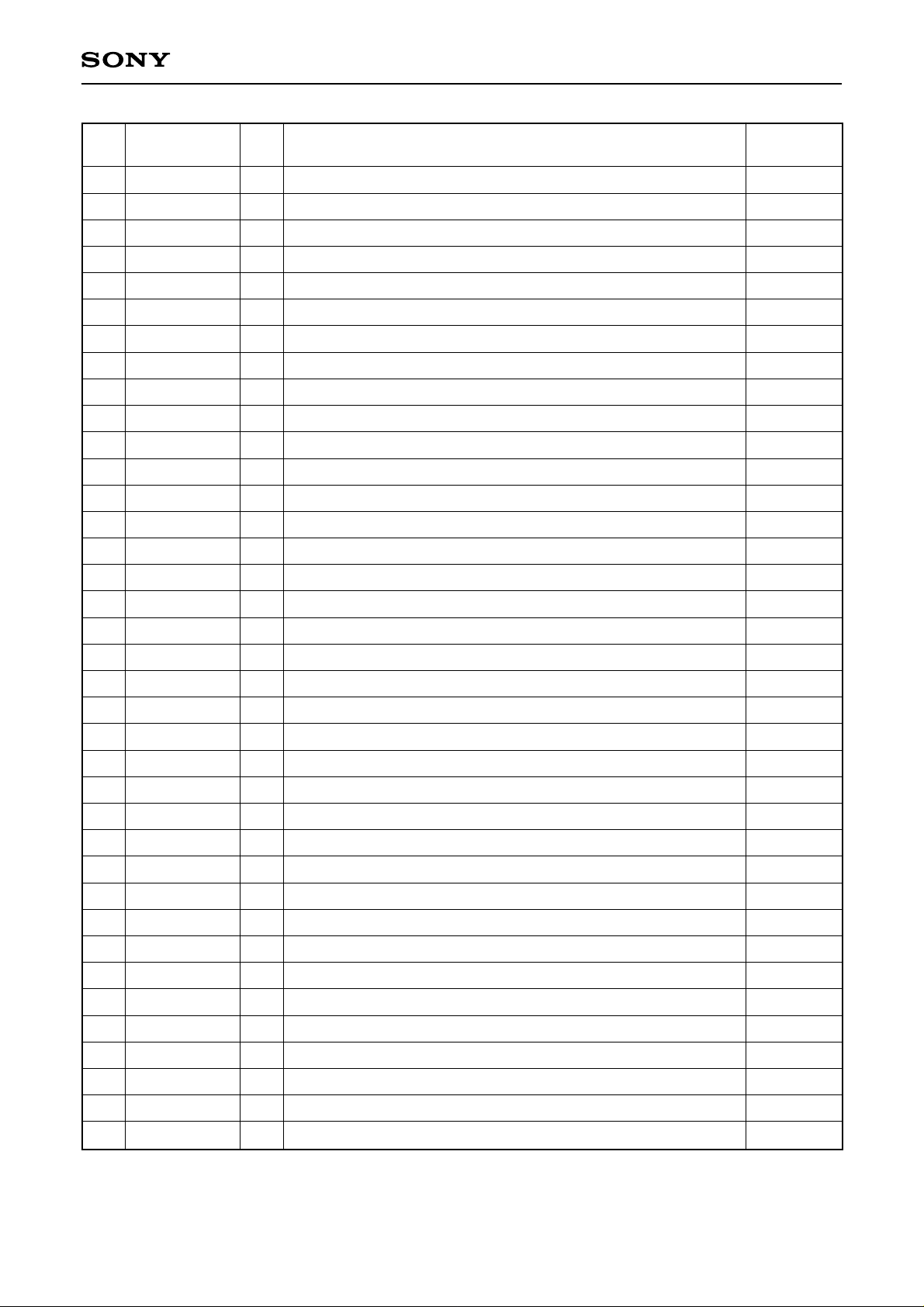

CXD3521GG

Pin

No.

M7

L7

K7

J7

M6

L6

K6

M5

L5

K5

J5

M4

L4

M3

L3

M12

A12

Symbol I/O Description

B21

B11

B01

XR31

XR21

XR11

XR01

XG31

XG21

XG11

XG01

XB31

XB21

XB11

XB01

TESTP

TEST

O

Blue signal output

O

Blue signal output

O

Blue signal output

O

R31 signal inversion output

O

R21 signal inversion output

O

R11 signal inversion output

O

R01 signal inversion output

O

G31 signal inversion output

O

G21 signal inversion output

O

G11 signal inversion output

O

G01 signal inversion output

O

B31 signal inversion output

O

B21 signal inversion output

O

B11 signal inversion output

O

B01 signal inversion output

I

Test input (Connect to GND.)

I

Test input (Connect to GND.)

Input pin for

open status

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

∗

DWN

M2

L1

K4

K3

J4

J3

K2

K1

J2

J1

H4

H3

H2

H1

G4

G3

G2

VST

XVST

ENB

XENB

VCK

XVCK

HCK1

XHCK1

HCK2

XHCK2

HST1

XHST1

HST2

XHST2

OE1

XOE1

OE2

O

VST pulse output

O

VST pulse inversion output

O

ENB pulse output

O

ENB pulse inversion output

O

VCK pulse output

O

VCK pulse inversion output

O

HCK1 pulse output

O

HCK1 pulse inversion output

O

HCK2 pulse output

O

HCK2 pulse inversion output

O

HST1 pulse output

O

HST1 pulse inversion output

O

HST2 pulse output

O

HST2 pulse inversion output

O

OE1 pulse output

O

OE1 pulse inversion output

O

OE2 pulse output

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

G1

XOE2

D8

XB32

A7

XB22

∗

DWN: Pull-down (typ. 180kΩ)

O

O

O

OE2 pulse inversion output

B32 signal inversion output

B22 signal inversion output

– 5 –

—

—

—

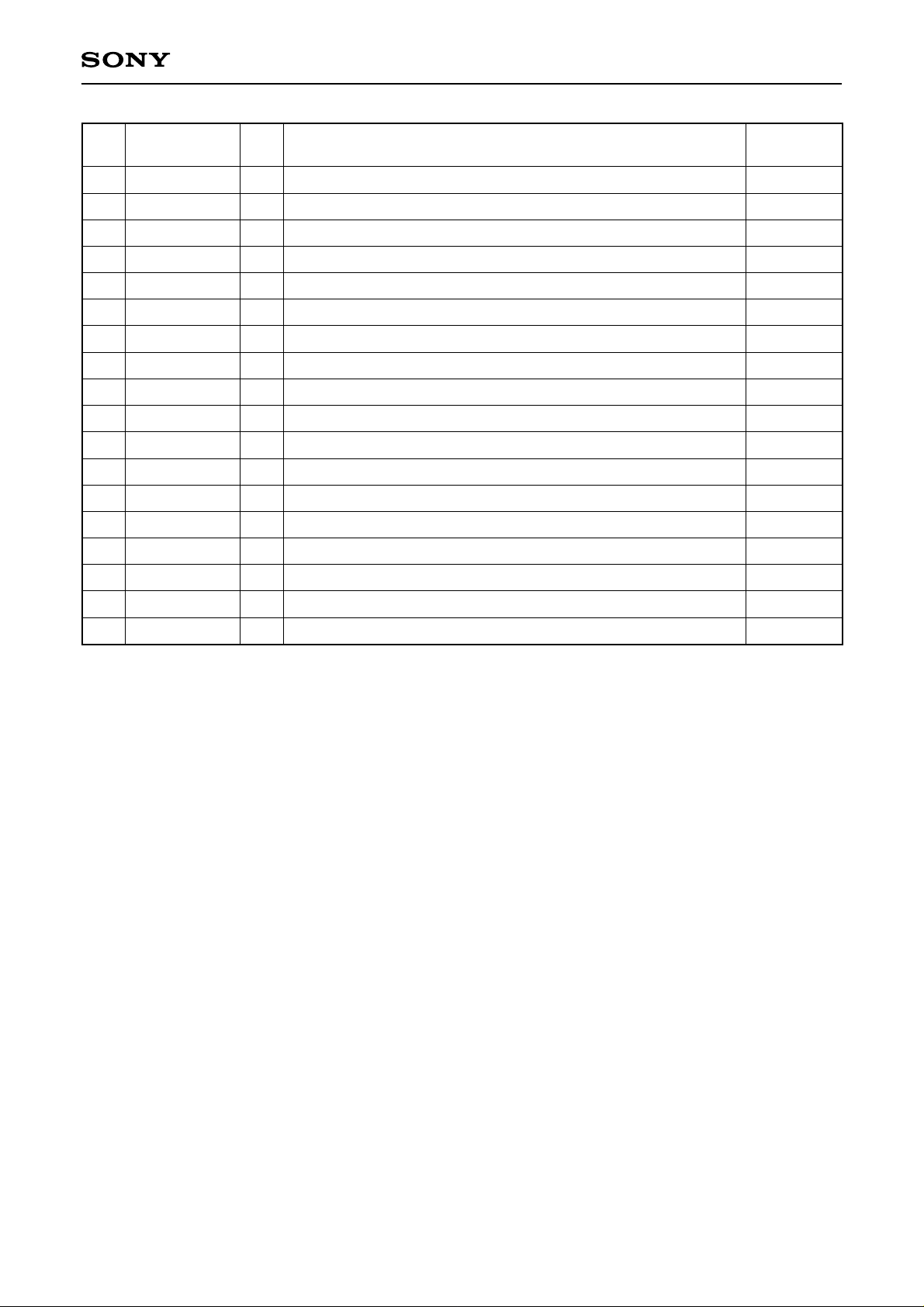

CXD3521GG

Pin

No.

B7

C7

D9

A8

B8

C8

D10

A9

B9

C9

C11

D11

A10

B10

B12

C12

Symbol I/O Description

XB12

XB02

XG32

XG22

XG12

XG02

XR32

XR22

XR12

XR02

B32

B22

B12

B02

G32

G22

O

B12 signal inversion output

O

B02 signal inversion output

O

G32 signal inversion output

O

G22 signal inversion output

O

G12 signal inversion output

O

G02 signal inversion output

O

R32 signal inversion output

O

R22 signal inversion output

O

R12 signal inversion output

O

R02 signal inversion output

O

Blue signal output

O

Blue signal output

O

Blue signal output

O

Blue signal output

O

Green signal output

O

Green signal output

Input pin for

open status

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

D12

A11

F12

F11

E12

E11

B4

D3

F4

B2

D2

D7

A4

C5

D6

B6

A6

G12

G02

R32

R22

R12

R02

VSS2

VSS2

VSS2

VDD2

VDD2

VDD2

TESTL1

TESTL2

TESTL3

TESTL4

TESTL5

O

Green signal output

O

Green signal output

O

Red signal output

O

Red signal output

O

Red signal output

O

Red signal output

—

GND (Analog)

—

GND (Analog)

—

GND (Analog)

—

Power supply (5.0V)

—

Power supply (5.0V)

—

Power supply (5.0V)

O

Test output (Leave it open.)

O

Test output (Leave it open.)

I

Test input (Connect to GND.)

I

Test input (Connect to GND.)

O

Test output (Leave it open.)

—

—

—

—

—

—

—

—

—

—

—

—

—

—

DWN

—

—

∗

A5

TESTL6

C6

TESTL7

B5

TESTL8

F3

V0

∗

DWN: Pull-down (typ. 180kΩ)

I

I

I

O

Test input (Connect to GND.)

Test input (Connect to GND.)

Test input (Connect to GND.)

V0 output

– 6 –

—

—

—

—

CXD3521GG

Pin

No.

E2

E4

D1

C1

D4

C3

B3

D5

A3

A1

F2

F1

E1

E3

C2

B1

Symbol I/O Description

V1

V2

V3

V4

V5

V6

V7

V8

VCOM

VRFSTB

VH1

VL1

VH2

VL2

VH6

VL6

O

V1 output

O

V2 output

O

V3 output

O

V4 output

O

V5 output

O

V6 output

O

V7 output

O

V8 output

O

VCOM output

I

Reference voltage driver on/off selector switch

I

VH1 input

I

VL1 input

I

VH2 input

I

VL2 input

I

VH6 input

I

VL6 input

Input pin for

open status

—

—

—

—

—

—

—

—

—

∗

DWN

—

—

—

—

—

—

A2

VH8

C4

VL8

∗

DWN: Pull-down (typ. 180kΩ)

I

I

VH8 input

VL8 input

—

—

– 7 –

Loading...

Loading...