Sony CXD3504R Datasheet

CXD3504R

Selective Delay Line for LCD

Description

The CXD3504R is a selective delay line IC for

performing signal processing during dot and line

inverted drive of liquid crystal panels for Sony

projectors.

This chip has three built-in 10-bit × 1200-word 1H

delay lines, and data path with or without a 1H delay

can be selected by the control pins.

Features

• Supports dot and line inverted drive of liquid crystal

panels for Sony projectors

• Three built-in 10-bit × 1200-word 1H delay lines

• Data path with or without a 1H delay can be selected

by the control pins.

Applications

LCD projectors, etc.

Structure

Silicon gate CMOS IC

Absolute Maximum Ratings (Vss = 0V)

• Supply voltage VDD –0.3 to +4.6 V

• Input voltage VI –0.3 to VDD + 0.3 V

• Output voltage VO –0.3 to VDD + 0.3 V

• Operating temperature Topr –30 to +75 °C

• Storage temperature Tstg –55 to +125 °C

• Allowable power dissipation

PDmax 850mW (Ta ≤ 75°C)

Recommended Operating Conditions

• Supply voltage VDD 3.0 to 3.6 V

• Operating temperature Topr –30 to +75 °C

• Input voltage VIN 0 to VDD V

– 1 –

E99815-PS

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

176 pin LQFP (Plastic)

– 2 –

CXD3504R

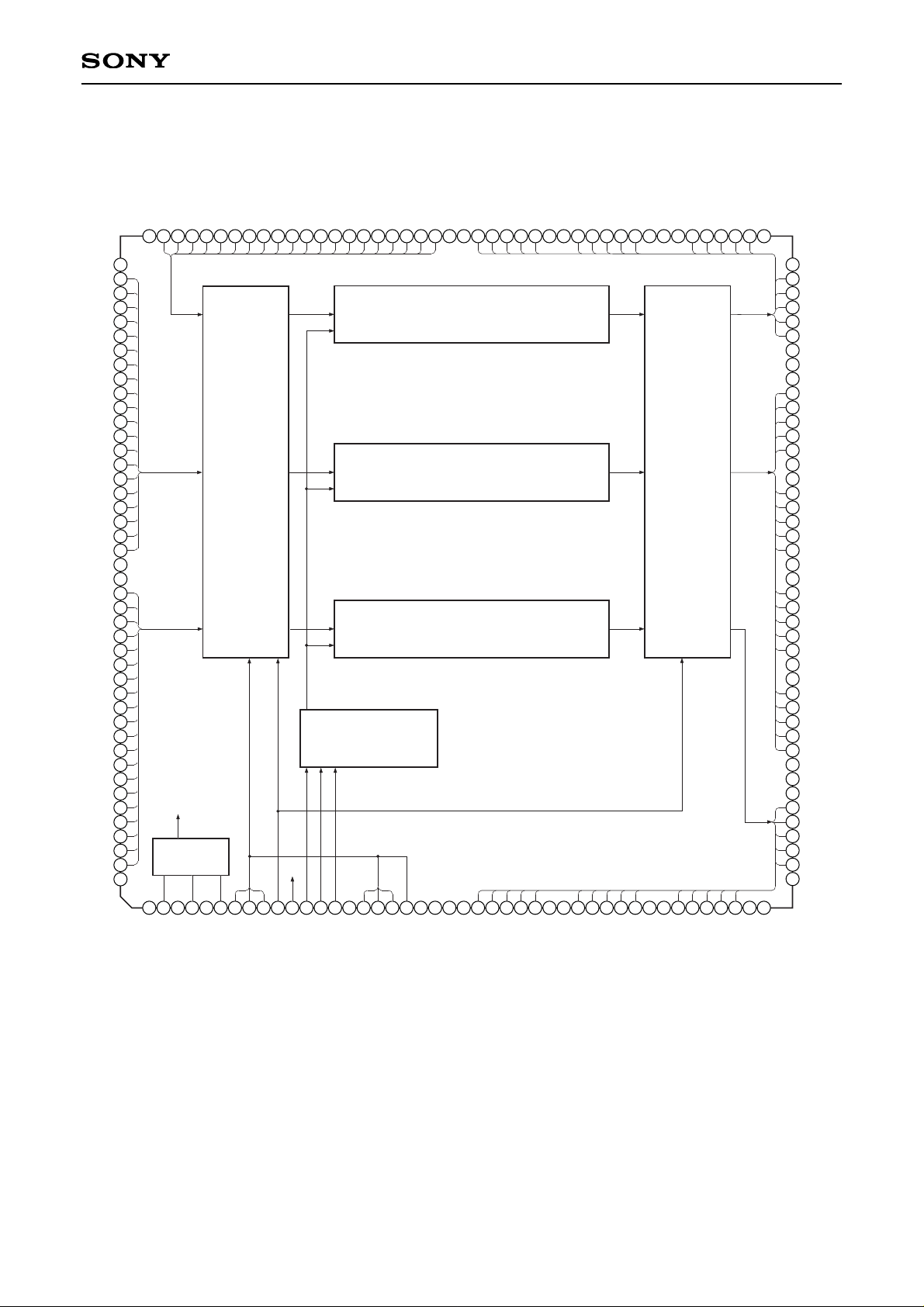

Block Diagram

117118119120121122123124125126127128129130131132

VDD

R2IN0

R2IN1

R2IN2

R2IN3

R2IN4

R2IN5

R2IN6

R2IN7

R2IN8

R2IN9

R1IN0

R1IN1

R1IN2

R1IN3

R1IN4

111112113114115116

R1IN5

R1IN6

R1IN7

R1IN8

R1IN9

V

SS

110

VDD

109

R1OUT9

108

R1OUT8

107

R1OUT7

106

R1OUT6

105

R1OUT5

104

VSS

103

VDD

102

R1OUT4

101

R1OUT3

100

R1OUT2

R1OUT1

R1OUT0

VSSVDD

TEST3

R2OUT9

R2OUT8

R2OUT7

R2OUT6

R2OUT5

V

SS

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

85

86

87

88

99 98 97 96 95 94 93 92 91 90 89

79

80

81

82

83

84

V

SS

B1OUT5

B1OUT6

B1OUT7

B1OUT8

B1OUT9

TEST1

V

DD

VSS

G2OUT0

G2OUT1

G2OUT2

G2OUT3

G2OUT4

V

DD

VSS

G2OUT5

G2OUT6

G2OUT7

G2OUT8

G2OUT9

V

DD

VSS

G1OUT0

G1OUT1

G1OUT2

G1OUT3

G1OUT4

V

DD

VSS

G1OUT5

G1OUT6

G1OUT7

G1OUT8

G1OUT9

TEST2

V

DD

VSS

R2OUT0

R2OUT1

R2OUT2

R2OUT3

R2OUT4

V

DD

169

170

171

172

173

174

175

162

161

160

159

158

157

163

164

165

166

167

168

176

VDD

B2IN0

B2IN1

B2IN2

B2IN3

B2IN5

B2IN4

B2IN6

B2IN7

B2IN8

B2IN9

B1IN0

B1IN1

B1IN2

B1IN3

B1IN4

B1IN5

B1IN6

B1IN7

B1IN8

149

150

151

152

153

154

155

142

141

140

139

138

137

143

144

145

146

147

148

156

B1IN9

V

SS

VDD

G2IN0

G2IN1

G2IN3

G2IN2

G2IN4

G2IN5

G2IN6

G2IN7

G2IN8

G2IN9

G1IN0

G1IN1

G1IN2

G1IN3

G1IN4

G1IN5

G1IN6

136

135

134

G1IN7

G1IN8

G1IN9

133

VSS

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40

VSS

PECLCK

NC

CMOSCK

V

SS

CLKSEL

SELRA

SELGA

SELBA

SELB

XCLR

HD

HDSEL

HDEDGE

NC

REDGE

GEDGE

BEDGE

POLSLA

NC

NC

V

DD

VSS

B2OUT0

B2OUT1

B2OUT2

B2OUT3

B2OUT4

V

DD

VSS

B2OUT5

B2OUT6

41 42 43 44

B1OUT3

B1OUT4

TEST0

V

DD

B2OUT7

B2OUT8

B2OUT9

V

DD

VSS

B1OUT0

B1OUT1

B1OUT2

R CH FIFO

G CH FIFO

TIMING

GENERATOR

INPUT

LATCH

&

SELECT

OUTPUT

SELECT

&

LATCH

CLK SEL

B CH FIFO

– 3 –

CXD3504R

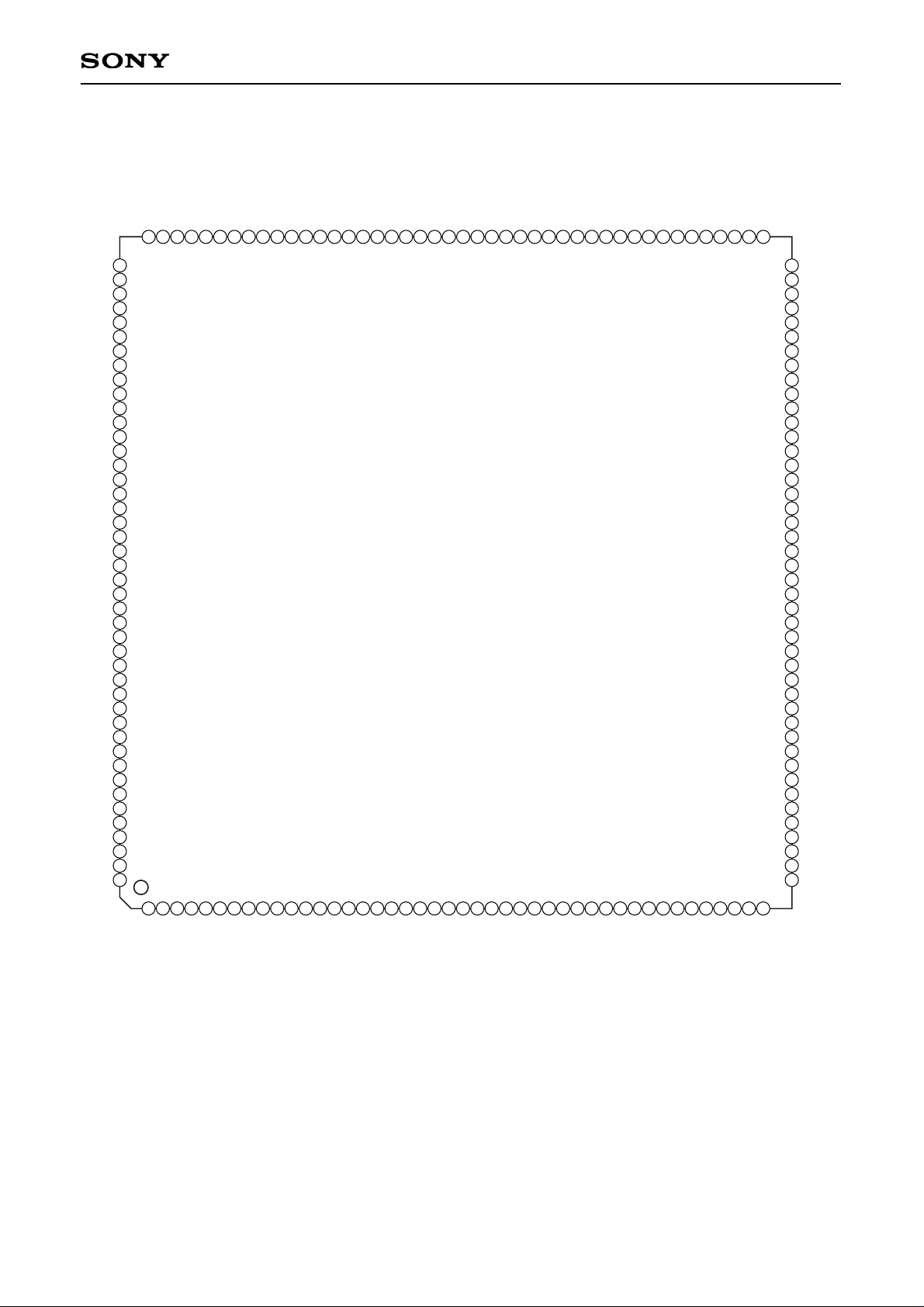

Pin Configuration

117118119120121122123124125126127128129130131132

VDD

R2IN0

R2IN1

R2IN2

R2IN3

R2IN4

R2IN5

R2IN6

R2IN7

R2IN8

R2IN9

R1IN0

R1IN1

R1IN2

R1IN3

R1IN4

111112113114115116

R1IN5

R1IN6

R1IN7

R1IN8

R1IN9

V

SS

110

VDD

109

R1OUT9

108

R1OUT8

107

R1OUT7

106

R1OUT6

105

R1OUT5

104

VSS

103

VDD

102

R1OUT4

101

R1OUT3

100

R1OUT2

R1OUT1

R1OUT0

VSSVDD

TEST3

R2OUT9

R2OUT8

R2OUT7

R2OUT6

R2OUT5

V

SS

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

85

86

87

88

99 98 97 96 95 94 93 92 91 90 89

79

80

81

82

83

84

V

SS

B1OUT5

B1OUT6

B1OUT7

B1OUT8

B1OUT9

TEST1

V

DD

VSS

G2OUT0

G2OUT1

G2OUT2

G2OUT3

G2OUT4

V

DD

VSS

G2OUT5

G2OUT6

G2OUT7

G2OUT8

G2OUT9

V

DD

VSS

G1OUT0

G1OUT1

G1OUT2

G1OUT3

G1OUT4

V

DD

VSS

G1OUT5

G1OUT6

G1OUT7

G1OUT8

G1OUT9

TEST2

V

DD

VSS

R2OUT0

R2OUT1

R2OUT2

R2OUT3

R2OUT4

V

DD

169

170

171

172

173

174

175

162

161

160

159

158

157

163

164

165

166

167

168

176

VDD

B2IN0

B2IN1

B2IN2

B2IN3

B2IN5

B2IN4

B2IN6

B2IN7

B2IN8

B2IN9

B1IN0

B1IN1

B1IN2

B1IN3

B1IN4

B1IN5

B1IN6

B1IN7

B1IN8

149

150

151

152

153

154

155

142

141

140

139

138

137

143

144

145

146

147

148

156

B1IN9

V

SS

VDD

G2IN0

G2IN1

G2IN3

G2IN2

G2IN4

G2IN5

G2IN6

G2IN7

G2IN8

G2IN9

G1IN0

G1IN1

G1IN2

G1IN3

G1IN4

G1IN5

G1IN6

136

135

134

G1IN7

G1IN8

G1IN9

133

VSS

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40

VSS

PECLCK

NC

CMOSCK

V

SS

CLKSEL

SELRA

SELGA

SELBA

SELB

XCLR

HD

HDSEL

HDEDGE

NC

REDGE

GEDGE

BEDGE

POLSLA

NC

NC

V

DD

VSS

B2OUT0

B2OUT1

B2OUT2

B2OUT3

B2OUT4

V

DD

VSS

B2OUT5

B2OUT6

41 42 43 44

B1OUT3

B1OUT4

TEST0

V

DD

B2OUT7

B2OUT8

B2OUT9

V

DD

VSS

B1OUT0

B1OUT1

B1OUT2

– 4 –

CXD3504R

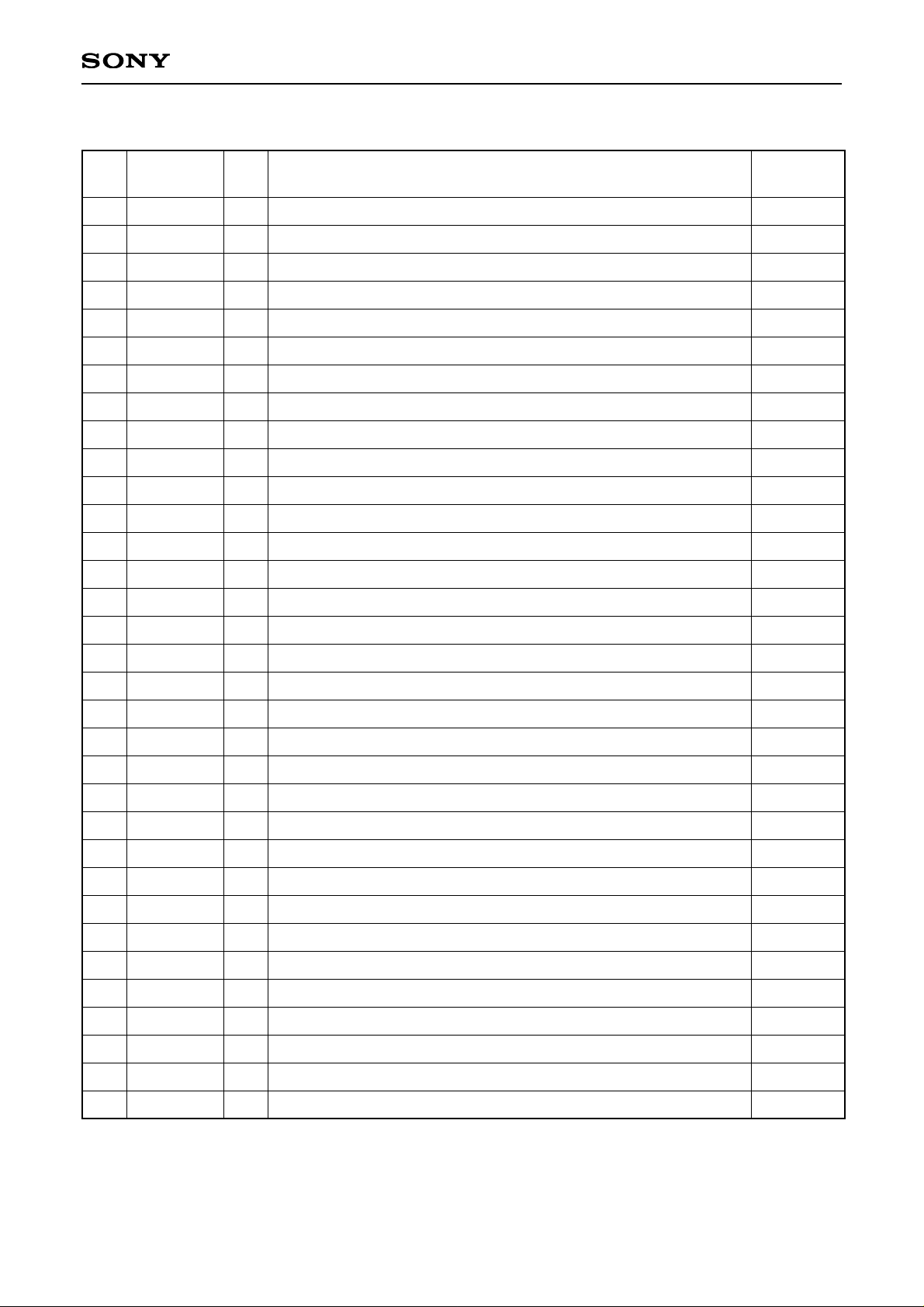

Pin Description

∗1

Connect to GND or VDD when using CMOS clock.

∗2

Connect to GND or VDD when using small amplitude clock.

Pin

No.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

Symbol

VSS

PECLCK

NC

CMOSCK

VSS

CLKSEL

SELRA

SELGA

SELBA

SELB

XCLR

HD

HDSEL

HDEDGE

NC

REDGE

GEDGE

BEDGE

POLSLA

NC

NC

VDD

VSS

B2OUT0

B2OUT1

B2OUT2

B2OUT3

B2OUT4

VDD

VSS

B2OUT5

B2OUT6

B2OUT7

I/O

P

I

I

P

I

I

I

I

I

I

I

I

I

I

I

I

I

P

P

O

O

O

O

O

P

P

O

O

O

Description

GND

Very little amp. clock input

∗1

CMOS clock input

∗2

GND

0: PECL, 1: CMOS

SELA (Data path selection A) for R

SELA (Data path selection A) for G

SELA (Data path selection A) for B

Data path selection B

0: Direct Reset

Horizontal sync signal input

HD selection (0: ↓, 1: ↑)

CK trigger selection of HD (0: ↓, 1: ↑)

Reserve

CK trigger selection of R (0: ↓, 1: ↑)

CK trigger selection of G (0: ↓, 1: ↑)

CK trigger selection of B (0: ↓, 1: ↑)

SELA polarity selection

Power supply

GND

B2 output

B2 output

B2 output

B2 output

B2 output

Power Supply

GND

B2 output

B2 output

B2 output

Input pin for

open status

L

L

L

L

L

H

L

L

L

L

L

L

Loading...

Loading...