Sony CXD3029R Datasheet

CXD3029R

Description

The CXD3029R is a digital signal processor LSI for CD

players. This LSI incorporates a digital servo, high & bass

boost, shock-proof memory controller, 1-bit DAC and

analog low-pass filter.

Features

• All digital signal processing during playback is performed

with a single chip

• Highly integrated mounting possible due to a built-in RAM

Digital Signal Processor (DSP) Block

• Supports CAV (Constant Angular Velocity) playback

• Frame jitter free

• 0.5× to 4× speed continuous playback possible

• Allows relative rotational velocity readout

• Wide capture range playback mode

• Spindle rotational velocity following method

• Supports 1× to 4× speed playback

• Supports variable pitch playback

• The bit clock, which strobes the EFM signal, is generated

by the digital PLL.

• EFM data demodulation

• Enhanced EFM frame sync signal protection

• Refined super strategy-based powerful error correction

C1: double correction, C2: quadruple correction

Supported during 4× speed playback

• Noise reduction during track jumps

• Auto zero-cross mute

• Subcode demodulation and subcode-Q data error

detection

• Digital spindle servo

• 16-bit traverse counter

• Asymmetry correction circuit

• CPU interface on serial bus

• Error correction monitor signal, etc. output from a new

CPU interface

• Servo auto sequencer

• Fine search performs track jumps with high accuracy

• Digital audio interface outputs

• Digital level meter, peak meter

• Bilingual compatible

• VCO control mode

• CD TEXT data demodulation

• Digital Out can be generated from the audio serial input.

(also supported after shock-proof and digital bass boost

processing, subcode-Q addition function)

Digital Servo (DSSP) Block

• Microcomputer software-based flexible servo control

• Offset cancel function for servo error signal

• Auto gain control function for servo loop

• E:F balance, focus bias adjustment functions

• Surf jump function supporting micro two-axis

• Tracking filter: 6 stages

Focus filter: 5 stages

Shock-proof Memory Controller Block

• Supports an external 4M-bit/16M-bit DRAM

• Time axis-based data linking

• ADPCM compression method (uncompressed/4 bits/

6 bits/8 bits)

Digital Filter, DAC and Analog Low-pass Filter Blocks

• Digital dynamic bass boost and high boost

Bass Boost:4th-order IIR 24dB/Oct

+10dB/+14dB/+18dB/+22dB

High Boost: Second-order IIR 12dB/Oct

+4dB/+6dB/+8dB/+10dB

• Independent turnover frequency selection possible

Bass Boost: 125Hz/160Hz/200Hz

High Boost: 5kHz/7kHz

• Digital dynamics (compressor)

Volume increased by +5dB at low level

• 8× oversampling digital filter

(attenuation: 61dB, ripple within band: ±0.0075dB)

• Digital signal output possible after boost

• Serial data format selectable from (output) 20 bits/

18 bits/16 bits (rearward truncation, MSB first)

• Digital attenuation: –∞, –60 to +6dB, 2048 steps (linear)

• Soft mute

• Digital de-emphasis

• High-cut filter

Applications

CD players

Structure

Silicon gate CMOS IC

Absolute Maximum Ratings

• Supply voltage V

DD, AVDD –0.3 to +4.6 V

• Input voltage V

I –0.3 to +4.6 V

(V

SS – 0.3V to VDD + 0.3V)

• Output voltage V

O –0.3 to +4.6 V

•

Storage temperature

Tstg –40 to +125 °C

• Supply voltage difference

AV

SS – VSS –0.3 to +0.3 V

AV

DD – VDD –0.3 to +0.3V(AVDD < 2.2V)

AV

DD – VDD –0.3 to +1.4V(AVDD = 2.2 to 3.6V)

Recommended Operating Conditions

• Supply voltage V

DD , AVDD0, 3 2.2 to 3.6 V

AV

DD1, 2, DVDD VDD to 3.6 V

•

Operating temperature

Topr –20 to +75 °C

I/O Pin Capacitance

• Input capacitance C

I 12 (max.) pF

• Output capacitance C

O 12 (max.) pF

Note) Measurement conditions V

DD = VI = 0V

f

M = 1MHz

– 1 –

E01429-PS

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

120 pin LQFP (Plastic)

CD Digital Signal Processor with Built-in Digital Servo +

Shock-proof Memory Controller + Digital High & Bass Boost

– 2 –

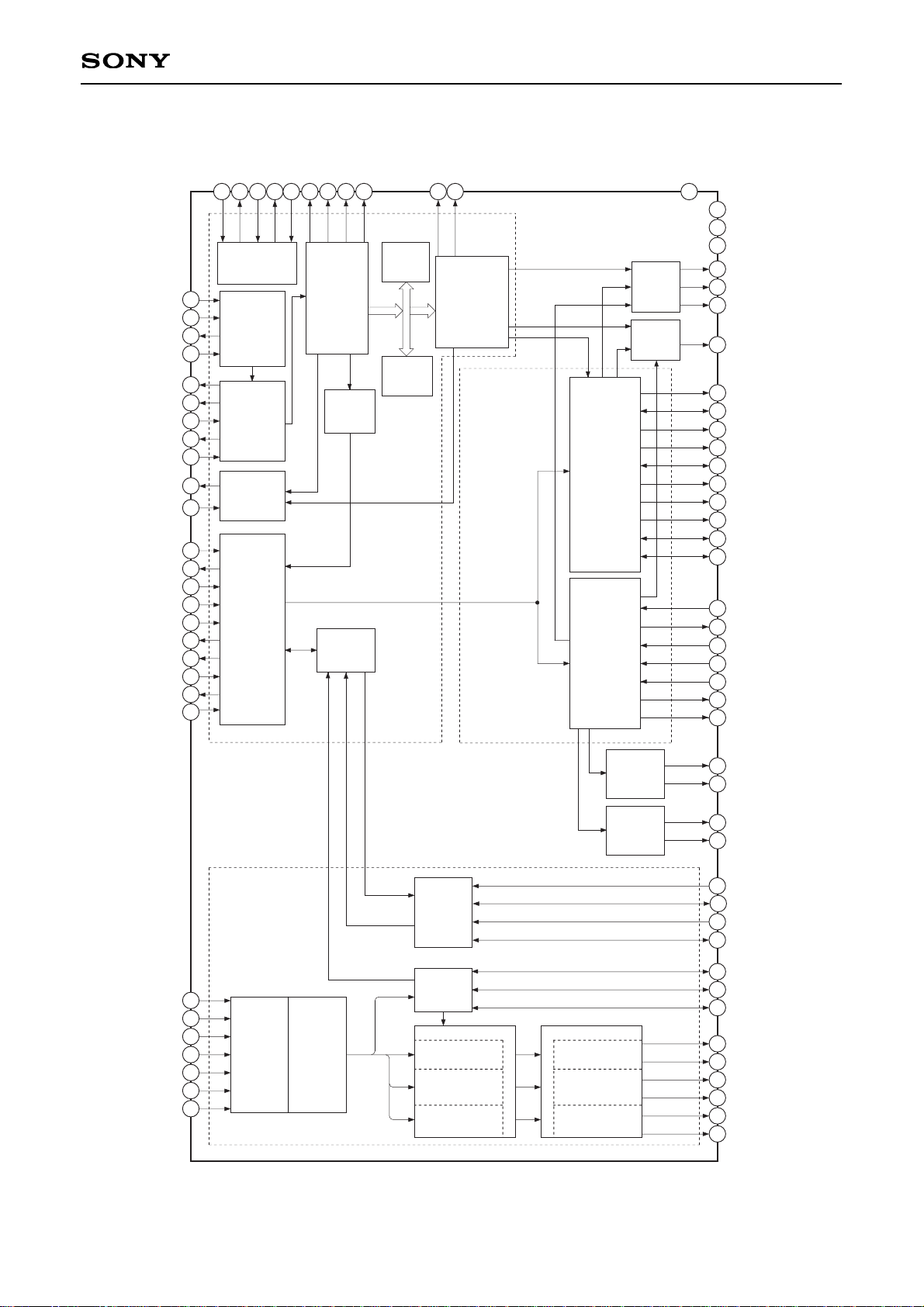

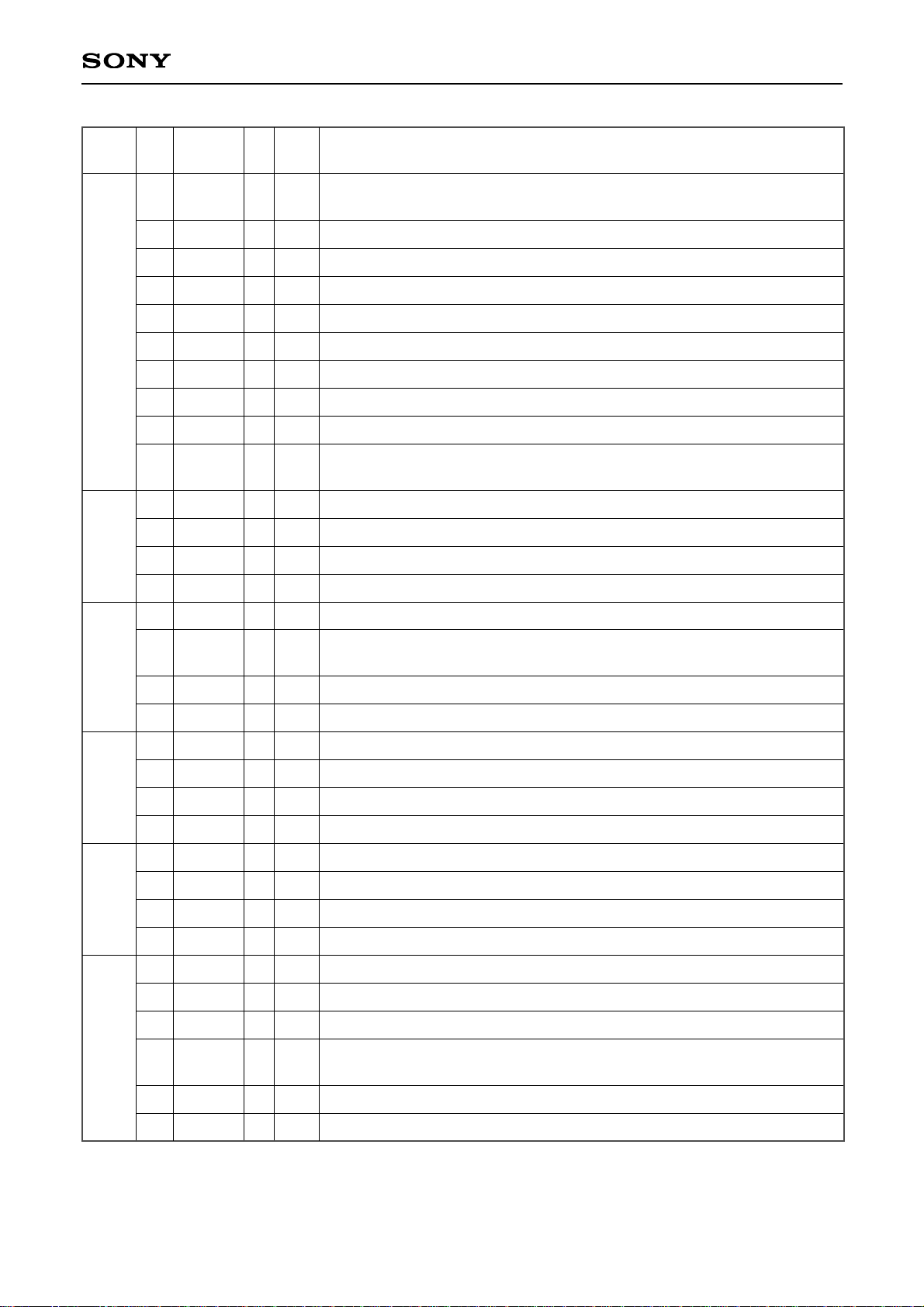

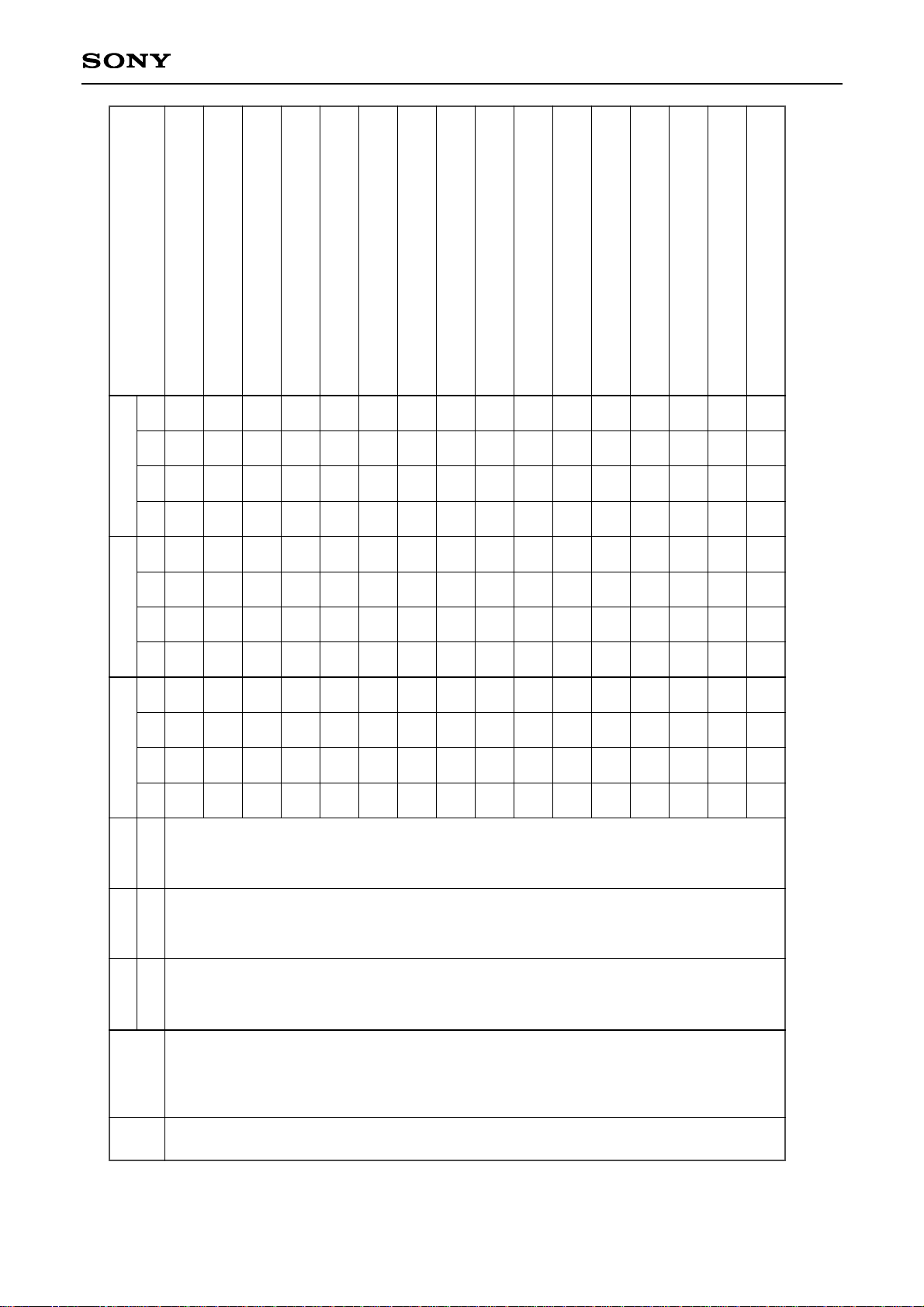

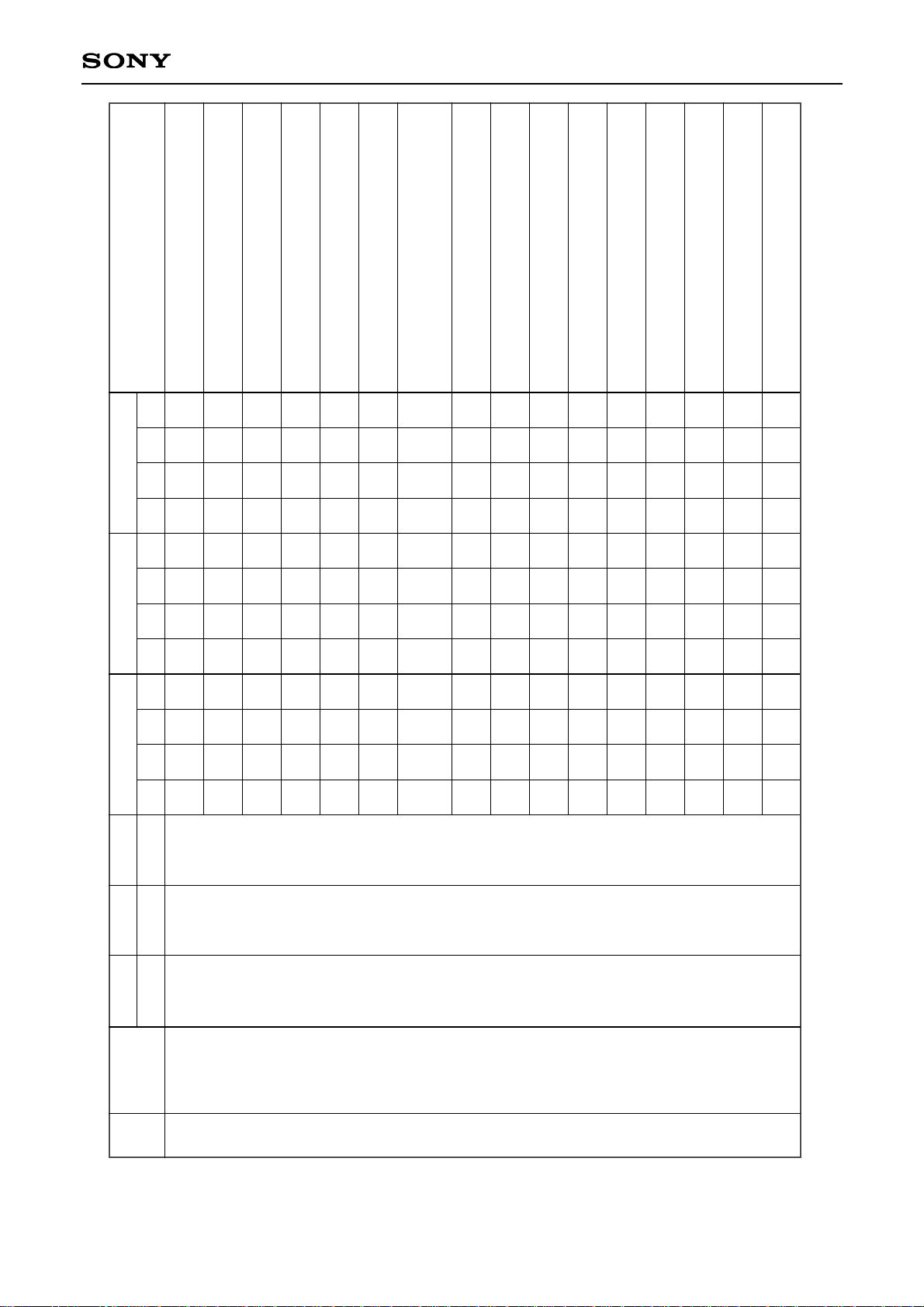

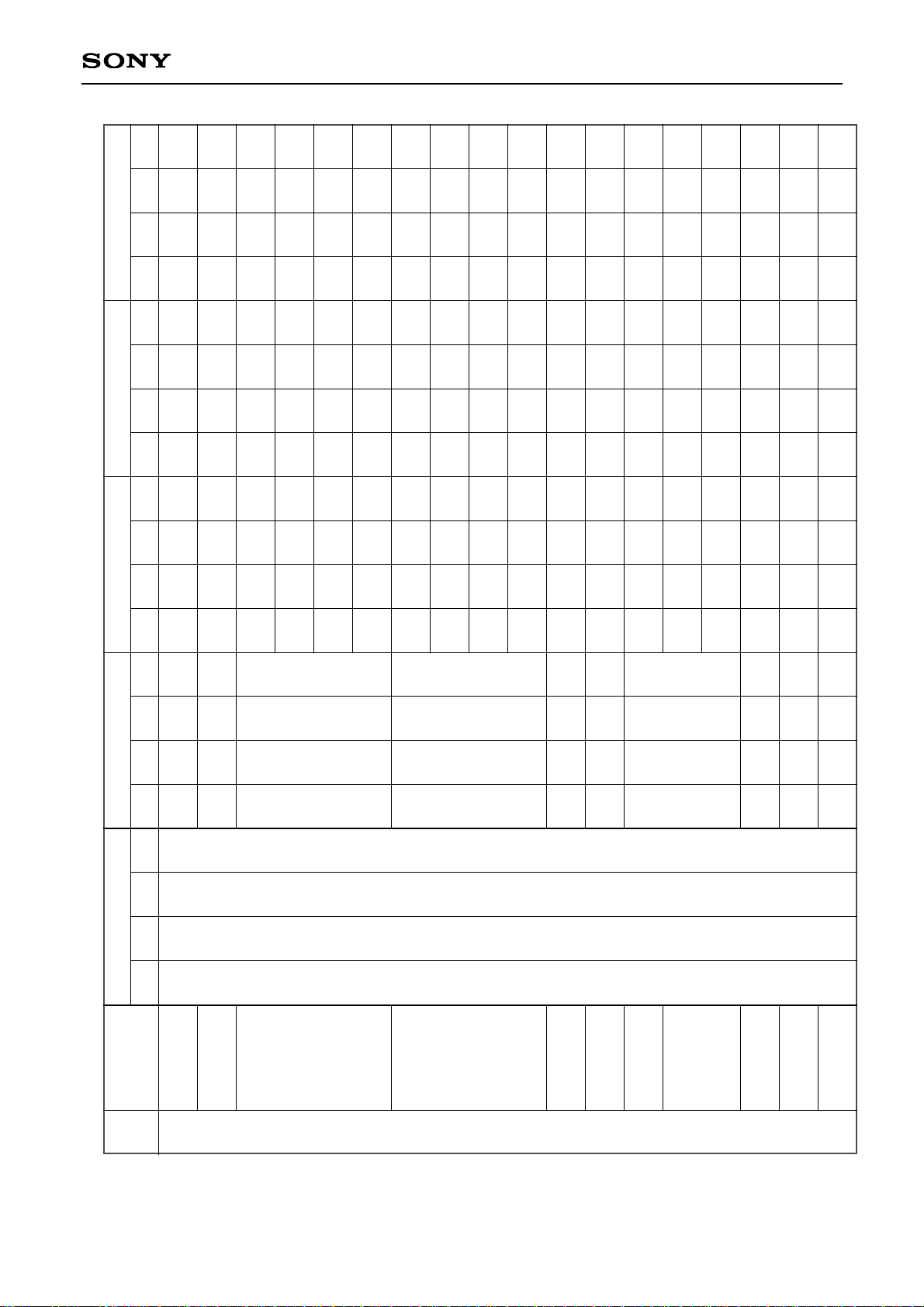

CXD3029R

A0 to A11

D0 to D3

XEMP

XWIH

XQOK

BCK

LRCK

DOUT

PCMD

XRST

TEST

TES1

D/A

Interface

EFM

demodulator

Error

Corrector

32K

RAM

Sub Code

Processor

Clock

Generator

Asymmetry

Corrector

Digital

PLL

CPU

Interface

C2PO

WFCK

EMPH

GFS

XUGF

XTAI

RFAC

ASYI

ASYO

BIAS

FILO

FILI

PCO

CLTV

MDP

PWMI

SENS

DATA

XLAT

CLOK

SCOR

SBSO

EXCK

WDCK

XTAO

VPCO

VCTL

XPCK

SQSO

SQCK

Digital

CLV

SERVO

Interface

ATSK

SCLK

SSTP

MIRR

DFCT

FOK

MIRR

DFCT

FOK

SERVO DSP

FOCUS SERVO

TRACKING

SERVO

SLED SERVO

PWM GENERATOR

FOCUS PWM

GENERATOR

TRACKING PWM

GENERATOR

SLED PWM

GENERATOR

FFDR

FRDR

TFDR

TRDR

SFDR

SRDR

RFDC

CE

TE

SE

FE

VC

IGEN

OPAmp

Analog SW

A/D

Converter

COUT

XRAS

XWE

XCAS

XWRE

XRDE

Selecter

Digital

OUT

XTSL

Servo

Auto

Sequencer

XSOE

SYSM

LRMU

LRCKI

BCKI

PCMDI

LPF

AOUT1

VREFL

LPF

AOUT2

VREFR

DAC

HPL

HPR

Signal

Processor

Block

Servo Block

Memory Controller,

Bass Boost Block

Shock-proof

Memory

Controller +

Compression/

Expansion

TEST1 to 4

Block Diagram

– 3 –

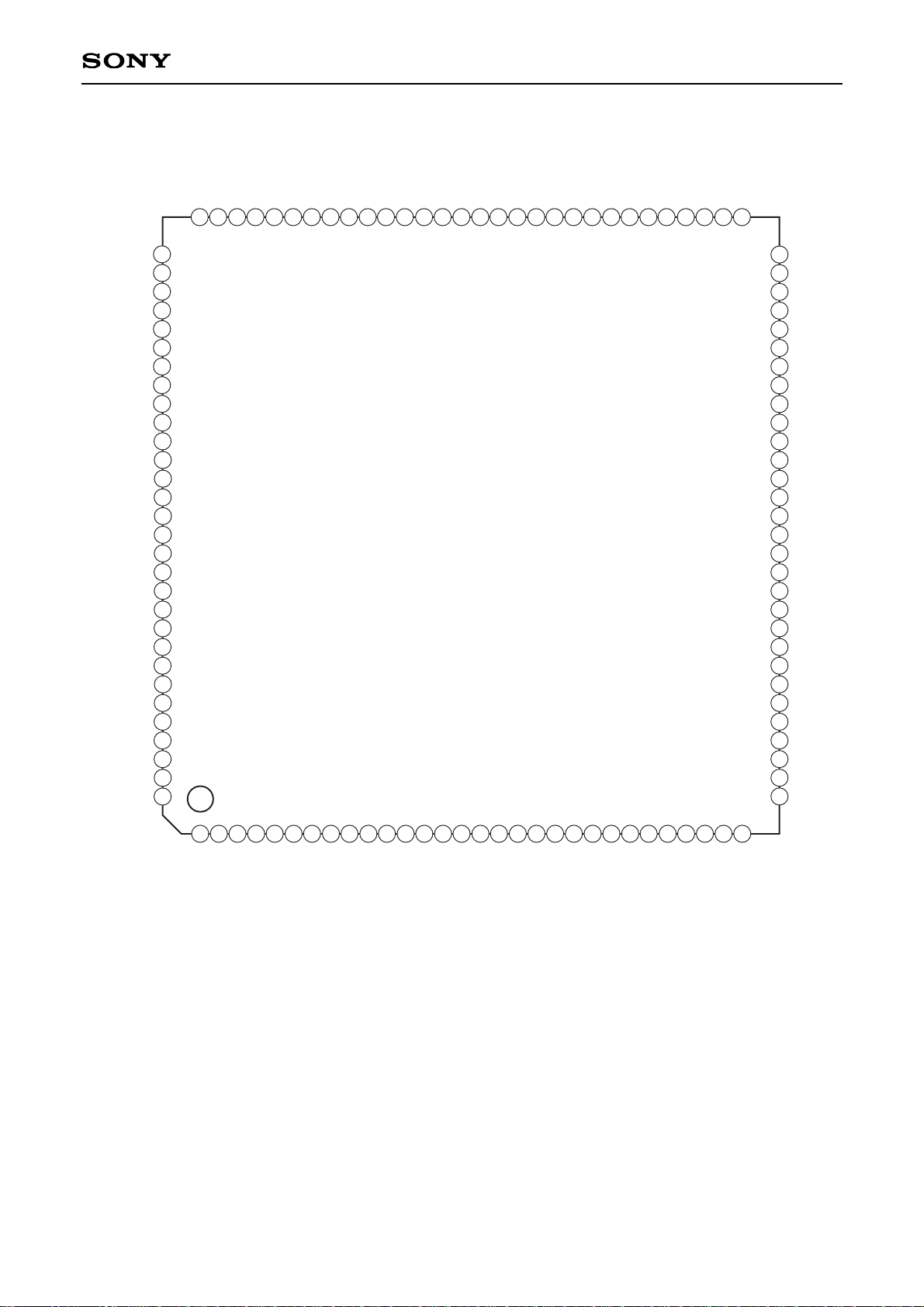

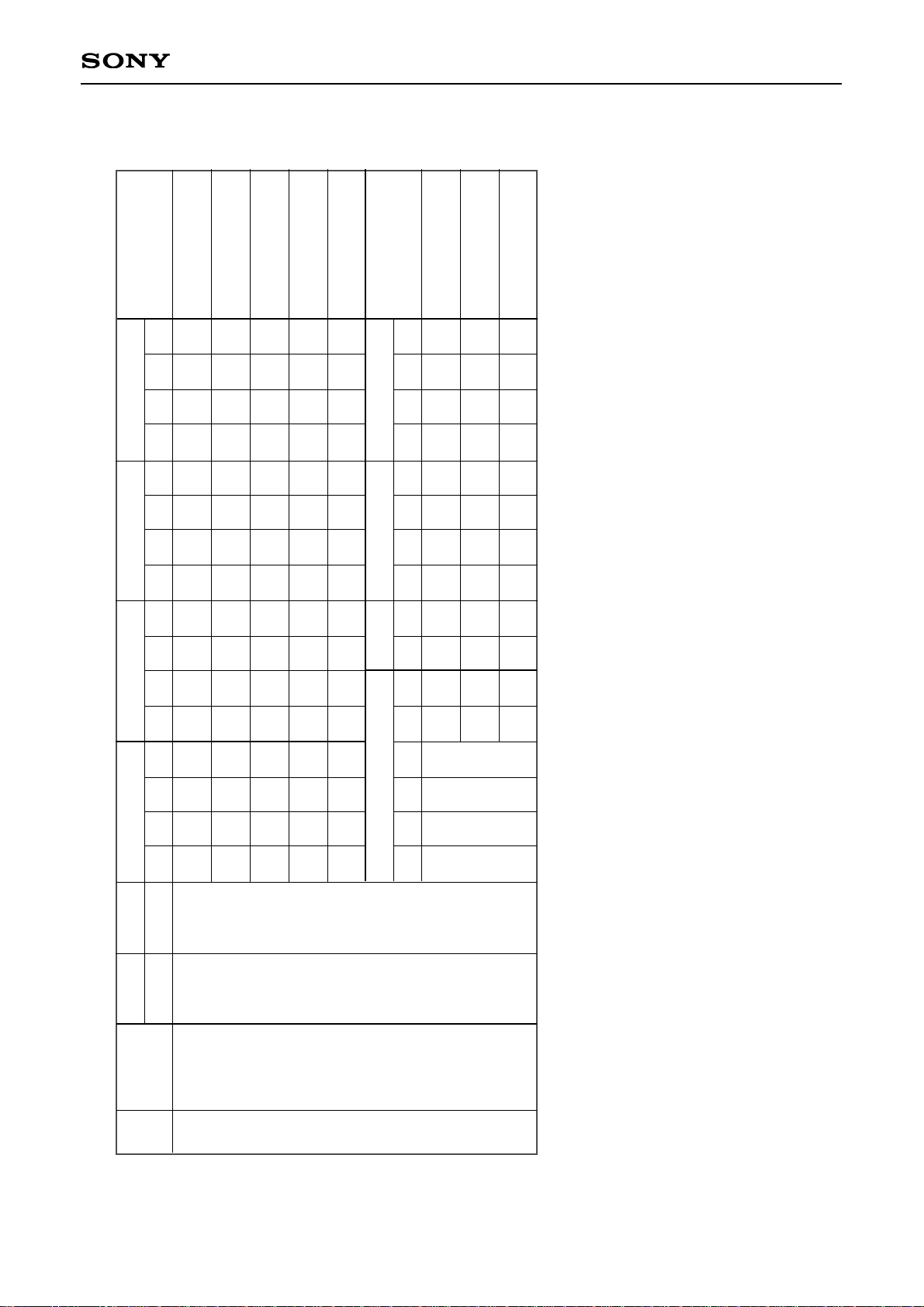

CXD3029R

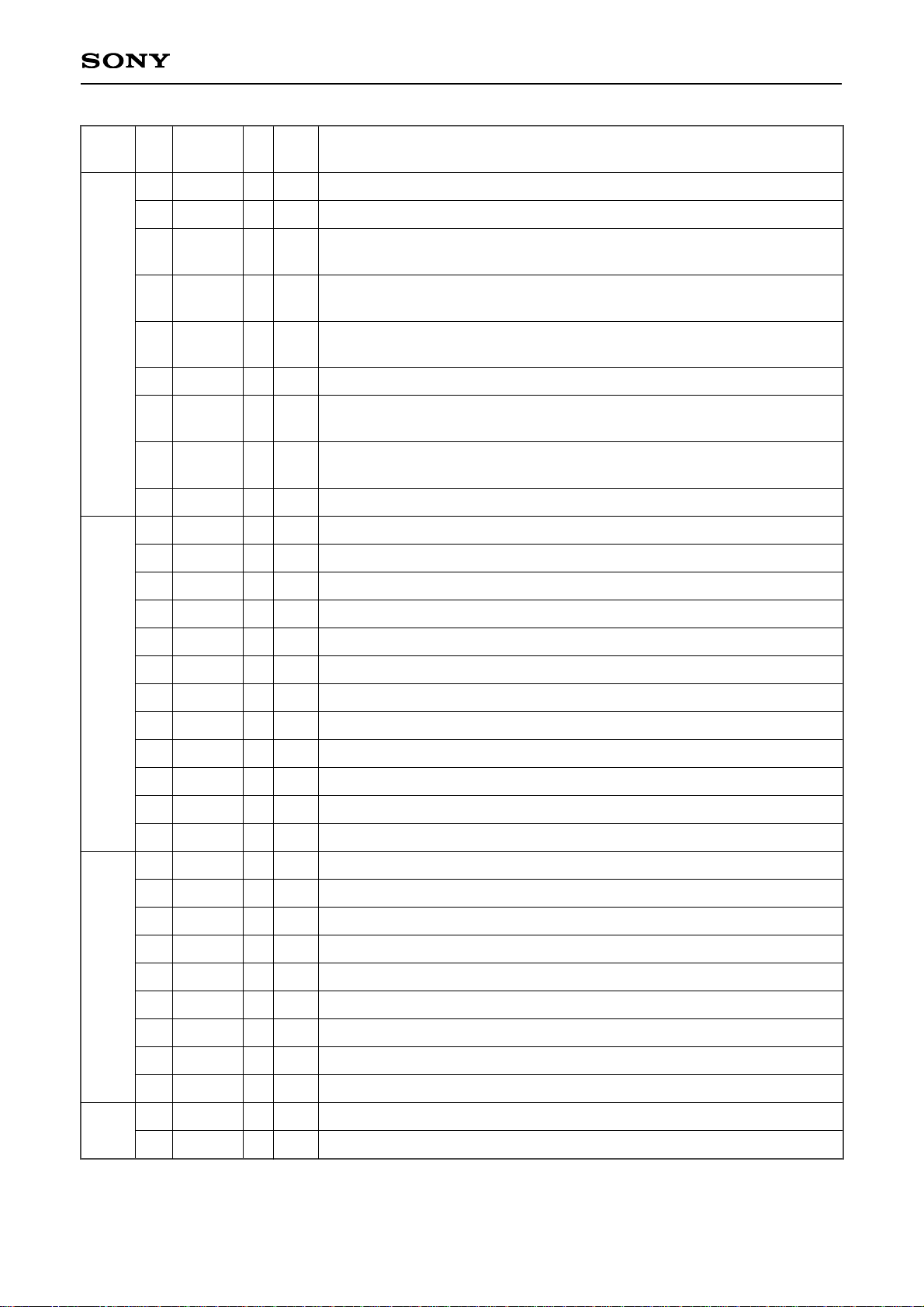

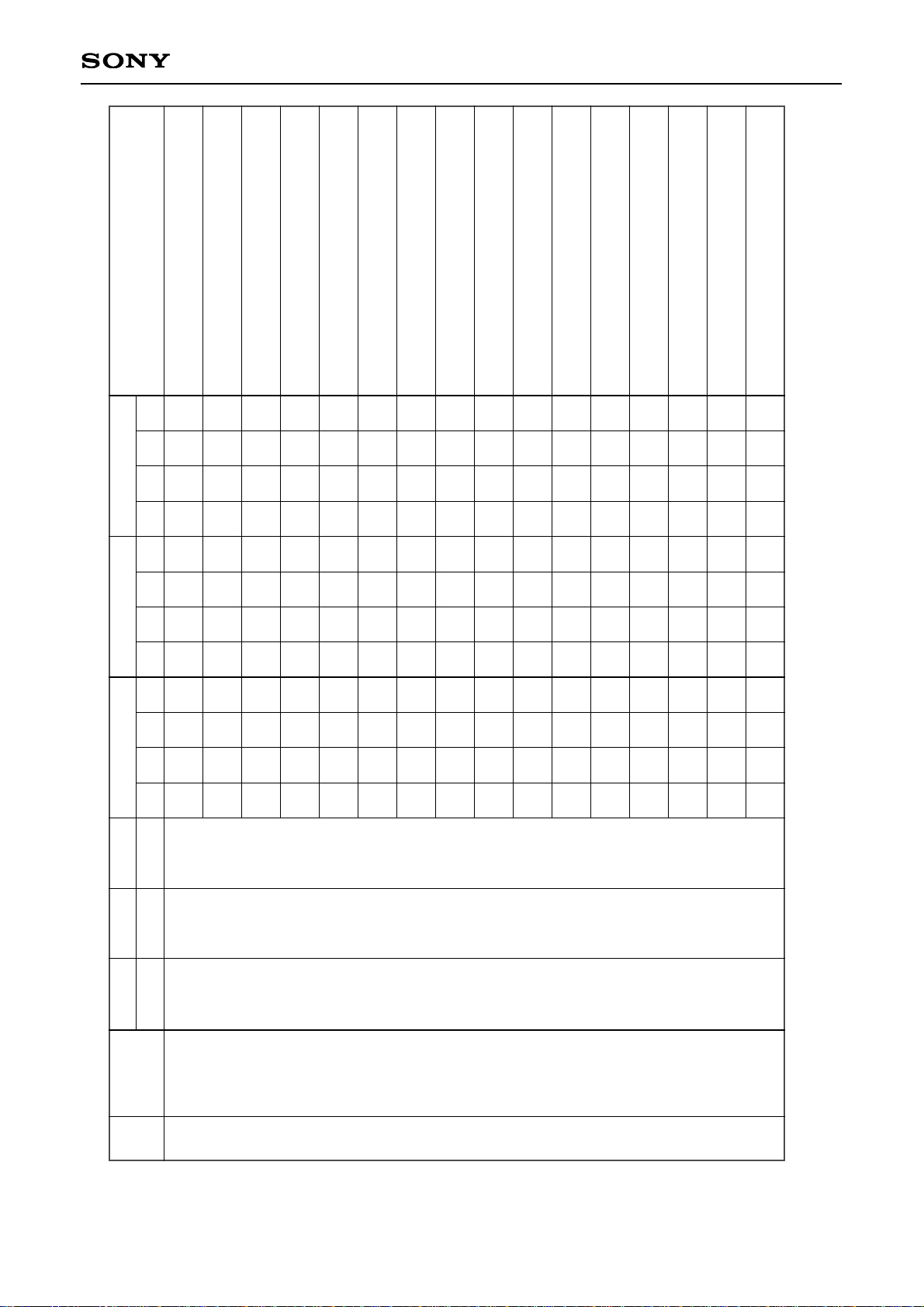

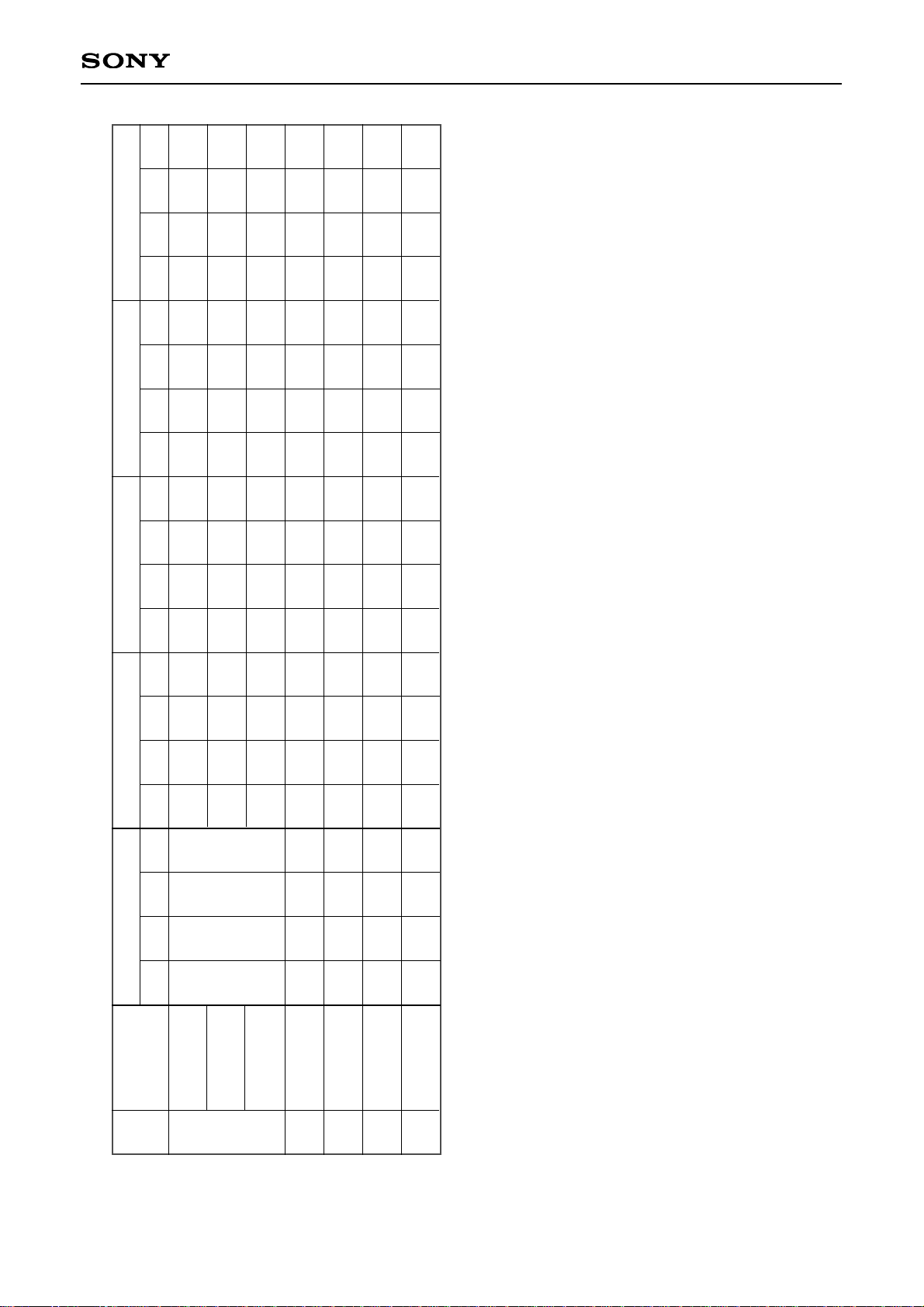

Pin Configuration

36

35

34

31

32

33

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

1

40

39

38

37

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

70

69

68

67

63

64

65

66

61

62

71

72

97

96

95

94

91

92

93

99

98

73

74

81

82

83

84

75

76

77

78

88

87

86

85

79

80

89

90

TE

CE

RFAC

AV

DD

3

BIAS

ASYI

AV

SS

3

VPCO

VCTL

CLTV

FILO

FILI

PCO

V

DD

1

GFS

C2PO

COUT

MIRR

FOK

DFCT

ATSK

DOUT

AV

DD

0

ASYO

XUGF

LRMU

XRAS

XWE

D1

TEST1

TEST2

XCAS

WFCK

A9

A8

A7

DV

SS

A6

A5

A4

XRDE

V

DD

0

CLOK

DATA

SENS

XLAT

XSOE

SYSM

WDCK

SCOR

XRST

XQOK

D3

D2

D0

PWMI

HPL

HV

SS

XTSL

EXCK

SBSO

XWIH

XEMP

SCLK

SQCK

V

SS0

R4M

XWRE

VREFR

AV

SS2

AV

SS1

VREFL

AOUT1

AV

DD1

XV

SS

XTAO

XTAI

XV

DD

HVDD

HPR

TES1

AV

DD2

AOUT2

SQSO

TEST

V

SS1

XPCK

AV

SS

0

IGEN

RFDC

PCMD

PCMDI

BCK

BCKI

DV

DD

A3

A2

A0

A10

A11

TEST3

TEST4

FFDR

TRDR

TFDR

SRDR

SFDR

SSTP

MDS

MDP

C176

V

DD2

LRCKI

VC

V

SS2

FRDR

A1

FE

SE

LRCK

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

– 4 –

CXD3029R

Pin Description

Pin

No.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

Power

supply

2-3V

I/F

Digital

O

O

I/O

I/O

I/O

I/O

O

O

O

O

O

O

O

—

O

O

O

I/O

—

I

I

O

I

I

I

O

O

I

I

I/O

I/O

1, 0

1, 0

1, 0

1, 0

1, 0

1, 0

1, 0

1, 0

1, 0

1, 0

1, 0

—

1, 0

1, 0

1, 0

1, 0

—

1, Z, 0

1, 0

1, 0

1, 0

1, 0

DRAM row address strobe signal.

DRAM data input enable signal.

DRAM data bus 1.

DRAM data bus 0.

DRAM data bus 3.

DRAM data bus 2.

Test pin. Do not connect.

Test pin. Do not connect.

DRAM column address strobe signal.

WFCK output. XOE is output by switching with the command.

DRAM address 9.

DRAM address 8.

DRAM address 7.

DRAM interface GND.

DRAM address 6.

DRAM address 5.

DRAM address 4.

DRAM readout enable signal input. XRDE monitor is output by switching

with the command.

Digital power supply.

Serial data transfer clock input from CPU. SQSO and SENS readout

clocks are output by switching with the command.

Serial data input from CPU.

SENS output to CPU. SQSO data is output by switching with the command.

Latch input from CPU. The serial data is latched at the falling edge. XLAT

which is low for 6µs or more is enabled.

CPU serial data output enable signal.

Mute input. Muted when high.

Word clock output f = 2Fs. GRSCOR is output by switching with the command.

High output when the subcode sync is detected. SCOR, which is

interpolated in the IC, is output by switching with the command.

System reset. Reset when low.

Spindle motor external control input.

Subcode Q OK input. XQOK monitor is output by switching with the command.

DRAM write enable signal input. XWRE monitor is output by switching with

the command.

XRAS

XWE

D1

D0

D3

D2

TEST1

TEST2

XCAS

WFCK

A9

A8

A7

DV

SS

A6

A5

A4

XRDE

VDD0

CLOK

DATA

SENS

XLAT

XSOE

SYSM

WDCK

SCOR

XRST

PWMI

XQOK

XWRE

Symbol I/O Value

Description

– 5 –

CXD3029R

Pin

No.

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

Power

supply

Digital

H/P

X'tal

Lch

Rch

Digital

O

—

I

I

O

O

O

O

I

I

—

O

O

—

I

O

—

O

O

—

—

O

O

—

I

I

—

O

O

I/O

1, 0

—

1, 0

1, 0

1, 0

1, 0

—

1, 0

1, 0

—

—

Analog

Analog

—

—

Analog

Analog

—

—

1, 0

1, 0

1, 0

Microcomputer clock output. R8M and C4M are output by switching with

the command.

Digital GND.

SQSO readout clock input.

SENS serial data readout clock input.

Subcode Q 80-bit and PCM peak and level data output. CD TEXT data output.

DRAM readout prohibited signal.

Write to DRAM prohibited signal.

Subcode P to W serial output.

SBSO readout clock input.

Crystal selection input. Low when the crystal is 16.9344 MHz; high when

the crystal is 33.8688MHz.

Headphone GND.

Lch headphone PDM output.

Rch headphone PDM output.

Headphone power supply.

Master clock power supply.

Crystal oscillation circuit input. The master clock is externally input from

this pin.

Crystal oscillation circuit output.

Master clock GND.

Analog power supply.

Lch analog output.

Lch reference voltage.

Analog GND.

Analog GND.

Rch reference voltage.

Rch analog output.

Analog power supply.

Test pin. Normally GND.

Test pin. Normally GND.

Digital GND.

OR signal output of Lch, Rch “0” detection flag (AND output) and SYSM.

Only "0" detection flag is output by switching with the command.

Digital Out output.

Anti-shock input/output.

R4M

VSS0

SQCK

SCLK

SQSO

XEMP

XWIH

SBSO

EXCK

XTSL

HVSS

HPL

HPR

HVDD

XVDD

XTAI

XTAO

XVSS

AVDD1

AOUT1

VREFL

AVSS1

AVSS2

VREFR

AOUT2

AVDD2

TES1

TEST

VSS1

LRMU

DOUT

ATSK

Symbol I/O Value

Description

– 6 –

CXD3029R

Pin

No.

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

Power

supply

Digital

ASYM

A/D

Digital

I/O

I/O

I/O

I/O

O

O

O

O

—

O

I

O

I

I

O

—

O

O

I

—

I

—

I

—

I

I

I

I

I

I

—

O

1, 0

1, 0

1, 0

1, 0

1, 0

1, 0

1, 0

1, 0

—

1, Z, 0

Analog

1, Z, 0

—

1, 0

—

—

—

—

1, 0

Defect signal input/output.

Focus OK signal input/output.

Mirror signal input/output. SCOR Window is output by switching with the

command.

Track number count signal input/output. SCOR is output by switching with

the command.

C2PO output. MNT3 and GTOP are output by switching with the

command.

GFS output. MNT2 and XROF are output by switching with the command.

XUGF output. MNT0, RFCK, C4M and QRCVD are output by switching

with the command.

XPCK output. MNT1, FSTO and GTOP are output by switching with the

command.

Digital power supply.

Master PLL charge pump output.

Master PLL filter input.

Master PLL (slave = digital PLL) filter output.

Multiplier VCO1 control voltage input.

Wide-band EFM PLL VCO2 control voltage input.

Wide-band EFM PLL charge pump output.

Analog GND.

EFM full-swing output (low = Vss, high = V

DD).

Asymmetry comparator voltage input.

Asymmetry circuit constant current input.

Analog power supply.

EFM signal input.

Analog power supply.

Operational amplifier constant current input.

Analog GND.

RF signal input.

Center servo analog input or E input.

Tracking error signal input or F input.

Sled error signal input or B input.

Focus error signal input or A input.

Center voltage input.

Digital GND.

Focus drive output.

DFCT

FOK

MIRR

COUT

C2PO

GFS

XUGF

XPCK

V

DD1

PCO

FILI

FILO

CLTV

VCTL

VPCO

AVSS3

ASYO

ASYI

BIAS

AVDD3

RFAC

AVDD0

IGEN

AVSS0

RFDC

CE

TE

SE

FE

VC

VSS2

FRDR

Symbol I/O Value

Description

– 7 –

CXD3029R

Notes) • PCMD is a MSB first, two's complement output.

• GTOP is used to monitor the frame sync protection status. (High: sync protection window released.)

• XUGF is the frame sync obtained from the EFM signal, and is negative pulse. It is the signal before

sync protection.

• XPCK is the inverse of the EFM PLL clock. The PLL is designed so that the falling edge and the EFM

signal transition point coincide.

• The GFS signal goes high when the frame sync and the insertion protection timing match.

• RFCK is derived from the crystal accuracy, and has a cycle of 136µs.

• C2PO represents the data error status.

• XROF is generated when the 32K RAM exceeds the ±28 frame jitter margin.

• C4M is a 4.2336MHz output that changes in CAV-W mode and variable pitch mode.

• R8M is the 8.4672MHz output.

• FSTO is the 2/3 frequency-division output of the XTAI pin.

• SOUT is the serial data output inside the servo block.

• SOCK is the serial data readout clock output inside the servo block.

• XOLT is the serial data latch output inside the servo block.

Pin

No.

96

97

98

99

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

Power

supply

2-3V

I/F

O

O

O

O

O

I

O

O

O

—

O

I

O

I

O

I

—

O

O

O

O

O

I/O

O

O

1, 0

1, 0

1, 0

1, 0

1, 0

1, Z, 0

1, Z, 0

1, 0

—

1, 0

1, 0

1, 0

—

1, 0

1, 0

1, 0

1, 0

1, 0

1, 0

Focus drive output.

Tracking drive output.

Tracking drive output.

Sled drive output.

Sled drive output.

Disc innermost detection signal input.

Spindle drive output.

Spindle motor servo control output.

176.4kHz output. 88.2kHz for quasi-double speed setting.

Digital power supply.

D/A interface. LR clock output f = Fs.

D/A interface. LR clock input.

D/A interface. Serial data output. (two’s complement, MSB first)

D/A interface. Serial data input. (two’s complement, MSB first)

D/A interface. Bit clock output.

D/A interface. Bit clock input.

DRAM interface power supply.

DRAM address 3.

DRAM address 2.

DRAM address 1.

DRAM address 0.

DRAM address 10.

DRAM address 11. Write prohibition factor is input by switching with the

command.

Test pin. Do not connect.

Test pin. Do not connect.

FFDR

TRDR

TFDR

SRDR

SFDR

SSTP

MDS

MDP

C176

VDD2

LRCK

LRCKI

PCMD

PCMDI

BCK

BCKI

DVDD

A3

A2

A1

A0

A10

A11

TEST3

TEST4

Symbol I/O Value

Description

Digital

– 8 –

CXD3029R

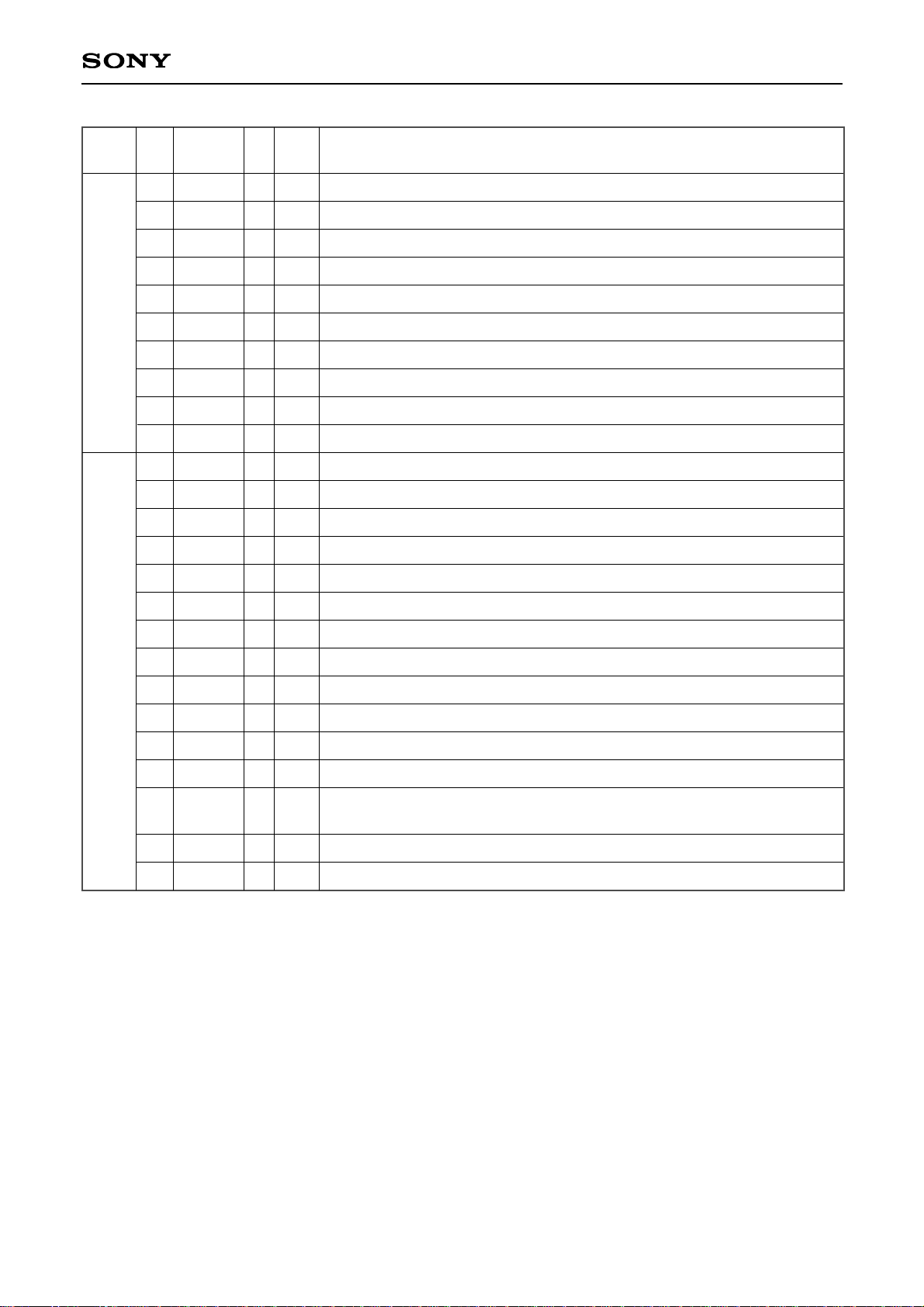

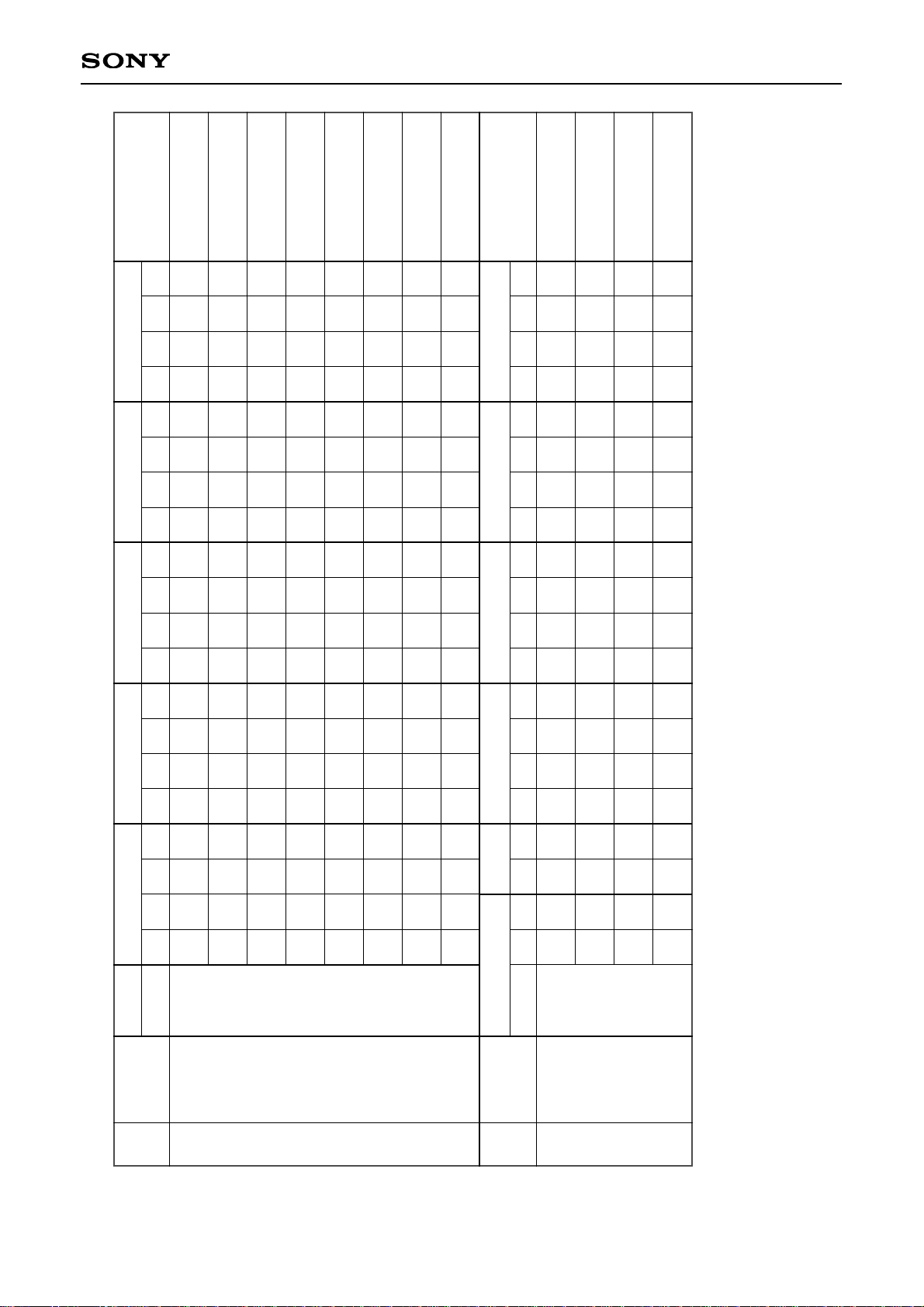

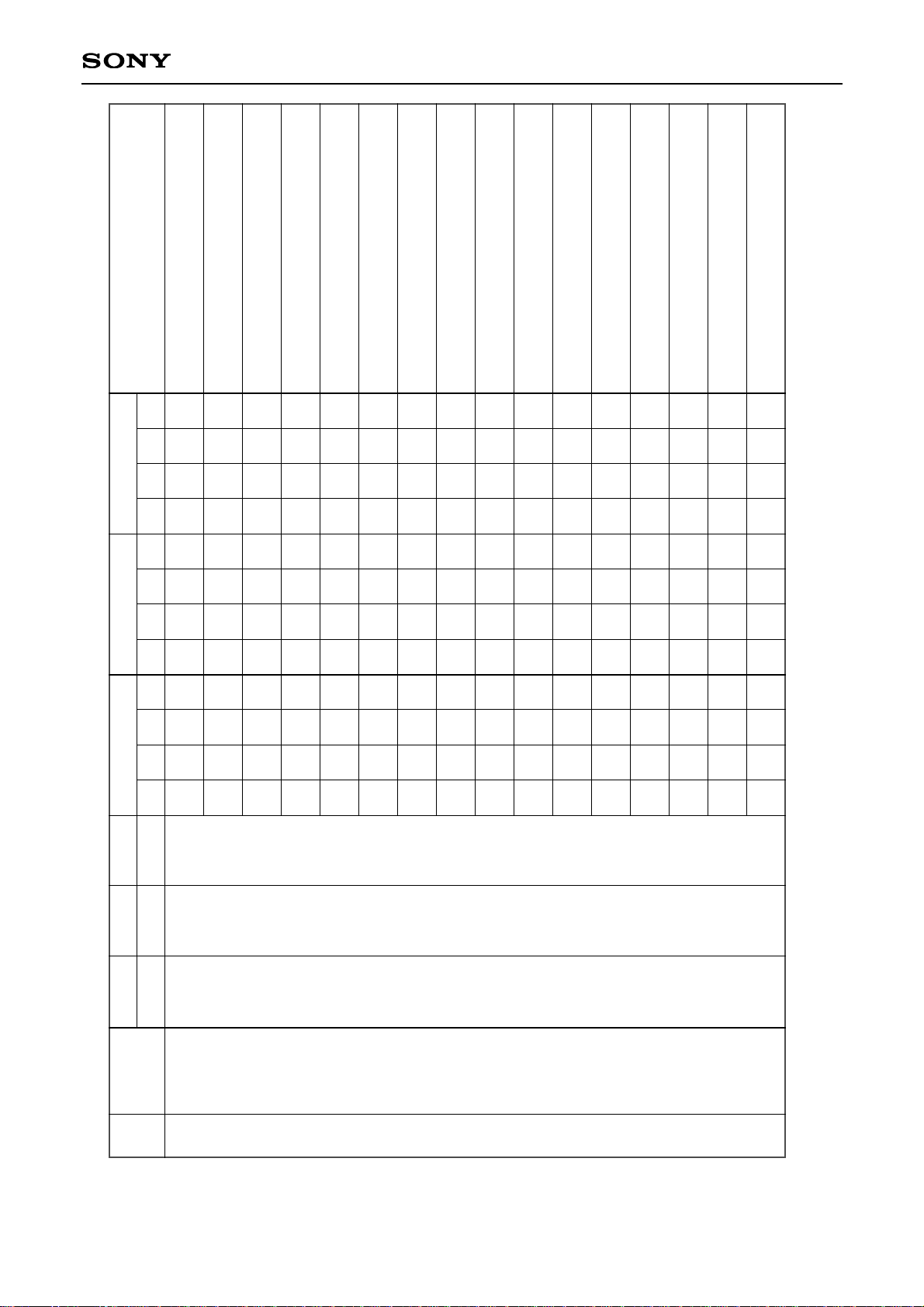

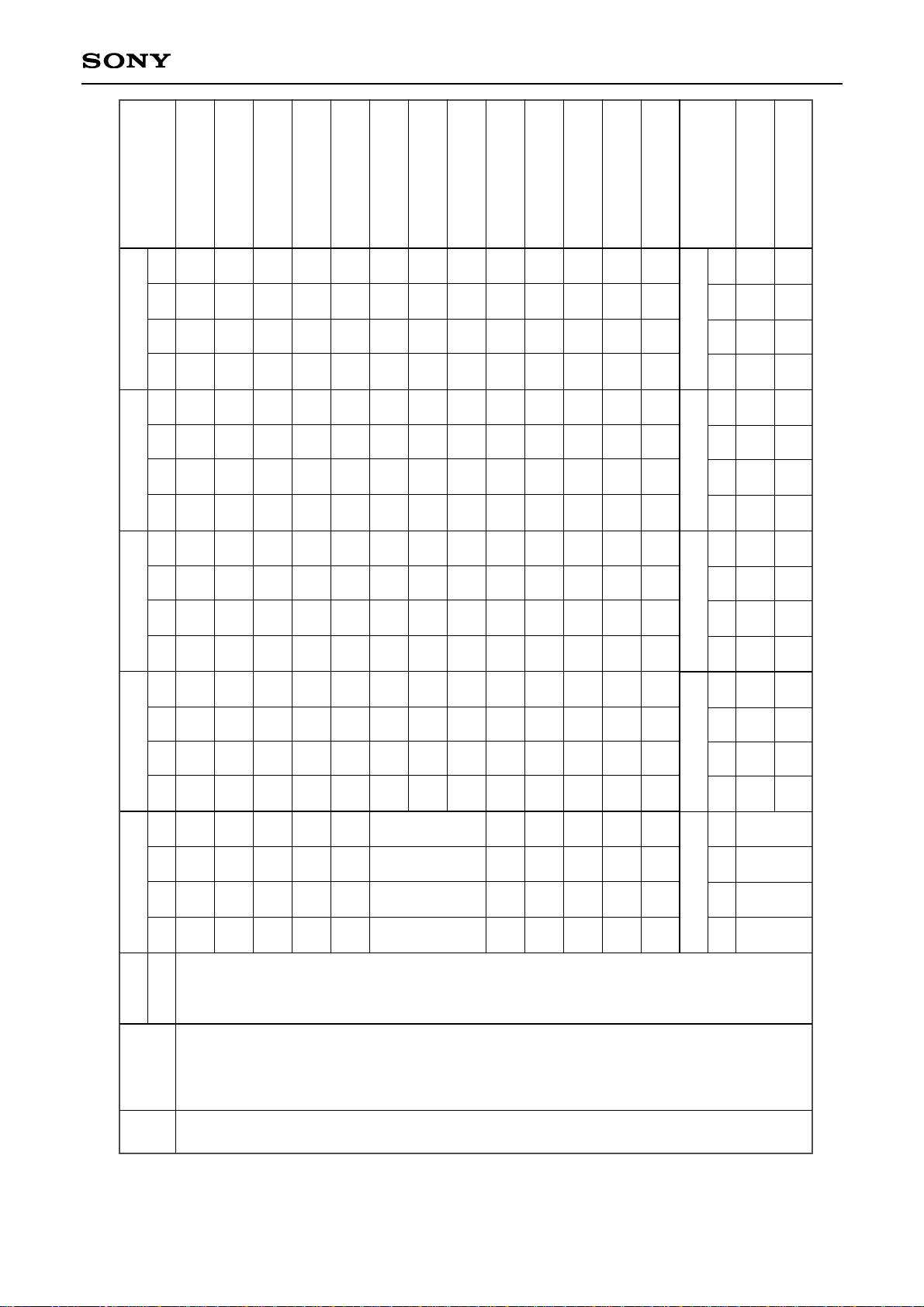

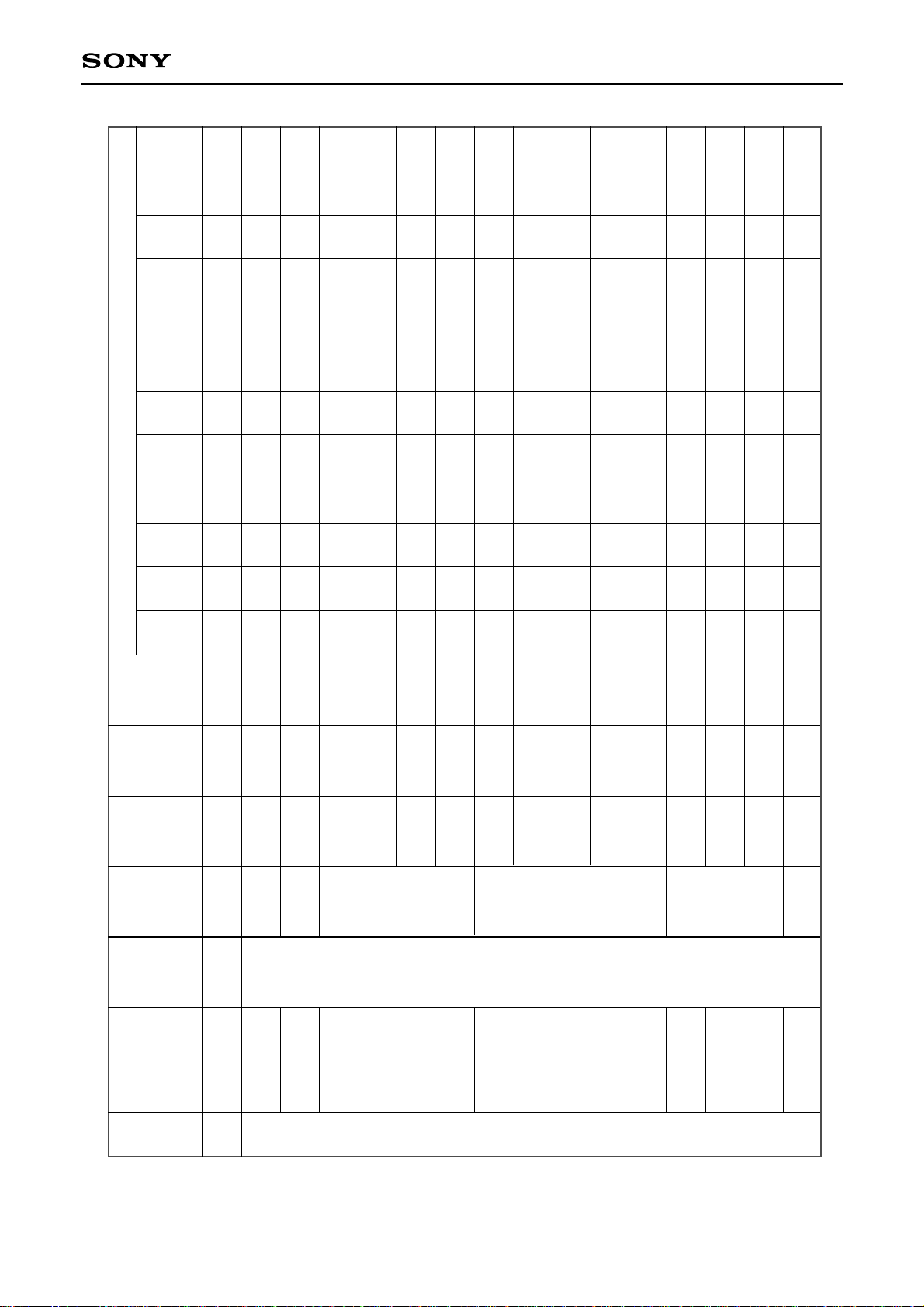

Monitor Pin Output Combinations

Command bit

Output data

SRO1

MTSL1

MTSL0

XUGF

XPCK

GFS

C2PO

MNT0

MNT1

MNT2

MNT3

RFCK

XPCK

XROF

GTOP

0

0

0

0

1

—

MONSEL

0

0

0

0

0

1

0

0

1

1

0

—

0

1

0

1

0

—

C4M

FSTO

GFS

C2PO

SOUT

SOCK

XOLT

C2PO

COUT

COUT

COUT

COUT

COUT

MIRR

MIRR

MIRR

MIRR

MIRR

QRCVD

GTOP

GFS

C2PO SCOR

SCOR

WINDOW

– 9 –

CXD3029R

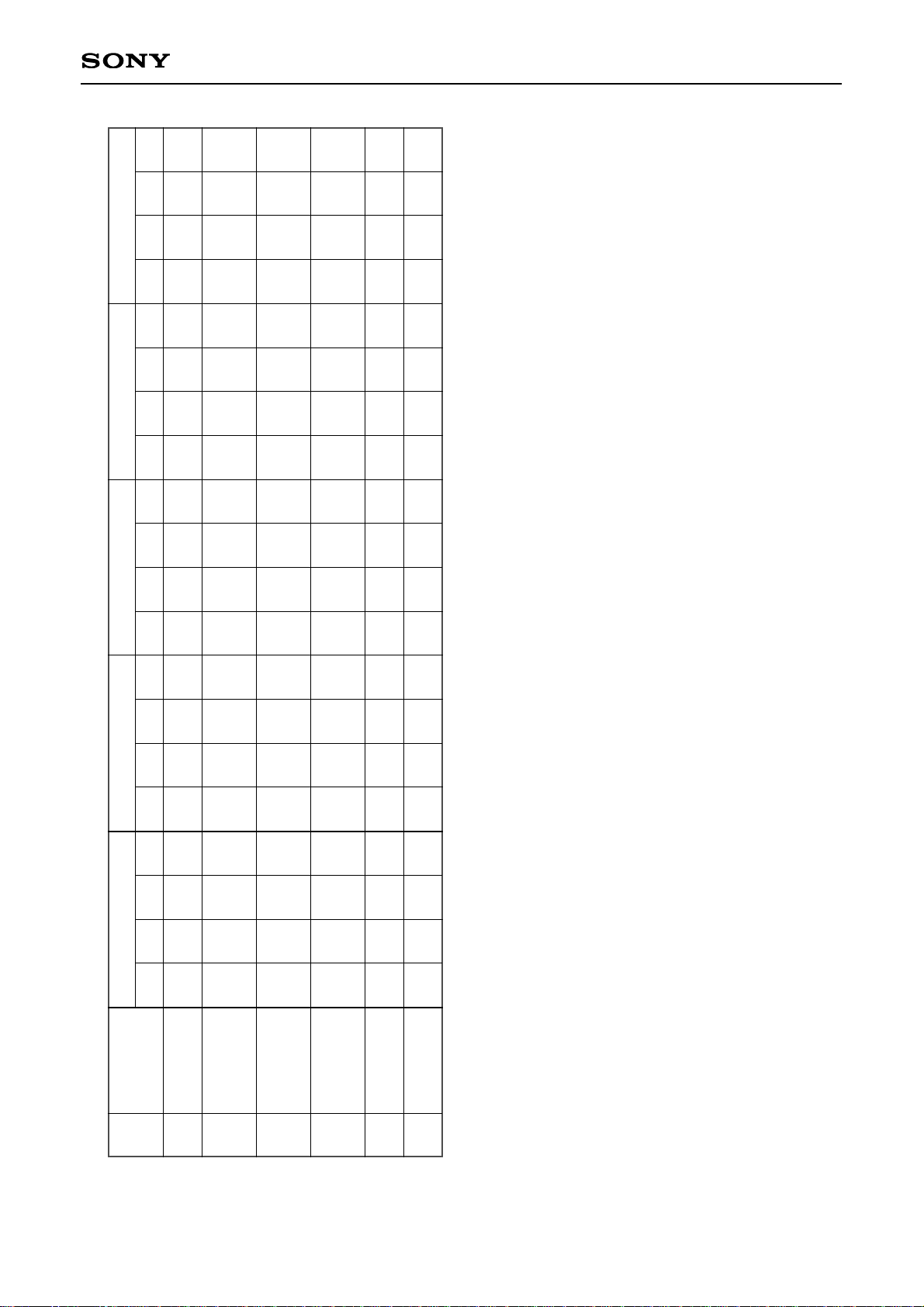

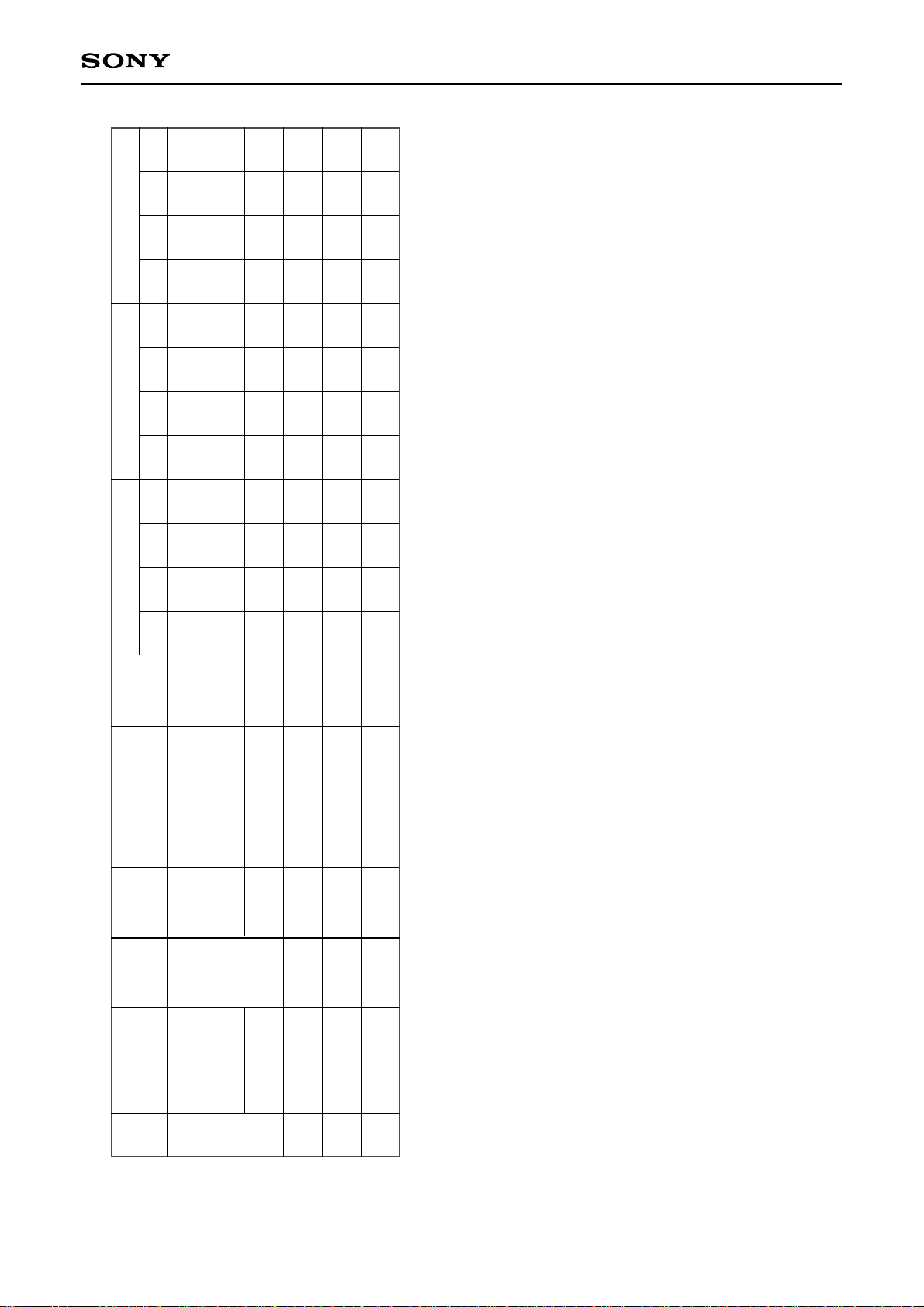

Electrical Characteristics

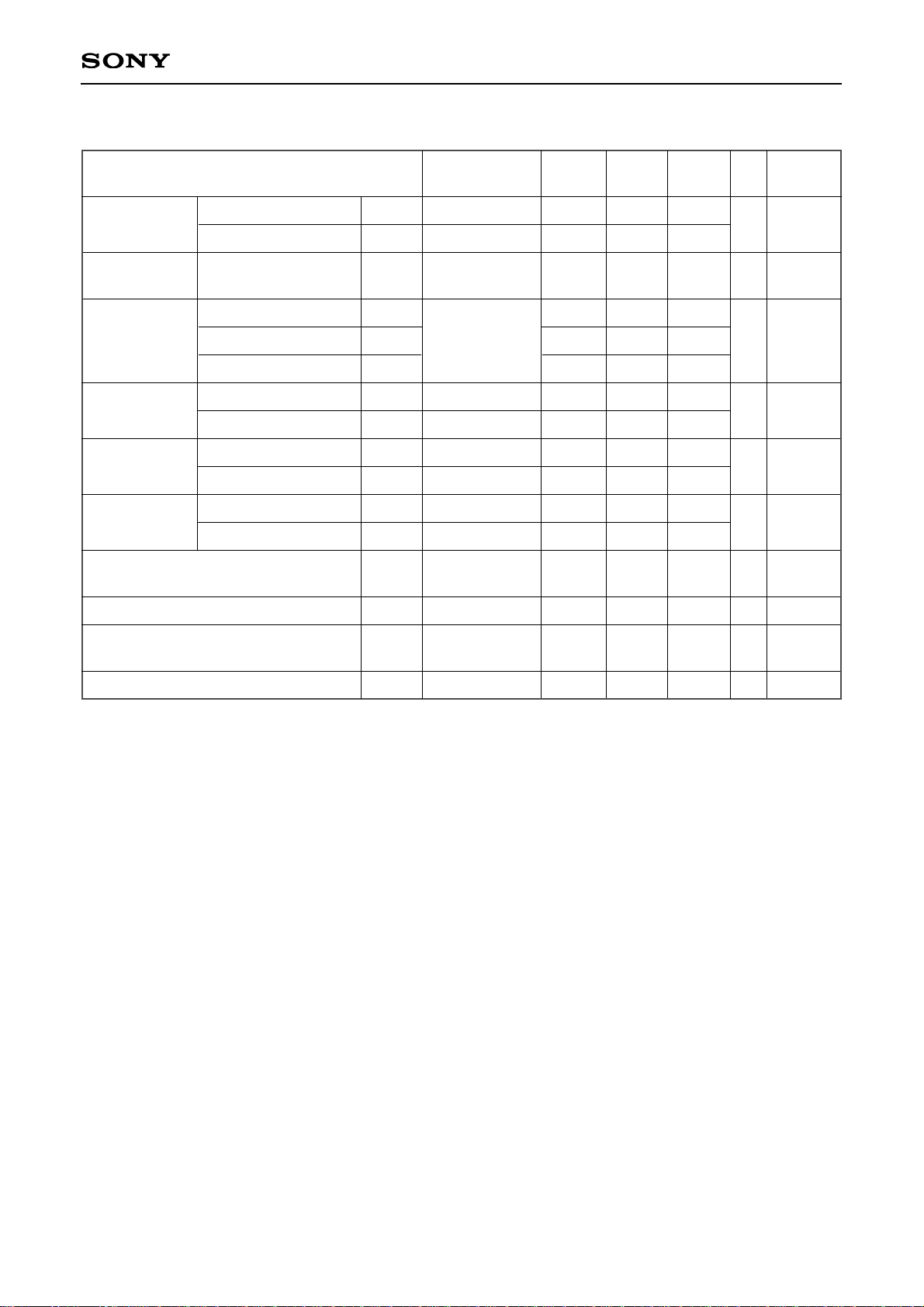

1. DC Characteristics (VDD1 = 3.3 ± 0.3V, VDD2 (logic) = 2.2 ± 0.2V, DVSS = VSS = 0V, Topr = –20 to +75°C)

Item

Input voltage

(1)

Input voltage

(2)

Input voltage

(3)

Input leak current (1)

∗

13

,

∗15

∗

14

∗12, ∗13

∗13

∗15

Schmitt input

I

OH = –4mA

IOL = 4mA

VIN = 0 to VDD

VIN = 0 to VDD

High level input voltage

Low level input voltage

High level input voltage

Low level input voltage

Hysteresis

High level output voltage

Low level output voltage

VIH

VIL

Vt+

Vt–

Vt+–

VOH

VOL

ILI (1)

ILI (2)

0.7VDD1

0.7VDD1

VDD1 – 0.4

0

–10

–40

0.2V

DD

1

0.2VDD1

VDD1

0.4

10

40

V

V

V

µA

µA

Conditions Min.

Typ.

Max.

Unit

Applicable

pins

Input leak current (2)

0.5

Input voltage

(1)

Input voltage

(2)

Input voltage

(3)

Output voltage

(1)

Output voltage

(2)

Output voltage

(3)

∗

1, ∗2,

∗

3, ∗4

∗

6, ∗7

∗

5

∗

2, ∗8,

∗

10, ∗15

Input leak current (1)

Input leak current (2)

Input leak current (3)

Tri-state output leak current

∗

1, ∗3,

∗

5, ∗6

∗

2, ∗4

V

V

V

V

∗

9

V

∗

11

V

µA

µA

∗

10

µA

∗

7

µA

Schmitt input

Analog input

I

OH = –4mA

IOL = 4mA

IOH = –1mA

IOL = 1mA

IOH = –0.28mA

IOL = 0.36mA

VIN = 0 to VDD

V

IN = 0 to VDD

V

IN = 0.25VDD

to 0.75V

DD

V

O = 0 to 3.6V

High level input voltage

Low level input voltage

Input voltage

High level input voltage

Low level input voltage

Hysteresis

High level output voltage

Low level output voltage

High level output voltage

Low level output voltage

High level output voltage

Low level output voltage

VIH (1)

VIL (1)

VIN (2)

Vt+

Vt–

Vt+–

VOH (1)

VOL (1)

VOH (2)

VOL (2)

VOH (3)

VOL (3)

ILI (1)

ILI (2)

ILI (3)

ILO

0.7VDD

VSS

0.7VDD

VDD – 0.4

0

VDD – 0.4

0

VDD – 0.5

0

–10

–40

–40

–5

0.5

0.2VDD

VDD

0.2VDD

VDD

0.4

VDD

0.4

VDD

0.4

10

40

40

5

(V

DD = AVDD = 3.3 ± 0.3V, VSS = AVSS = 0V, Topr = –20 to +75°C)

Item

Conditions Min.

Typ.

Max.

Unit

Applicable

pins

– 10 –

CXD3029R

Applicable pins

∗1

TEST, TES1

∗2

COUT, MIRR, DFCT, FOK, XQOK, XWRE, ATSK

∗3

SYSM, DATA, XSOE, XTSL

∗4

SSTP, PWMI

∗5

SQCK, EXCK, XRST, CLOK, SCLK, XLAT

∗6

VCTL, FILI, CLTV, ASYI, IGEN, BIAS

∗7

RFDC, CE, TE, SE, FE, VC

∗8

XEMP, XWIH, SQSO, SBSO, XUGF, XPCK, GFS, C2PO, SCOR, WDCK, SFDR, SRDR, TFDR, TRDR,

FFDR, FRDR, ASYO, DOUT, C176

∗9

R4M

∗10

SENS, MDP, VPCO, PCO, MDS

∗11

FILO

∗12

A0 to A10, XRAS, XCAS, XWE, WFCK, LRCK, BCK, PCMD

∗13

D0 to D3, XRDE, A11

∗14

LRCKI, BCKI

∗15

PCMDI

∗16

HPL, HPR

Input voltage

(1)

Input voltage

(2)

Input voltage

(3)

Output voltage

(1)

Output voltage

(2)

Output voltage

(3)

∗

1, ∗2,

∗

3, ∗4

∗

6, ∗7

∗

5

∗

2, ∗8,

∗

10, ∗16

Input leak current (1)

Input leak current (2)

Input leak current (3)

Tri-state output leak current

∗

1, ∗3,

∗

5, ∗6

∗

2, ∗4

V

V

V

V

∗

9

V

∗

11

V

µA

µA

∗

10

µA

∗

7

µA

Schmitt input

Analog input

I

OH = –2.4mA

IOL = 2.4mA

IOH = –0.6mA

IOL = 0.6mA

IOH = –0.28mA

IOL = 0.36mA

VIN = 0 to VDD

VIN = 0 to VDD

VIN = 0.25VDD

to 0.75VDD

VO = 0 to 3.6V

High level input voltage

Low level input voltage

Input voltage

High level input voltage

Low level input voltage

Hysteresis

High level output voltage

Low level output voltage

High level output voltage

Low level output voltage

High level output voltage

Low level output voltage

VIH (1)

VIL (1)

VIN (2)

Vt+

Vt–

Vt+–

VOH (1)

VOL (1)

VOH (2)

VOL (2)

VOH (3)

VOL (3)

ILI (1)

I

LI (2)

ILI (3)

I

LO

0.7VDD

VSS

0.7VDD

VDD – 0.4

0

VDD – 0.4

0

VDD – 0.5

0

–10

–40

–40

–5

0.5

0.2VDD

VDD

0.2VDD

VDD

0.4

VDD

0.4

VDD

0.4

10

40

40

5

(VDD = AVDD = 2.2 ± 0.2V, VSS = AVSS = 0V, Topr = –20 to +75°C)

Item

Conditions Min.

Typ.

Max.

Unit

Applicable

pins

– 11 –

CXD3029R

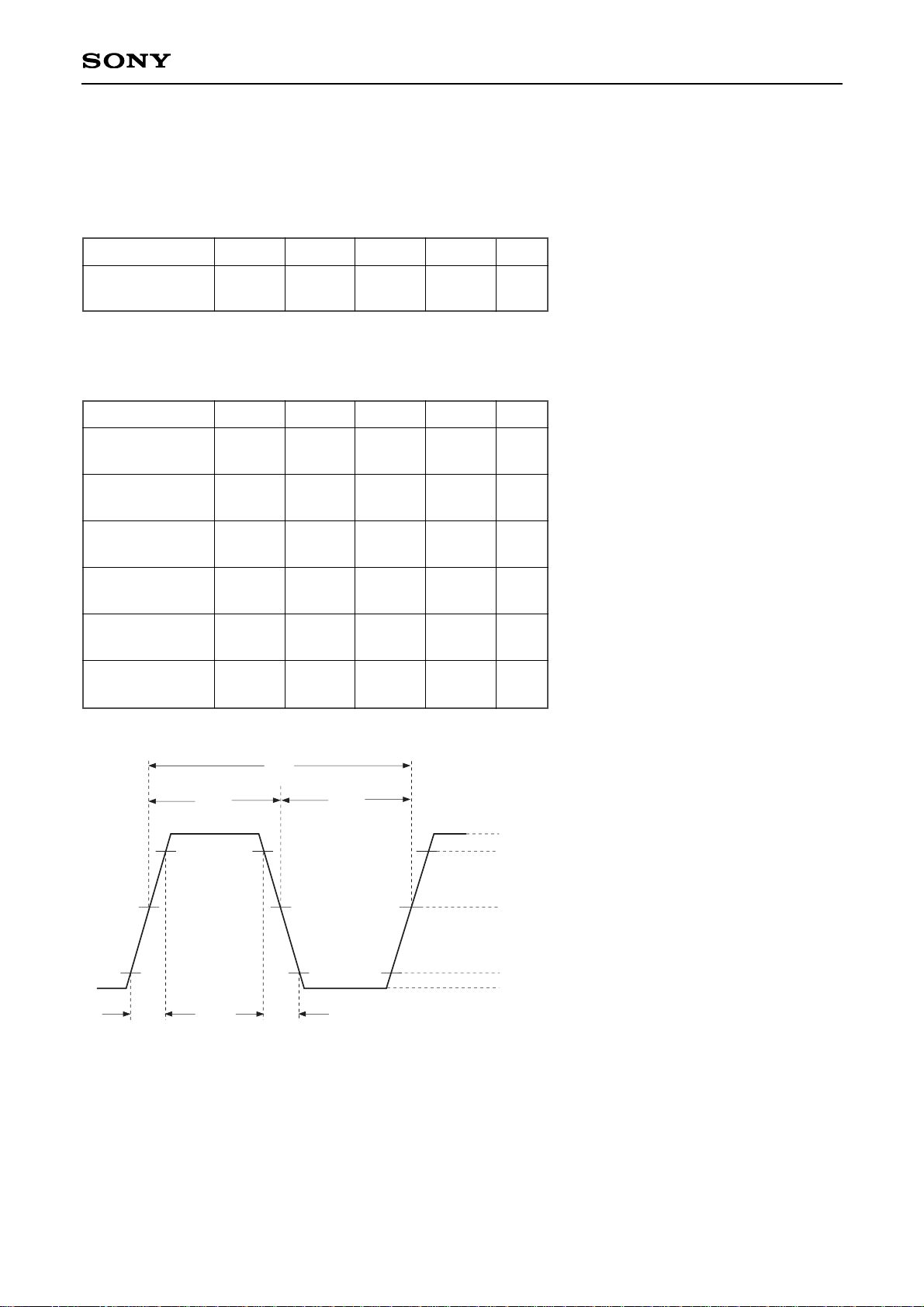

2. AC Characteristics

(1) XTAI pin

(a) When using self-excited oscillation

(VDD = AVDD = 2.2 ± 0.2V and 3.3 ± 0.3V, Vss = AVss = 0V, Topr = –20 to +75°C)

(b) When inputting pulses to XTAI pin

(VDD = AVDD

= 2.2 ± 0.2V and 3.3 ± 0.3V, Vss = AVss = 0V, Topr = –20 to +75°C)

Note) When the pulse is input to the XTAI pin, be sure to input it via the capacitor.

Oscillation

frequency

f

MAX 734

MHz

Item Symbol Min. Typ. Max. Unit

High level pulse

width

tWHX

13 500

ns

Low level pulse

width

tWLX

13 500

ns

Pulse cycle

tCX

26 1000

ns

Input high level VIHX 0.7VDD

V

Input low level VILX 0.2VDD

V

Rise time,

fall time

tR, tF

10

ns

Item

Symbol Min. Typ. Max. Unit

tR tF

tWHX

tWLX

tCX

VILX

VIHX × 0.1

V

IHX × 0.9

V

IHX

XTAI

VDD/2

– 12 –

CXD3029R

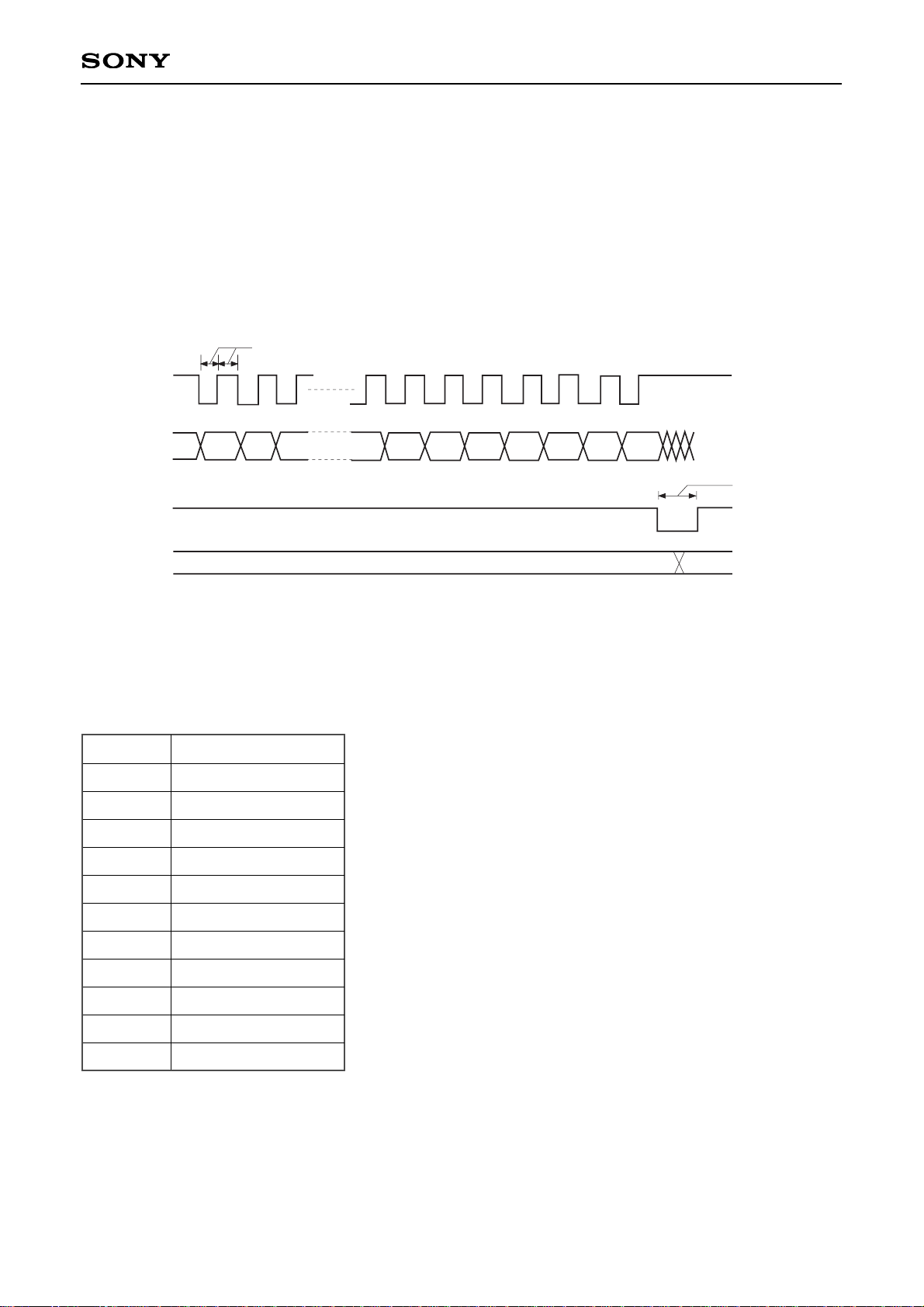

(2) CLOK, DATA, XLAT, SQCK and EXCK pins

(VDD = AVDD = 2.2 ± 0.2V and 3.3 ± 0.3V, VSS = AVSS = 0V, Topr = –22 to +75°C)

Clock frequency

Clock pulse width

Setup time

Hold time

Delay time

Latch pulse width

Latch pulse width

(during $AAX MLAT ON)

Command transfer interval

(during $AAX MLAT ON)

EXCK SQCK frequency

EXCK SQCK pulse width

COUT frequency (during input)

∗

COUT pulse width (during input)

∗

fCK

tWCK

t

SU

tH

tD

tWL

tWL

tWSC

fT

tWT

fT

tWT

750

300

300

300

750

6

11

750

7.5

0.65

30000

30000

0.65

65

MHz

ns

ns

ns

ns

ns

µs

µs

MHz

ns

kHz

µs

Item

Symbol Min.

Typ. Max. Unit

tWCK tWCK

1/fCK

tH

tSU

tWL

tD

1/fT

tWT tWT

tH

tSU

CLOK

DATA

XLAT

EXCK

SQCK

COUT

SBSO

SQSO

tWSC

∗

Only when $44 and $45 are executed.

(3) R4M pin (when $A4X CKOUTSL2 = CKOUTSL1 = 0)

(V

DD = AVDD = 2.2 ± 0.2V and 3.3 ± 0.3V, VSS = AVSS = 0V, Topr = –22 to +75°C)

Output frequency

Output duty

Output amplitude

fOUT

DOUT

VOUT

4.2336

50

VDD

MHz

%

V

Item

Symbol Min.

Typ. Max. Unit

– 13 –

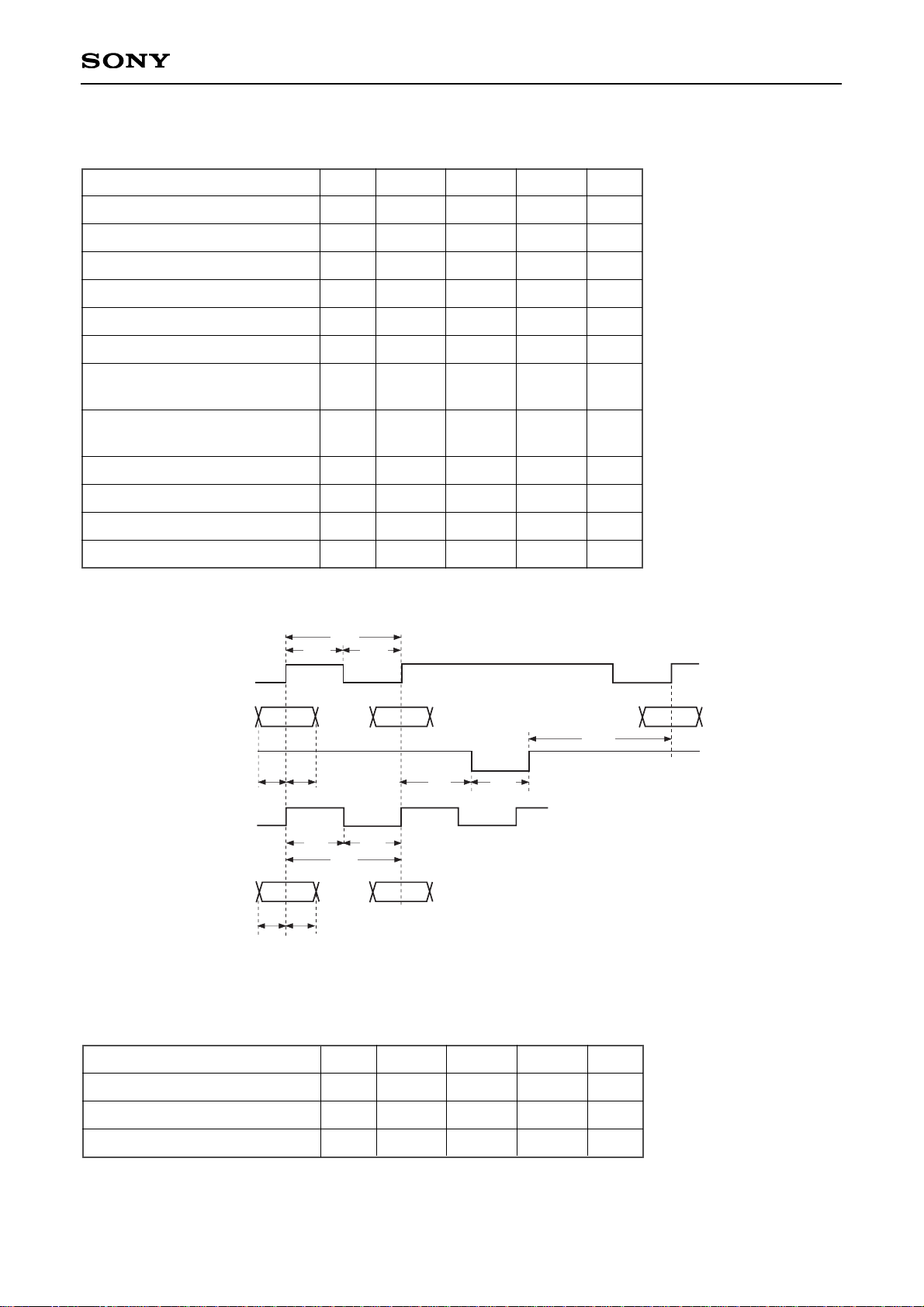

CXD3029R

(4) SCLK pin

SCLK frequency

SCLK pulse width

Delay time

fSCLK

tSPW

tDLS

31.3

15

16 MHz

ns

µs

Item

Symbol

Min. Typ.

Max. Unit

(5) COUT, MIRR and DFCT pins

Operating frequency

(VDD = AVDD = 2.2 ± 0.2V and 3.3 ± 0.3V, VSS = AVSS = 0V, Topr = –20 to +75°C)

COUT maximum

operating frequency

MIRR maximum

operating frequency

DFCT maximum

operating frequency

fCOUT

fMIRR

fDFCTH

40

40

5

kHz

kHz

kHz

∗1

∗2

∗3

Signal

Symbol Min. Typ. Max.

Unit

Conditions

∗1

When using a high-speed traverse TZC.

∗2

When the RF signal continuously satisfies the following conditions during the above traverse.

• A = 0.11VDD to 0.23VDD

• ≤ 25%

∗3

During complete RF signal omission.

When settings related to DFCT signal generation are Typ.

A

B

B

A + B

(VDD = AVDD = 2.2 ± 0.2V and 3.3 ± 0.3V, VSS = AVSS = 0V, Topr = –20 to +75°C)

XLAT

tSPWtDLS

SCLK

Serial Read Out Data

(SENS)

1/fSCLK

MSB LSB

...

...

– 14 –

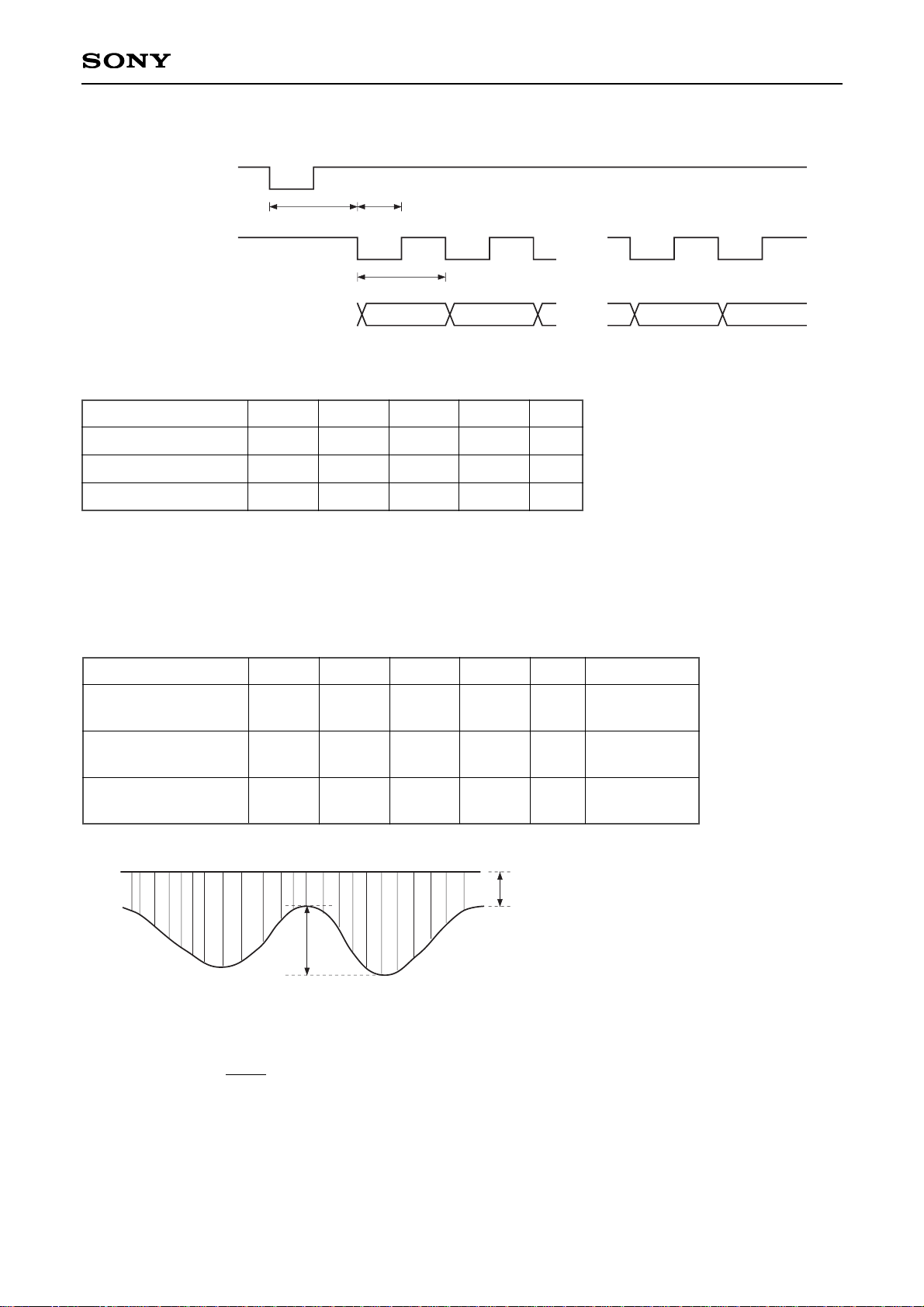

CXD3029R

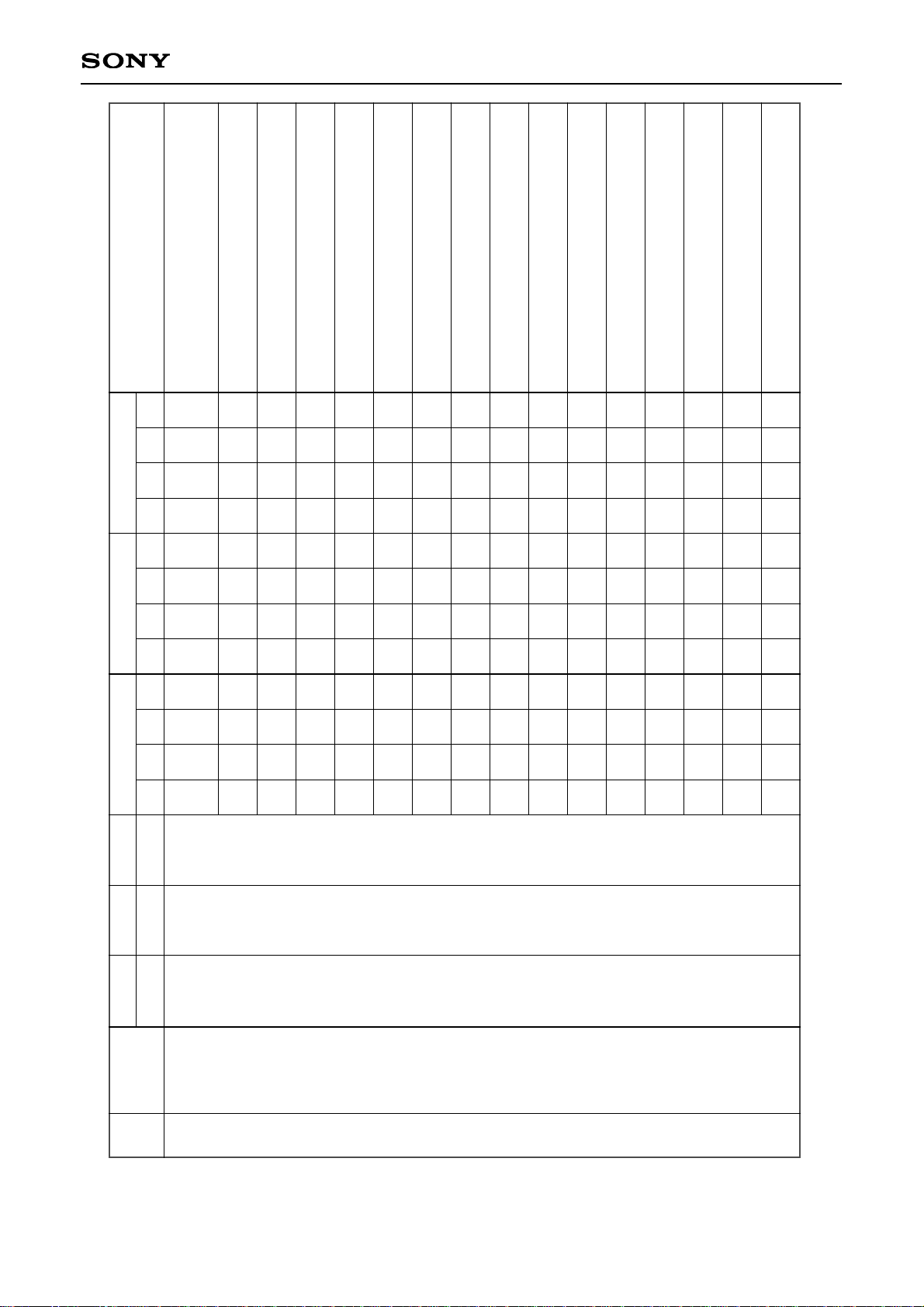

Fs = 44.1kHz in all cases.

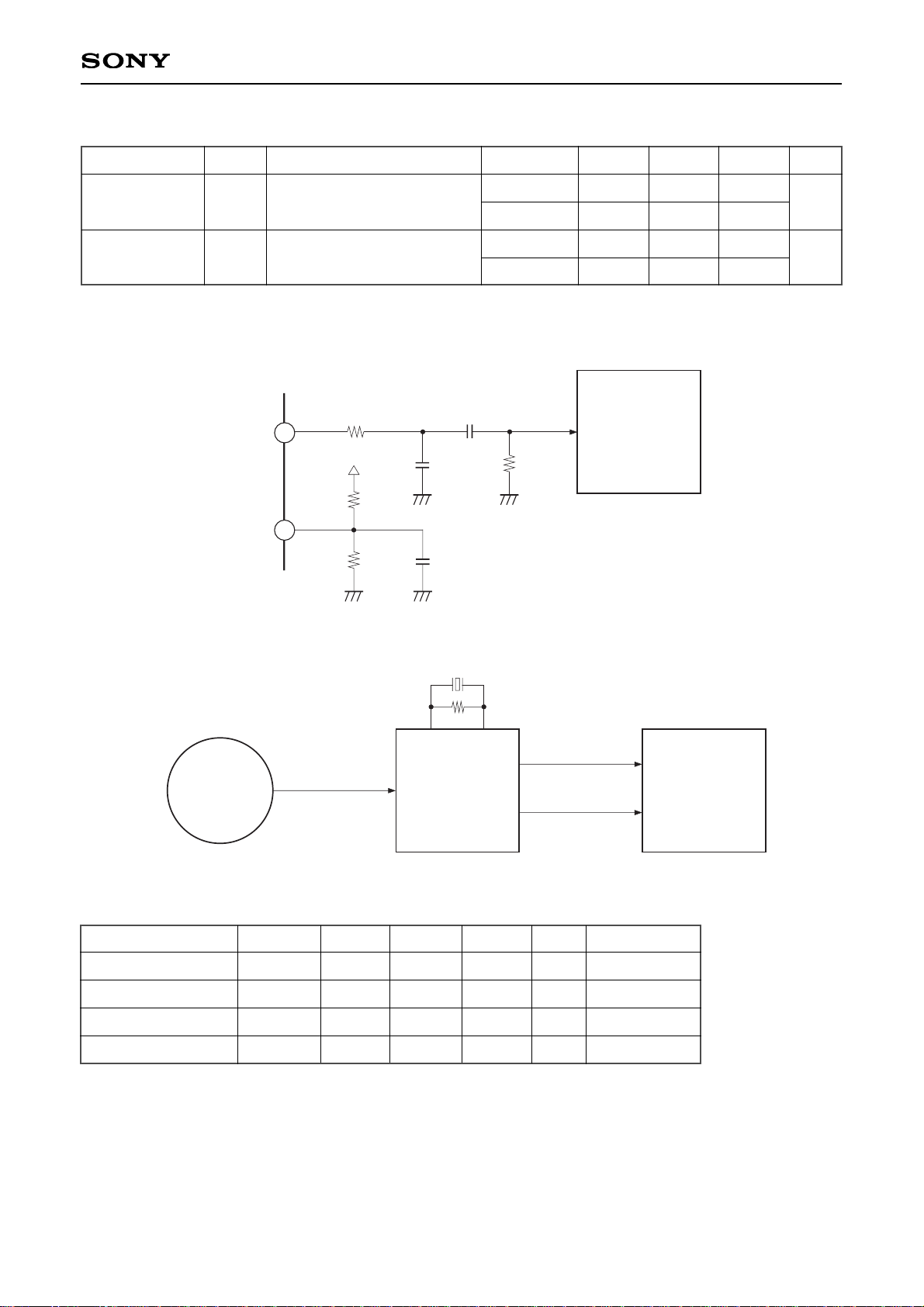

The total harmonic distortion and signal-to-noise ratio measurement circuits are shown below.

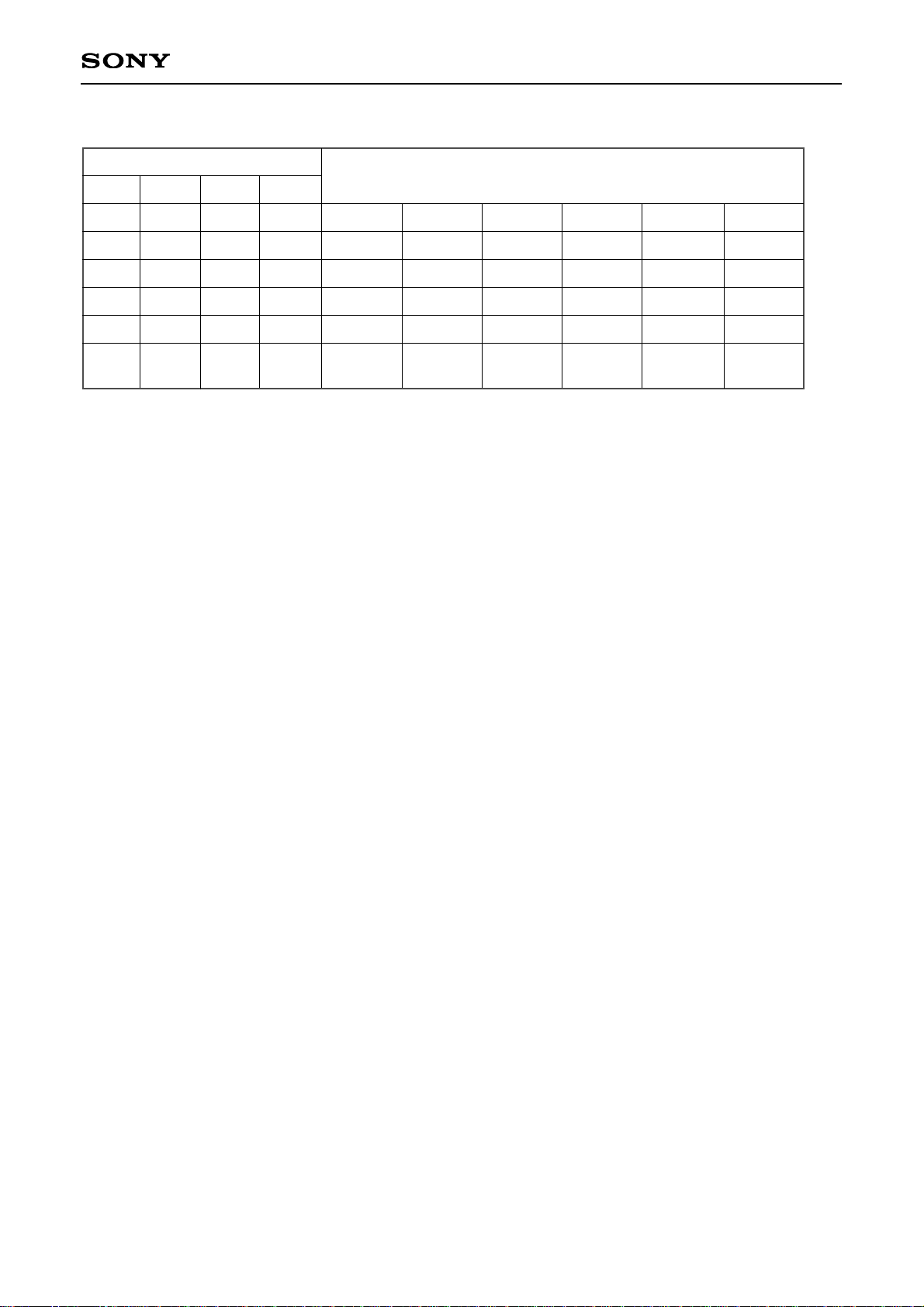

1-bit DAC and LPF Block Analog Characteristics (VDD = AVDD = 3.3V, VSS = AVSS = 0V, Ta = 25°C)

Item

Total harmonic

distortion

Signal-to-noise

ratio

Symbol

THD

S/N

Conditions

1kHz, 0dB data

Crystal

1kHz, 0dB data, AMUT OFF

(Using A-weighting filter)

384Fs

768Fs

384Fs

768Fs

93

93

0.006

0.006

95

95

0.008

0.008

Min.

Typ.

Max.

Unit

%

dB

SHIBASOKU (AM51A)

22kΩ

22µF

AOUT1 (2)

VREFL (R)

22kΩ

10µF

220Ω

0.01µF

100kΩ

Audio Analyzer

Audio Analyzer

CXD3029R

Rch A

Lch B

DATA RF

TEST DISC

768Fs/384Fs

(VDD = AVDD = 3.3V, VSS = AVSS = 0V, Ta = –20 to +75°C)

V

OUT

RL

RVREF

CVREF

100

∗

1

∗1

∗2

∗2

Vrms

kΩ

kΩ

µF

Symbol

10

Min.

Max.

0.80

1

Typ.

Applicable pinsUnit

Output voltage

Load resistance

VREF pin resistance

VREF pin capacitance

Item

∗

Measurement is conducted for the above circuit diagrams with the sine wave output of 1kHz and 0dB.

Applicable pins

∗∗

1

AOUT1, AOUT2

∗∗

2

VREFL, VREFR

Block diagram of analog characteristics measurement

LPF external circuit diagram

– 15 –

CXD3029R

Contents

[1] CPU Interface

§1-1. CPU Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

§1-2. CPU Interface Command Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

§1-3. CPU Command Presets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

§1-4. Description of SENS Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

§1-5. Description of Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

[2] Subcode Interface

§2-1. P to W Subcode Readout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

§2-2. 80-bit Subcode-Q Readout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

[3] Description of Modes

§3-1. CLV-N Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

§3-2. CLV-W Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

§3-3. CAV-W Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

§3-4. VCO-C Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

[4] Description of Other Functions

§4-1. Channel Clock Recovery by Digital PLL Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

§4-2. Frame Sync Protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

§4-3. Error Correction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

§4-4. DA Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

§4-5. Digital Out . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

§4-6. Servo Auto Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

§4-7. Digital CLV . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

§4-8. CD-DSP Block Playback Speed . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127

§4-9. Description of DAC Block and Shock-proof Memory Controller Block Circuits . . . . . . . . . . . . . . 127

§4-10. DAC Block Input Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

§4-11. Description of DAC Block Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

§4-12. LPF Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134

§4-13. Description of Shock-proof Memory Controller Block Functions . . . . . . . . . . . . . . . . . . . . . . . . . 135

§4-14. CPU to DRAM Access Function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 140

§4-15. Asymmetry Correction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 144

§4-16. CD TEXT Data Demodulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 145

[5] Description of Servo Signal Processing System Functions and Commands

§5-1. General Description of Servo Signal Processing System . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 147

§5-2. Digital Servo Block Master Clock (MCK) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 148

§5-3. DC Offset Cancel [AVRG Measurement and Compensation] . . . . . . . . . . . . . . . . . . . . . . . . . . . 149

§5-4. E:F Balance Adjustment Function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 150

§5-5. FCS Bias Adjustment Function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 150

§5-6. AGCNTL Function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 152

§5-7. FCS Servo and FCS Search . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 154

§5-8. TRK and SLD Servo Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 155

§5-9. MIRR and DFCT Signal Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 156

§5-10. DFCT Countermeasure Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 157

§5-11. Anti-shock Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 157

§5-12. Brake Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 158

§5-13. COUT Signal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 159

§5-14. Serial Readout Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 159

§5-15. Writing to Coefficient RAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 160

§5-16. PWM Output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 160

§5-17. Servo Status Changes Produced by LOCK Signal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 161

§5-18. Description of Commands and Data Sets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 161

§5-19. List of Servo Filter Coefficients . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 189

§5-20. Filter Composition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 191

§5-21. TRACKING and FOCUS Frequency Response . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 197

[6] Application Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 198

Explanation of abbreviations

AVRG: Average

AGCNTL: Auto gain control

FCS: Focus

TRK: Tracking

SLD: Sled

DFCT: Defect

– 16 –

CXD3029R

[1] CPU Interface

§1-1. CPU Interface Timing

• CPU interface

This interface uses DATA, CLOK and XLAT to set the modes.

The interface timing chart is shown below. (See 2. AC Characteristics in Electrical Characteristics, for the

details of the AC characteristics.)

• The internal registers are initialized by a reset when XRST = 0.

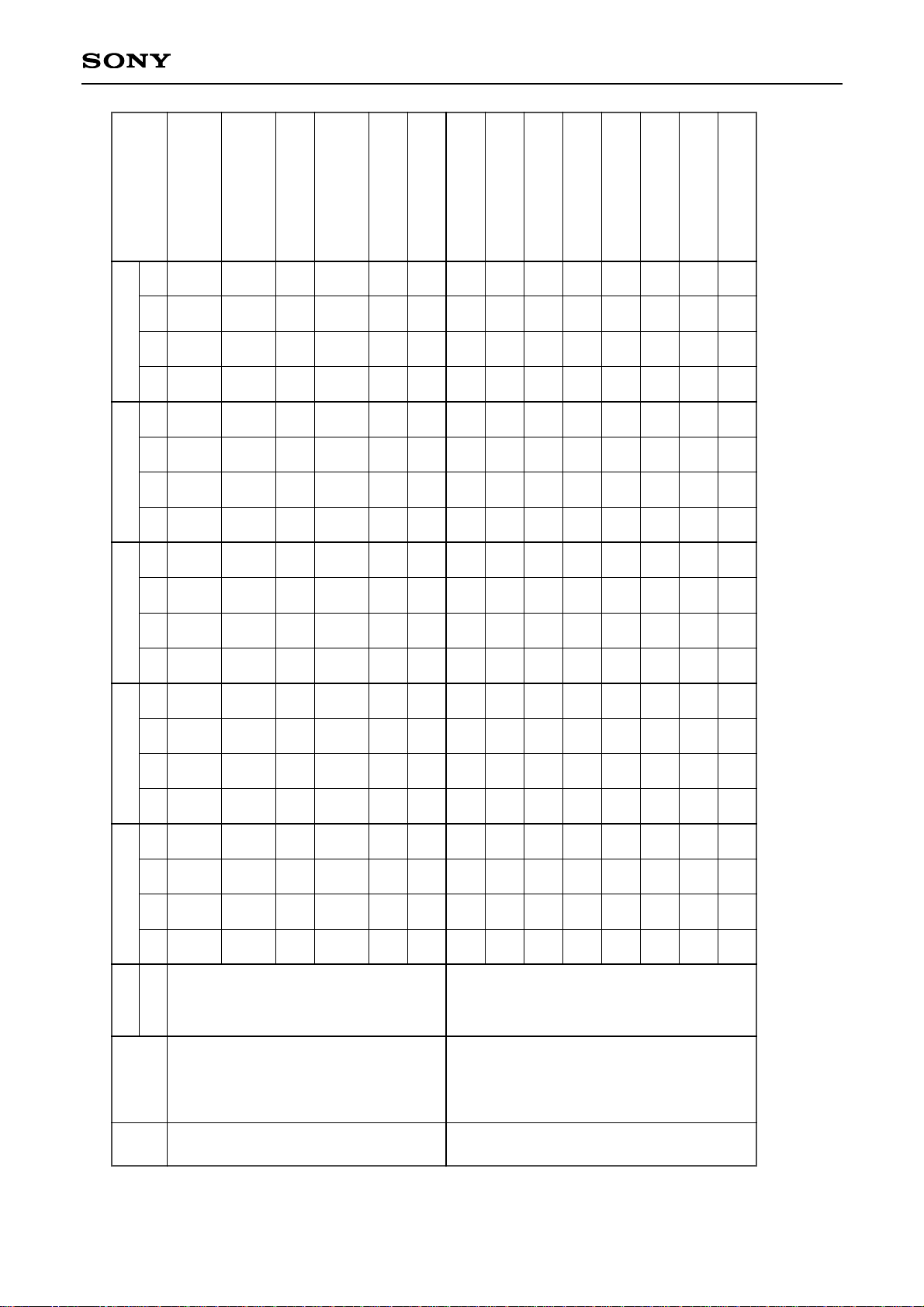

§1-2. CPU Interface Command Table

Total bit length for each register

Register

0 to 2

3

4 to 6

7

8

9

A

B

C

D

E

8 bits

8 to 24 bits

16 bits

20 bits

32 bits

32 bits

28 bits

28 bits

28 bits

28 bits

20 bits

Total bit length

750ns to 30µs

D18 D19 D20 D21 D22 D23

750ns or more

(6µs or more

when $AAX

MLAT ON)

Valid

CLOK

DATA

XLAT

Registers

D0 D1

– 17 –

CXD3029R

FOCUS SERVO ON

(FOCUS GAIN

NORMAL)

FOCUS SERVO ON

(FOCUS GAIN

DOWN)

FOCUS SERVO OFF,

0V OUT

FOCUS SERVO OFF,

FOCUS SEARCH

VOLTAGE OUT

FOCUS SEARCH

VOLTAGE DOWN

FOCUS SEARCH

VOLTAGE UP

ANTI SHOCK ON

ANTI SHOCK OFF

BRAKE ON

BRAKE OFF

TRACKING GAIN

NORMAL

TRACKING GAIN UP

TRACKING GAIN UP

FILTER SELECT 1

TRACKING GAIN UP

FILTER SELECT 2

1

1

0

0

0

0

1

0

—

—

—

—

—

—

0

1

—

—

—

—

0

—

1

0

—

—

—

—

—

—

0

1

1

1

—

—

—

—

0

1

—

—

—

—

—

—

0

1

—

—

—

—

—

—

1

0

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

0

1

0 0 0 0

0 0 0 1

FOCUS

CONTROL

TRACKING

CONTROL

Regis-

ter

Command

Address

D23 to D20

Data 1

D19 D18 D17 D16

Data 2

D15 D14 D13 D12

Data 3

D11 D10 D9 D8

Data 4

D7 D6 D5 D4

Data 5

D3 D2 D1 D0

Command Table ($0X to 1X)

—: don’t care

– 18 –

CXD3029R

TRACKING SERVO OFF

TRACKING SERVO ON

FORWARD TRACK JUMP

REVERSE TRACK JUMP

SLED SERVO OFF

SLED SERVO ON

FORWARD SLED MOVE

REVERSE SLED MOVE

SLED KICK LEVEL

(±1 × basic value) (default)

SLED KICK LEVEL

(±2 × basic value)

SLED KICK LEVEL

(±3 × basic value)

SLED KICK LEVEL

(±4 × basic value)

0

0

1

1

—

—

—

—

0

0

0

0

0

0

0

0

0

0

1

1

0

1

0

1

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

0

1

0

1

—

—

—

—

—

—

—

—

0

0

1

1

—

—

—

—

0

1

0

1

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

2

3

0 0 1 0

0 0 1 1

TRACKING

MODE

SELECT

Regis-

ter

Command

Address

D23 to D20

Regis-

ter

Command

Address

D23 to D20

Data 1

D19 D18 D17 D16

Data 1

D19 D18 D17 D16

Data 2

D15 D14 D13 D12

Data 2

D15 D14 D13 D12

Data 3

D11 D10 D9 D8

Data 4

D7 D6 D5 D4

Data 5

D3 D2 D1 D0

Data 3

D11 D10 D9 D8

Data 4

D7 D6 D5 D4

Data 5

D3 D2 D1 D0

—: don’t care

Command Table ($2X to 3X)

– 19 –

CXD3029R

KRAM DATA (K00)

SLED INPUT GAIN

KRAM DATA (K01)

SLED LOW BOOST FILTER A-H

KRAM DATA (K02)

SLED LOW BOOST FILTER A-L

KRAM DATA (K03)

SLED LOW BOOST FILTER B-H

KRAM DATA (K04)

SLED LOW BOOST FILTER B-L

KRAM DATA (K05)

SLED OUTPUT GAIN

KRAM DATA (K06)

FOCUS INPUT GAIN

KRAM DATA (K07)

SLED AUTO GAIN

KRAM DATA (K08)

FOCUS HIGH CUT FILTER A

KRAM DATA (K09)

FOCUS HIGH CUT FILTER B

KRAM DATA (K0A)

FOCUS LOW BOOST FILTER A-H

KRAM DATA (K0B)

FOCUS LOW BOOST FILTER A-L

KRAM DATA (K0C)

FOCUS LOW BOOST FILTER B-H

KRAM DATA (K0D)

FOCUS LOW BOOST FILTER B-L

KRAM DATA (K0E)

FOCUS PHASE COMPENSATE FILTER A

KRAM DATA (K0F)

FOCUS DEFECT HOLD GAIN

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

KD7

KD7

KD7

KD7

KD7

KD7

KD7

KD7

KD7

KD7

KD7

KD7

KD7

KD7

KD7

KD7

KD6

KD6

KD6

KD6

KD6

KD6

KD6

KD6

KD6

KD6

KD6

KD6

KD6

KD6

KD6

KD6

KD5

KD5

KD5

KD5

KD5

KD5

KD5

KD5

KD5

KD5

KD5

KD5

KD5

KD5

KD5

KD5

KD4

KD4

KD4

KD4

KD4

KD4

KD4

KD4

KD4

KD4

KD4

KD4

KD4

KD4

KD4

KD4

KD3

KD3

KD3

KD3

KD3

KD3

KD3

KD3

KD3

KD3

KD3

KD3

KD3

KD3

KD3

KD3

KD2

KD2

KD2

KD2

KD2

KD2

KD2

KD2

KD2

KD2

KD2

KD2

KD2

KD2

KD2

KD2

KD1

KD1

KD1

KD1

KD1

KD1

KD1

KD1

KD1

KD1

KD1

KD1

KD1

KD1

KD1

KD1

KD0

KD0

KD0

KD0

KD0

KD0

KD0

KD0

KD0

KD0

KD0

KD0

KD0

KD0

KD0

KD0

3 0 0 1 1 0 1 0 0 0 0 0 0SELECT

Regis-

ter

Command

Address 1

D23 to D20

Address 2

D19 to D16

Address 3

D15 to D12

Address 4

D11 D10 D9 D8

Data 1

D7 D6 D5 D4

Data 2

D3 D2 D1 D0

Command Table ($340X)

– 20 –

CXD3029R

KRAM DATA (K10)

FOCUS PHASE COMPENSATE FILTER B

KRAM DATA (K11)

FOCUS OUTPUT GAIN

KRAM DATA (K12)

ANTI SHOCK INPUT GAIN

KRAM DATA (K13)

FOCUS AUTO GAIN

KRAM DATA (K14)

HPTZC / AUTO GAIN HIGH PASS FILTER A

KRAM DATA (K15)

HPTZC / AUTO GAIN HIGH PASS FILTER B

KRAM DATA (K16)

ANTI SHOCK HIGH PASS FILTER A

KRAM DATA (K17)

HPTZC / AUTO GAIN LOW PASS FILTER B

KRAM DATA (K18)

FIX

KRAM DATA (K19)

TRACKING INPUT GAIN

KRAM DATA (K1A)

TRACKING HIGH CUT FILTER A

KRAM DATA (K1B)

TRACKING HIGH CUT FILTER B

KRAM DATA (K1C)

TRACKING LOW BOOST FILTER A-H

KRAM DATA (K1D)

TRACKING LOW BOOST FILTER A-L

KRAM DATA (K1E)

TRACKING LOW BOOST FILTER B-H

KRAM DATA (K1F)

TRACKING LOW BOOST FILTER B-L

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

KD7

KD7

KD7

KD7

KD7

KD7

KD7

KD7

KD7

KD7

KD7

KD7

KD7

KD7

KD7

KD7

KD6

KD6

KD6

KD6

KD6

KD6

KD6

KD6

KD6

KD6

KD6

KD6

KD6

KD6

KD6

KD6

KD5

KD5

KD5

KD5

KD5

KD5

KD5

KD5

KD5

KD5

KD5

KD5

KD5

KD5

KD5

KD5

KD4

KD4

KD4

KD4

KD4

KD4

KD4

KD4

KD4

KD4

KD4

KD4

KD4

KD4

KD4

KD4

KD3

KD3

KD3

KD3

KD3

KD3

KD3

KD3

KD3

KD3

KD3

KD3

KD3

KD3

KD3

KD3

KD2

KD2

KD2

KD2

KD2

KD2

KD2

KD2

KD2

KD2

KD2

KD2

KD2

KD2

KD2

KD2

KD1

KD1

KD1

KD1

KD1

KD1

KD1

KD1

KD1

KD1

KD1

KD1

KD1

KD1

KD1

KD1

KD0

KD0

KD0

KD0

KD0

KD0

KD0

KD0

KD0

KD0

KD0

KD0

KD0

KD0

KD0

KD0

3 0 0 1 1 0 1 0 0 0 0 0 1SELECT

Regis-

ter

Command

Address 1

D23 to D20

Address 2

D19 to D16

Address 3

D15 to D12

Address 4

D11 D10 D9 D8

Data 1

D7 D6 D5 D4

Data 2

D3 D2 D1 D0

Command Table ($341X)

– 21 –

CXD3029R

KRAM DATA (K20)

TRACKING PHASE COMPENSATE FILTER A

KRAM DATA (K21)

TRACKING PHASE COMPENSATE FILTER B

KRAM DATA (K22)

TRACKING OUTPUT GAIN

KRAM DATA (K23)

TRACKING AUTO GAIN

KRAM DATA (K24)

FOCUS GAIN DOWN HIGH CUT FILTER A

KRAM DATA (K25)

FOCUS GAIN DOWN HIGH CUT FILTER B

KRAM DATA (K26)

FOCUS GAIN DOWN LOW BOOST FILTER A-H

KRAM DATA (K27)

FOCUS GAIN DOWN LOW BOOST FILTER A-L

KRAM DATA (K28)

FOCUS GAIN DOWN LOW BOOST FILTER B-H

KRAM DATA (K29)

FOCUS GAIN DOWN LOW BOOST FILTER B-L

KRAM DATA (K2A)

FOCUS GAIN DOWN PHASE COMPENSATE FILTER A

KRAM DATA (K2B)

FOCUS GAIN DOWN DEFECT HOLD GAIN

KRAM DATA (K2C)

FOCUS GAIN DOWN PHASE COMPENSATE FILTER B

KRAM DATA (K2D)

FOCUS GAIN DOWN OUTPUT GAIN

KRAM DATA (K2E)

Not used

KRAM DATA (K2F)

Not used

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

KD7

KD7

KD7

KD7

KD7

KD7

KD7

KD7

KD7

KD7

KD7

KD7

KD7

KD7

KD7

KD7

KD6

KD6

KD6

KD6

KD6

KD6

KD6

KD6

KD6

KD6

KD6

KD6

KD6

KD6

KD6

KD6

KD5

KD5

KD5

KD5

KD5

KD5

KD5

KD5

KD5

KD5

KD5

KD5

KD5

KD5

KD5

KD5

KD4

KD4

KD4

KD4

KD4

KD4

KD4

KD4

KD4

KD4

KD4

KD4

KD4

KD4

KD4

KD4

KD3

KD3

KD3

KD3

KD3

KD3

KD3

KD3

KD3

KD3

KD3

KD3

KD3

KD3

KD3

KD3

KD2

KD2

KD2

KD2

KD2

KD2

KD2

KD2

KD2

KD2

KD2

KD2

KD2

KD2

KD2

KD2

KD1

KD1

KD1

KD1

KD1

KD1

KD1

KD1

KD1

KD1

KD1

KD1

KD1

KD1

KD1

KD1

KD0

KD0

KD0

KD0

KD0

KD0

KD0

KD0

KD0

KD0

KD0

KD0

KD0

KD0

KD0

KD0

3 0 0 1 1 0 1 0 0 0 0 1 0SELECT

Regis-

ter

Command

Address 1

D23 to D20

Address 2

D19 to D16

Address 3

D15 to D12

Address 4

D11 D10 D9 D8

Data 1

D7 D6 D5 D4

Data 2

D3 D2 D1 D0

Command Table ($342X)

– 22 –

CXD3029R

KRAM DATA (K30)

SLED INPUT GAIN (when TGup2 is accessed with

SFSK = 1)

KRAM DATA (K31)

ANTI SHOCK LOW PASS FILTER B

KRAM DATA (K32)

Not used

KRAM DATA (K33)

ANTI SHOCK HIGH PASS FILTER B-H

KRAM DATA (K34)

ANTI SHOCK HIGH PASS FILTER B-L

KRAM DATA (K35)

ANTI SHOCK FILTER COMPARATE GAIN

KRAM DATA (K36)

TRACKING GAIN UP2 HIGH CUT FILTER A

KRAM DATA (K37)

TRACKING GAIN UP2 HIGH CUT FILTER B

KRAM DATA (K38)

TRACKING GAIN UP2 LOW BOOST FILTER A-H

KRAM DATA (K39)

TRACKING GAIN UP2 LOW BOOST FILTER A-L

KRAM DATA (K3A)

TRACKING GAIN UP2 LOW BOOST FILTER B-H

KRAM DATA (K3B)

TRACKING GAIN UP2 LOW BOOST FILTER B-L

KRAM DATA (K3C)

TRACKING GAIN UP PHASE COMPENSATE FILTER A

KRAM DATA (K3D)

TRACKING GAIN UP PHASE COMPENSATE FILTER B

KRAM DATA (K3E)

TRACKING GAIN UP OUTPUT GAIN

KRAM DATA (K3F)

Not used

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

KD7

KD7

KD7

KD7

KD7

KD7

KD7

KD7

KD7

KD7

KD7

KD7

KD7

KD7

KD7

KD7

KD6

KD6

KD6

KD6

KD6

KD6

KD6

KD6

KD6

KD6

KD6

KD6

KD6

KD6

KD6

KD6

KD5

KD5

KD5

KD5

KD5

KD5

KD5

KD5

KD5

KD5

KD5

KD5

KD5

KD5

KD5

KD5

KD4

KD4

KD4

KD4

KD4

KD4

KD4

KD4

KD4

KD4

KD4

KD4

KD4

KD4

KD4

KD4

KD3

KD3

KD3

KD3

KD3

KD3

KD3

KD3

KD3

KD3

KD3

KD3

KD3

KD3

KD3

KD3

KD2

KD2

KD2

KD2

KD2

KD2

KD2

KD2

KD2

KD2

KD2

KD2

KD2

KD2

KD2

KD2

KD1

KD1

KD1

KD1

KD1

KD1

KD1

KD1

KD1

KD1

KD1

KD1

KD1

KD1

KD1

KD1

KD0

KD0

KD0

KD0

KD0

KD0

KD0

KD0

KD0

KD0

KD0

KD0

KD0

KD0

KD0

KD0

3 0 0 1 1 0 1 0 0 0 0 1 1SELECT

Regis-

ter

Command

Address 1

D23 to D20

Address 2

D19 to D16

Address 3

D15 to D12

Address 4

D11 D10 D9 D8

Data 1

D7 D6 D5 D4

Data 2

D3 D2 D1 D0

Command Table ($343X)

– 23 –

CXD3029R

KRAM DATA (K40)

TRACKING HOLD FILTER INPUT GAIN

KRAM DATA (K41)

TRACKING HOLD FILTER A-H

KRAM DATA (K42)

TRACKING HOLD FILTER A-L

KRAM DATA (K43)

TRACKING HOLD FILTER B-H

KRAM DATA (K44)

TRACKING HOLD FILTER B-L

KRAM DATA (K45)

TRACKING HOLD FILTER OUTPUT GAIN

KRAM DATA (K46)

TRACKING HOLD INPUT GAIN (when TGup2 is

accessed with THSK = 1)

KRAM DATA (K47)

Not used

KRAM DATA (K48)

FOCUS HOLD FILTER INPUT GAIN

KRAM DATA (K49)

FOCUS HOLD FILTER A-H

KRAM DATA (K4A)

FOCUS HOLD FILTER A-L

KRAM DATA (K4B)

FOCUS HOLD FILTER B-H

KRAM DATA (K4C)

FOCUS HOLD FILTER B-L

KRAM DATA (K4D)

FOCUS HOLD FILTER OUTPUT GAIN

KRAM DATA (K4E)

Not used

KRAM DATA (K4F)

Not used

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

KD7

KD7

KD7

KD7

KD7

KD7

KD7

KD7

KD7

KD7

KD7

KD7

KD7

KD7

KD7

KD7

KD6

KD6

KD6

KD6

KD6

KD6

KD6

KD6

KD6

KD6

KD6

KD6

KD6

KD6

KD6

KD6

KD5

KD5

KD5

KD5

KD5

KD5

KD5

KD5

KD5

KD5

KD5

KD5

KD5

KD5

KD5

KD5

KD4

KD4

KD4

KD4

KD4

KD4

KD4

KD4

KD4

KD4

KD4

KD4

KD4

KD4

KD4

KD4

KD3

KD3

KD3

KD3

KD3

KD3

KD3

KD3

KD3

KD3

KD3

KD3

KD3

KD3

KD3

KD3

KD2

KD2

KD2

KD2

KD2

KD2

KD2

KD2

KD2

KD2

KD2

KD2

KD2

KD2

KD2

KD2

KD1

KD1

KD1

KD1

KD1

KD1

KD1

KD1

KD1

KD1

KD1

KD1

KD1

KD1

KD1

KD1

KD0

KD0

KD0

KD0

KD0

KD0

KD0

KD0

KD0

KD0

KD0

KD0

KD0

KD0

KD0

KD0

3 0 0 1 1

0 1 0 0 0 1 0 0

SELECT

Regis-

ter

Command

Address 1

D23 to D20

Address 2

D19 to D16

Address 3

D15 to D12

Address 4

D11 D10 D9 D8

Data 1

D7 D6 D5 D4

Data 2

D3 D2 D1 D0

Command Table ($344X)

– 24 –

CXD3029R

Regis-

ter

Command Table ($348X to 3FX)

PGFS, PFOK, RFAC

DOUT

Booster Surf Brake

Booster

DFCT

FCS Bias Limit

FCS Bias Data

Traverse Center Data

3

1

1

1

1

1

1

0

0

0

1

1

1

0

1

1

0

1

1

0

0

1

0

0

1

PGFS1

A/D

SEL

SFBK1

THBON

IDFS3

1

0

0

PGFS0

COPY

EN

SFBK2

FHBON

IDFS2

0

1

0

PFOK1

EMPH

D

0

TLB10N

IDFS1

FBL9

FB9

TV9

PFOK0

CAT

b8

0

FLB1ON

IDFS0

FBL8

FB8

TV8

0

DOUT

EN1

LB1

SN

TLB2ON

0

FBL7

FB7

TV7

0

DOUT

DMUT

LB2

SN

0

DF

SLS

FBL6

FB6

TV6

0

DOUT

WOD

LB2

SM

HBST1

IDFT1

FBL5

FB5

TV5

MRS

WIN

EN

0

HBST0

IDFT0

FBL4

FB4

TV4

MRT1

DOUT

EN2

0

LB1S1

0

FBL3

FB3

TV3

MRT0

0

0

LB1S0

0

FBL2

FB2

TV2

0

0

0

LB2S1

LPDF

0

FBL1

FB1

TV1

0

0

0

LB2S0

INVRFDC

—

—

TV0

SELECT

Command

Address 1 Address 2

D23 to D20

Address 3

D15

D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D1 D0D3 D2

Data 3Data 2Data 1Address 3

D14 D13 D12

Data 1

D11 D10 D9 D8

Data 2

D7 D6 D5 D4

Data 3

D3 D2 D1 D0

0 0 1 1

D19 to D16

0 1 0 0

– 25 –

CXD3029R

FCS search, AGF

TRK jump, AGT

FZC, AGC, SLD move

DC measure, cancel

Serial data readout

FCS Bias, Gain,

Surf jump/brake

Gain

FOCUS

Mirr, DFCT, FOK

TZC, COUT, Bottom,

MIRR

SLD filter

Filter

Clock, others

3

FT1

TDZC

FZSH

VCLM

DAC

0

1

1

SFO2

COSS

SFID

F1NM

0

1

0

1

0

1

0

1

0

1

0

1

0

1

1

0

0

1

1

0

0

1

1

1

1

1

0

0

0

0

1

1

1

1

0

0

0

1

1

1

1

1

1

1

1

FT0

DTZC

FZSL

VCLC

SD6

FBON

0

0

SFO1

COTS

SFSK

F1DM

AGG4

FS5

TJ5

SM5

FLM

SD5

FBSS

0

0

SDF2

CETZ

THID

F3NM

XT4D

FS4

TJ4

SM4

FLC0

SD4

FBUP

0

1

SDF1

CETF

THSK

F3UM

XT2D

FS3

TJ3

SM3

RFLM

SD3

FBV1

FPG

S1

0

MAX2

COT2

ABEF

T1NM

0

FS2

TJ2

SM2

RFLC

SD2

FBV0

FPG

S0

0

MAX1

COT1

TLD2

T1UM

DRR2

FS1

TJ1

SM1

AGF

SD1

FIF

ZC

TPG

S1

0

SFOX

MOT2

TLD1

T3NM

DRR1

FS0

TJ0

SM0

AGT

SD0

TJD0

TPG

S0

0

BTF

0

TLD0

T3DM

DRR0

FTZ

SFJP

AGS

DFSW

0

FPS1

0

UD

FZC

D2V2

BTS1

SDF6

DFIS

0

FG6

TG6

AGJ

LKSW

0

FPS0

0

0

D2V1

BTS0

SDF5

TLCD

ASFG

FG5

TG5

AGGF

TBLM

0

TPS1

0

0

D1V2

MRC1

SDF4

0

FTQ

FG4

TG4

AGGT

TCLM

0

TPS0

0

0

D1V1

MRC0

SDF3

LKIN

1

FG3

TG3

AGV1

FLC1

0

SVDA

0

0

RINT

0

0

COIN

SRO1

FG2

TG2

AGV2

TLC2

0

SJHD

0

0

0

0

0

MDFI

0

FG1

TG1

AGHS

TLC1

0

INBK

0

0

0

0

0

MIRI

AGHF

FG0

TG0

AGHT

TLC0

0

MTI0

0

0

0

0

0

XT1D

ASOT

SELECT

Regis-

ter

Command

Address 1 Address 2

D23 to D20 D19 D18 D17 D16

Data 1

D15 D14 D13 D12

Data 2

D11 D10 D9 D8

Data 3

D7 D6 D5 D4

Data 4

D3 D2 D1 D0

0 0 1 1

Command Table ($34FX to 3FX) cont.

System GAIN

FOCUS

1

1

0

0

0

0

0

1

SYG3

FSUD

SYG2

FFS

UP

SYG1

0

SYG0

1

FI

FZB3

0

FI

FZB2

0

FI

FZB1

FFS5

FI

FZB0

FFS4

FI

FZA3

FFS3

FI

FZA2

FFS2

FI

FZA1

FFS1

FI

FZA0

FFS0

Address 2

D19 D18 D17 D16

Address 3

D15 D14 D13 D12

Data 1

D11 D10 D9 D8

Data 2

D7 D6 D5 D4

Data 3

D3 D2 D1 D0

1

111

– 26 –

CXD3029R

Command Table ($4X to EX)

—: don’t care

Auto sequence

Blind (A, E),

Brake (B),

Overflow (C, G)

Sled KICK,

BRAKE (D),

KICK (F)

Auto sequence (N)

track jump count

setting

MODE

specification

Function

specification

0

0

0

0

1

1

1

1

1

1

0

0

0

0

1

1

0

0

0

1

0

1

0

1

AS3

TR3

SD3

32768

CD-

ROM

1

AS2

TR2

SD2

16384

DOUT

Mute

DSPB

ON-OFF

AS1

TR1

SD1

8192

DOUT

Mute-F

ASEQ

ON-OFF

AS0

TR0

SD0

4096

WSEL

1

MT3

0

KF3

2048

VCO

SEL2

BiliGL

MAIN

MT2

0

KF2

1024

ASHS

BiliGL

SUB

MT1

0

KF1

512

SOCT0

FLFC

MT0

0

KF0

256

VCO

SEL1

0

LSSL

0

0

128

KSL3

0

0

0

0

64

KSL2

0

0

0

0

32

KSL1

0

0

0

0

16

KSL0

0

—

—

—

8

VCO1

CS1

1

—

—

—

4

VCO1

CS0

0

—

—

—

2

0

0

—

—

—

1

0

1

4

5

6

7

8

9

Regis-

ter

Command

Address

D3 D2 D1 D0 D3 D2 D1 D0 D3 D2 D1 D0 D3 D2 D1 D0 D3 D2 D1 D0

Data 1 Data 2 Data 3 Data 4

– 27 –

CXD3029R

Command Table ($4X to EX) cont.

Audio CTRL

Signal select

Bass boost

Headphone

Shock-proof

memory setting

Shock-proof

memory control

DOUT subcode-Q

setting

DRAM I/F

Compression

setting

EFM playability

enhancement settin

g

Sync expansion

specification

101

0

0

0

0

0

0

1

1

1

1

1

0

1

1

1

1

0

0

0

0

1

Mute

0

0

1

1

0

0

1

1

0

ATT

0

1

0

1

0

1

0

1

0

PCT1

RSL1

0

0

1

1

0

0

1

1

SL

XQOK

XQOK

SubQA3

1

1

ADPON

ARDTEN

AVW

PCT2

RSL0

0

1

0

1

0

1

0

1

SL

XWRE

XWRE

SubQA2

1

1

BITSL1

1

0

0

0

1

PWDN

BBON1

COMP

ON

1

PWDN

BBON1

COMP

ON

GTOP

CHECK

XRDE

SubQA1

1

1

BITSL0

1

SFP5

SOC2

0

ZMUTA

ZDPL

BBON0

0

ZMUTA

ZDPL

BBON0

0

NOLIM

WDCK

XSOEO

SubQA0

0

1

0

1

SFP4

0

DTSL1

SMUT

WOC

HBON1

0

SMUT

XWOC

HBON1

0

SPSL

COM

XSOEO2

0

1

DADR19

ADP

WO

1

SFP3

0

DTSL0

AD10

DAC

EMPH

HBON0

0

AD10

DAC

EMPH

HBON0

0

READ2

ADDRST

0

DRWR

DADR18

0

0

SFP2

0

MCSL1

AD9

HiCut

FILTER

BBSL1

0

AD9

HiCut

FILTER

BBSL1

0

REFSEL

SCOR

MOD

0

DRADR

DADR17

0

1

SFP1

0

MCSL0

AD8

BST

CL

BBSL0

0

AD8

BST

CL

BBSL0

0

REFON

SDTO

OUT

0

0

DADR16

0

0

SFP0

0

0

AD7

1

HBSL1

0

AD7

1

HBSL1

0

XOE

OUT

SubQD7

DRD15

DADR15

0

0

0

1

SDSL2

AD6

0

HBSL0

0

AD6

0

HBSL0

0

MSL2

SubQD6

DRD14

DADR14

GRSEL

0

0

0

SDSL1

AD5

OBIT1

BBST

Vdwn1

1

AD5

OBIT1

BBST

Vdwn1

1

MSL1

SubQD5

DRD13

DADR13

0

1

0

0

SDSL0

AD4

OBIT0

BBST

Vdwn0

0

AD4

OBIT0

BBST

Vdwn0

0

MSL0

SubQD4

DRD12

DADR12

0

0

0

A

Regis-

ter

Command

Address

D3 D2 D1 D0 D3 D2 D1 D0 D3 D2 D1 D0 D3 D2 D1 D0 D3 D2 D1 D0

Data 1 Data 2 Data 3 Data 4

– 28 –

CXD3029R

Command Table ($4X to EX) cont.

1

1

1

1

0

1

1

1

1

0

0

1

1

0

1

0

1010

1

1

1

32768

Gain

MDP1

0

CM3

Sleep setting

Variable pitch

setting

Spindle servo

setting

Traverse monitor

counter setting

Spindle servo

coefficient setting

CLV CTRL

SPD mode

1

1

1

16384

Gain

MDP0

TB

CM2

0

1

1

8192

Gain

MDS1

TP

CM1

1

0

1

4096

Gain

MDS0

Gain

CLVS

CM0

ADCPS

VARI

ON

SYG3

EA

2048

Gain

DCLV1

VP7

EPWM

DSP

SLEEP

VARI

USE

SYG2

EA

1024

Gain

DCLV0

VP6

SPD

DSSP

SLEEP

WTC

C2PO

SYG1

EA

512

PCC1

VP5

ICAP

ASYM

SLEEP

SCSY

(sub)

SYG0

EA

256

PCC0

VP4

SFSL

ESP

SLEEP

SENS

SEL3

MDP

OUTSL1

128

SFP3

VP3

VC2C

LPF

SLEEP

SENS

SEL2

MDP

OUTSL0

64

SFP2

VP2

HIFC

DSUB

SLEEP

SENS

SEL1

LPWR2

32

SFP1

VP1

LPWR

ASEQ

SLEEP

SENS

SEL0

0

16

SFP0

VP0

VPON

PCOL

MDS

CTL

8

SRP3

VP

CTL1

Gain

CAV1

HCAV

SLEEP

MDP

UP

4

SRP2

VP

CTL0

Gain

CAV0

0

0

2

SPR1

0

0

0

MDP

CTL4

1

SRP0

0

INV

VPCO

B

C

D

E

A

Regis-

ter

Command

Address

D3 D2 D1 D0 D3 D2 D1 D0 D3 D2 D1 D0 D3 D2 D1 D0 D3 D2 D1 D0

Data 1 Data 2 Data 3 Data 4

– 29 –

CXD3029R

—: don’t care

Command Table ($4X to EX) cont.

MODE

specification

Function

specification

AUDIO CTRL

Signal select

Bass boost

Headphone

Shock-proof

memory setting

DOUT subcode-Q

setting

DRAM I/F

Compression

setting

8

9

A

1 0 0 0

1 0 0 1

1 0 1 0

0 0 ∗ ∗

0 1 0 0

0 1 0 1

0 1 1 0

0 1 1 1

1 0 0 1

1 0 1 0

0 0 1 ∗

0 1 ∗ ∗

1 0 ∗ ∗

1 1 ∗ 0

001∗

01∗ ∗

10∗ ∗

11∗ 0

∗∗∗∗

1 1 1 0

1 1 1 1

0 0 0 0

ERC4

0

0

EN

XSOE

AD3

0

BBST

Vup1

0

AD3

0

BBST

Vup1

0