Sony CXD1265R Datasheet

CCD Camera Timing Generator

Description

The CXD1265R generates the timing pulses

required by the CCD image sensors as well as

signal processing circuits.

Features

• NTSC and PAL compatible

• Compatible with digital and analog camera

systems

• Black-and-white mode compatible

(EIA/CCIR compatible)

• Electronic shutter function

• H-driver

• Standby function

• Compatible with field/frame accumulation

modes

∗1

∗2

∗1, ∗2

Characteristics of CCD image sensor are

guaranteed by field accumulation.

Low speed shutter can not be used during frame

accumulation mode.

CXD1265R

64 pin LQFP (Plastic)

Absolute Maximum Ratings (Ta = 25°C)

• Supply voltage VDD Vss – 0.5 to +7.0 V

• Input voltage VI Vss – 0.5 to VDD + 0.5 V

• Output voltage VO Vss – 0.5 to VDD + 0.5 V

• Operating temperature Topr –20 to +75 °C

• Storage temperature Tstg –55 to +150 °C

• Supply voltage VEE –5 to Vss V

• Allowable power dissipation

PD 500 mW

Applications

CCD cameras

Structure

Silicon gate CMOS IC

Applicable CCD Image Sensors

ICX038BNA, ICX038BNB, ICX038BLA

ICX039BNA, ICX039BNB, ICX039BLA

ICX058AK, ICX058AKB, ICX058AL

ICX059AK, ICX059AKB, ICX059AL

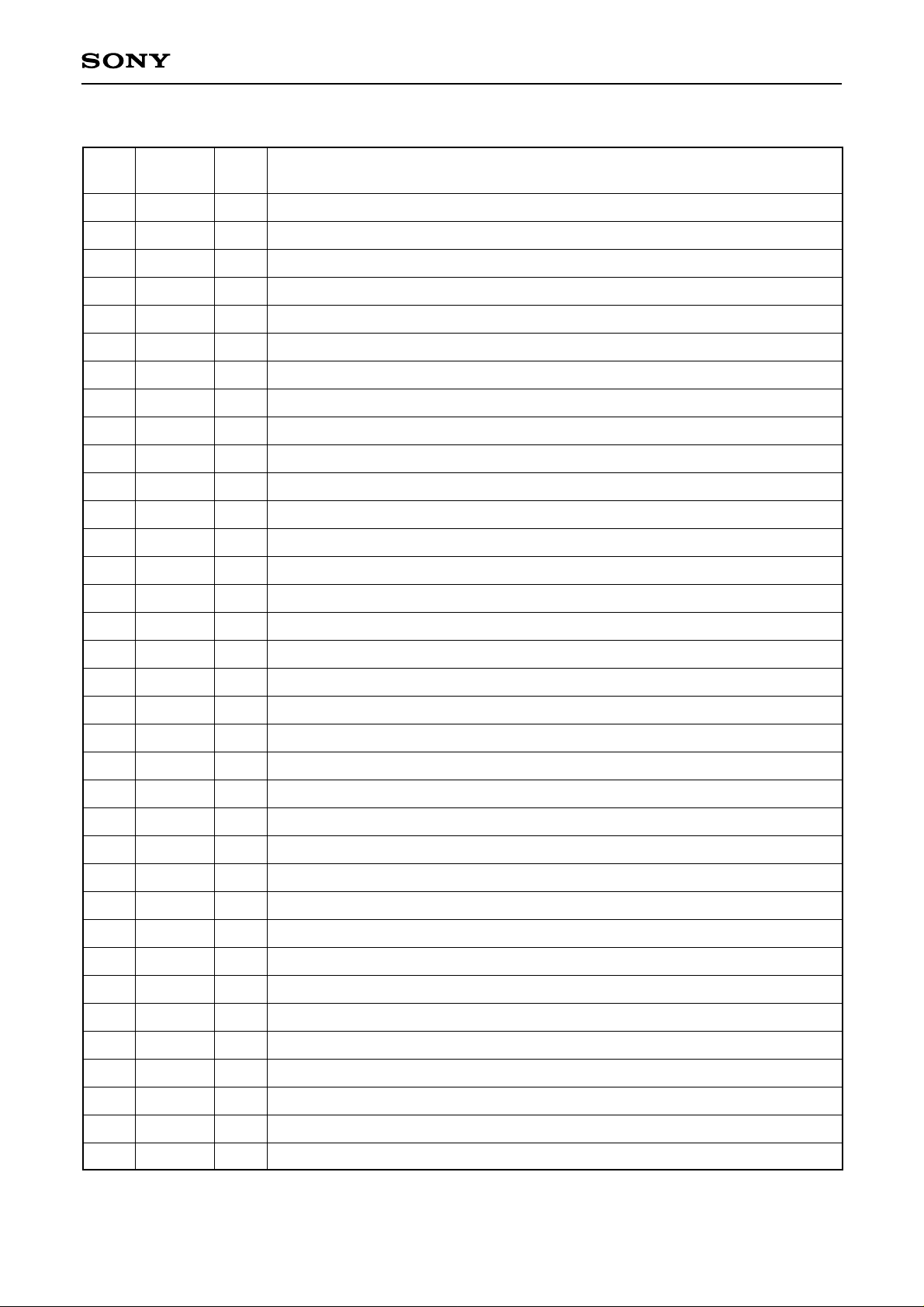

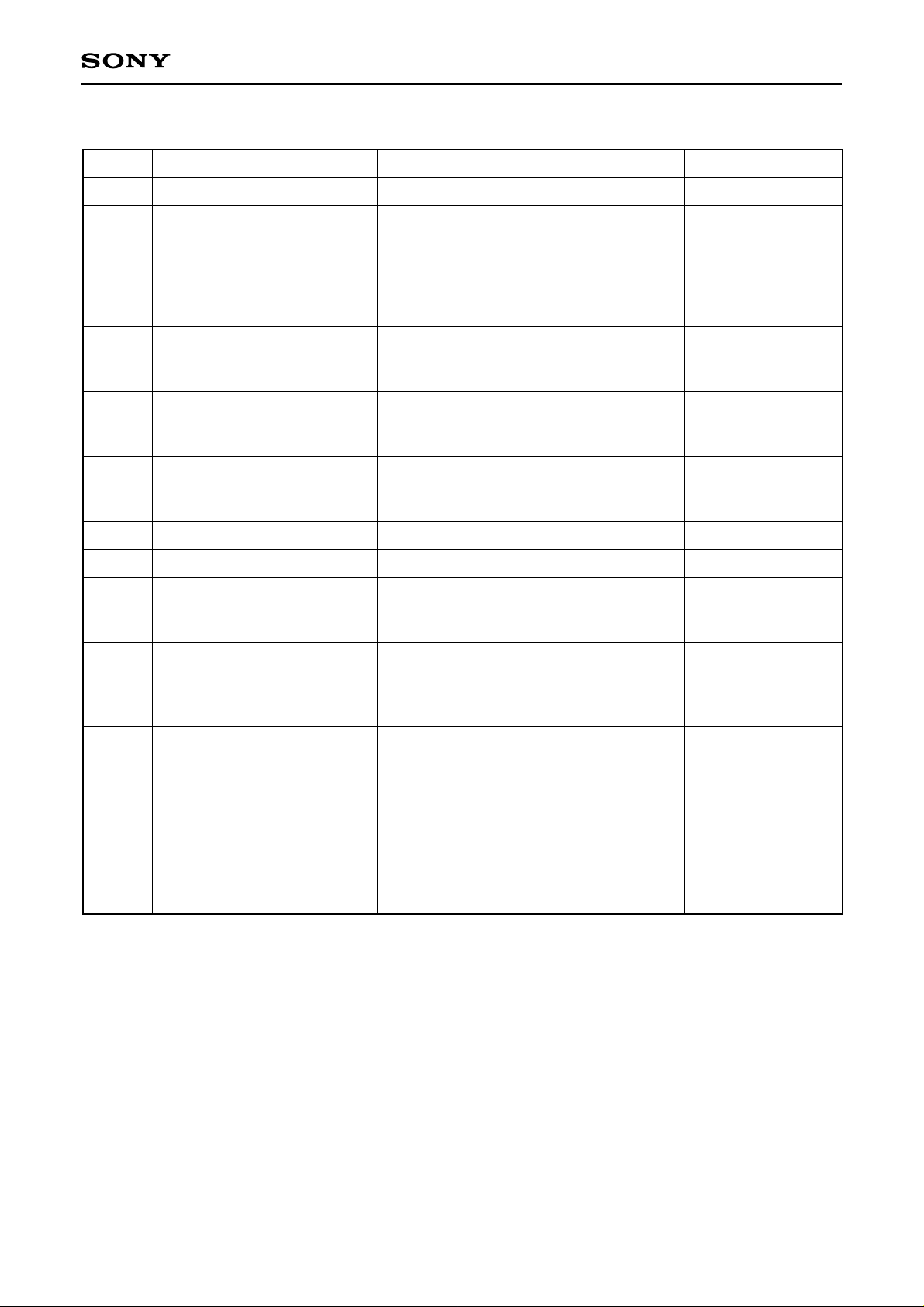

Block Diagram

62

VD INITIALIZE

60

SYNC

GEN

59

57

63

64

1

2

41

42

43

44

45

46

22

37

HD INITIALIZE

HIGH-SPEED

GENERATION

CIRCUIT

PULSE

38

39

1/2

23

VSS

40

28

8

ADR . COUNT

DRIVER

26

27

VDD

24

H – ROM

LATCH

GATE

10

3

56

25

DECODER

GATE

48

47

Recommended Operating Conditions

• Supply voltage VDD 5.0 ± 0.25 V

• Operating temperature Topr –20 to +75 °C

VEE

ADR . COUNT

V – ROM

LATCH

GATE

COUNTER

49

51

50

52

21

53

MODE

SET

ADR . COUNT

ROG – ROM

LATCH

SHUT

ROM

54

29

30

15

31

19

18

17

16

GATE

CONTROLLER

DECODER

32

35

33

34

20

11

12

13

14

23

36

61

HTSG

4

5

MICROCOMPUTER

6

7

9

55

58

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

– 1 –

E92611C52-ST

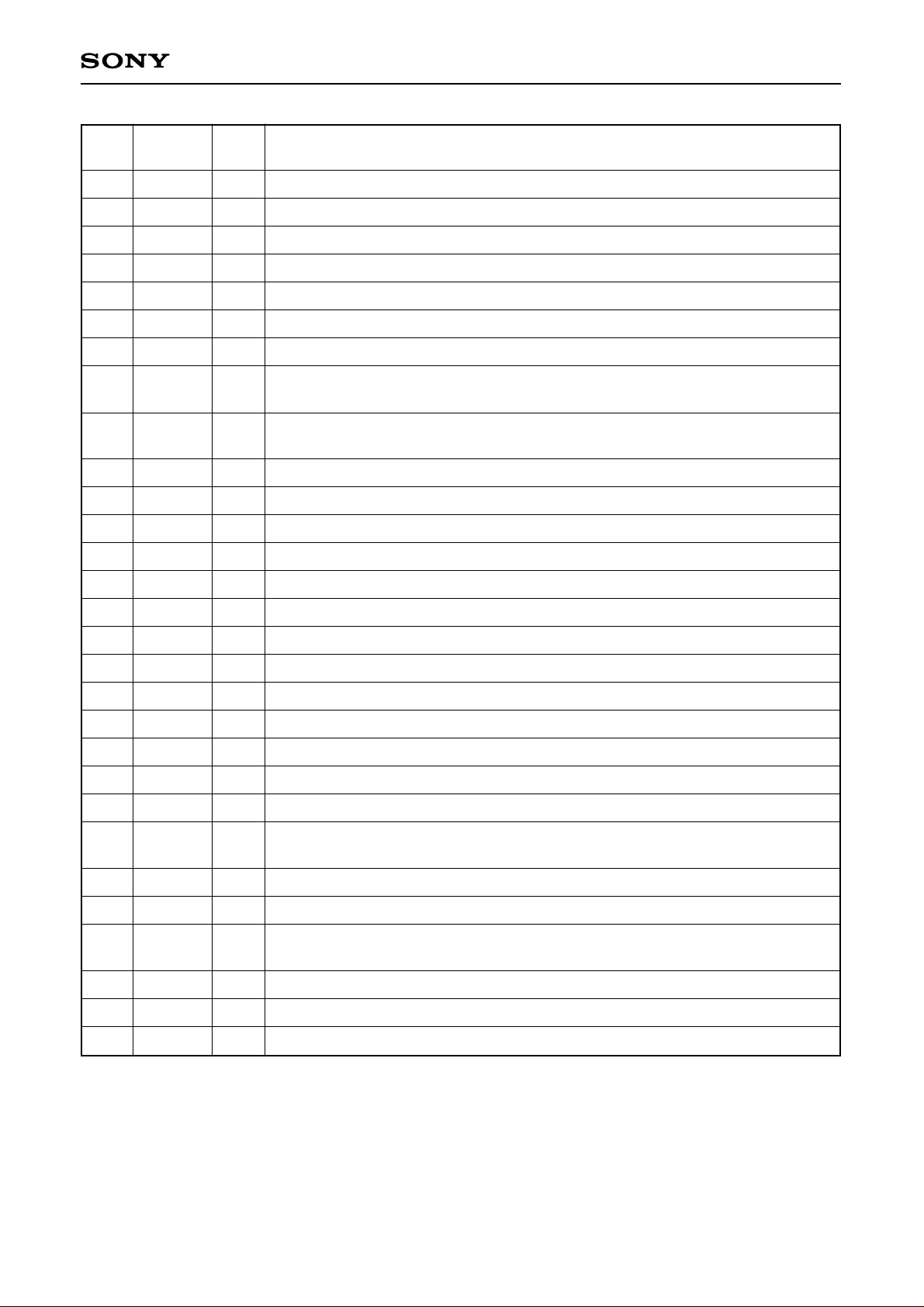

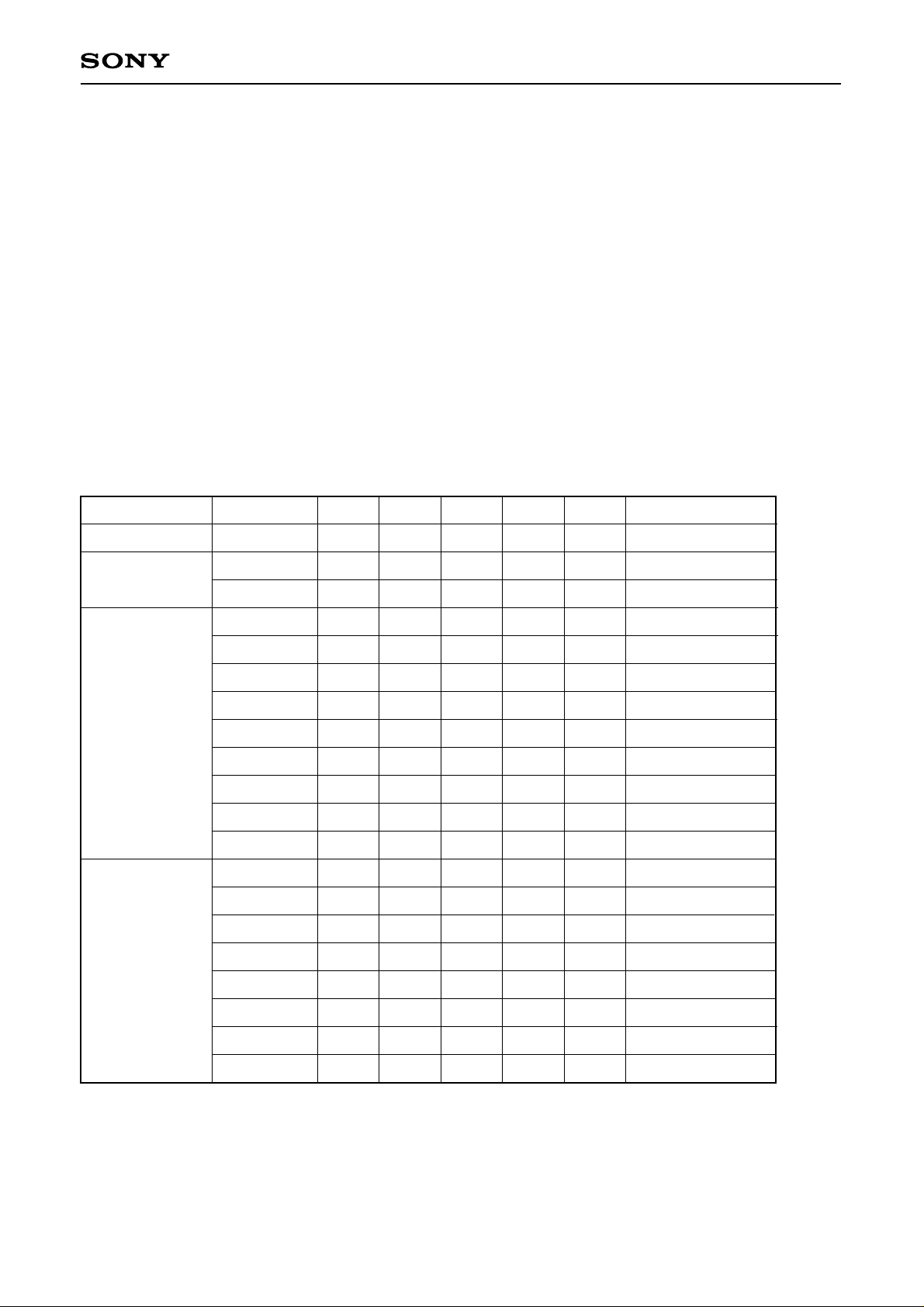

Pin Description

CXD1265R

Pin

No.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

Symbol I/O Description

OSCO

OSCI

EF

ED0

ED1

ED2

SMD1

Vss

SMD2

XVCT

D1

D2

D3

D4

A5

O

Inverter output for oscillation.

I

Inverter input for oscillation.

I

Not used. (With pull-up resistor)

I

Shutter speed setting. Strobe input for serial mode. (With pull-up resistor)

I

Shutter speed setting. Clock input for serial mode. (With pull-up resistor)

I

Shutter speed setting. Data input for serial mode. (With pull-up resistor)

I

Shutter mode setting. (With pull-up resistor)

—

GND

I

Shutter mode setting. (With pull-up resistor)

O

Not used. (Open)

I

Fix at Low in normal operation. (With pull-down resistor)

I

Low: Color, High: Black-and-white. (With pull-down resistor)

I

Low: Field readout, High: Frame readout∗. (With pull-down resistor)

I

Low: NTSC/EIA, High: PAL/CCIR. (With pull-down resistor)

O

Not used. (Open)

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

A4

A3

A0

A1

A2

VEE

RG

NC

VDD

VDD

H1

H2

Vss

XSUB

XV2

XV1

XSG1

O

Not used. (Open)

O

Not used. (Open)

O

Not used. (Open)

O

Not used. (Open)

O

Not used. (Open)

—

GND

O

Reset gate pulse output.

—

Not used. (Open)

—

Power supply.

—

Power supply for H1 and H2.

O

Clock output for CCD horizontal register drive.

O

Clock output for CCD horizontal register drive.

—

GND for H1 and H2.

O

CCD discharge pulse output.

O

Clock output for CCD vertical register drive.

O

Clock output for CCD vertical register drive.

O

CCD sensor charge readout pulse output.

33

XV3

34

XSG2

35

XV4

∗

Characteristics of CCD image sensor are guaranteed by field accumulation.

O

Clock output for CCD vertical register drive.

O

CCD sensor charge readout pulse output.

O

Clock output for CCD vertical register drive.

– 2 –

CXD1265R

Pin

No.

36

37

38

39

40

41

42

43

44

45

46

47

48

49

Symbol I/O Description

TEST2

MCK

XSHP

XSHD

Vss

XSP1

XSP2

XSH1/

SHP

XSH2/

SHD

XDL1

XDL2

BFG

CLP1

CLP2

I

Test input. Set at Low in normal operation.

O

NTSC: 910fH, PAL: 908fH. Clock output.

O

Precharge level sample-and-hold pulse.

O

Data sample-and-hold pulse.

—

GND

O

Color separation sample-and-hold pulse. Halted for black-and-white mode.

O

Color separation sample-and-hold pulse. Halted for black-and-white mode.

Switching sample-and-hold pulse/precharge level sample-and-hold pulse

O

(black-and-white mode).

Switching sample-and-hold pulse/data sample-and-hold pulse

O

(black-and-white mode).

O

Delay line clock output. Halted for black-and-white mode.

O

Delay line clock output. Halted for black-and-white mode.

O

Pulse output for chroma modulator in encoder. Halted for black-and-white mode.

O

Clamp pulse output.

I/O

Clamp pulse output. When GM is set at High, standby mode switching input.

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

CLP3

CLP4

PBLK

ID

WEN

GM

VDD

CL

PS

HD

VD

HTSG

TEST

XCK

CK

I/O

Clamp pulse output. When GM is set at High, standby mode switching input.

O

Clamp pulse output.

O

Blanking cleaning pulse output.

O

Line identification output. Halted for black-and-white mode.

O

Write enable output for low-speed shutter operation.

I

Low: Analog signal processing, High: Digital signal processing. (With pull-down resistor)

—

Power supply.

O

NTSC/EIA: 910fH, PAL/CCIR: 908fH. Clock output.

Switching for electronic shutter speed input method. (With pull-up resistor)

I

Low: Serial input, High: Parallel input.

I

Horizontal synchronizing signal input.

I

Vertical synchronizing signal input. (During Low, 9H for NTSC and 7.5H for PAL)

Control input for XSG1 and XSG2. (With pull-up resistor)

I

Low: XSG1, XSG2 halted, High: XSG1, XSG2 generated.

I

Test input. Set at Low in normal operation. (With pull-down resistor)

O

NTSC/EIA: 1820fH, PAL/CCIR: 1816fH. Clock output.

I

NTSC/EIA: 1820fH, PAL/CCIR: 1816fH. Clock input.

– 3 –

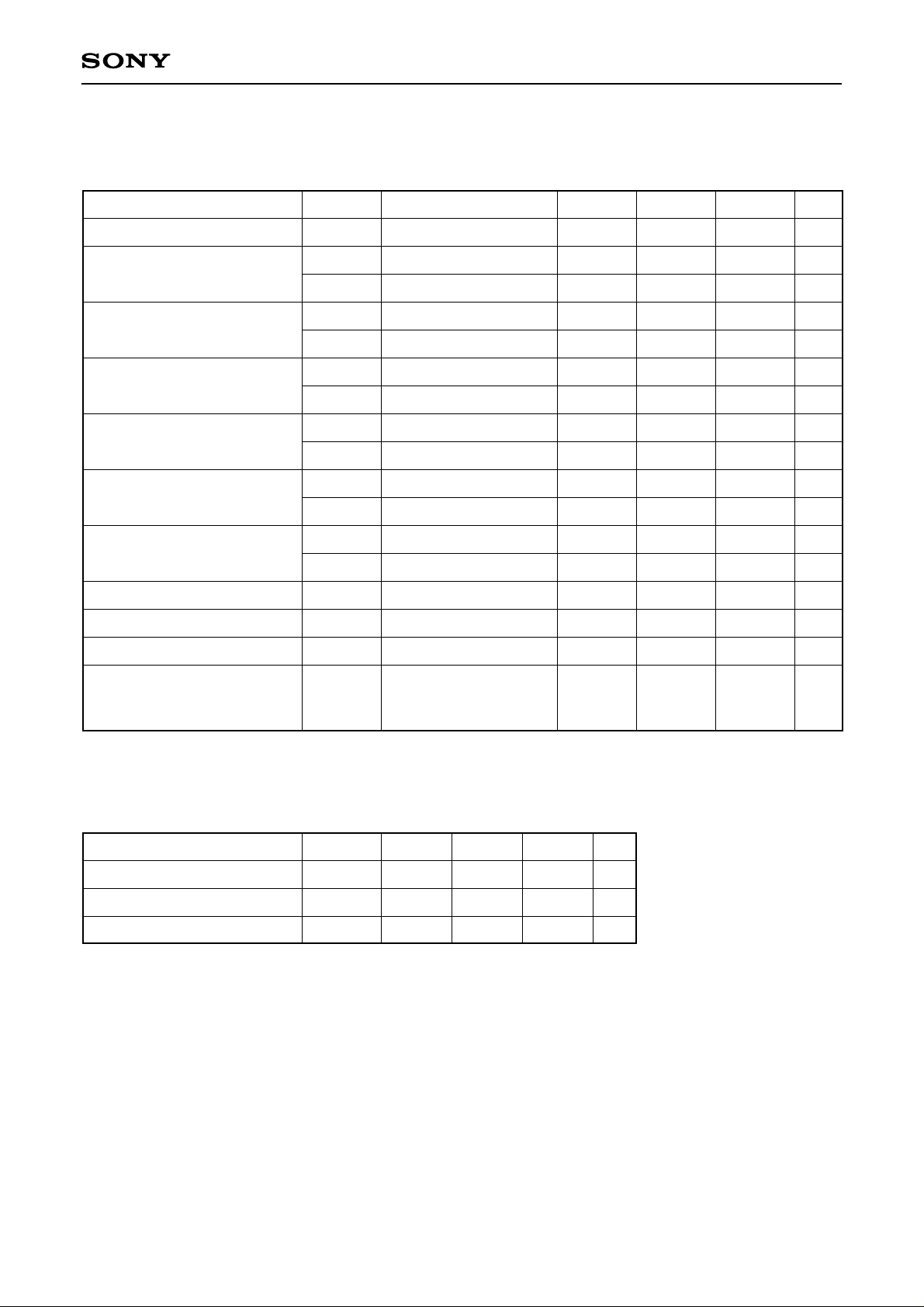

CXD1265R

Electrical Characteristics

DC Characteristics (VDD = 5V ± 0.25V, Topr = –20 to +75°C)

Item

Symbol Conditions Min. Typ. Max. Unit

Supply voltage VDD

Input voltage 1

(Input pins other than those below)

Input voltage 2

(Pins 59 and 60)

Output voltage 1

(Output pins other than those below)

Output voltage 2

(Pins 22, 37, 38, 39, 57, and 63)

Output voltage 3

(Pins 26 and 27)

Output voltage 4

(Pin 1)

Feedback resistor

Pull-up resistor

Pull-down resistor

VIH1

VIL1

VIH2

VIL2

VOH1

VOL1

VOH2

VOL2

VOH3

VOL3

VOH4

VOL4

RFB

RPU

RPD

IOH = –2mA

IOL = 4mA

IOH = –4mA

IOL = 8mA

IOH = –8mA

IOL = 8mA

IOH = –1mA

IOL = 1mA

VIN = Vss or VDD

VIL = 0V

VIH = VDD

VDD = 5V

Current consumption

IDD

ICX058AK in normal

operating state

∗

Power consumption: 370mW typ., ICX058 load (in normal operating state)

4.75

0.7VDD

2.2

VDD – 0.5

VDD – 0.5

VDD – 0.5

VDD/2

500k

40k

40k

5.0

2M

100k

100k

74

5.25

0.3VDD

0.8

0.4

0.4

0.4

VDD/2

5M

250k

250k

V

V

V

V

V

V

V

V

V

V

V

V

V

Ω

Ω

Ω

mA

I/O Pin Capacitances

Item

Input pin capacitance

Output pin capacitance

I/O pin capacitance

(VDD = VI = 0V, fM = 1MHz)

Symbol Min. Typ. Max. Unit

CIN

COUT

CI/O

9

11

11

pF

pF

pF

– 4 –

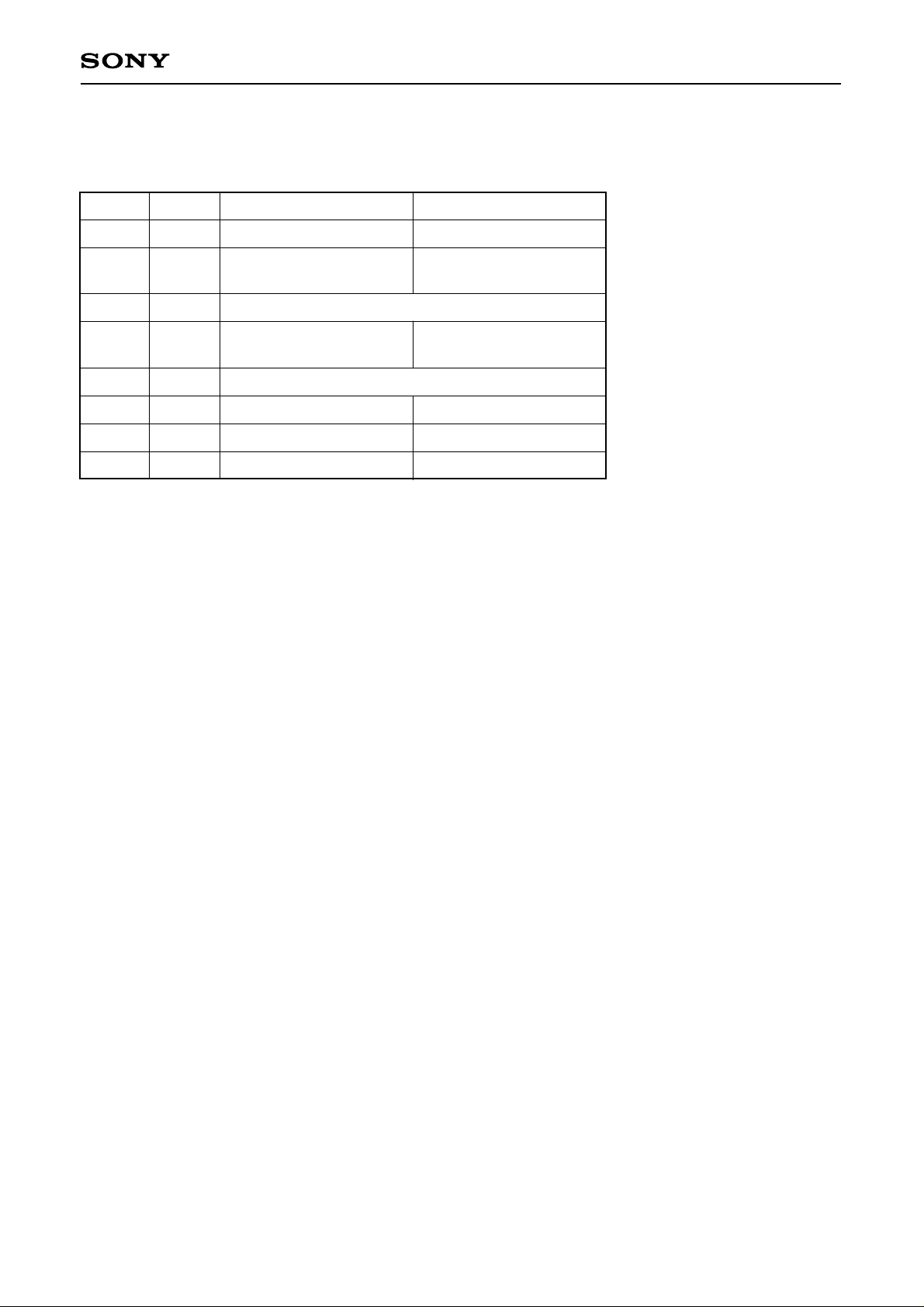

Description of Operation

1. Mode Control

CXD1265R

Symbol

GM

PS

EF

HTSG

D1

D2

D3

D4

∗1

Characteristics of CCD image sensor are guaranteed by field accumulation.

∗2

Operation with GM = High and D2 = High (black-and-white digital signal processing) cannot be used.

Pin No. L H

∗2

∗2

55

58

3

61

11

12

13

14

Analog signal processing Digital signal processing

Serial shutter Parallel shutter

speed setting speed setting

Fix at High in normal operation

XSG1, 2 XSG1, 2

OFF ON

Fix at Low in normal operation

Color Black-and-white

Field readout Frame readout

NTSC/EIA PAL/CCIR

∗1

– 5 –

2. Changes in I/O Signals in Each Mode

CXD1265R

Symbol

GM

D2

TEST2

XSP1

XSP2

XSH1

XSH2

XDL1

XDL2

BFG

Pin No. Analog color Digital color 1 Digital color 2 Analog B/W

55

12

36

41

42

43

44

45

46

47

Color separation

sample-and-hold

pulse output

Color separation

sample-and-hold

pulse output

Switching sampleand-hold pulse

output

Switching sampleand-hold pulse

output

Delay line clock

Delay line clock

Burst flag gate

pulse output

L

L

L

H

L

L

H

L

H

L

H

L

Color separation

Halted at High

sample-and-hold

Halted at High

pulse output

Color separation

Halted at High

sample-and-hold

Halted at High

pulse output

Halted at Low

Halted at Low

Halted at High

Halted at Low

Burst flag gate

pulse output

(normally not used)

Switching sampleand-hold pulse

output

Switching sampleand-hold pulse

output

Halted at High

Halted at Low

Burst flag gate

pulse output

(normally not used)

Precharge level

sample-and-hold

pulse output

Data sample-andhold pulse output

Halted at High

Halted at Low

Halted at Low

Standby control input

CLP2

49

Clamp pulse output

Low: Standby

High: Normal

operation

Standby control

∗

Low: All circuits

halted for

CLP3

50

Clamp pulse output

standby mode

High: Only CL

output for

standby mode

ID

∗

When CLP2 = High, normal operation occurs regardless of whether CLP3 is high or low.

53

Line identification

output

Line identification

output

Standby control input

Low: Standby

High: Normal

operation

Standby control

∗

Low: All circuits

halted for

standby mode

High: Only CL

output for

standby mode

Line identification

output

Clamp pulse output

Clamp pulse output

(phase change)

Halted at Low

(Mode combinations other than those shown above cannot be used.)

Note) In the standby mode described above, XCK, XSG1, XSG2, XV1, XV2, XV3, XV4, XSUB, H1, H2, RG,

XSHD, XSHP, XSP1, XSP2, XSH1, XSH2, XDL1, and XDL2 pins are halted at Low. MCK, CLP1, CLP4,

PBLK, ID, XVCT, WEN, BFG, A0, A1, A2, A3, A4, and A5 pins are halted at the state just before

standby.

– 6 –

3. Electronic Shutter

<Shutter Modes>

SMD1 SMD2

L L Flickerless: Eliminates fluorescent frequency-induced flicker.

L H High-speed shutter: Shutter speed faster than 1/60 (NTSC), 1/50 (PAL)

H L Low-speed shutter: Shutter speed slower than 1/60 (NTSC), 1/50 (PAL)

H H No shutter operation

<Shutter Mode and Speed Setting Method>

PS = High: Parallel input; set by ED0 to ED2, SMD1, and SMD2.

PS = Low: Serial input; set by inputting ED0 (strobe), ED1 (clock), and ED2 (data) to each pin.

3-1. Parallel input (PS = H)

Shutter Speed Compatibility Chart

CXD1265R

Mode

OFF

Flickerless

High-speed

shutter

Low-speed

shutter

∗

NTSC/PAL

X

NTSC

PAL

NTSC

PAL

X

X

X

X

X

X

X

X

X

X

X

X

SMD1 SMD2 ED0 ED1 ED2 Shutter speed

H

L

L

L

L

L

L

L

L

L

L

L

H

H

H

H

H

H

L

L

H

H

H

H

H

H

H

H

H

L

L

L

L

L

X

X

X

H

H

L

H

L

H

L

H

L

H

L

H

L

H

X

X

X

H

H

H

L

L

H

H

L

L

H

H

L

L

H

X

X

X

H

H

H

H

H

L

L

L

L

H

H

H

H

L

Shutter off

1/100 (S)

1/120 (S)

1/60 (S)

1/50 (S)

1/125 (S)

1/250 (S)

1/500 (S)

1/1000 (S)

1/2000 (S)

1/4000 (S)

1/10000 (S)

2FLD

4FLD

6FLD

8FLD

10FLD

X

X

X

∗

During frame accumulation mode, low speed shutter data set to ED0 to ED2 are all invalid.

H

H

H

L

L

L

L

H

L

H

L

L

L

12FLD

L

14FLD

L

16FLD

Shutter speed is 1/30s for NTSC; 1/25s for PAL.

– 7 –

CXD1265R

3-2. serial input (PS=L)

For serial input (PS = L), SMD1 and SMD2 bits within ED2 (DATA) take priority over SMD1 (Pin 7) and SMD2

(Pin 9) pins as SMD1 and SMD2 (shutter mode control).

In this case, control by SMD1 and SMD2 pins is invalid.

ED1 (CLK)

ED2 (DATA)

ED0 (STB)

ED2 data is latched to the register at the rise of ED1, and transferred to the within during the Low period of ED0.

D0 D1

D2 D3 D4 D5 D6 D7 D8 SMD1 SMD2 Dummy

– 8 –

Loading...

Loading...