Sony CXD1254AR, CXD1254AQ Datasheet

CXD1254AR/AQ

CCD Camera Synchronization and Timing Signal Generator

Description

The CXD1254AR and CXD1254AQ Ics generates

the necessary synchronization and timing signals for

camera systems employing CCD image sensors

(ICX044, ICX045, ICX046, etc.).

Features

• Supports color (NTSC) and black & white

(EIA/CCIR) systems

• On-chip electronic shutter

• On-chip horizontal (H) driver

• Timing generator for mirror images

Applications

CCD camera systems

CXD1254AR CXD1254AQ

64 pin LQFP (Plastic) 64 pin QFP (Plastic)

Absolute Maximum Ratings (Ta=25 °C, VSS=0 V)

• Supply voltage VSS –0.5 to +7.0 V

• Input voltage VSS –0.5 to VDD +0.5 V

• Output voltage VSS –0.5 to VDD +0.5 V

• Operating temperature –20 to +75 °C

• Storage temperature –55 to +150 °C

Structure

Silicon gate CMOS IC

Recommended Operating Conditions

• Supply voltage 4.75 to 5.25 V

• Operating temperature –20 to +75 °C

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

—1—

E91845B67-TE

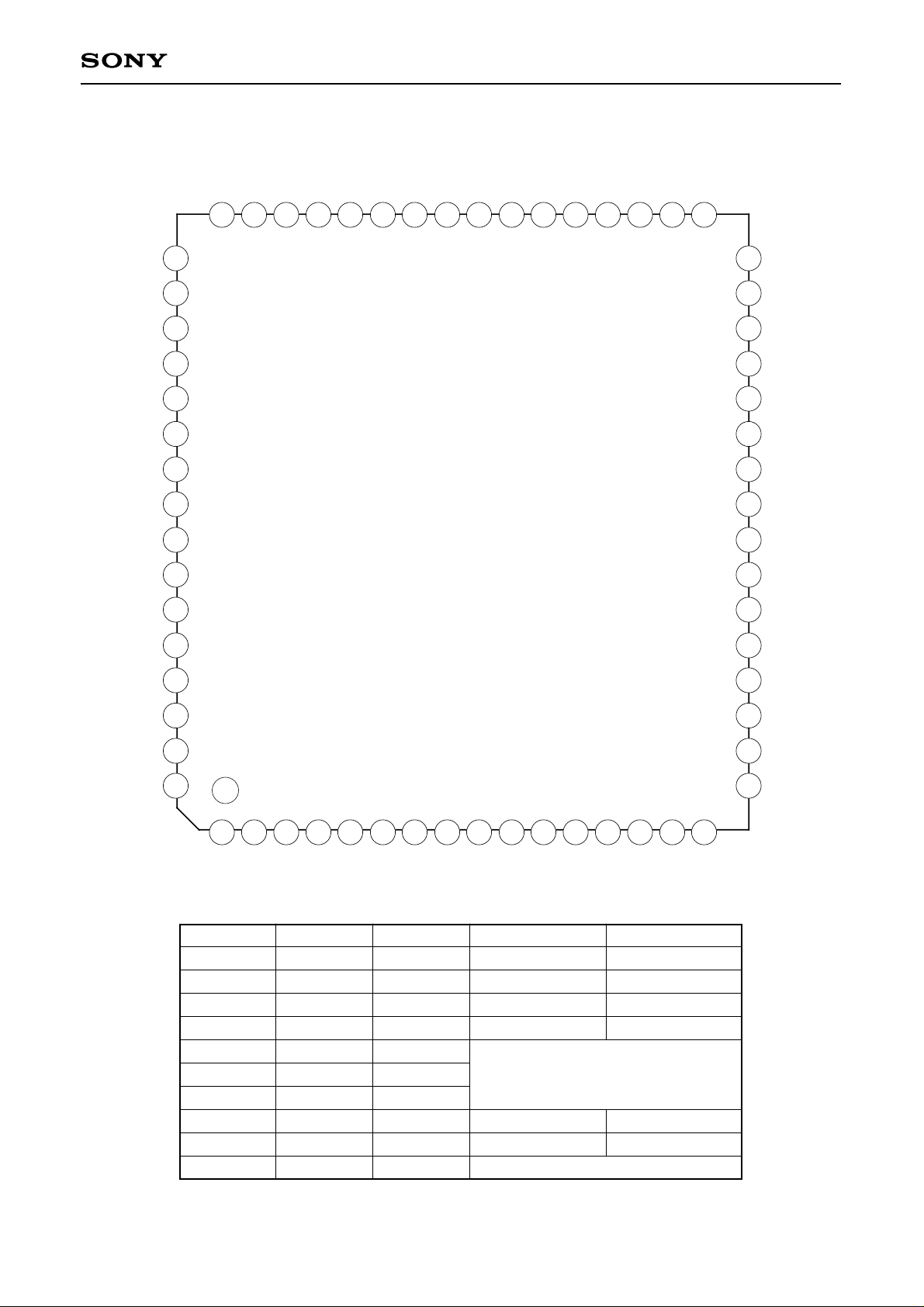

Block Diagram (Pin No.s given for CXD1254AR)

TEST2

54

TEST3

58

GENERATOR

TEST

52

EXT

48

TEST1

FLD

49

GENERATOR

RESET

1/7 or 1/6

COUNTER

1/65 COUNTER

H-DECODER

1/525 or 1/625

COUNTER

V-DECODER

V-CONTROL

CXD1254AR/AQ

4

D1

5

D2

6

D3

HD

VD

C KIN

OSCI

OSCO

PS

ED0

ED1

ED2

ENB

OUTPUT CONTROL

1

2

H-INIT

V-INIT

11

1/3

9

1/2

10

3

CL

RESET

CK

GENERATION

PHASE CONT.

16

13

14

15

12

V-RELATIVE

COUNTER

V-ROM

(VD1)

LATCH

CONVERTER

PARALLEL

SERIAL-

SELECT

SHUTTER

ROM

H-RELATIVE COUNTER

LATCH

H-ROM

(HD1)

H-ROM

(HD2)

LATCH LATCH LATCH

GATE

COUNTER/GATE

ADDRESS

COUNTER

H-ROM

(HD3)

GATE GATEGATE

LATCH

H-ROM

(RD1)

H-RELATIVE COUNTER

ADDRESS

COUNTER

H-ROM

(RD2)

BF

62

63

CBLK

64

SYNC

XDL1

XDL2

41 4342 44

H2

H3

H1

H4

XSHP

XSHD

XSP1

XSP2

RG

XSUB

PBLK

BFG

ID

CLP2

CLP1

27 2926 3121 233334 35 3618 2037 38 19 25 3945 46 28 30

XV1

XV2

CLP4

CLP3

XV3

XV4

XSG1

XSG2

—2—

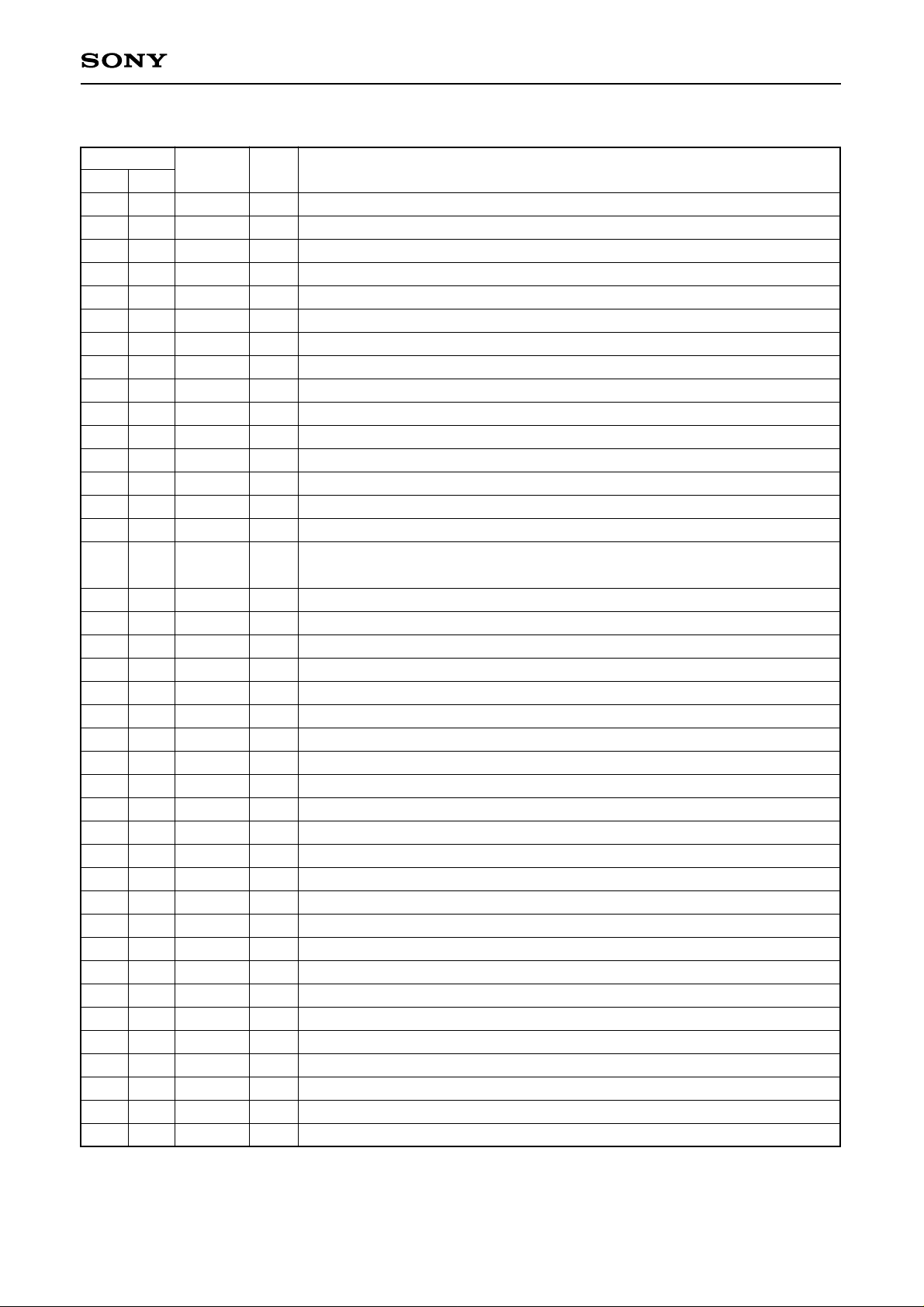

Pin Configuration (1)

CXD1254AR/AQ

FLD

HTSG

DD

V

EXT

SS

V

TEST2

NC

DD

V

NC

TEST3

SS

V

49

50

51

52

53

54

55

56

57

58

59

TEST1

DD

V

SS

CLP4

CLP3

ID

PBLK

CLP2

CXD1254AR

CLP1

V

BFG

XDL2

XDL1

XSP2

XSP1

XSHD

33343536373839404142434445464748

XSHP

32

31

30

29

28

27

26

25

24

23

22

SS

V

XV4

XSG2

XV3

XSG1

XV1

XV2

XSUB

DD

V

RG

SS

AV

NC

NC

BF

CBLK

SYNC

60

61

62

63

64 17

21

20

19

18

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16

TRIG

SS

V

OSCI

OSCO

CKIN

ENB

ED0

Low High

NTSC/EIA CCIR

Normal Image Mirror Image

Color B/W

Normal Shutter

Shutter Speed

Serial input Parallel input

Internal External

Normally Low

ED1

ED2

PS

Mode

D1

D2

D3

ENB

ED0

ED1

ED2

PS

EXT

TEST2

HD

VD

CL

Pin No.

4

5

6

12

13

14

15

16

52

54

D1

D2

D3

PRESET

Low

Low

Low

High

High

High

High

High

Low

Low

H4

H3

H2

H1

AV

DD

—3—

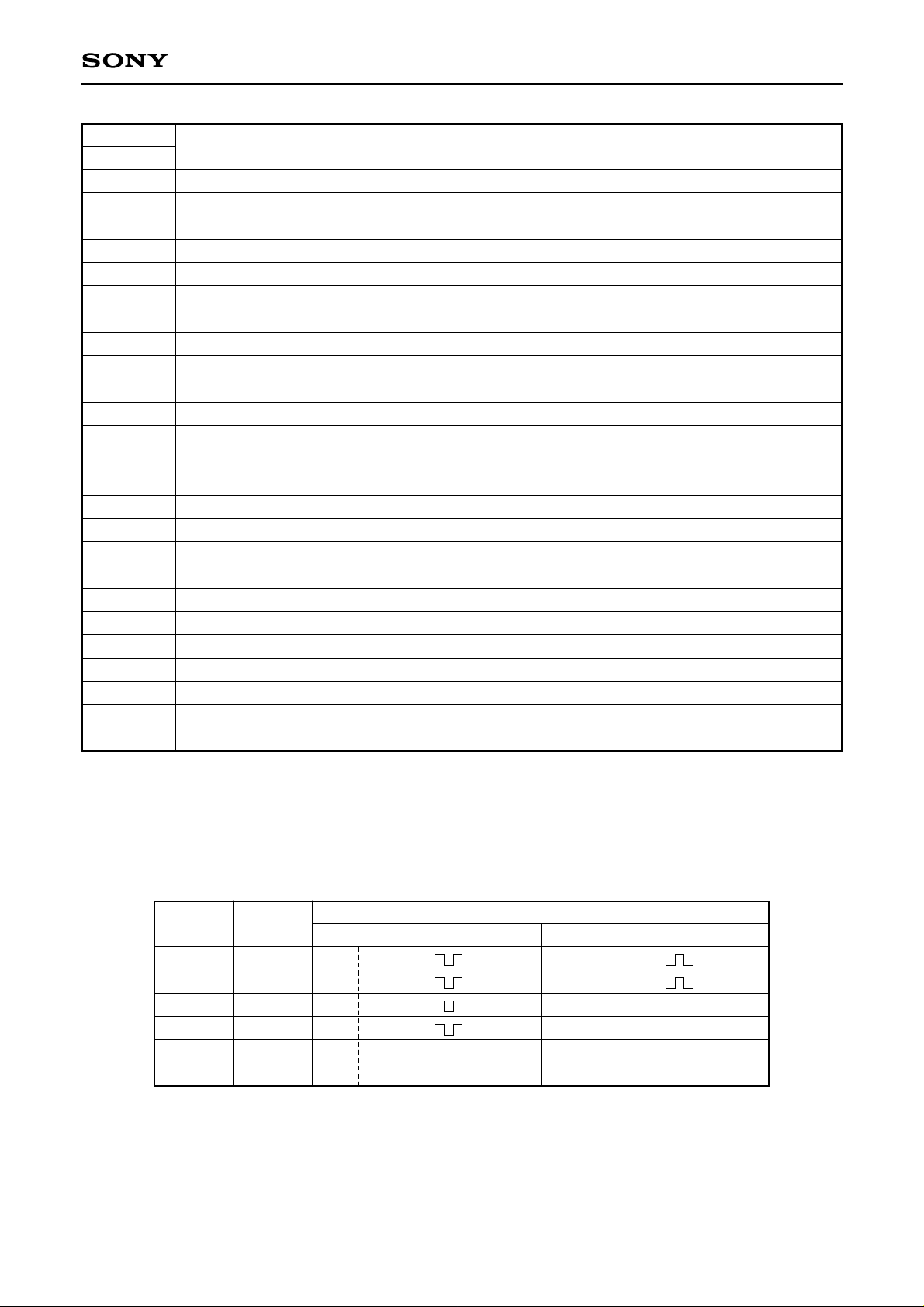

Pin Configuration (2)

CXD1254AR/AQ

HTSG

V

EXT

V

TEST2

NC

V

NC

TEST3

V

NC

NC

DD

SS

DD

SS

52

53

54

55

56

57

58

59

60

61

62

63

FLD

TEST1

DD

V

PBLK

CLP4

CLP3

ID

CLP2

SS

V

CLP1

CXD1254AQ

BFG

XDL2

XDL1

XSP2

XSP1

XSHD

XSHP

SS

V

XV4

33343536373839404142434445464748495051

32

XSG2

31

XV3

30

XSG1

29

XV1

28

XV2

27

XSUB

26

DD

V

25

RG

24

SS

AV

23

H4

22

H3

21

H2

BF

64

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19

CBLK

SYNC

Mode

D1

D2

D3

ENB

ED0

ED1

ED2

PS

EXT

TEST2

HD

VD

CL

Pin No.

6

7

8

14

15

16

17

18

54

56

D1

D2

D3

PRESET

Low

Low

Low

High

High

High

High

High

Low

Low

TRIG

SS

V

OSCI

OSCO

CKIN

ENB

ED0

ED1

Low High

NTSC/EIA CCIR

Normal Image Mirror Image

Color B/W

Normal Shutter

Shutter Speed

Serial input Parallel input

Internal External

Normally Low

ED2

PS

DD

AV

20

H1

—4—

Pin Description

CXD1254AR/AQ

Pin No.

LQFP QFP

13

24

35

46

57

68

79

810

911

10 12

11 13

12 14

13 15

14 16

15 17

16 18

17 19

18 20

19 21

20 22

21 23

22 24

23 25

24 26

25 27

26 28

27 29

28 30

29 31

30 32

31 33

32 34

33 35

34 36

35 37

36 38

37 39

38 40

39 41

40 42

Pin

HD

VD

CL

D1

D2

D3

TRIG

VSS

OSCI

OSCO

CKIN

ENB

ED0

ED1

ED2

PS

AVDD

H1

H2

H3

H4

AVSS

RG

VDD

XSUB

XV2

XV1

XSG1

XV3

XSG2

XV4

VSS

XSHP

XSHD

XSP1

XSP2

XDL1

XDL2

BFG

VSS

I/O

O

Horizontal drive pulse output

O

Vertical drive pulse output

O

Clock output NTSC/EIA: 14.318 MHz CCIR: 14.1875 MHz

I

Mode selection “Low”: NTSC/EIA “High”: CCIR (Pull-down resistor)

I

Mode selection “Low”: Normal “High”: Mirror (Pull-down resistor)

I

Mode selection “Low”: Color “High”: B/W (Pull-down resistor)

I

Shutter speed setting pulse input (Pull-up resistor)

—

GND for signal generator

I

Oscillator input NTSC/EIA: 28.636 MHz CCIR: 28.375 MHz

O

Oscillator output

I

Input for determining oscillator duty cycle

I

Shutter selection “Low”: Normal “High”: Shutter (Pull-up resistor)

I

Shutter speed control (Pull-up resistor)

I

Shutter speed control (Pull-up resistor)

I

Shutter speed control (Pull-up resistor)

Shutter speed setting data format selection

I

—

Independent power supply for horizontal driver

O

Clock output for horizontal register driver

O

Clock output for horizontal register driver (Leave open except for ICX046.)

O

Clock output for horizontal register driver (Use as H2 except for ICX046.)

O

Clock output for horizontal register driver (Leave open except for ICX046.)

—

Independent GND for horizontal driver

O

Reset gate pulse output

—

Power supply for timing generator

O

Sensor charge sweep output pulse output

O

Clock output for vertical register driver

O

Clock output for vertical register driver

O

Sensor charge readout pulse output

O

Clock output for vertical register driver

O

Sensor charge readout pulse output

O

Clock output for vertical register driver

O

GND for timing generator

Pre-charge level/sample-and-hold pulse output

O

Data sample-and-hold pulse output

O

Color separation sample-and-hold pulse output

O

Color separation sample-and-hold pulse output

O

Pulse output for delay line

O

Pulse output for delay line

O

O

Burst flag gate pulse output

—

GND for timing generator

“Low”: Serial “High”: Parallel (Pull-up resistor)

Function

∗

1

∗

1

∗

1

∗

1

∗

1

∗

1

—5—

CXD1254AR/AQ

Pin No.

LQFP QFP

41 43

42 44

43 45

44 46

45 47

46 48

47 49

48 50

49 51

50 52

51 53

52 54

53 55

54 56

55 57

56 58

57 59

58 60

59 61

60 62

61 63

62 64

63 1

64 2

Pin

CLP1

CLP2

CLP3

CLP4

PBLK

ID

VDD

TEST1

FLD

HTSG

VDD

EXT

VSS

TEST2

NC

VDD

NC

TEST3

VSS

NC

NC

BF

CBLK

SYNC

I/O

O

Pulse output for clamp

O

Pulse output for clamp

O

Pulse output for clamp

O

Pulse output for clamp

O

Blanking/cleaning pulse output

O

Line discrimination pulse output

—

Power supply for timing generator

I

Test input/H reset pulse input

I/O

Field pulse output/V reset pulse input

I

XSG1, 2 controller/Test input

—

Power supply for signal generator

Synchronization mode selection.

I

—

GND for signal generator

I

Test input (Normally open) (Pull-down resistor)

—

Used open

—

Power supply for signal generator

—

Used open

I

Test input (Normally fixed at “Low”)

—

GND for signal generator

—

Used open

—

Used open

O

Burst flag pulse output

O

Composite blanking pulse output

O

Composite synchronization pulse output

(Note)∗1…Output determined by mode setting.

∗

2…Function determined by mode setting.

Function

∗

∗

∗

“Low”: Internal “High”: External (Pull-down resistor)

2

2

2

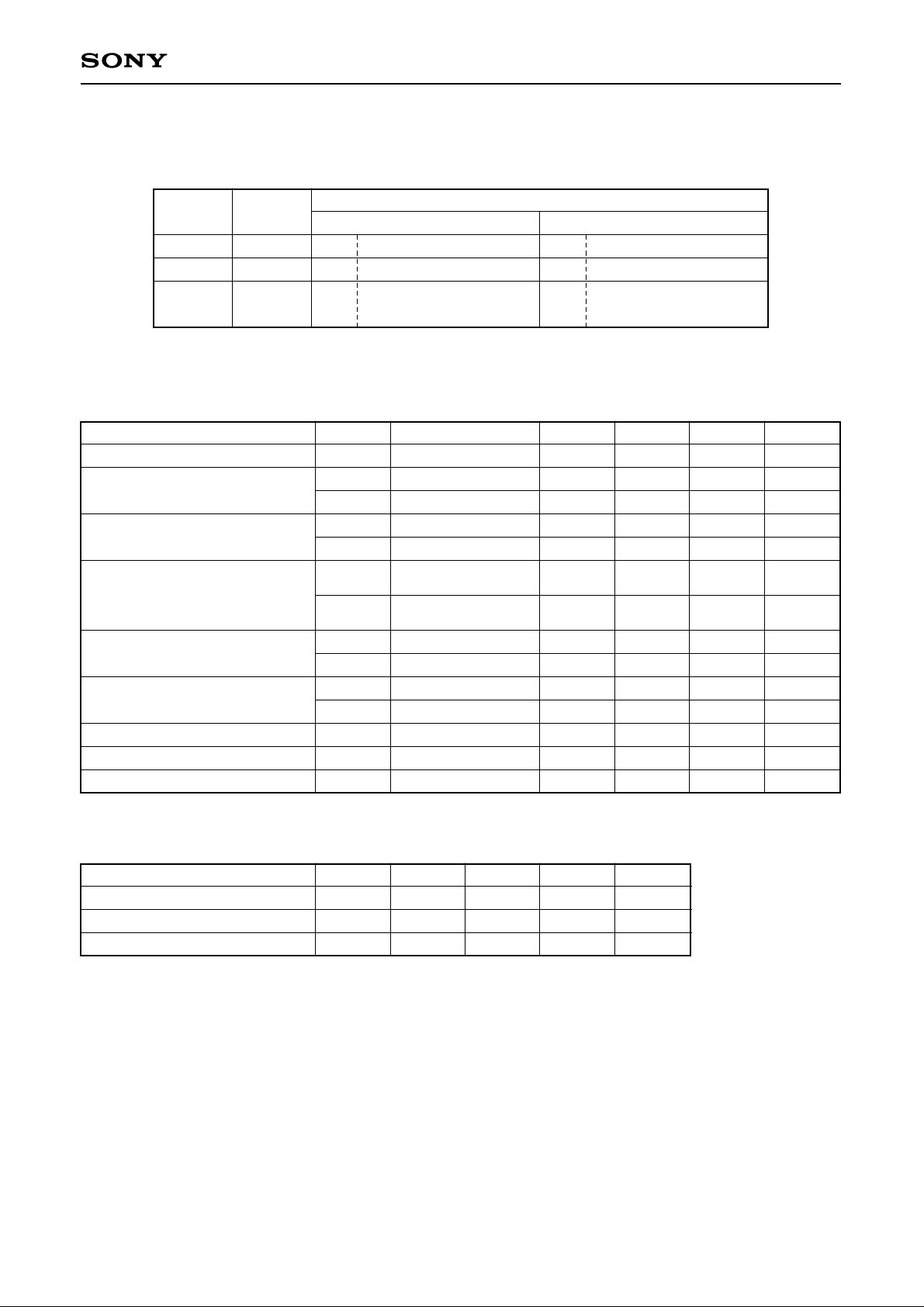

Outputs for Pins Determined by Mode Setting

∗

1

Pin

XSHP

XSHD

XSP1

XSP2

XDL1

XDL2

Pin No.

(LQFP)

33

34

35

36

37

38

Low (Color) High (B/W)

O

O

O

O

XSHP ( ) output

XSHD ( ) output

XSP1 ( ) output

XSP2 ( ) output

O

O

XDL1 output

XDL2 output

—6—

D3 (Pin 6)

O

O

O

O

O

O

SHP ( ) output

SHD ( ) output

(Out put stopped)

(Out put stopped)

(Out put stopped)

(Out put stopped)

CXD1254AR/AQ

Functions for Pins Determined by Mode Settings

∗

2

Pin

TEST1

FLD

HTSG

Pin No.

(LQFP)

48

49

50

Low (Internal) High (External)

Test input (Normally low)

I

O

I

(“Low” : OFF “High” : ON)

FLD output

XSG1, 2 control input

EXT (Pin 11)

I

I

I

H reset pulse input

V reset pulse input

Test input (Normally low)

Electrical Characteristics

1) DC Characteristics (VDD=5 V ±0.25 V, Topr= –20 to +75 °C)

Item

Supply voltage

Input voltage

Output voltage 1

Output voltage 2

Symbol

VDD

VIH1

VIL1

VOH1

VOL1

VOH2

Conditions

IOH=–2 mA

IOL=4 mA

IOH=–4 mA

Min.

4.75

0.7 VDD

VDD–0.5

VDD–0.5

Typ.

5.0

CL, RG, XSHP, XSHD, XSP1,

XSP2, XDL1, XDL2

Output voltage 3

H1, H2, H3, H4

Output voltage 4

OSC0

Feedback resistance

Pull-up resistor

Pull-down resistor

VOL2

VOH3

VOL3

VOH4

VOL4

RFB

RPU

RPD

IOL=8 mA

IOH=–8 mA

IOL=8 mA

IOH=–1 mA

IOL=1 mA

VIN=VSS or VDD

VIL=0 V

VIH=VDD

VDD–0.5

VDD/2

500 k

40 k

40 k

2 M

100 k

100 k

2) Input/Output Capacitance (VDD=VI=0 V, fM=1 MHz)

Item

Input pin capacitance

Output pin capacitance

Input/Output pin capacitance

Symbol

CIN

COUT

CI/O

Min. Typ. Max.

9

11

11

Unit

pF

pF

pF

Max.

5.25

0.3 VDD

0.4

0.4

0.4

VDD/2

5 M

250 k

250 k

Unit

V

V

V

V

V

V

V

V

V

V

V

Ω

Ω

Ω

—7—

Loading...

Loading...