Sony CXD1250N, CXD1250M Datasheet

CXD1250M/N

Vertical Clock Driver for CCD Image sensor

Description

CXD1250M/N is a clock driver developed for the

vertical register drive of CCD Image sensor.

Features

4-channel vertical clock driver and 1 channel

substrate driver are built-in.

Application

CCD camera

Structure

CMOS

Absolute Maximum Ratings (Ta = 25°C)

• Supply voltage VDD VL – 0.3 to VL + 35.0 V

VM VL – 0.3 to VL + 35.0 V

VH VL – 0.3 to VL + 35.0 V

VHH VL – 0.3 to VL + 35.0 V

• Input volltage VI VL – 0.3 to VDD + 0.3 V

• Output voltage MVφ (pins 13, 17) VL – 0.3 to VM + 0.3 V

• Output voltage HVφ (pins 14, 16) VL – 0.3 to VH + 0.3 V

• Output voltage HHVφ (pin 19) VL – 0.3 to VHH + 0.3 V

• Operating temperature Topr –25 to +85 °C

• Storage temperature Tstg –40 to +125 °C

CXD1250M

20 pin SOP (Plastic)

CXD1250N

20 pin SSOP (Plastic)

Recommended Operating Conditions

• Supply voltage VDD 5.0 ± 0.5 V

VM VL + 10.0 V

VH VL + 25.0 V

VHH VL + 30.0 V

VL –10.0 V

• Operating temperature Topr –20 to +75 °C

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

– 1 –

80639C43-PK

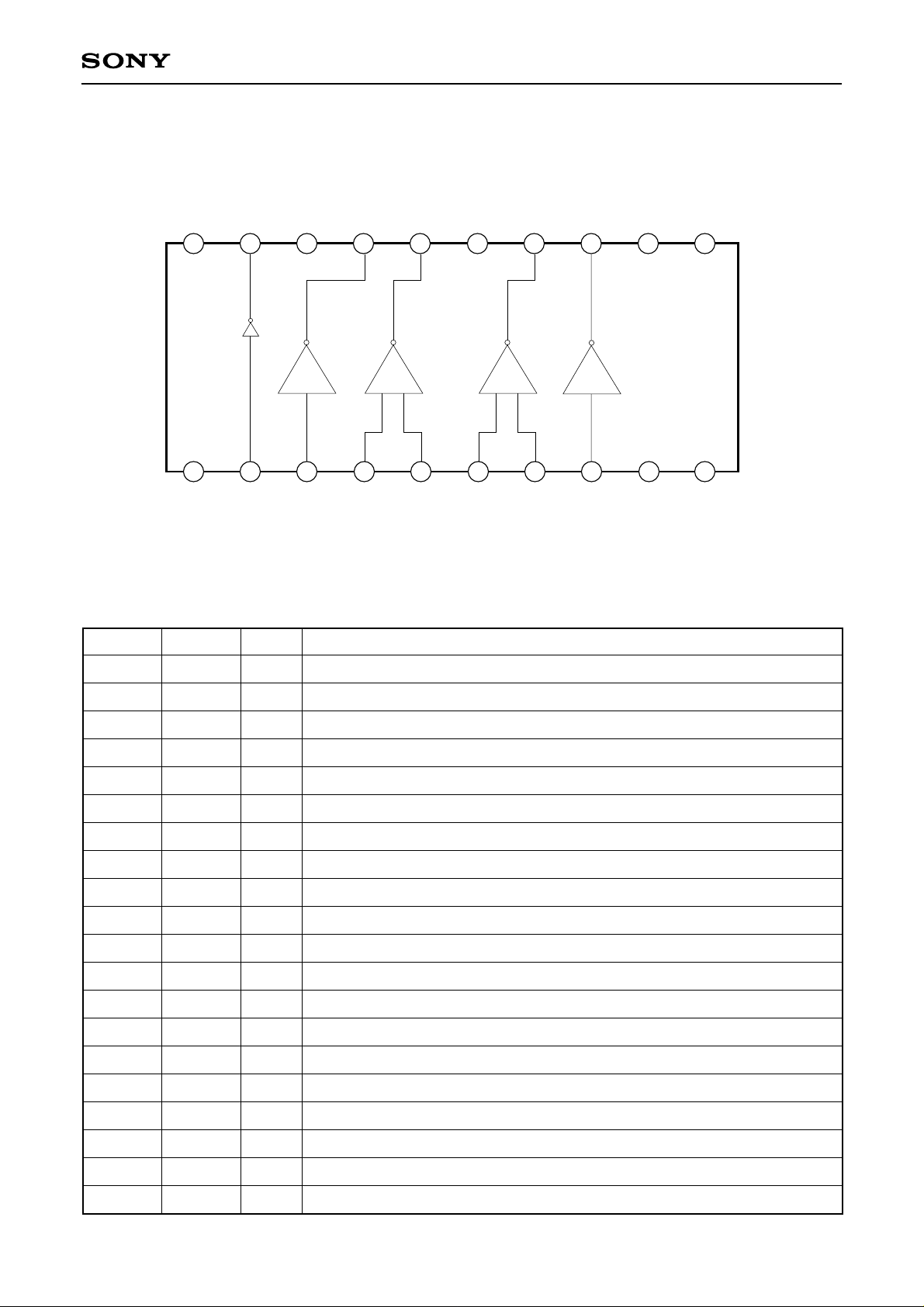

Block Diagram and Pin Configuration (Top View)

CXD1250M/N

Pin Description

No.

Symbol I/O Description

20

1

(20V)

HH

V

GND

19

Vsub

2

Xsub

(–10V)

L

V

18

3

XV2

17

4

Vφ2

XV1

16

5

Vφ1

XSG1

6

(0V)

M

V

XV3

1415

7

Vφ3

XSG2

13

8

Vφ4

XV4

12

9

(15V)

H

V

(5V)

DD

V

N.C

11

10

N.C

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

GND

Xsub

XV2

XV1

XSG1

XV3

XSG2

XV4

VDD

NC

NC

VH

Vφ4

Vφ3

VM

Vφ1

Vφ2

—

—

—

—

—

O

O

—

O

O

GND

I

Output control (Vsub)

I

Output control (Vφ2)

I

Output control (Vφ1)

I

Output control (Vφ1)

I

Output control (Vφ3)

I

Output control (Vφ3)

I

Output control (Vφ4)

Power supply (5V)

Power supply (15V)

Output (2 level : VM, VL)

Output (3 level : VH, VM, VL)

Power supply (0V)

Output (3 level : VH, VM, VL)

Output (2 level : VM, VL)

18

19

20

VL

Vsub

VHH

—

O

—

Power supply (–10V)

Output (2 level : VHH, VL)

Power supply (20V)

– 2 –

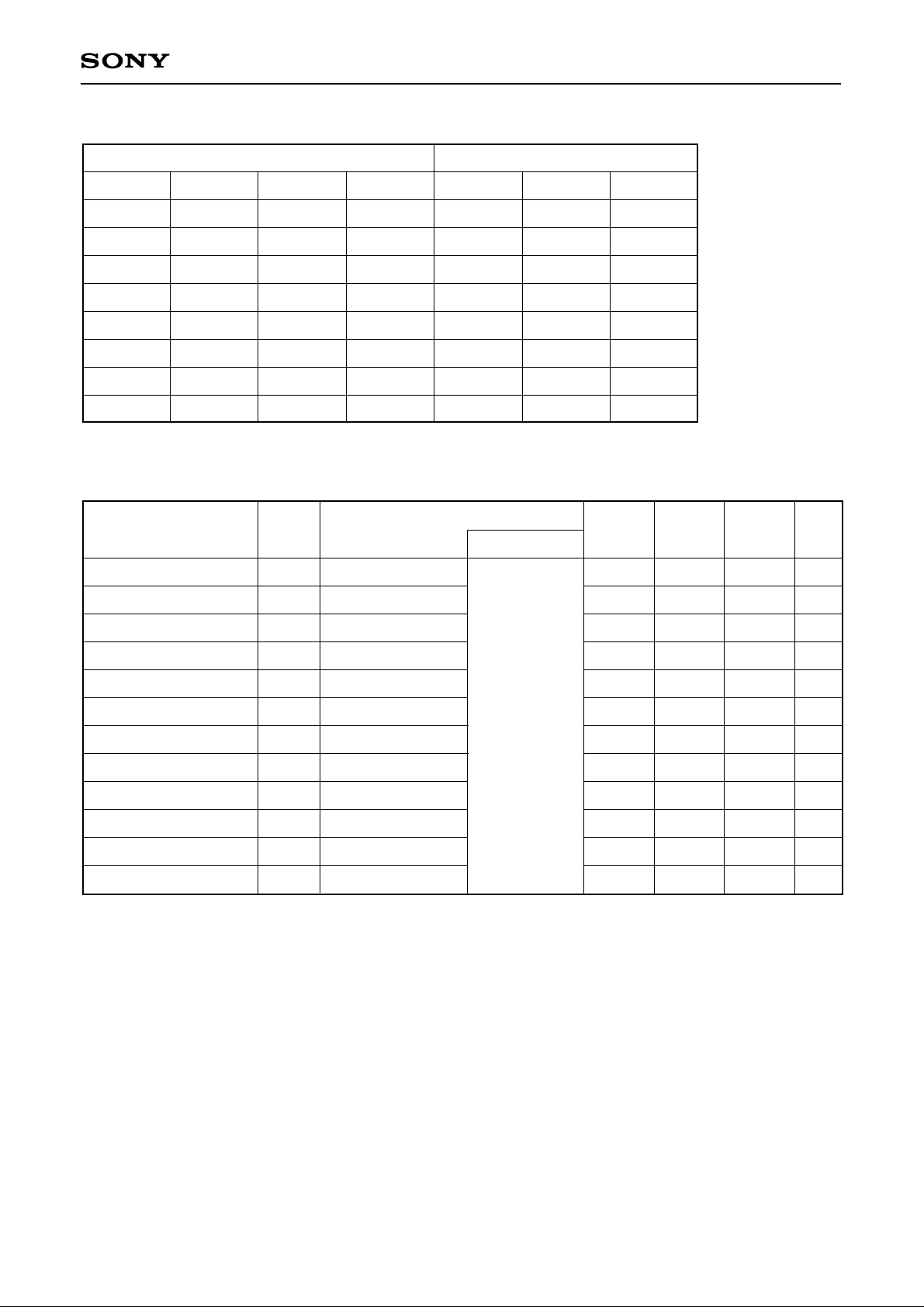

Truth Table

CXD1250M/N

Input

XV1 · 3

L

H

X

X

X

X

L

H

XSG1 · 2 XV2 · 4 Xsub

H

H

X

X

X

X

L

L

DC Characteristics (Ta = 25°C)

Item

"H" level input voltage

"L" level input voltage

Symbol Min. Typ. Max. Unit

VIH

VIL

Output

Vφ1 · 3 Vφ2 · 4

X

X

L

H

X

X

X

X

X

X

X

X

L

H

X

X

VM

VL

X

X

X

X

VH

Z

X

X

VM

VL

X

X

X

X

Vsub

X

X

X

X

VHH

VL

X

X

X : Don't care

Z : High impedance

Test condition

Power supply

3.5

—

—

—

—

1.5

V

V

"L" level output voltage

"M" level output voltage

"M" level output voltage

"H" level output voltage

"HH" level output voltage

Input current

Power supply current

Power supply current

Power supply current

Power supply current

∗

Suuply current at operation (See the Test Circuit)

VφL

VφM

VφM

VφH

VφHH

IφL = 20µA

IφM = –20µA

IφM = 20µA

IφH = –20µA

IφHH = –20µA

Ii

∗

IM

∗

IDD

∗

IH

∗

IHH

VDD = 5V

VL = –10V

VM = 0V

VH = 15V

VHH = 20V

—

—

–0.1

14.9

19.9

—

—

—

—

—

–10

0.0

0.0

15

20

1.0

4.5

0.3

0.1

0.05

–9.9

0.1

—

—

—

—

5.0

0.5

0.2

0.1

V

V

V

V

V

µA

mA

mA

mA

mA

– 3 –

Loading...

Loading...