Sony CXD1196AR Datasheet

—1—

E92128B78-TE

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

Absolute Maximum Ratings (Ta=25 °C)

• Supply voltage VDD VSS –0.5 to +7.0 V

• Input voltage VI VSS –0.5 to VDD +0.5 V

• Output voltage VO VSS –0.5 to VDD +0.5 V

• Operating temperature

Topr –20 to +75 °C

• Storage temperature

Tstg –55 to +150 °C

Recommended Operating Conditions

• Supply voltage

VDD +3.5 to +5.5 (+5.0 Typ.) V

• Operating temperature

Topr –20 to +75 °C

Description

The CXD1196AR is a CD-ROM decoder LSI with a

built-in ADPCM decoder.

Features

• CD-ROM, CD-I and CD-ROM XA format

compatible

• Real time error correction

• Double speed playback compatible

(when VDD=5.0±10 %)

• Can be connected to a standard SRAM up to 32

Kbytes (256 Kbits).

• All audio output sampling frequency : 132.3 kHz

(Built-in oversampling filter)

• Built-in de-emphasis digital filter

• Capable of VDD 3.5 V operation

Applications

CD-ROM drive

Structure

Silicon gate CMOS IC

CD-ROM DECODER

80 pin LQFP (Plastic)

CXD1196AR

For the availability of this product, please contact the sales office.

—2—

CXD1196AR

Block Diagram

5-11.13-20

MAO-MA14

3

34

36

37

38

59

55 54 57 35

50

48

47

46

45

53

51

44

67

68

66

65

64

78

4

24-31

DMA

SEQUENCER

ADDRESS GEN

COP I/F

DESCRAMBLER

SYNC CONTROL

GALOIS FIELD

SYNDROME GEN

ECC

CORRECTOR

PRIORITY

RESOLVER

CLOCK GEN

DIGITAL

FILTER

DAC

I/F

ADPCM

DECODER

CPU DMA

CPU I/F

DMA FIFO

XMOE XMWR MDBO-MDB7

C2PO

BCLK

DATA

LRCK

XRST

XTL1 XTL2 CLK

WCKO

LRCO

DATO

BCKO

MUTE

69

DO-D7

XRD

XWR

XCS

AO

INT

INTP

DRO

XDAC

2.12.23.32.42.52.63.72

GND

33.73

V

DD

EMP

—3—

CXD1196AR

Pin Description

No. Symbol I/O Description

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

TD7

GND

XMOE

XMWR

MA0

MA1

MA2

MA3

MA4

MA5

MA6

GND

MA7

MA8

MA9

MA10

MA11

MA12

MA13

MA14

TD6

TD5

GND

MDB0

MDB1

MDB2

MDB3

MDB4

MDB5

MDB6

MDB7

GND

VDD

C2PO

EMP

BCLK

DATA

LRCK

TD4

TD3

I/O

—

O

O

O

O

O

O

O

O

O

—

O

O

O

O

O

O

O

O

I/O

I/O

—

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

—

—

I

I

I

I

I

I/O

I/O

Test pin

Ground pin

Buffer memory output enable negative logic signal

Buffer memory write enable negative logic signal

Buffer memory address (LSB)

Buffer memory address

Buffer memory address

Buffer memory address

Buffer memory address

Buffer memory address

Buffer memory address

Ground pin

Buffer memory address

Buffer memory address

Buffer memory address

Buffer memory address

Buffer memory address

Buffer memory address

Buffer memory address

Buffer memory address (MSB)

Test pin

Test pin

Ground pin

Buffer memory data bus (LSB)

Buffer memory data bus

Buffer memory data bus

Buffer memory data bus

Buffer memory data bus

Buffer memory data bus

Buffer memory data bus

Buffer memory data bus (MSB)

Ground pin

Power supply pin

C2 pointer positive logic signal from CD player

Emphasis positive logic signal from CD player

Bit clock signal from CD player

Data signal from CD player

LR clock signal from CD player

Test pin

Test pin

—4—

CXD1196AR

No. Symbol I/O Description

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

TD2

GND

TD1

INTP

WCKO

LRCO

DATO

BCKO

N. C

MUTE

DRQ

GND

XDAC

XTL2

XTL1

TD0

CLK

TDIO

XRST

TA3

TA2

TA1

GND

XRD

XWR

XCS

INT

A0

D7

D6

D5

GND

VDD

D4

D3

D2

D1

D0

TA0

N. C

I/O

—

I/O

I

O

O

O

O

—

O

O

—

I

O

I

I/O

O

I

I

I

I

I

—

I

I

I

O

I

I

I

I

—

—

I

I

I

I

I

I

—

Test pin

Ground pin

Test pin

INT pin polarity control signal

Word clock signal to DA converter

LR clock signal to DA converter

Data signal to DA converter

Bit clock signal to DA converter

Mute positive logic signal

DMA request positive logic signal

Ground pin

Acknowledge negative logic signal for DRQ

Crystal oscillator circuit output pin

Crystal oscillator circuit input pin

Test pin

Clock with 1/2 frequency of XTL1

Test pin

Chip reset negative logic signal

Test pin

Test pin

Test pin

Ground pin

CPU register read strobe negative logic signal

CPU register write strobe negative logic signal

Chip select negative logic signal from CPU

Interrupt request signal to CPU

CPU address signal

CPU data bus (MSB)

CPU data bus

CPU data bus

Ground pin

Power supply pin

CPU data bus

CPU data bus

CPU data bus

CPU data bus

CPU data bus (LSB)

Test pin

—5—

CXD1196AR

Electrical Characteristics

DC characteristics (VDD=5 V±10 %, VSS=0 V, Topr=–20 to 75 °C)

Item

TTL input level pin (∗1)

input voltage H level

TTL input level pin (∗1)

input voltage L level

CMOS input level pin (∗2)

input voltage H level

CMOS input level pin (∗2)

input voltage L level

TTL schmitt input level pin (∗3)

input voltage H level

TTL schmitt input level pin (∗3)

input voltage L level

TTL schmitt input level pin (∗3)

input voltage hysteresis

CMOS schmitt input level pin (∗4)

input voltage H level

CMOS schmitt input level pin (∗4)

input voltage L level

CMOS schmitt input level pin (∗4)

input voltage hysteresis

Pull-up resistor provided input pin

(∗5) input current

Pull-down resistor provided input pin

(∗6) input current

Pull-up resistor provided bidirectional

pin (∗7) input current

Output voltage H level (∗8)

Output voltage L level (∗8)

Input leak current (∗9)

Oscillation cell (∗10) input voltage

H level

Oscillation cell input voltage L level

Oscillation cell logic threshold value

Oscillation cell feedback

resistance value

Oscillation cell output voltage H level

Oscillation cell output voltage L level

Symbol

VIH1

VIL1

VIH2

VIL2

VIH3

VIL3

VIH3

–VIL3

VIH4

VIL4

VIH4

–VIL4

IIL1

IIL2

IIL3

VOH1

VOL1

IIL2

VIH4

VIL4

LVTH

RFB

VOH2

VOL2

Conditions

VIN=0 V

VIN=0 V

VIN=0 V

VOH=–2 mA

IOL=4 mA

VIN=VSS or VDD

IOH=–3 mA

IOL=3 mA

Min. Typ. Max. Unit

2.2 V

0.8 V

0.7 VDD V

0.3 VDD V

2.2 V

0.8 V

0.4 V

0.8 VDD V

0.2 VDD V

0.6 V

–40 –100 –240 µA

40 100 240 µA

–90 –200 –440 µA

VDD–0.8 V

0.4 V

–40 40 µA

0.7 VDD V

0.3 VDD V

0.5 VDD V

500 K 1 M 2 M Ω

0.5 VDD V

0.5 VDD V

—6—

CXD1196AR

DC characteristics (VDD=3.5 V, VSS=0 V, Topr=–20 to 75 °C)

Item

TTL input level pin (∗1)

input voltage H level

TTL input level pin (∗1)

input voltage L level

CMOS input level pin (∗2)

input voltage H level

CMOS input level pin (∗2)

input voltage L level

TTL schmitt input level pin (∗3)

input voltage H level

TTL schmitt input level pin (∗3)

input voltage L level

TTL schmitt input level pin (∗3)

input voltage hysteresis

CMOS schmitt input level pin (∗4)

input voltage H level

CMOS schmitt input level pin (∗4)

input voltage L level

CMOS schmitt input level pin (∗4)

input voltage hysteresis

Pull-up resistor provided input pin

(∗5) input current

Pull-down resistor provided input pin

(∗6) input current

Pull-up resistor provided bidirectional

pin (∗7) input current

Output voltage H level (∗8)

Output voltage L level (∗8)

Input leak current (∗9)

Oscillation cell (∗10) input voltage

H level

Oscillation cell input voltage L level

Oscillation cell threshold value

Oscillation cell feedback

resistance value

Oscillation cell output voltage H level

Oscillation cell output voltage L level

Symbol

VIH1

VIL1

VIH2

VIL2

VIH3

VIL3

VIH3

–VIL3

VIH4

VIL4

VIH4

–VIL4

IIL1

IIL2

IIL3

VOH1

VOL1

IIL2

VIH4

VIL4

LVTH

RFB

VOH2

VOL2

Conditions

VIN=0 V

VIN=0 V

VIN=0 V

VOH=–1.6 mA

IOL=3.2 mA

VIN=VSS or VDD

IOH=–1.3 mA

IOL=1.3 mA

Min. Typ. Max. Unit

2.2 V

0.6 V

0.7 VDD V

0.3 VDD V

2.2 V

0.6 V

0.3 V

0.8 VDD V

0.2 VDD V

0.5 V

–10 –25 –60 µA

10 25 60 µA

–20 –50 –110 µA

VDD–0.8 V

0.4 V

–40 40 µA

0.7 VDD V

0.3 VDD V

0.5 VDD V

1.2 K 2.5 M 5 M Ω

0.5 VDD V

0.5 VDD V

—7—

CXD1196AR

∗

1. D7 to 0, MDB7 to 0, TD7 to 0

∗

2. DATA, LRCK, C2PO, EMP, INTP, TDIO, TA3 to 0

∗

3. XWR, XRD, XCS, A0, XDAC

∗

4. BCLK, XRST

∗

5. XDAC, TA3 to 0

∗

6. C2PO, INTP

∗

7. D7 to 0, MDB7 to 0, TD7 to 0

∗

8. All output pins except XTL2

∗

9. All input pins except ∗7

∗

10. input : XTL1, output : XTL2

Input/Output Capacitance (VDD=VI=0 V, f=1 MHz)

Item

Input pin

Output pin

Input/Output pin

Symbol

CIN

COUT

COUT

Min. Typ. Max.

9

11

11

Unit

pF

pF

pF

—8—

CXD1196AR

AC Characteristics (VDD=5 V±10 %, VSS=0 V, Topr=–20 to 75 °C, Output load=50 pF)

The values in parentheses in the table are those obtained when VDD=3.5 V, VSS=0 V, Topr=–20 to 75 °C, and

output load=50 pF.

Values without parentheses are common to VDD=5 V±10 % and 3.5 V.

1. CPU interface

(1) Read

(2) Write

AO

XCS

XRD

D7-D0

Tsar Tdrd

Tfrd

Trrl

Thar

Item

Address setting time (with respect to XCS & XRD ↓)

Address holding time (with respect to XCS & XRD ↑)

Data delay time (with respect to XCS & XRD ↓)

Data float time (with respect to XCS & XRD ↑)

L level XRD pulse width

Symbol

Tsar

Thar

Tdrd

Tfrd

Trr1

Min.

30 (70)

20 (50)

0

150 (250)

Typ. Max.

120 (200)

20 (40)

Unit

ns

ns

ns

ns

ns

AO

XCS

XWR

D7-D0

Twwl Thaw

Tsaw

Tsdw

Thdw

Item

Address setting time (with respect to XCS & XWR ↓)

Address holding time (with respect to XCS & XWR ↑)

Data setting time (with respect to XCS & XWR ↓)

Data holding time (with respect to XCS & XWR ↑)

L level XWR pulse width

Symbol

Tsaw

Thaw

Tsdw

Thwd

Twwl

Min.

30 (70)

20 (50)

50 (70)

20 (30)

70 (100)

Typ. Max. Unit

ns

ns

ns

ns

ns

—9—

CXD1196AR

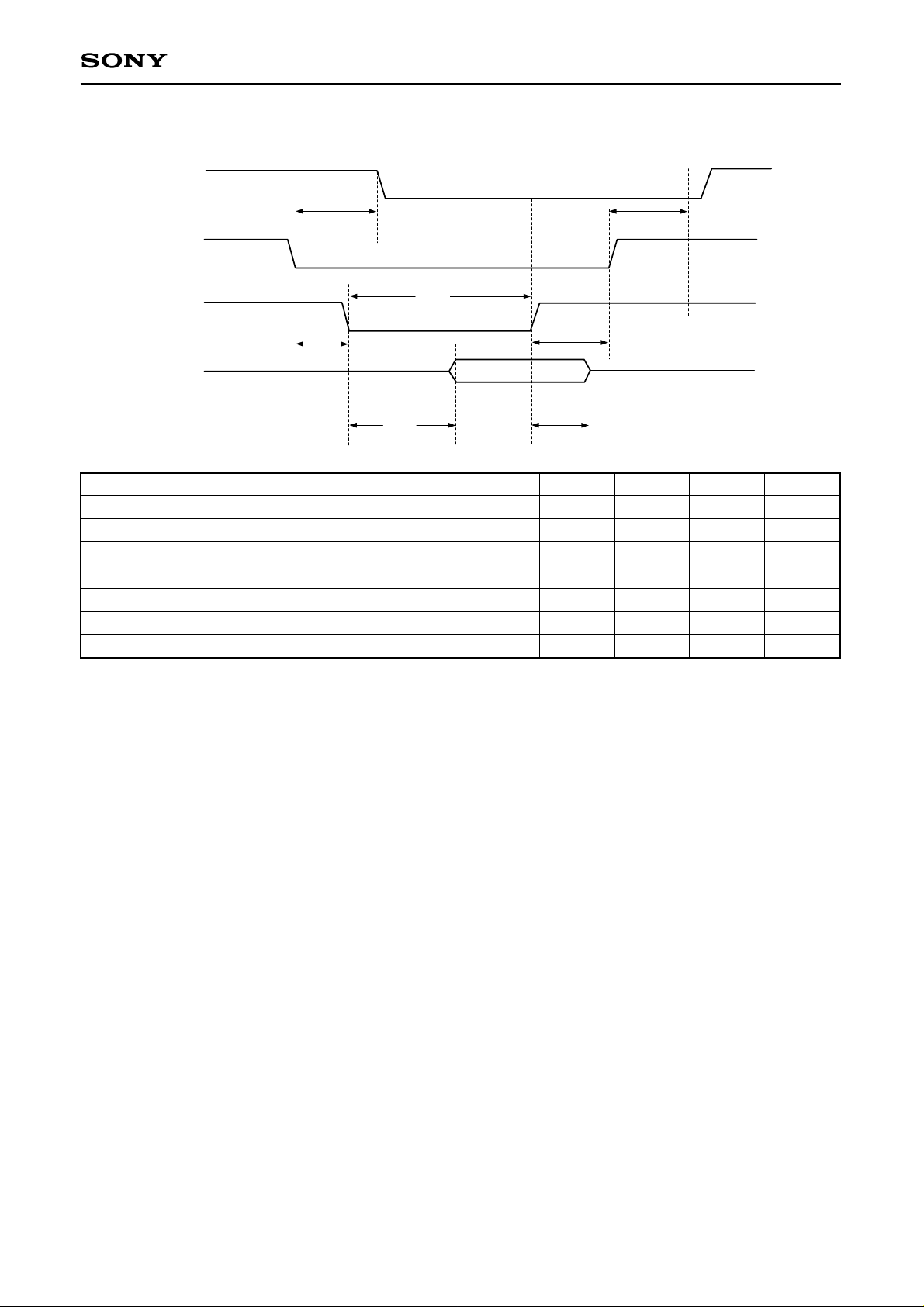

(3) DMA

Tdar1

Tsac

Tdrd

Trrl

Thac

Tdar2

Tfrd

DRQ

XDAC

XRD

D7-D0

Item

DRQ fall time (with respect to XDAC ↓)

DRQ rise time (with respect to XDAC ↑)

XDAC setting time (with respect to XRD ↓)

XDAC holding time (with respect to XRD ↑)

Data delay time (with respect to XRD ↓)

Data float time (with respect to XRD ↑)

L level XRD pulse width

Symbol

Tdar1

Tdar2

Tsac

Thac

Tdrd

Tfrd

Trrl

Min.

10 (30)

10 (30)

0

150 (250)

Typ. Max.

50 (120)

50 (120)

120 (200)

20 (40)

Unit

ns

ns

ns

ns

ns

ns

ns

Loading...

Loading...