Sony CXB1586AR Datasheet

—1—

E97319C83-TE

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

Absolute Maximum Ratings (Ta=25 °C)

• Supply voltage VCC –0.3 to 4 V

• Operating temperature Topr –55 to +70 °C

• Storage temperature Tstg –65 to +150 °C

• Allowable power dissipation

PD to 1109 mW

Operating Conditions

Supply voltage VCC 3.14 to 3.46 V

Description

The CXB1586AR is a transceiver IC with a built-in

PLL for Fibre Channel. For a receiver 1.0625

Gbaud serial data is received and output it as the

10-bit parallel data; for transmitter 1.0625 Gbaud 10bit parallel data is output as the serial data.

Features

• Transmitter and receiver in a single chip

• ANSI X3T11 Fibre Channel compatible (FC_0) at

1.0625 Gbaud

• Conforms to 10-bit interface specification

• TTL / ECL compatible

• Single +3.3 V power supply

• PLL for clock generation and clock / data recovery

• Byte sync detector (positive character of comma)

• Local loop back circuit

• Low power consumption (0.8 W typ.)

• 64-pin plastic LQFP package (10 mm × 10 mm)

Applications

1.0625 Gbaud Fibre channel

Structure

Bipolar silicon monolithic IC

10 Bit 1.0625 Gbaud Transceiver

64 pin LQFP (Plastic)

CXB1586AR

For the availability of this product, please contact the sales office.

—2—

CXB1586AR

Block Diagram

Pin Configuration (Top View)

TX0-9

D Q

10 10

Pin

P/S Conv.

Sout

LCKREF∗

LBEN

SDOUT∗

SDOUT

REFCLK

(106.25M)

TX_PLL

LCLK

(106.25M)

TCLK

(1.0625G)

REFCLK

LPF_TX0

LPF_TX1

RCLK (1.0625G)

RDATA

1/10

PX_PLL

S/P

Conv.

RX0-9

BYTSYNC

1/2

FCLK (106.25M)

RBC1

RBC0

SDIN∗

SDIN

LPF_RX0

LPF_RX1

BYTSYNCEN

1

0

10

56

LPF_RX1

VCCP_RX

VEEP_RX

SDIN∗

VCCE

SDIN

VCCG

VEEG

VCCG

VEEG

VCCG

VCCE

SDOUT∗

SDOUT

VCCE

VEEE

VEET

RBC0

RBC1

VCCT

VCCG

LCKREF∗

TEST∗

VEEG

BYTSYNCEN

VCCG

REFCLK

VEEG

VCCG

LBEN

VCCP_TX

LPF_TX1

LPF_RX0

BYTSYNC

VEET

RX0

RX1

RX2

VCCT

RX3

RX4

RX5

RX6

VCCT

RX7

RX8

RX9

VEET

VEET

TX0

TX1

TX2

VCCG

TX3

TX4

TX5

TX6

VCCG

TX7

TX8

TX9

VEET

VEEP_TX

LPF_TX0

49

48 40 33

32

17

24

1681

64

—3—

CXB1586AR

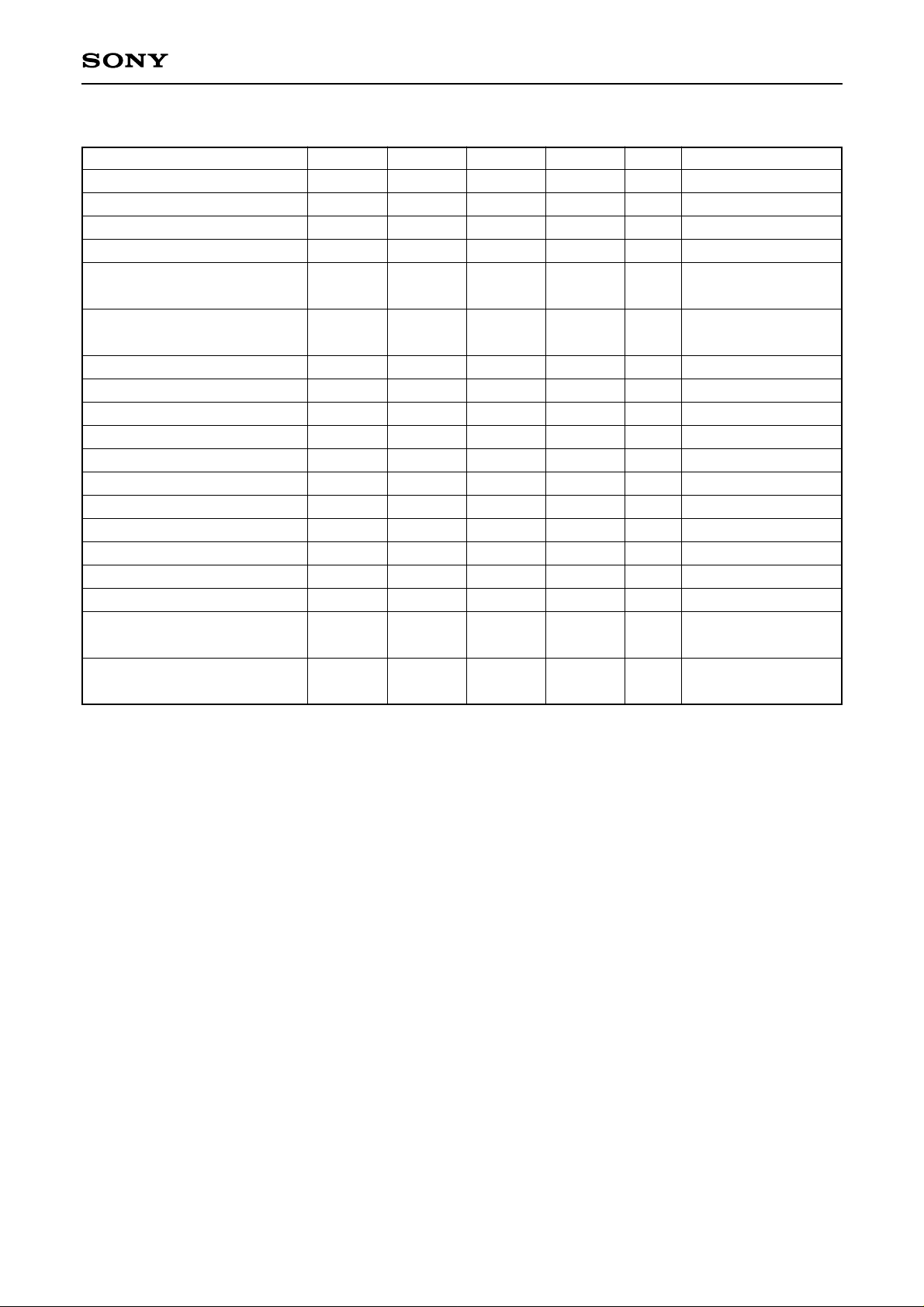

DC Characteristics (under the recommended conditions)

Symbol

VIH_T

VIL_T

IIH_T

IIL_T

VOH_T

VOL_T

VIH_E

VIL_E

VIS_E

1)

VOH_E

VOL_E

VOS_E

2)

ICC

PD

Item

TTL high level input voltage

TTL low level input voltage

TTL high level input current

TTL low level input current

TTL high level output voltage

TTL low level output voltage

ECL high level input voltage

ECL low level input voltage

ECL peak-to-peak differential

input voltage swing

ECL high level output voltage

ECL low level output voltage

ECL peak-to-peak differential

output voltage swing

Current consumption

Power dissipation

Min.

2

0

–400

2.2

VCC–1.17

VCC–1.81

400

VCC–1.05

VCC–1.81

1200

Typ.

250

825

Max.

5.5

0.8

20

0.5

VCC–0.88

VCC–1.48

2000

VCC–0.81

VCC–1.55

1900

320

1109

Unit

V

V

µA

µA

V

V

V

V

mV

V

V

mV

mA

mW

Conditions

Vin=VCC

Vin=0

IOH=–0.4 mA

IOL=2 mA

AC coupling input

50 Ω terminated

to VCC–2 V

50 Ω terminated

to VCC–2 V

Output pins open

Output pins open

Note :

1) ECL peak-to-peak differential input voltage swing

2) ECL peak-to-peak differential output voltage swing

Vi1

Voltage

VCC

VIH_E

VIL_E

VEE=GND

signal-in

+

signal-in

–

Vi2

1) VIS_E= |Vi1| + |Vi2|

Vo1

Voltage

VCC

VOH_E

VOL_E

VEE=GND

signal-out

+

signal-out

–

Vo2

2) VOS_E= |Vo1| + |Vo2|

—4—

CXB1586AR

AC Characteristics (under the recommended operating conditions)

Symbol

Tir_TX

Tif_TX

Tir_REF

Tif_REF

Tor_T

Tof_T

Tor_E

Tof_E

Tp_REF

DC_REF

Ftol_REF

Ts_TX

Th_TX

Ts_RX

Th_RX

Tsk_RBC

DC_RBC

DJ

RJ

JT

Item

TTL input rise time of TX

TTL input fall time of TX

TTL input rise time of REFCLK

TTL input fall time of REFCLK

TTL output rise time

TTL output fall time

ECL output rise time

ECL output fall time

REFCLK period

REFCLK duty cycle

REFCLK frequency tolerance

TX setup time to REFCLK

TX hold time to REFCLK

RX setup time to RBC

RX hold time to RBC

Skew between RBC0 and 1

RBC duty cycle

Deterministic jitter (p-p)

Random jitter (p-p)

Jitter tolerance

Min.

0.7

0.7

0.7

0.7

9.26

40

–100

2

1.5

3

1.5

Tp/2–0.5

40

Typ.

9.41

Tp/2

0.02

0.18

Max.

4.8

4.8

2.4

2.4

3.5

3.5

400

400

9.56

60

100

Tp/2+0.5

60

0.07

0.23

0.7

Unit

ns

ns

ns

ns

ns

ns

ps

ps

ns

%

ppm

ns

ns

ns

ns

ns

%

UI

UI

UI

Conditions

0.8 V to 2.0 V

2.0 V to 0.8V

0.8 V to 2.0 V

2.0 V to 0.8 V

0.8 V to 2.0 V,

CL=10 pF

2.0 V to 0.8 V,

CL=10 pF

20 % to 80 %, CL=2 pF

20 % to 80 %, CL=2 pF

Tp is period of RBC

in frequency lock

Serial data output

(k28.5)

Serial data output

Serial data input

—5—

CXB1586AR

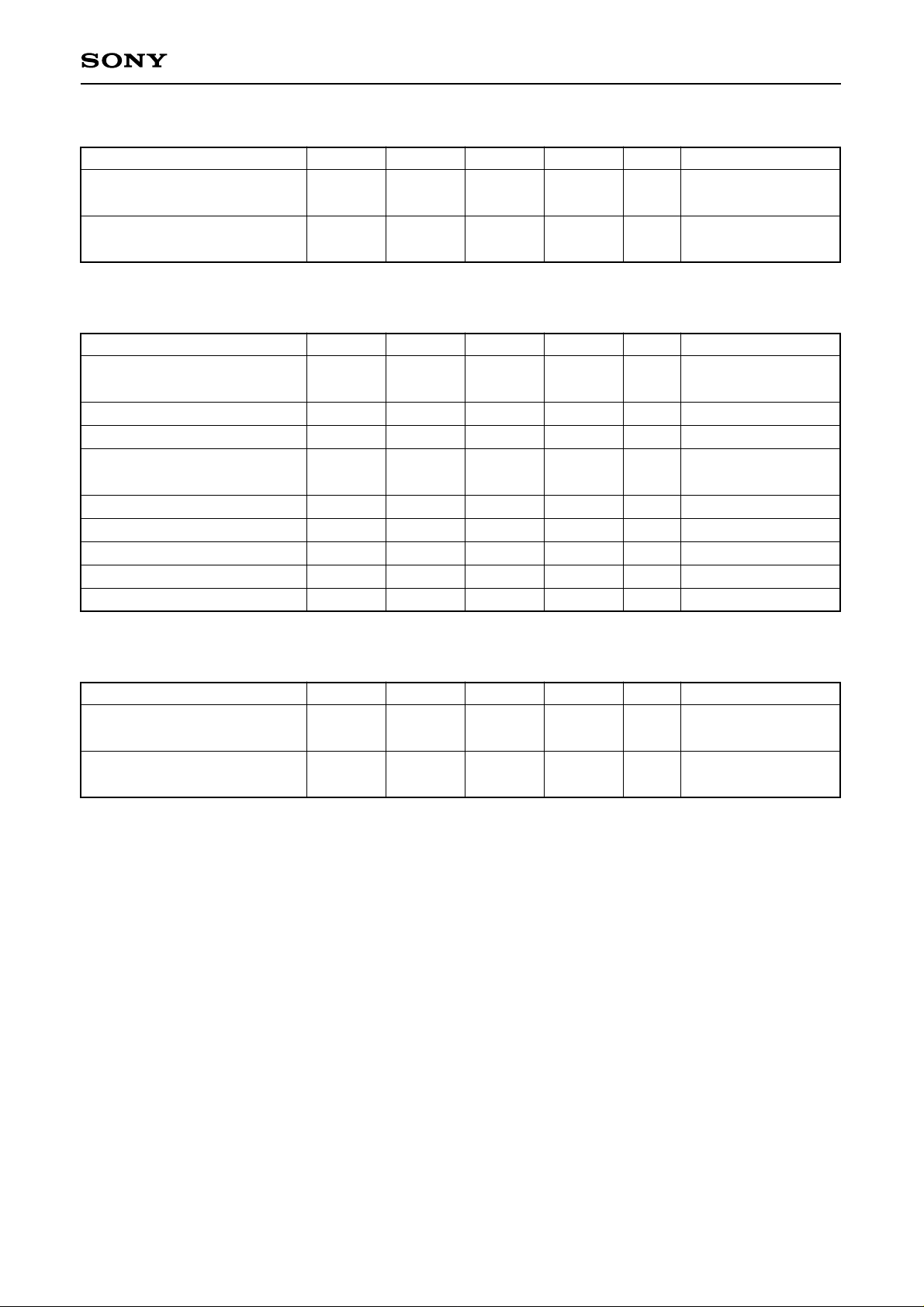

PLL AC Characteristics (under the recommended operating conditions)

Symbol

Tfa

Tbs

Item

Frequency acquisition time of

TX and RX PLL

Bit synchronization time of RX

PLL

Min. Typ. Max.

500

2500

Unit

µs

bit

Conditions

Loop damping

capacitor=0.01 µF

Recommended Operating Conditions

Symbol

VCC

Ta

Item

Supply voltage

(Including VCCT5)

Ambient temperature

Min.

3.135

0

Typ.

3.3

Max.

3.465

70

Unit

V

°C

Remarks

Absolute Maximum Ratings (VEEE, VEET, VEEG, VEEP=GND)

Symbol

VCC

VI_T

VI_E

VIS_E

IOH_T

IOL_T

IO_E

Ta

Tstg

Item

Power supply voltage

(Except VCCT5)

TTL DC input voltage

ECL DC input voltage

ECL peak-to-peak differential

input voltage swing

TTL output current (High level)

TTL output current (Low level)

ECL output current

Ambient temperature

Storage temperature

Min.

–0.3

–0.5

VCC–2

–4

–20

0

–30

–55

–65

Typ. Max.

4

5.5

VCC

4

0

20

0

70

150

Unit

V

V

V

V

mA

mA

mA

°C

°C

Remarks

Under bias

—6—

CXB1586AR

Pin description

Symbol

VEET

TX0-9

VCCG

VEEP_TX

LPF_TX0

LPF_TX1

VCCP_TX

LBEN

VEEG

REFCLK

BYTSYNCEN

TEST

∗

LCKREF

∗

VCCT

RBC1

RBC0

RX0-9

BYTSYNC

LPF_RX0

LPF_RX1

VCCP_RX

VEEP_RX

Pin No.

1, 14, 32,

33, 46

2-4, 6-9,

11-13

5, 10, 20,

23, 28, 55,

57, 59

15

16

17

18

19

21, 25,

56, 58

22

24

26

27

29, 37, 42

30

31

34-36,

38-41,

43-45

47

48

49

50

51

Type

PS

I_TTL

PS

PS

EX

PS

I_TTL

PS

I_TTL

I_TTL

I_TTL

I_TTL

PS

O_TTL

O_TTL

O_TTL

EX

PS

PS

Equivalent

circuit

—

(a)

—

—

(e)

—

(a)

—

(a)

(a)

(a)

(a)

—

(b)

(b)

(b)

(e)

—

—

Description

Ground for TTL output : Normally 0 V.

Parallel transmit data inputs to be serialized.

TX0 is serialized first and TX9 is last.

Power supply for internal logic gates :

Normally 3.3 V.

Ground for TX PLL : Normally 0 V.

Connect to external loop filter of TX PLL. Connect a

capacitor (0.01 µF) between LPF_TX0 and LPF_TX1.

Power supply for TX PLL : Normally 3.3 V.

Loop back enable : When high, TX serializer output

internally connects to RX deserializer input,

SDOUT/SDOUT∗is held low/high, and SDIN/SDIN∗is

disabled. When low, SDOUT/SDOUT∗and

SDIN/SDIN∗are enabled.

Power supply for internal logic gates :

Normally 0 V.

Reference clock for PLL and transmit byte clock

(106.25 MHz). Supplied by the host system.

Byte synchronization enable : When high, the positive

comma character (0011111) detection circuit is

enabled to establish byte synchronization (see Timing

Chart).

Test pin : Normally 3.3 V or open.

Lock to reference clock : An active low input.

LCKREF∗forces the PLL lock to the REFCLK supplied

by the host system.

Power supply for TTL output : Normally 3.3 V.

Receive byte clocks recovered from the serial data

(53.125 MHz). These clocks are 180 degrees out of

phase, and RX0-9 are alternatively clocked on the

rising edge of these clocks (see Timing Chart)

Parallel receive data output :

RX0 is received first and RX9 is last.

Byte synchronization indicator : High when a positive

comma character is detected (see Timing Chart)

Connect to external loop filter of RX PLL. Connect a

capacitor (0.01 µF) between LPF_RX0 and LPF_RX1.

Power supply for RX PLL : Normally 3.3 V.

Ground for RX PLL : Normally 0 V.

Loading...

Loading...