Sony CXB1454R Datasheet

VGA/SVGA/XGA 24bit Receiver

Description

CXB1454R is the 1 chip deserializer for VGA/SVGA/

XGA 24bit color digital RGB, and meet to the Gigabit

Video Interface specification.

Features

• 1 chip receiver for serial transmission of 24-bit color

VGA/SVGA/XGA picture

• On chip cable equalizer circuit to compensate the

cable loss

• On chip PLL circuit for data and clock recovery

• On chip panel mode automatically selectable circuit

• TTL compatible I/O

• Support 1 pixel/shiftclock mode with 1 chip and 2

pixel/shiftclock mode with 2 chips

• +3.3V single power supply

• Low power consumption

• 64pin plastic LQFP package with body size 14mm ×

14mm

Structure

Bipolar silicon monolithic IC

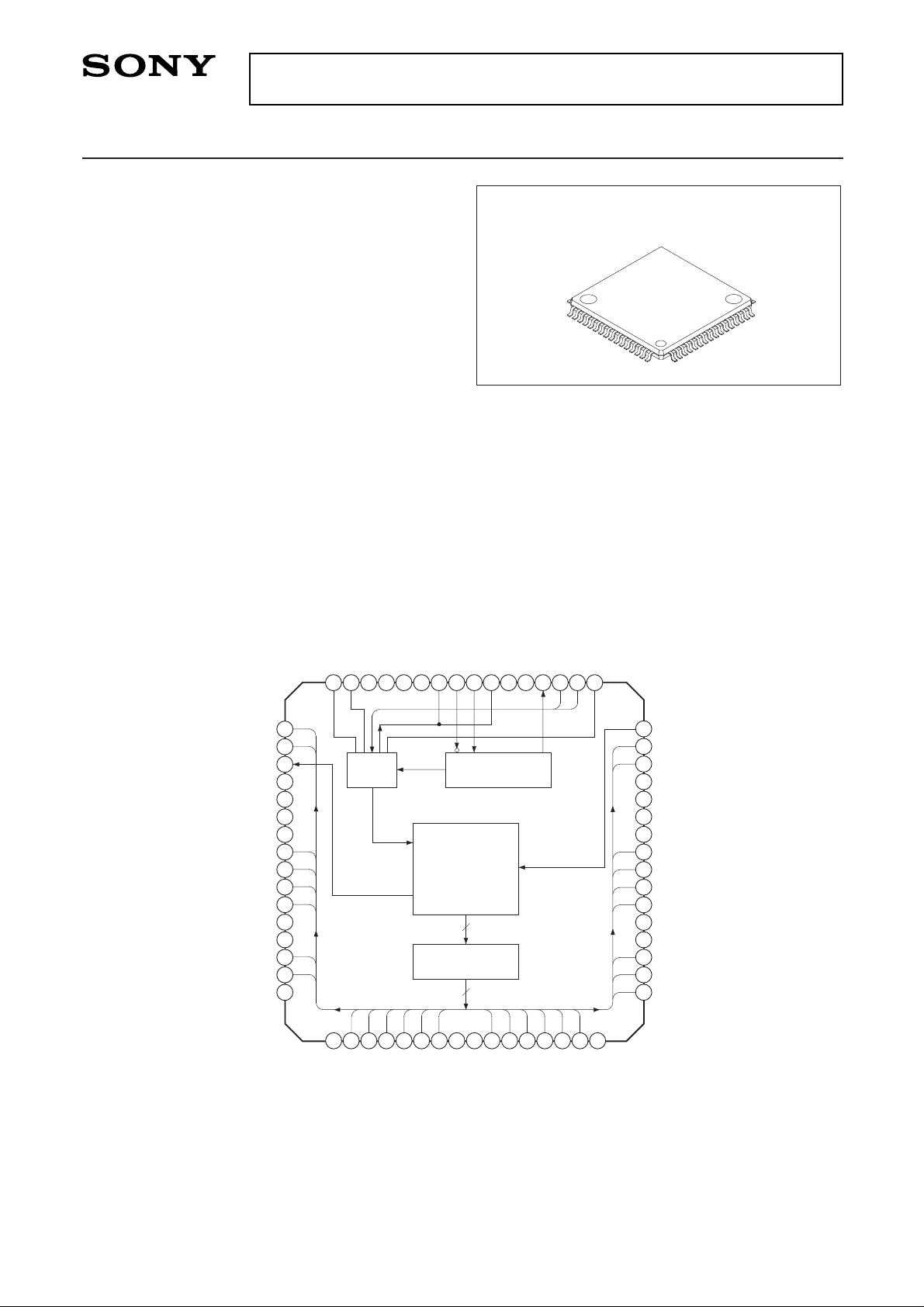

Block Digagram & Pin out

Absolute Maximum Ratings

• Supply voltage Vcc 4.0 V

• Storage temperature Tstg –65 to +150 °C

• Allowable power dissipation

PD 1710 mW

Recommended Operating Condition

• Supply voltage Vcc 3.3 ± 0.16 V

• Operating temperature Topr 0 to +60 °C

– 1 –

E98X24B03

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

CXB1454R

64 pin LQFP (Plastic)

10

11

1

Decoder

CDR

PLL

Serial

to

Parallel

Converter

12

13

14

15

16

2

3

4

5

6

7

8

9

63

64

61

62

40

39

38

37

36

35

34

33

48

41

42

43

44

45

46

47

Cable

EQ

60

59

58

57

56

55

54

53

52

51

50

49

21

30

31

32

22

23

24

25

26

27

28

29

17

18

19

20

CLKPOL

R0

R1

V

EET

VccT

V

EEG

VccG

R2

R3

R4

R5

V

EEG

V

CCG

R6

R7

V

EET

CNTL

DE

SFTCLK

V

EET

VccT

V

EEG

VccG

HSYNC

VSYNC

B7

B6

V

EEG

VccG

B5

B4

VccT

LPFB

LPFA

V

EE

S

V

EE

A

VccA

TESTEXN

REFRQN

SDATAN

SDATAP

REFRQP

TESTSB

TESTDT

LOS

PANEL1

PANEL0

REXT

V

EE

T

B3

B2

B1

B0

G7

G6

VccT

V

EE

T

G5

G4

G3

G2

G1

G0

VccT

Fig. 1. Block Diagram & Pin out

– 2 –

CXB1454R

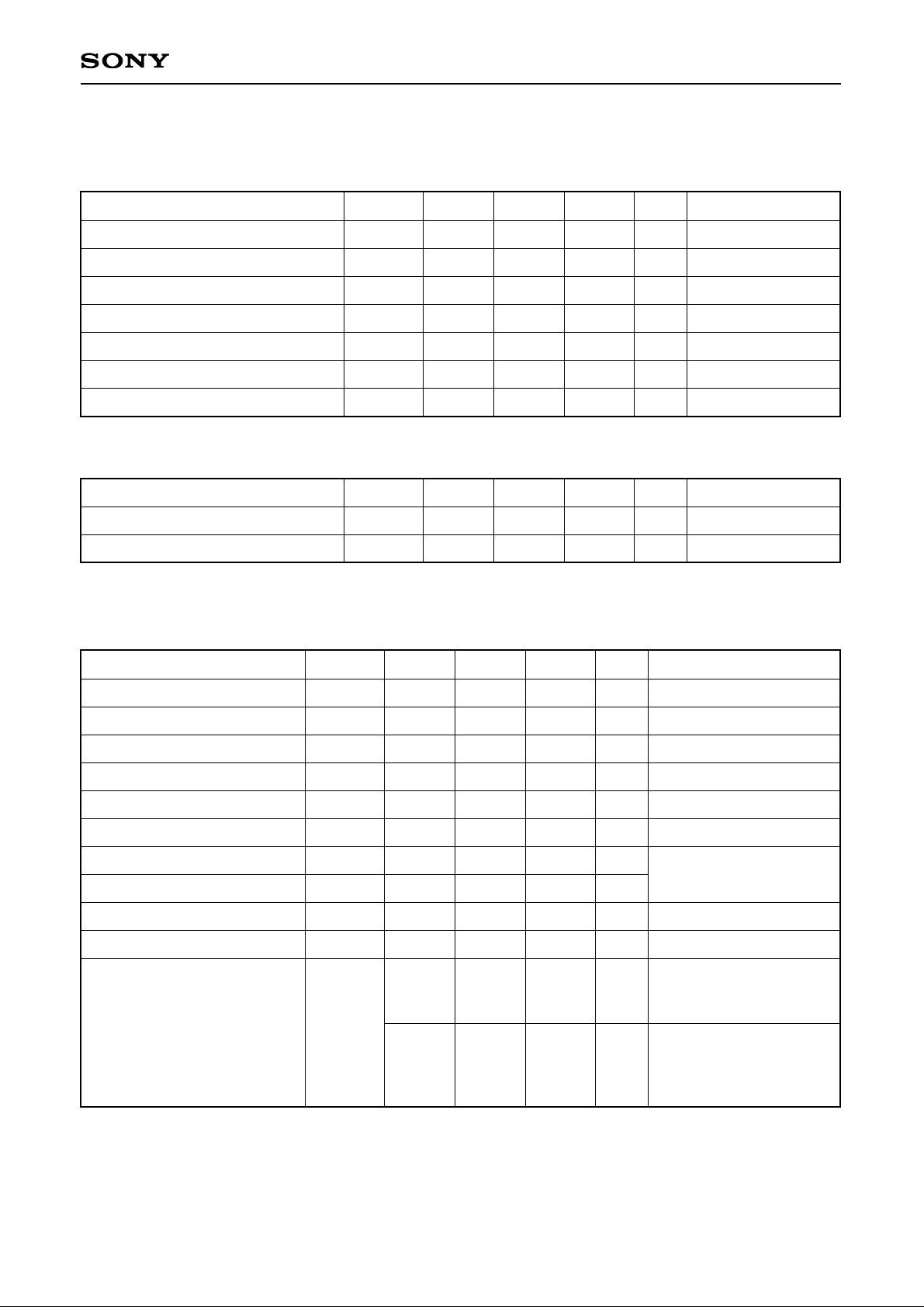

Pin List

Tab. 1. Power/Ground

Pin Name

VCCT

VEET

VCCG

VEEG

VCCA

VEEA

VEES

8, 16, 28, 53, 64

1, 9, 17, 29, 52

20, 26, 55, 61

21, 27, 54, 60

44

45

46

TTL power surpply, should be connected to 3.3V ± 5%

TTL ground, connected to 0V

Logical core power surpply, connected to 3.3V ± 5%

Logical core ground, connected to 0V

Analog power surpply, connected to 3.3V ± 5%

Analog ground, connected to 0V

Analog substrate, connected to 0V

Pin Number Descriptions

– 3 –

CXB1454R

Tab. 2. Digital Signals

Pin Name

SFTCLK

RED (7 to 0)

GRN (7 to 0)

BLU (7 to 0)

HSYNC

VSYNC

CNTL

DE

LOS

PANEL (1, 0)

CLKPOL

TESTEXN

TESTDT

TESTSB

51

18, 19, 22, 23,

24, 25, 30, 31,

6, 7, 10, 11,

12, 13, 14, 15,

58, 59, 62, 63,

2, 3, 4, 5

56

57

49

50

36

35, 34

32

43,

37,

38

TTL out

TTL out

TTL out

TTL out

TTL out

TTL out

TTL out

TTL in

TTL in

TTL in

Shift clock, for the data

fetch at falling or rising

edge

Pixel data

Hsync data

Vsync data

Control data

Display enable data

Los of signal

Panel mode select switch

Trigger edge select switch

Reserved for TEST under

fabrication

Pin Number Type Descriptions Equivalent circuit

VCCT

TTL-OUT

V

EET

300

6k

6k

VCCT

TTL-IN

V

EET

V

CCG

V

EEG

VCCG

SDATAP/N

REFRQP/N

V

EEG

SDATAP/N

REFRQP/N

40, 41

39, 42

Rx

Rx

Serial input

Refclk request

– 4 –

CXB1454R

Tab. 3. Special

Pin Name

33 External Resister

Pin Number Descriptions Equivalent circuit

REXT

47, 48 External loop filterLPFA/B

VCCG

REXT

V

EEG

VCCA

LPFA

LPFB

V

EEA

– 5 –

CXB1454R

Electrical characteristics

Tab. 4. Absolute Maximum Rating

Description

Power supply voltage

TTL DC input voltage

TTL output current (High)

TTL output current (Low)

Serial input pin voltage

REFRQ output pin voltage

Storage temperature

VCC

VI_T

IOH_T

IOL_T

Vsdin

VRQout

Tstg

–0.3

–0.5

–20

0

–0.5

0.5

–65

4

5.5

0

20

VCC + 0.5

VCC + 0.5

150

V

V

mA

'

mA

V

V

°C

Symbol Min. Typ. Max. Unit Comments

Tab. 5. Recommended Operating Conditions

Description

Power supply voltage (Include VCCT5)

Operating temperature

VCC

Topr

3.135

0

3.3 3.465

60

V

°C

Symbol Min. Typ. Max. Unit Comments

Tab. 6. DC Characteristics (Under the recommended conditons. See Tab. 5)

Description

Input HIGH voltage (TTL)

Input LOW voltage (TTL)

Input HIGH current (TTL)

Input LOW current (TTL)

Output HIGH voltage (TTL)

Output LOW voltage (TTL)

Output HIGH current (REFRQ)

Output LOW current (REFRQ)

Input dynamic range (SDATA)

Input dynamic range (SDATA)

Supply current

VIH_T

VIL_T

IIH_T

IIL_T

VOH_T

VOL_T

IOH_RQ

IOL_RQ

VIM_SD

VID_SD

ICC

2

0

–400

2.25

–0.1

7.8

VCC – 0.4

–0.5

0

325

350

5.5

0.8

20

0.5

+0.1

11

VCC + 0.2

+0.5

440

465

V

V

µA

µA

V

V

mA

mA

V

V

mA

mA

VIN = VCC

VIN = 0

IOH = –0.2mA

IOL = 4mA

See Fig. 3, 4

REXT = 1.3kΩ

Common mode voltage

Differential voltage

65MHz,

All low pattern,

Outputs open

65MHz,

Worst case pattern

See Fig. 8

Outputs open

Symbol Min. Typ. Max. Unit Conditions

– 6 –

CXB1454R

VCCA/G/T

V

EEA/G/T

VCC

CXB1454R

AA

37

38

43

39

42

TESTDT

TESTSB

TESTEXN

REFRQP

REFRQN

150Ω

150Ω

50Ω50Ω

Fig. 2. IOH_RQ and IOL_RQ DC measurement

Tab. 7. AC Characteristics (Under the recommended conditons. See Tab. 5)

Description

Minimum SFTCLK frequency

Maximum SFTCLK frequency

SFTCLK duty factor

Pixel/Sync/Cntl/DE setup to

SFTCLK

Pixel/Sync/Cntl/DE hold to

SFTCLK

SFTCLK rise time

SFTCLK fall time

Pixel/Sync/Cntl/DE rise time

Pixel/Sync/Cntl/DE fall time

CLOCK mode assert time

CLOCK mode deassert time

LOS signal assert time

LOS signal deassert time

Fsftclk

Dsftclk

Tsetup

Thold

Torc

Tofc

Tofd

Tord

TAclk

TDclk

TAlos

TDlos

65.0

40

16

10

5

17

11

6

0.9

50

0.5

0.1

25.0

60

3

2.5

4.5

2

MHz

MHz

%

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

µs

µs

µs

µs

Vth = 1.4V, CL = 10pF

Vth = 1.4V, CL = 10pF

25MHz

40MHz

65MHz

Vth = 1.4V, CL = 10pF

25MHz

40MHz

65MHz

0.8 to 2.0V, CL = 10pF

2.0 to 0.8V, CL = 10pF

0.8 to 2.0V, CL = 10pF

2.0 to 0.8V, CL = 10pF

Symbol Min. Typ. Max. Unit Conditions

TESTDT

TESTSB

TESTEXN

Fig. 3. IOH_RQ and IOL_RQ DC measurement setting

Electrical characteristics

Loading...

Loading...