Sony CXA3506R Datasheet

3-channel 8-bit 120MSPS A/D Converter Amplifier PLL

Description

The CXA3506R is a 3-channel 8-bit 120MSPS A/D

converter with built-in amplifier and PLL developed

for LCD projectors and LCD monitors.

The CXA3506R inputs RGB graphics signals from

personal computers or others. After the input levels

are controlled, the A/D conversion is performed with

a clock generated by PLL.

The digital output levels are compatible with TTL.

This IC operates at a maximum conversion rate of

120MHz, and can support up to XGA. Control register

supports both I2C and 3-wire bus.

Features

• Supply voltage: 5V, 3.3V

• Power consumption: 1.7W typ. (120MSPS)

• 144-pin LQFP

• 3-ch AMP and PLL eliminate design time for mutual

connections.

Structure

Bipolar silicon monolithic IC

Applications

• LCD monitors

• LCD projectors

• Digital TVs

• PDPs

Functions and Performance

• Power save function

• Supports both I

2

C and 3-wire bus

Amplifier block

• Clamp

• Main contrast: 8-bit

• Sub contrast: 8-bit × 3

• Main brightness: 8-bit × 3

• CbCr offset: 6-bit × 2

• Supports YCbCr input

• Two input systems

• AMP monitor output/SW monitor output

• SYNCSEP function

A/D converter block

• Maximum conversion rate: 120MSPS

• Supports XGA input

• Supports demultiplexed output

• Supports both in-phase and alternate phase during

demultiplexing

• Supports YUV4:2:2 output

• Output high impedance mode

• Built-in reference voltage

PLL block

• Sync input frequency: 10kHz to 100kHz

• Clock delay: 1/32 to 64/32CLK

• VCO counter: 12-bit

• Low clock jitter

• CLK inversion

• CLK and 1/2CLK outputs

• Phase comparison hold

• Output high impedance mode

– 1 –

E99Y22B1Z-PS

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

CXA3506R

144 pin LQFP (Plastic)

– 2 –

CXA3506R

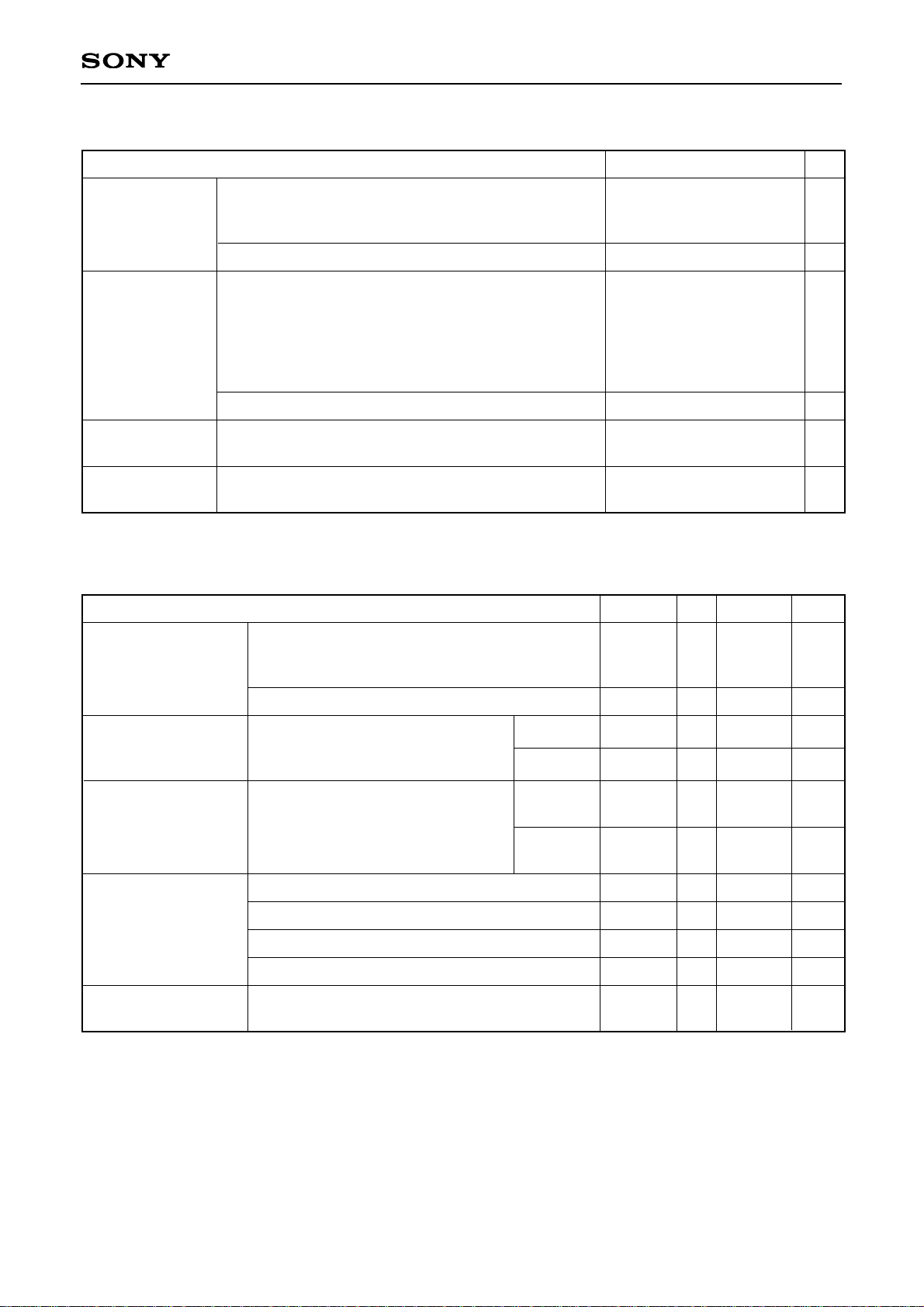

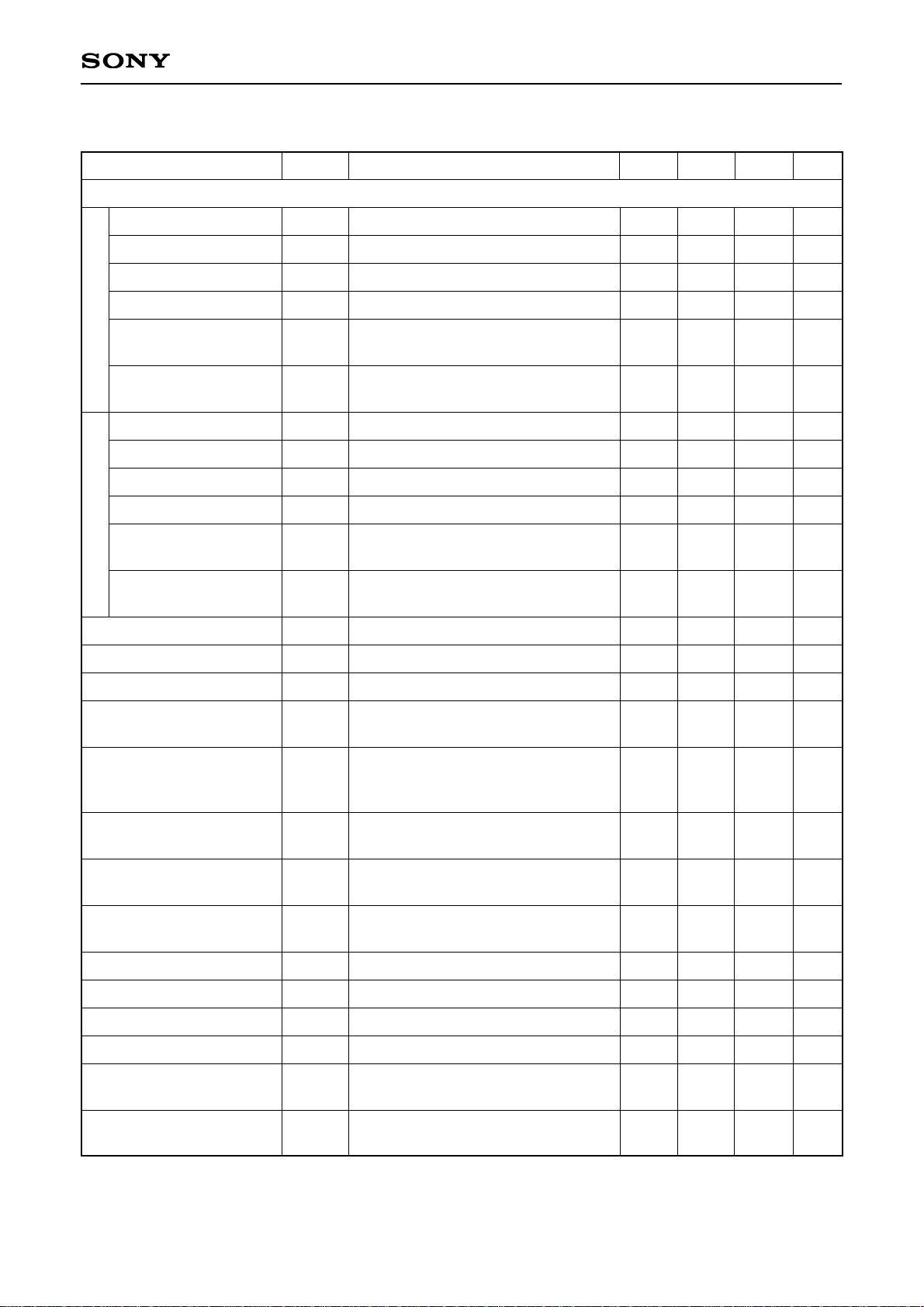

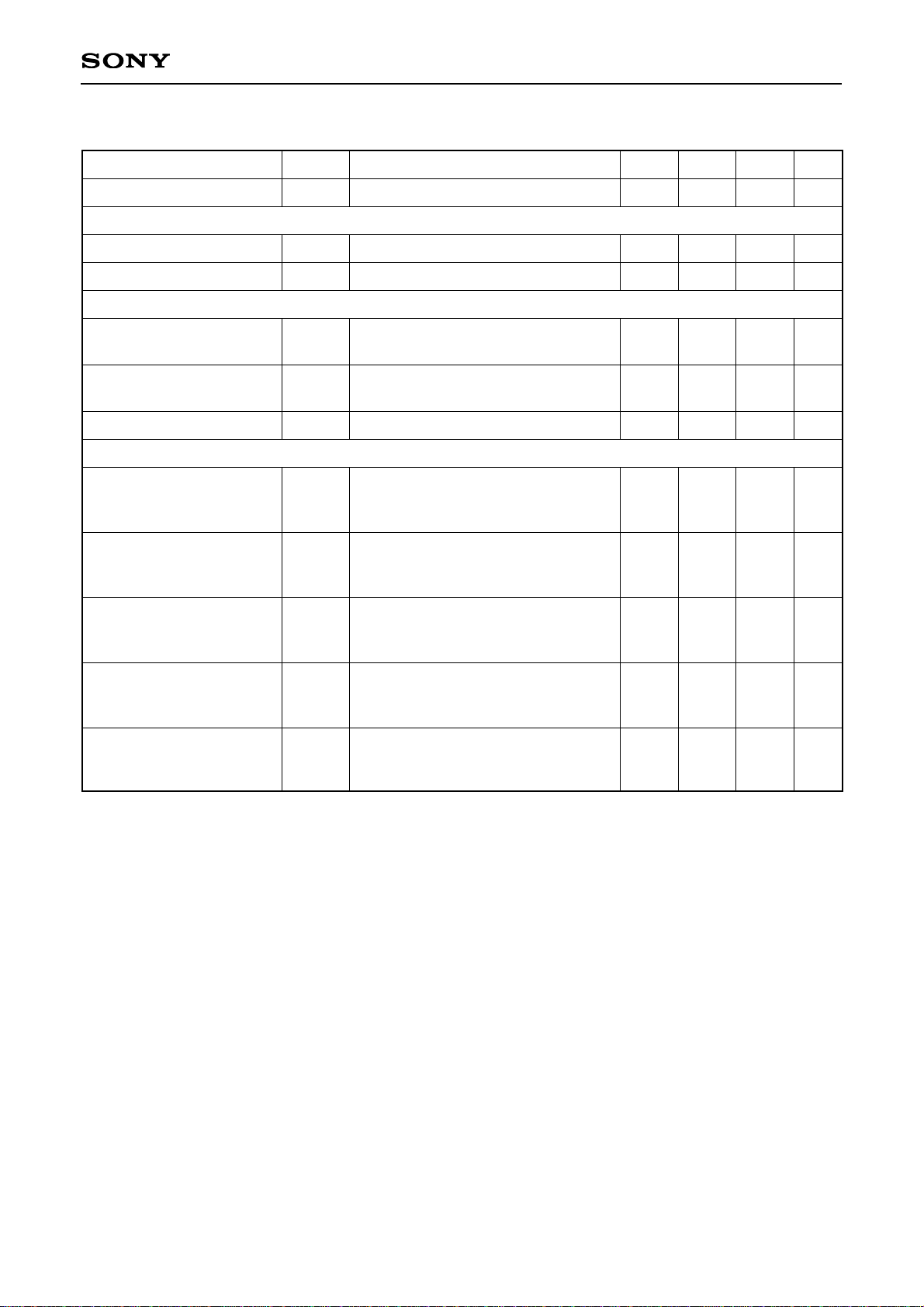

Absolute Maximum Ratings (Ta = 25°C)

Item

DV

CCREG, AVCCADREF, DVCCADTTL, DVCCAD,

DVCCPLLTTL, AVCCVCO, DVCCPLL, AVCCIR,

AVCCAMPR, AVCCAMPG, AVCCAMPB

AVCCAD3, DVCCAD3

ADDRESS, XPOWERSAVE, XSENABLE, 3WIRE/I2C,

HOLD, XTLOAD, EVEN/ODD, XCLKIN, CLKIN,

SYNCIN1, SYNCIN2, CLPIN, RC1, RC2, R/CrIN1,

R/CrIN2, R/CrCLP, G/YCLP, B/CbCLP, SOGIN1,

G/YIN1, SOGIN2, G/YIN2, B/CbIN1, B/CbIN2,

RCrOUT, G/YOUT, B/CbOUT, DACTESTOUT

SDA, SCL

Tstg

PD

Supply voltage

Input voltage

Storage

temperature

Allowable power

dissipation

5.5

5.5

GND – 0.5 to 5V VCC + 0.5

or 5.5

GND – 0.5 to 5.5

–65 to +150

5

V

V

V

V

°C

W

Maximum ratings Unit

Recommended Operating Conditions

Item

DV

CCREG, AVCCADREF, DVCCADTTL, DVCCAD,

DVCCPLLTTL, DVCCPLL, AVCCVCO, AVCCIR,

AVCCAMPR, AVCCAMPG, AVCCAMPB

AVCCAD3, DVCCAD3

XPOWERSAVE, HOLD, XTLOAD,

EVEN/ODD, SYNCIN1, SYNCIN2,

CLPIN

CLKIN, XCLKIN

Straight mode

DMUX mode

YUV4:2:2 D2 mode

YUV4:2:2 special mode

Ta

Supply voltage

TTL input pin

PECL input pin

Maximum conversion

rate

Operating ambient

temperature

4.75

3

2

—

DV

CCPLL

–0.8

—

100

120

100

100

–10

5

3.3

—

—

—

—

—

—

—

—

—

5.25

3.6

—

0.8

—

DV

CCPLL

–1.6

—

—

—

—

+75

V

V

V

V

V

V

MSPS

MSPS

MSPS

MSPS

°C

Max.Typ.Min. Unit

High level

Low level

High level

Low level

– 3 –

CXA3506R

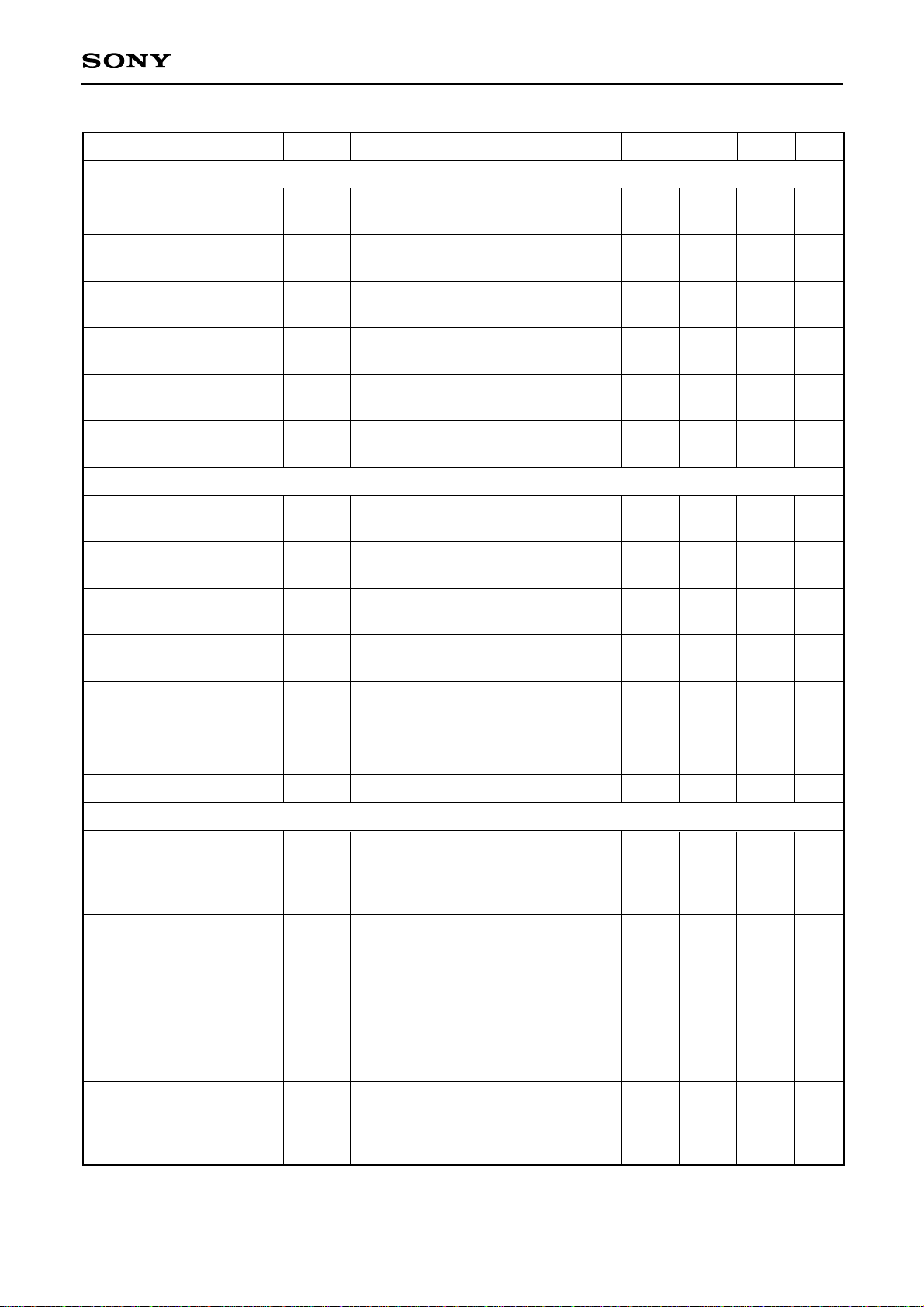

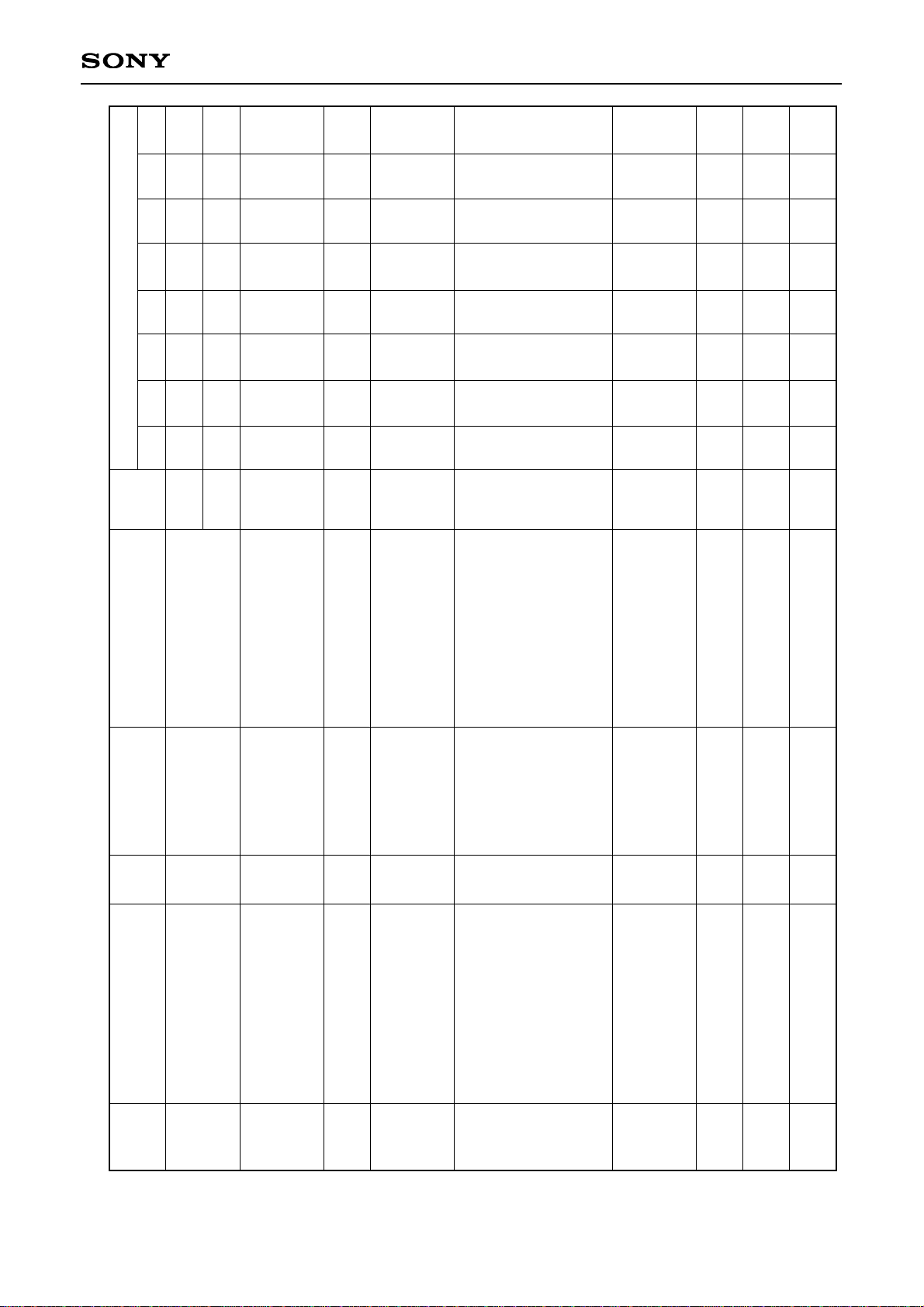

Pin Configuration (Top View)

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

7374757677

78

79

80

81

828384

85

8687

88

89

90

91

92

93

949596979899

100101102103104105

106

107108

133

134

135

136

137

138

139

140

141

1 2 3 4

121

122

123

124

125

126

127

128

129

130

131

132

142

143

144

110

109

111

112

113

114

115

116

117

118

119

120

5 6 7 8 9 10 12 13 14 15 16 17 18 19 20 22 23 24 25 26 27 28 29 30 32 33 34 35 3611 21 31

B/CbOUT

ADDRESS

R/CrOUT

NC

NC

XPOWER SAVE

DGNDREG

DVCCREG

SDA

SCL

XSENABLE

SEROUT

3WIRE/I

2

C

DPGND

AVCCADREF

AVCCAD3

VRT

DVCCAD3

DVCCADTTL

DGNDADTTL

RA0

RA1

DGNDAD3

RA2

RA3

RA4

RA5

RA6

AGNDAD3

DGNDAD3

RA7

DVCCADTTL

DGNDADTTL

RB0

RB1

RB2

GA4

GA3

GA2

GA1

GA0

DGNDADTTL

DGNDAD3

DVCCADTTL

BB7

BB6

BB5

BB4

BB3

GNDAD3

BB2

BB1

BB0

DGNDADTTL

DVCCADTTL

BA7

BA6

BA5

DGNDAD3

BA4

BA3

BA2

BA1

BA0

DGNDADTTL

DGNDAD3

DVCCADTTL

RB7

RB6

RB5

RB4

RB3

EVEN/ODD

XTLOAD

HOLD

SOGOUT

UNLOCK

DSYNC/DIVOUT

DPGND

1/2CLK

1/2XCLK

CLK

XCLK

DGNDPLLTTL

DV

CCPLLTTL

AGNDADREF

AV

CCAD3

VRB

DVCCAD3

DVCCAD

DVCCADTTL

DGNDADTTL

GB7

GB6

DGNDAD3

GB5

GB4

GB3

GB2

GB1

AGNDAD3

DGNDAD3

GB0

DGNDADTTL

DVCCADTTL

GA7

GA6

GA5

XCLKIN

CLKIN

SYNCIN1

SYNCIN2

CLPIN

DVCCPLL

DGNDPLL

AVCCVCO

AGNDVCO

RC1

RC2

AV

CCIR

IREF

DPGND

AGNDIR

G/YIN1

AV

CCAMPG

G/YIN2

AGNDAMPG

G/YCLP

B/CbCLP

R/CrCLP

DPGND

SOGIN1

B/CbIN1

AVCCAMPB

SOGIN2

B/CbIN2

AGNDAMPB

DPGND

R/CrIN1

AVCCAMPR

R/CrIN2

AGNDAMPR

G/YOUT

DACTESTOUT

– 4 –

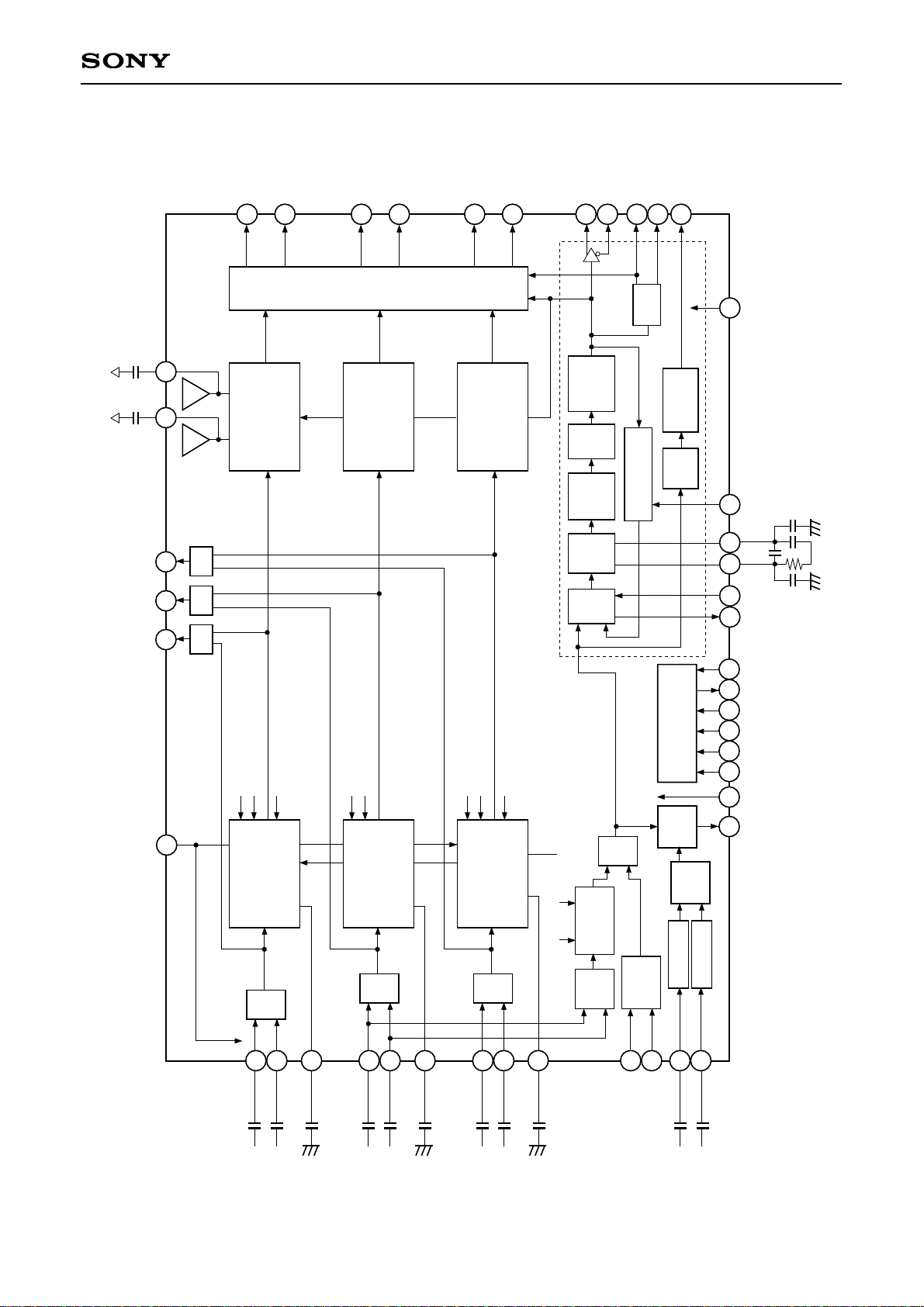

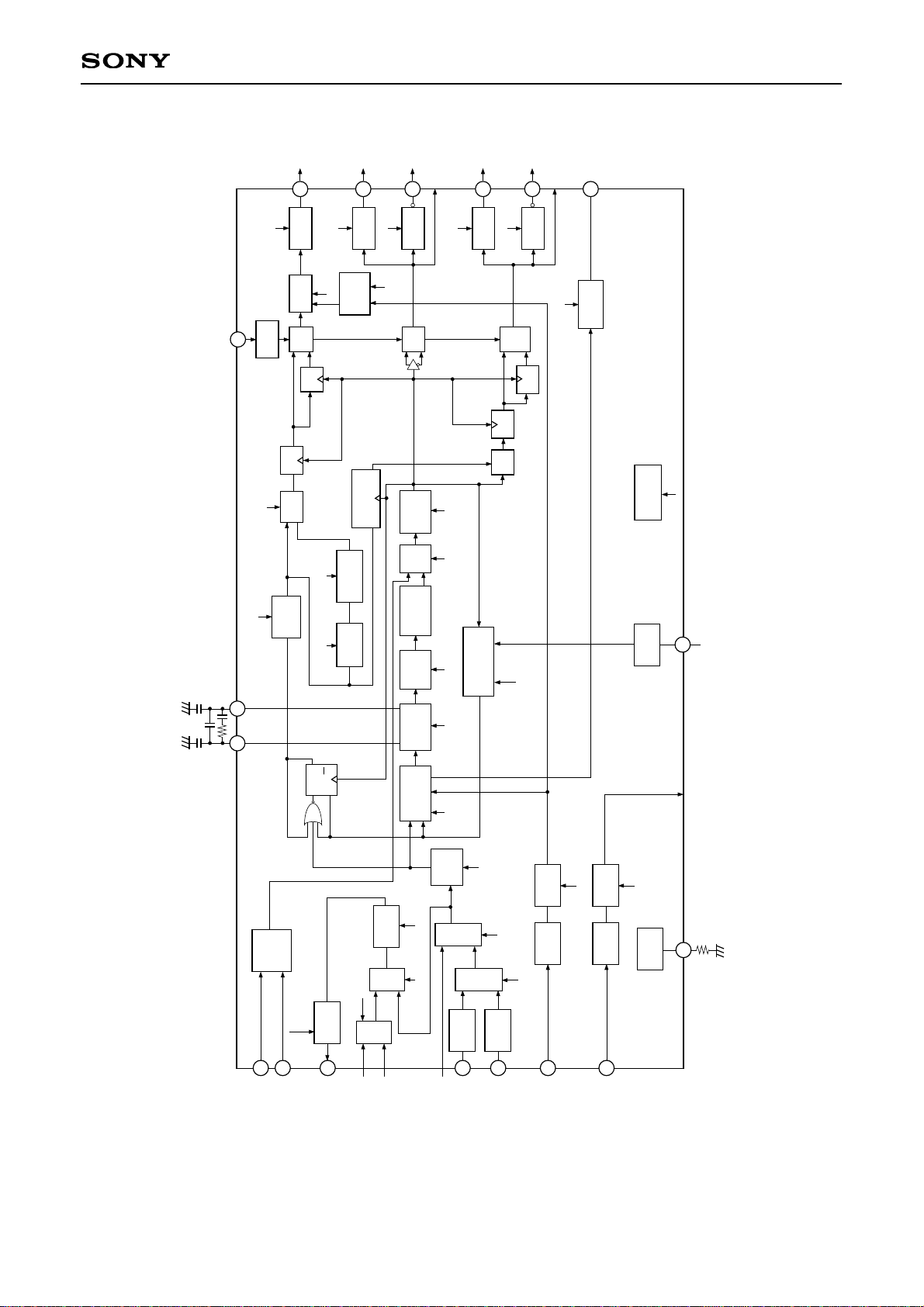

CXA3506R

AMP R

SW

R

AMP G

AMP B

ADC R

ADC G

ADC B

SW

SW

G

SW

B

SYNCSEP

SYNCSEP

SYNCSEP

SW

PLL

PD

PLL

CP (3)

FINE

DELAY

(6)

Width

(2)

COARSE

DELAY (2)

VCO

DIV

1, 2, 4, 8

REGISTER

ADDRESS

SOGOUT

XPOWER SAVE

SDA

SCL

XSENABLE

SEROUT

3WIRE/I

2

C

HOLD

XTLOAD

RC1

RC2

COUNTER (12)

1/2DIV

UNLOCK

Sub Contrast (8)

Sub Brightness (8)

R/CrIN1

CLPIN

R/CrOUT

R/CrIN2

R/CrCLP

G/YCLP

G/YIN1

G/YIN2

B/CbCLP

SYNCIN1

SYNCIN2

B/CbIN1

B/CbIN2

SOGIN1

SOGIN2

SYNCTIP

CLP

Cr Offset (6)

Sub Contrast (8)

Sub Brightness (8)

Sub Contrast (8)

Main Contrast (8)

V

TH (4) VHYS (2)

Sub Brightness (8)

Cb Offset (6)

SW

G/YOUT

SW

B/CbOUT

VRT

VRT VRB

VRB

DATA MODE

RB7 to RB0

RA7 to RA0

GB7 to GB0

GA7 to GA0

BB7 to BB0

BA7 to BA0

XCLK

1/2CLK

EVEN/ODD

1/2XCLK

DSYNC/DIVOUT

CLK

SW

SOGT

SW

SOGO

SW

SOGP

SW

SYNCIN

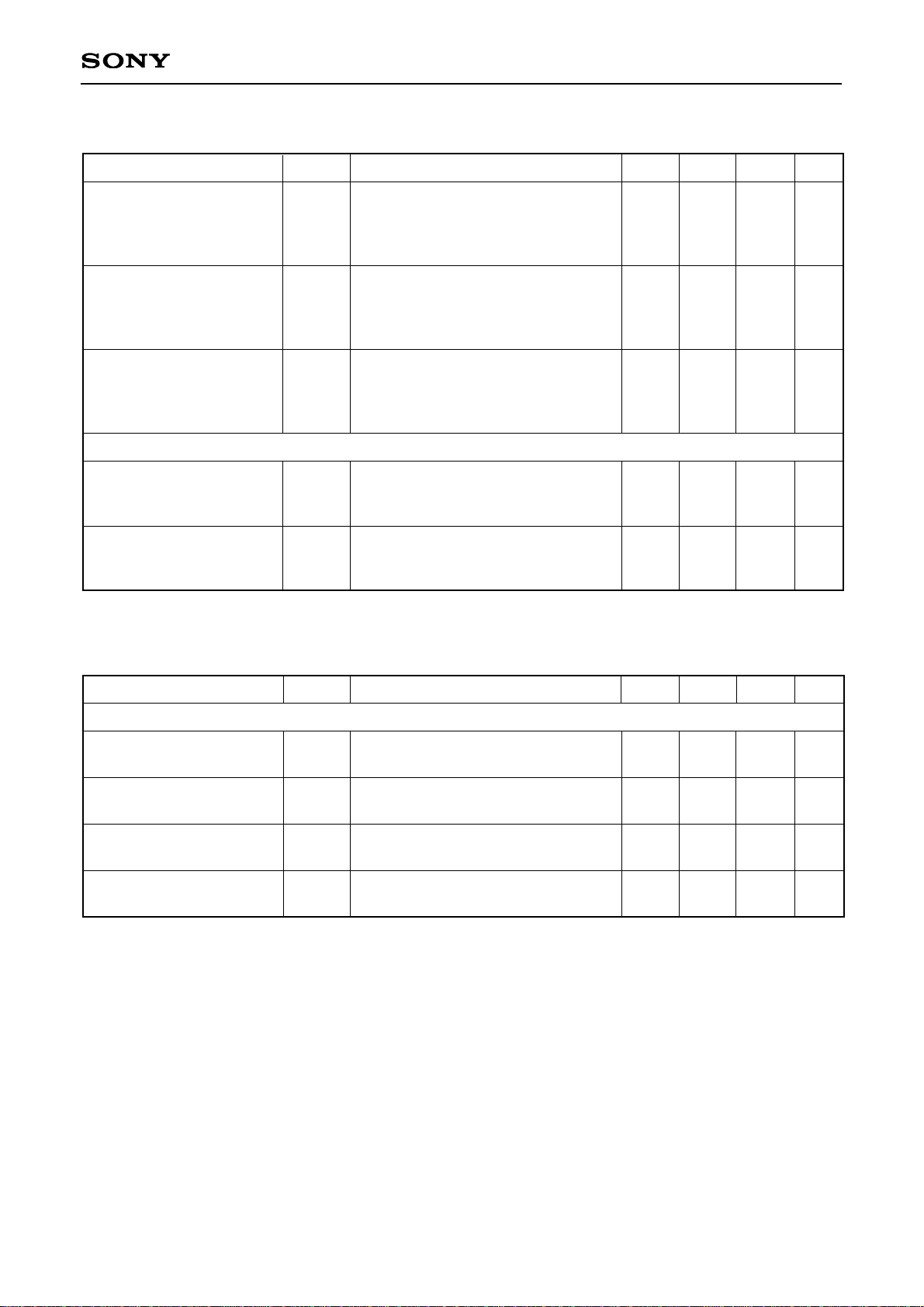

TOP Block Diagram

– 5 –

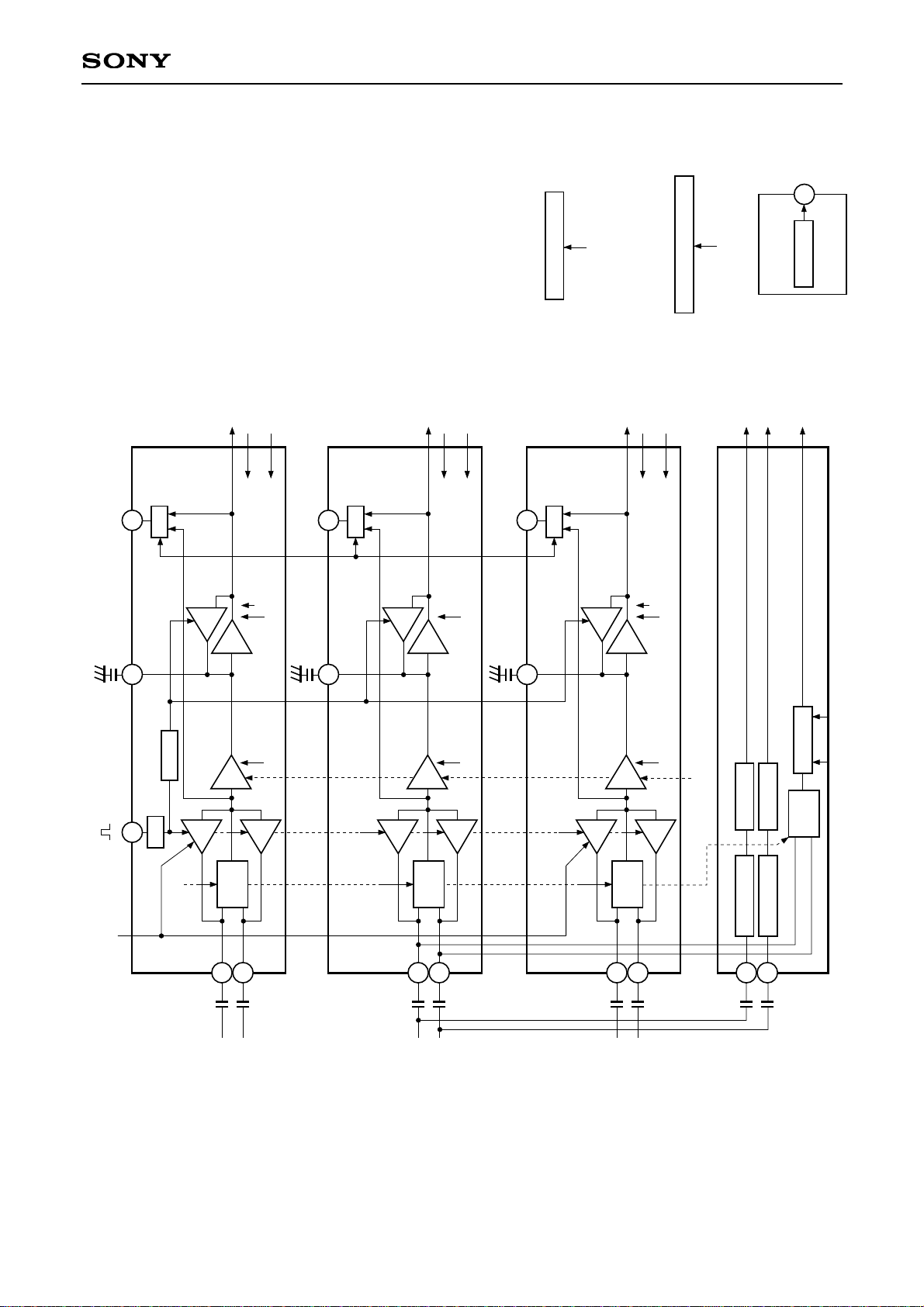

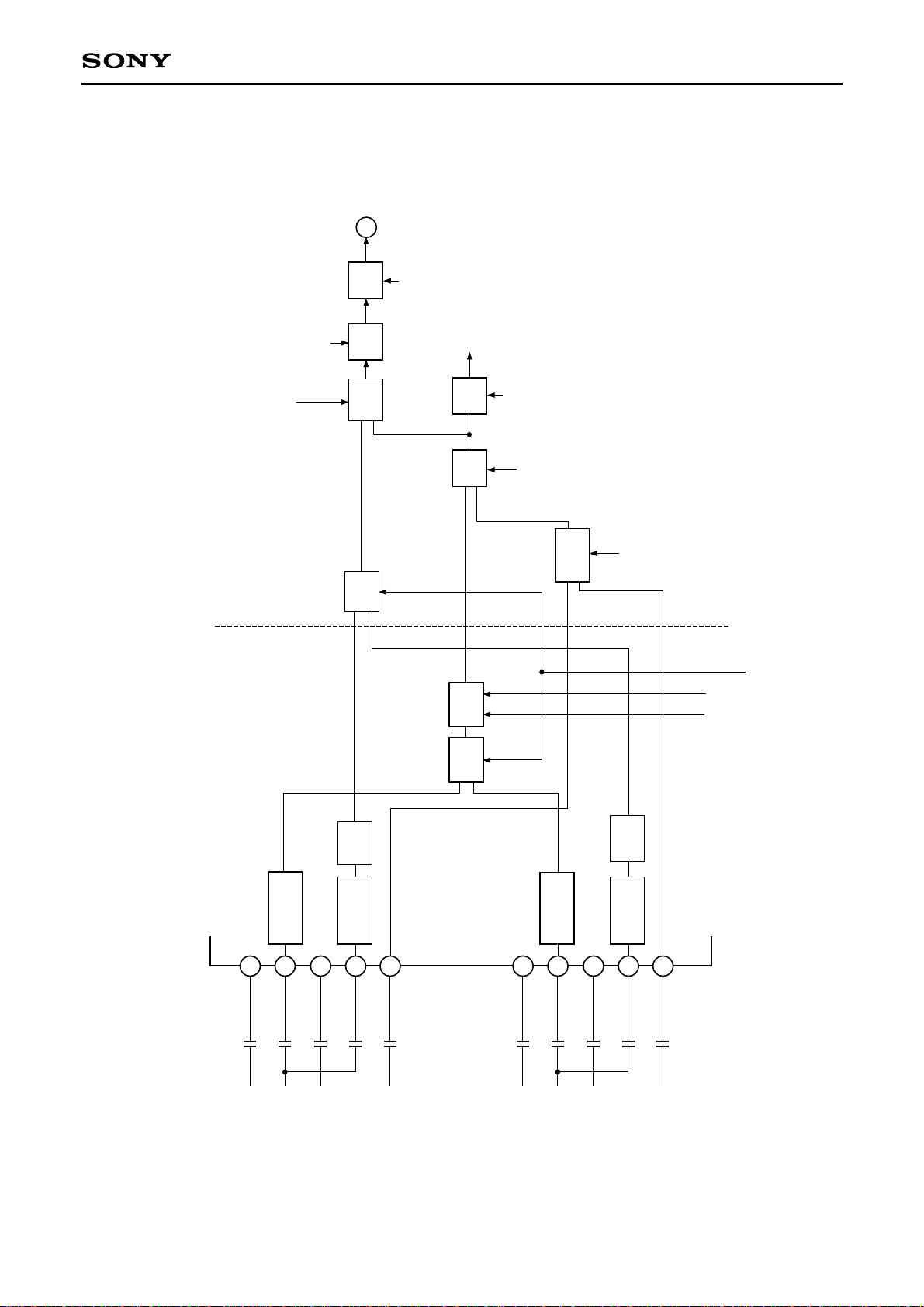

CXA3506R

Amplifier Block Diagram

CLP

CLP

DRV

GCA

CLP

POL

1bit

1bit

1bit

R/CrOUTR/CrCLPCLPIN

Rch

R/CrIN1

R/CrIN2

Sub

Contrast

8bit

Sub Brightness

8bit

CLPOFF

SW

VRT

VRB

ADC R

SW

R

Sub Brightness

8bit

Cr Offset

6bit

CLP

CLP

DRV

GCA

CLP

G/YOUTG/YCLP

Gch

RGB/YUV 1bit

G/YIN1

G/YIN2

Sub

Contrast

8bit

SW

VRT

VRB

ADC G

SW

G

Sub Brightness

8bit

Cb Offset

6bit

CLP

CLP

DRV

GCA

CLP

Main Contrast 8bit

SYNC ON GREEN SEPARATOR

B/CbOUTB/CbCLP

Bch

B/CbIN1

B/CbIN2

SOGIN1

SOGIN2

V

TH 4bit VHYS 2bit

Sub

Contrast

8bit

SW

VRT

VRB

ADC B

SYNC ON GREEN

SYNCT1

SYNC ON GREEN

SYNCT2

SYNC ON GREEN

SYNCP

SW

B

SW

SOGP

SYNC TIP CLP

SYNC TIP CLP

SYNC SEP

SYNC SEP

SYNC SEP

AMP POWER SAVE

1bit

SYNC SEP POWER SAVE

1bit

DACTEST DACTEST OUT

– 6 –

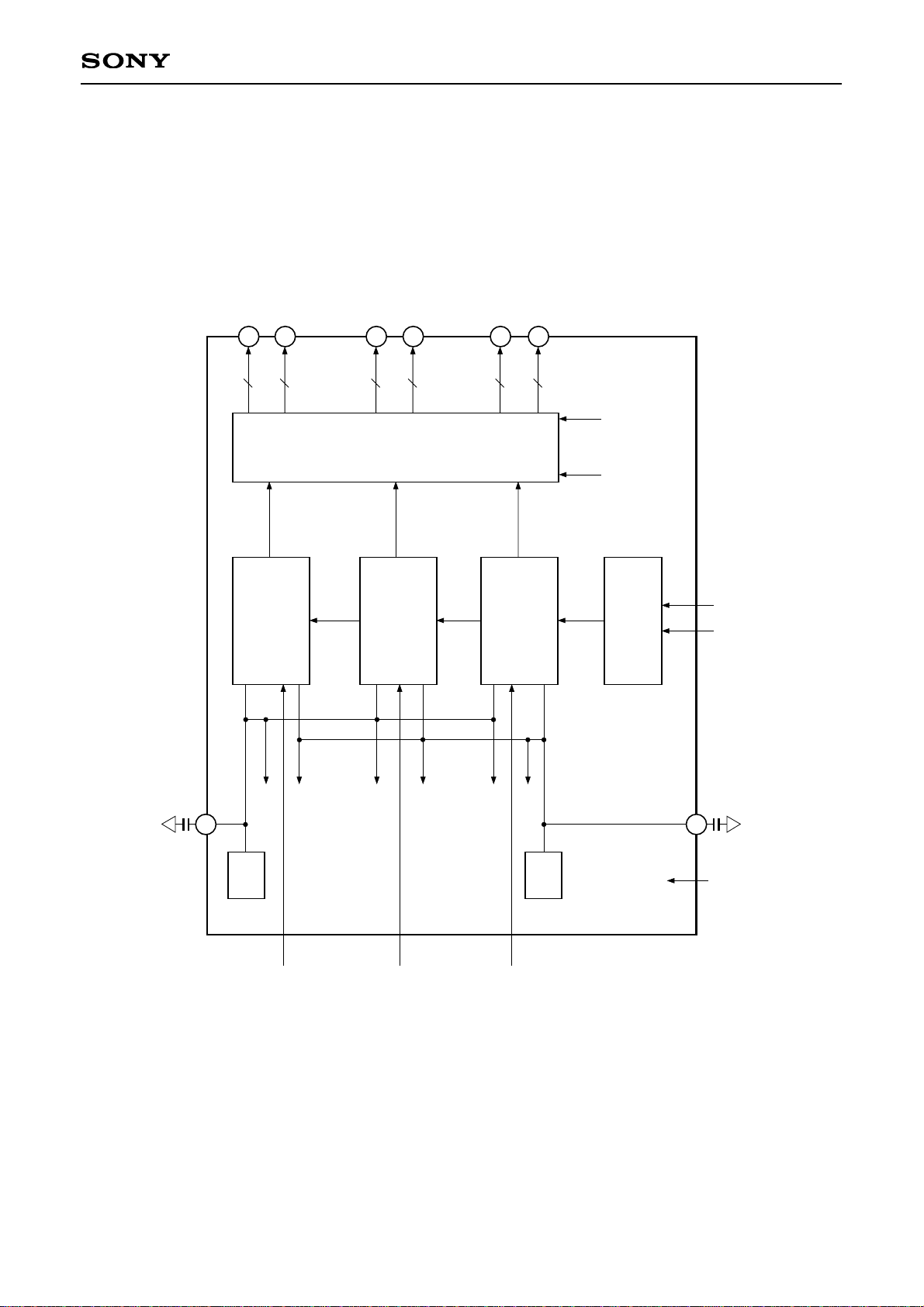

CXA3506R

PECLIN

RC2

PLL

1bit

PD POL

RC1

Reset Pulse

Generator

TTLIN

SW

M

Polarity TTLOUT

TTLOUT

TTLOUT

DSYNC

HOLD

SW

SW

M

M/S

1/2

SW

DIV

1, 2, 4, 8

VCO + 1/4

Fine

Delay

Charge

Pump

Phase

Detector

Programmable

Counter

TTLOUT

TTLIN

TTLIN

TTLIN Polarity

HOLD POL

1bit

1bit

SOG Enable

1bit

SOG OUT POLSYNC OUT SW

1bit

RGBIN1/2SEL

1bit

1bit

IREF Clamp

Pulse

XTLOAD

(TTL)

SYNCP/HSYNC

1bit

SYNC POL

3bit

12bit

VCO DIV

HSYNC1/2

1bit

CLP POL

1bit

TTLIN

DAC

Polarity

TTLIN

PLL

Power Save

Polarity

Polarity

SW

SW

SW

SW

6bit

1/256 to 1/4096

2bit

1bit

DSYNC By-pass

1bit

VCO

By-pass

2bit

RESET

1bit

1bit

DSYNC

HOLD

CLK Enable

DIV

1, 2, 4, 8

1bit

1bit

1bit

XCLK Enable

1bit

1/2CLK Enable

1bit

1/2XCLK Enable

UNLOCK Enable

TTLOUT

TTLOUT

1bit

1bit

DSYNC Enable

EVEN/ODD

(TTL)

DSYNC/DIVOUT

(TTL)

CLKIN

(PECL)

XCLKIN

(PECL)

SOGOUT

(TTL)

SYNCIN1

(TTL)

SYNCIN2

(TTL)

HOLD

(TTL)

CLPIN

(TTL)

SYNC ON GREEN

SYNCT1

SYNC ON GREEN

SYNCT2

SYNC ON GREEN

SYNCP

CLK

(TTL)

XCLK

(TTL)

1/2CLK

(TTL)

1/2XCLK

(TTL)

UNLOCK

1/2CLK (ADC)

CLK (ADC)

DSYNC POL

UNLOCK

Detect

J

K

Q

Q

M/S

SW

Coarse Delay

Coarse

Delay

DIVOUT

Pulse Width

2bit

DIVOUT WIDTH

1bit

DIVOUT Delay

DIVOUT

Delay

PLL Block Diagram

– 7 –

CXA3506R

R/CrIN1

R1

G1

B1

H1

G/YIN1

B/CbIN1

SOGIN1

SYNCIN1

R/CrIN2

R2

G2

B2

H2

G/YIN2

B/CbIN2

SOGIN2

SYNCIN2

SYNC TIP

CLAMP

SYNC

SEP

SW

SOGT

AMP

BLOCK

SYNCT1

SYNCT2

SYNCT

PLL

BLOCK

SW

SOGO

POL

TTL

OUT

SOGOUT

PLL

SYNC OUT SW

1bit

SOG OUT POL

1bit

PEDESTAL

CLAMP

PEDESTAL

CLAMP

SYNC TIP

CLAMP

SYNC

SEP

SW

PLL

SW

SYNCIN

POL

1bit

SYNCP/HSYNC

1bit

HSYNC1/2

4bit

V

TH

2bit

VHYS

1bit

RGB IN 1/2 Select

1bit

SYNC POL

1bit

SOG Enable

SW

SOGP

SYNC

SEP

SYNCP2

SYNCP1

SYNC Block Diagram

– 8 –

CXA3506R

ADC Block Diagram

8

RA7 to RA08RB7 to RB08GA7 to GA08GB7 to GB08BA7 to BA0

8

DATA FORMAT

3bit

DATA INV

1bit

BB7 to BB0

CLK

1/2CLK

AMP R

AMP G

AMP B

VRB

ADC R

ADC G MODE

ADC B

CLK CONT

VRB

VRB

VRB

VRB

VRT

VRT

VRT

VRT

ADC Power Save

1bit

VRT

– 9 –

CXA3506R

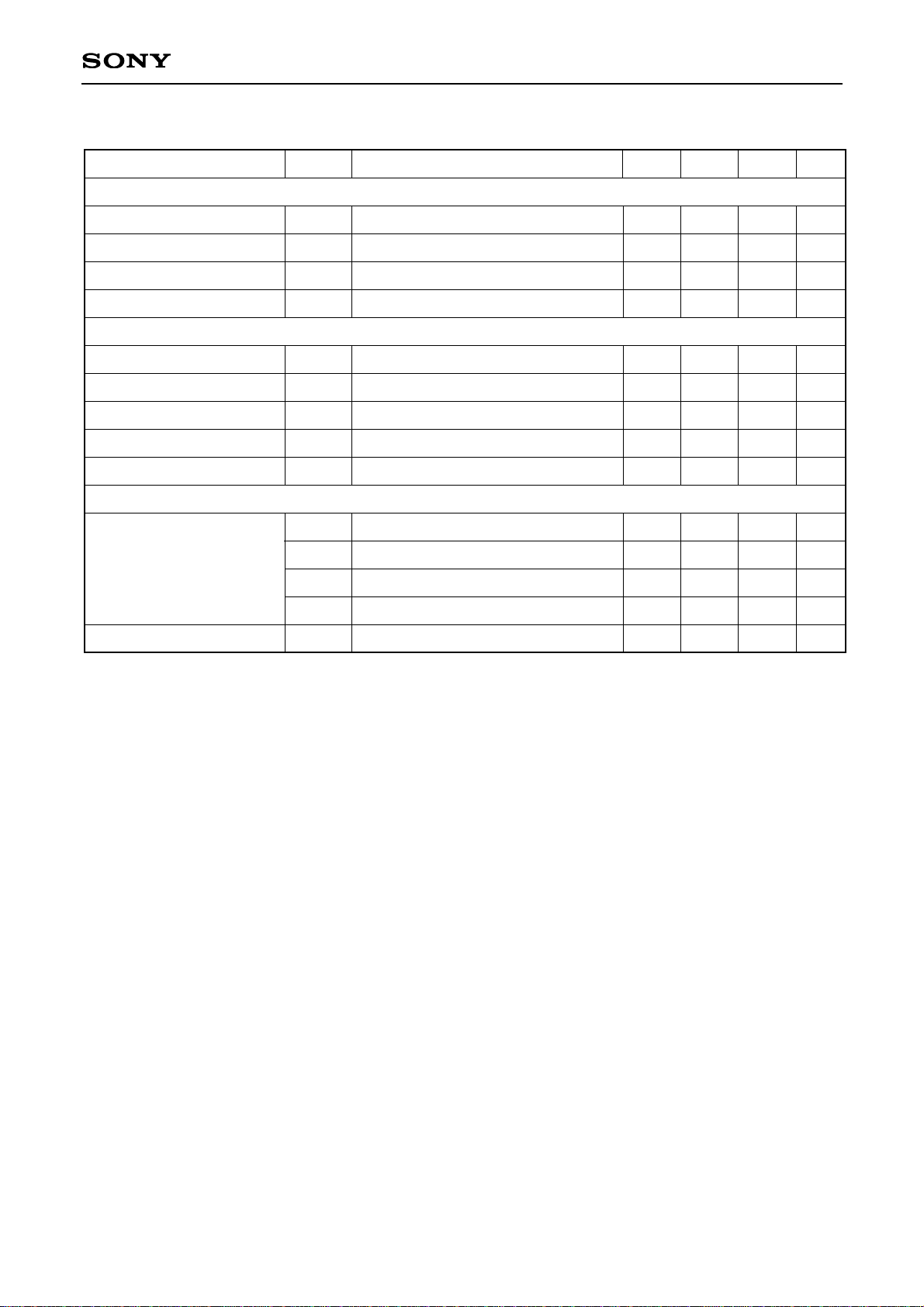

Pin Description

Pin No. Symbol I/O Typical signal Description

1

2

3

4

5

6

7

8

9

10

11

12

13

15

16, 94

17

18, 92

19, 32, 42, 54,

65, 76, 90

20, 33, 44, 55,

67, 77, 89

21, 22,

24 to 28, 31

23, 30, 43, 50,

59, 66, 79, 86

29, 80

34 to 41

45 to 49,

51 to 53

56 to 58,

60 to 64

68 to 75

78, 81 to 85,

87, 88

91

93

95

B/CbOUT

ADDRESS

R/CrOUT

NC

NC

XPOWER SAVE

DGNDREG

DVCCREG

SDA

SCL

XSENABLE

SEROUT

3WIRE/I2C

AVCCADREF

AVCCAD3

VRT

DVCCAD3

DVCCADTTL

DGNDADTTL

RA0 to RA7

DGNDAD3

AGNDAD3

RB0 to RB7

BA0 to BA7

BB0 to BB7

GA0 to GA7

GB0 to GB7

DVCCAD

VRB

AGNDADREF

O

I

O

—

—

I

—

—

I

I

I

O

I

—

—

O

—

—

—

O

—

—

O

O

O

O

O

—

O

—

1.83V

—

1.83V

—

—

TTL

GND

5V

—

—

TTL

TTL

—

5V

3.3V

2.9V

3.3V

5V

GND

TTL

GND

GND

TTL

TTL

TTL

TTL

TTL

5V

1.9V

GND

Amplifier output signal monitor

I2C slave address setting

Amplifier output signal monitor

Not used

Not used

Power save setting

Register GND

Register power supply

Control register data input

Control register CLK input

Enable signal input for 3-wire control register

3-wire control register data readout

Selection of input between I2C bus and 3-wire bus

Reference power supply for A/D converter

Analog power supply for A/D converter

Top reference voltage output for A/D converter

Digital power supply for A/D converter

TTL output power supply for A/D converter

TTL output GND for A/D converter

Data output for R-channel port A side

Digital GND for A/D converter

Analog GND for A/D converter

Data output for R-channel port B side

Data output for B-channel port A side

Data output for B-channel port B side

Data output for G-channel port A side

Data output for G-channel port B side

Digital power supply for A/D converter

Bottom reference voltage output for A/D converter

Reference voltage GND for A/D converter

– 10 –

CXA3506R

96

97

98

99

100

101

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

123

124

125

126

127

128

129

130

132

133

DVCCPLLTTL

DGNDPLLTTL

XCLK

CLK

1/2XCLK

1/2CLK

DSYNC/

DIVOUT

UNLOCK

SOGOUT

HOLD

XTLOAD

EVEN/ODD

XCLKIN

CLKIN

SYNCIN1

SYNCIN2

CLPIN

DV

CCPLL

DGNDPLL

AVCCVCO

AGNDVCO

RC1

RC2

AVCCIR

IREF

AGNDIR

G/YIN1

AVCCAMPG

G/YIN2

AGNDAMPG

G/YCLP

B/CbCLP

R/CrCLP

SOGIN1

B/CbIN1

—

—

O

O

O

O

O

O

O

I

I

I

I

I

I

I

I

—

—

—

—

—

—

—

I

—

I

—

I

—

—

—

—

I

I

5V

GND

TTL

TTL

TTL

TTL

TTL

Open collector

TTL

TTL

TTL

TTL

PECL

PECL

TTL

TTL

TTL

5V

GND

5V

GND

2.1V

2 to 4.5V

5V

1.2V

GND

—

5V

—

GND

—

—

—

2.8V

—

TTL output power supply for PLL

TTL output GND for PLL

Inverted CLK output

CLK output

Inverted 1/2CLK output

1/2CLK output

DSYNC or DIVOUT signal output

Unlock signal output

Output for SYNC ON GREEN

Input for phase comparison disable signal

Programmable counter reset setting

Inverted pulse input of ADC sampling CLK

Inverted CLK input for testing

CLK input for testing

Sync input 1

Sync input 2

Clamp pulse input

Digital power supply for PLL

Digital GND for PLL

Analog power supply for PLL VCO

Analog GND for PLL VCO

External pin for PLL loop filter

External pin for PLL loop filter

Analog power supply for IREF

Current setup

Analog GND for IREF

G/Y signal input 1

Power supply for G/Y amplifier block

G/Y signal input 2

GND for G/Y amplifier block

Clamp capacitor for brightness

Clamp capacitor for brightness

Clamp capacitor for brightness

SYNC ON GREEN signal input 1

B/Cb signal input 1

Pin No. Symbol I/O Typical signal Description

– 11 –

CXA3506R

134

135

136

137

139

140

141

142

143

144

14, 102, 122,

131, 138

AVCCAMPB

SOGIN2

B/CbIN2

AGNDAMPB

R/CrIN1

AVCCAMPR

R/CrIN2

AGNDAMPR

G/YOUT

DAC TEST

OUT

DPGND

—

I

I

—

I

—

I

—

O

O

—

5V

2.8V

—

GND

—

5V

—

GND

1.83V

5V

GND

Power supply for B/Cb amplifier block

SYNC ON GREEN signal input 2

B/Cb signal input 2

GND for B/Cb amplifier block

R/Cr signal input 1

Power supply for R/Cr amplifier block

R/Cr signal input 2

GND for R/Cr amplifier block

Monitor pin for amplifier output signal

DAC testing output for amplifier block control register

GND

Pin No. Symbol I/O Typical signal Description

– 12 –

CXA3506R

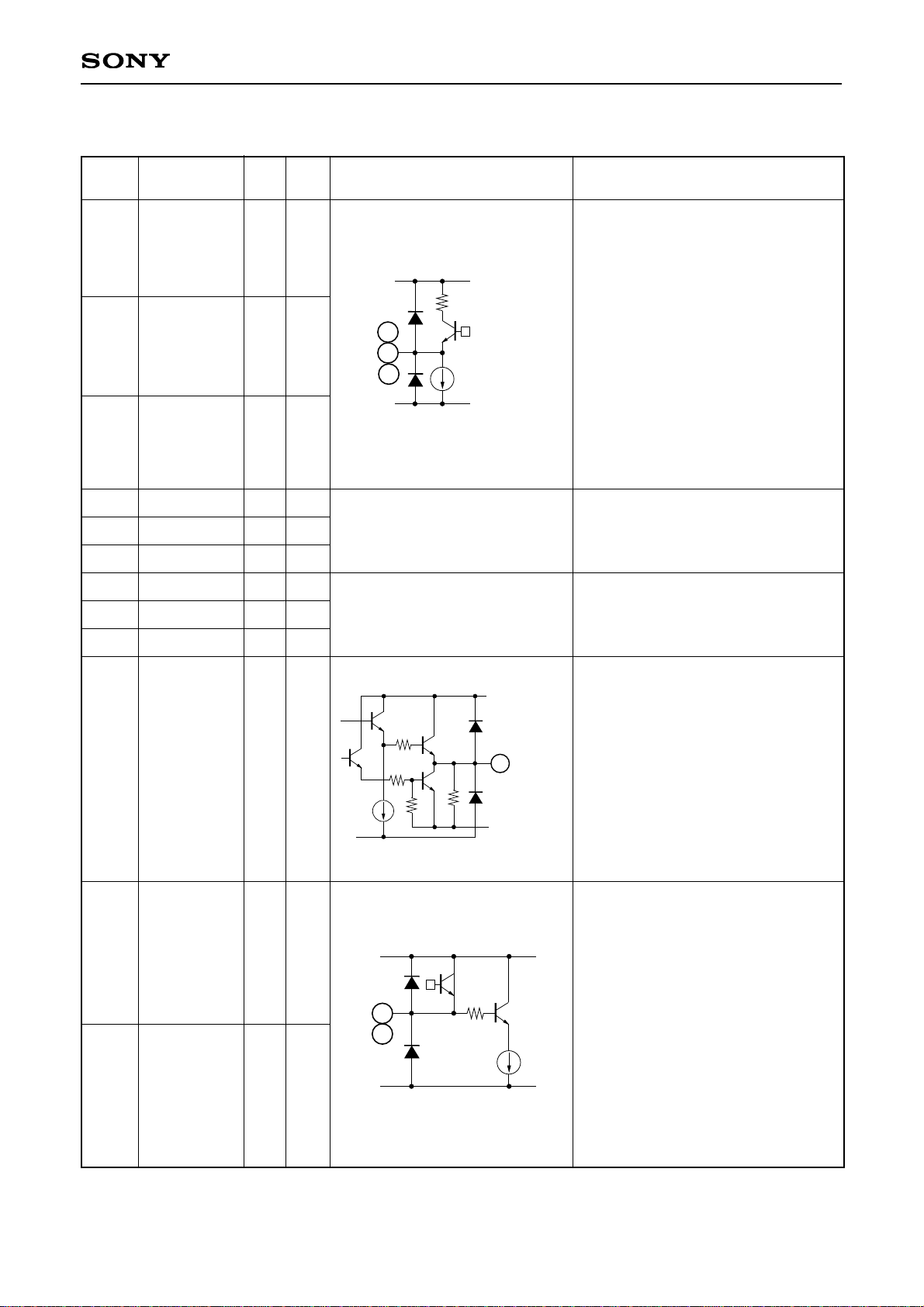

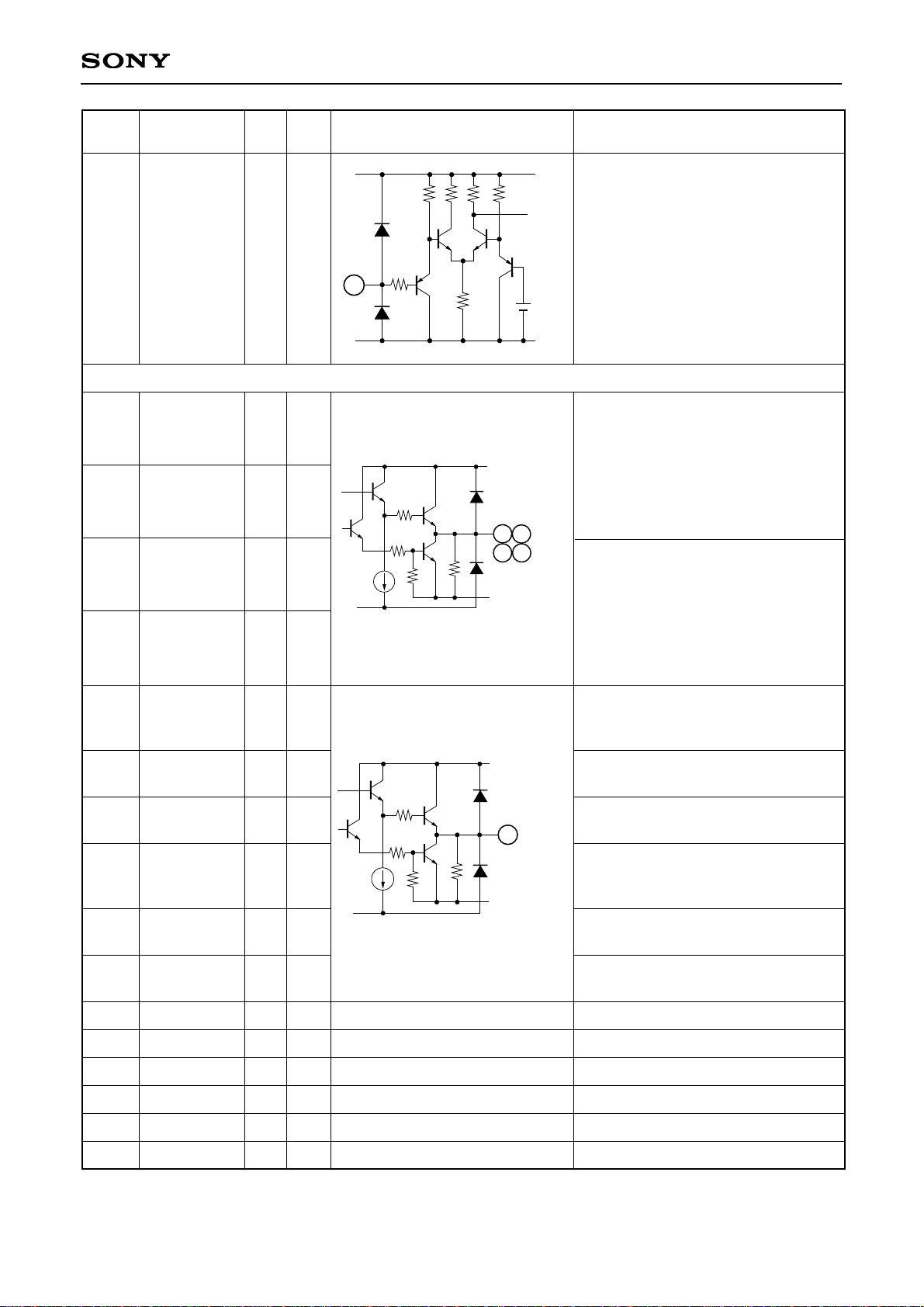

Pin Description and Pin Equivalent Circuit

Pin

No.

Symbol I/O

Typical

signal

Equivalent circuit Description

Power supply for amplifier block.

GND for amplifier block.

Sync separated SYNC signal output.

Separates and outputs the SYNC

signal from SYNC ON GREEN input

signal.

(SYNC signal input from SYNCIN1

and SYNCIN2 pins can be output.)

Both positive and negative polarity

outputs are supported.

The polarity is selected by the control

register.

SYNC ON GREEN signal inputs.

Input via a 0.1µF capacitor.

When not used, connect to AV

CC.

The SYNC TIP clamp level is

approximately 2.0V + Vf (0.8V) =

approximately 2.8V. At this time, if

the pin voltage is lowered, these pins

go to low impedance and current

flows from the IC.

When these pins are at the SYNC

TIP level or higher, the clamp circuit

is off and only an input base current

of approximately 1.2µA flows.

Amplifier output signal monitor.

Each monitor can output either the

entered signal immediately before

A/D converter or the signal after

switching between 2 types of input

signals. The 2 types of input signals

can be selected by the control

register and output.

These pins are emitter follower

outputs, but the internal bias current

is so small that a 820Ω resistor

should be connected between these

pins and GND to monitor high

frequency signals.

When not used, connect to AV

CCAMP.

3

R/CrOUT O

1.83V

143 G/YOUT O

1.83V

1

B/CbOUT

O

1.83V

105

SOGOUT

O

TTL

132

SOGIN1

I

2.8V

135

SOGIN2

I

2.8V

140

125

134

142

127

137

AV

CCAMPR

AVCCAMPG

AVCCAMPB

AGNDAMPR

AGNDAMPG

AGNDAMPB

—

—

—

—

—

—

5V

5V

5V

GND

GND

GND

100

AV

CCAMP

AGNDAMP

280µ

1

3

143

DGNDPLL

100k

DV

CCPLL

DVCCPLLTTL

DGNDPLLTTL

105

150

AV

CCAMPG

AGNDAMPG 100µ

132

135

– 13 –

CXA3506R

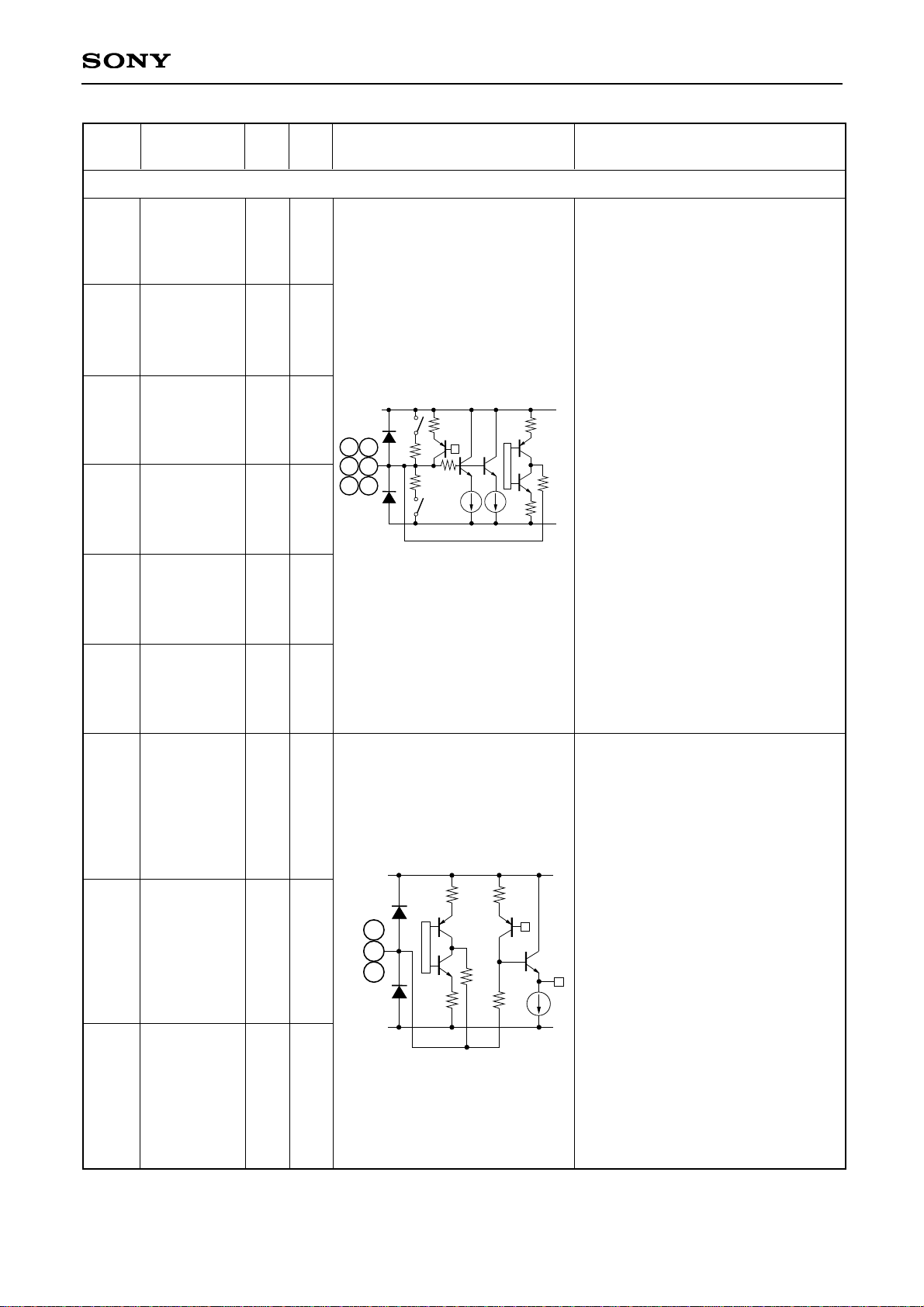

Amplifier block

Analog input signal.

Input via a 0.1µF ceramic capacitor.

The typical signal level is 0.7V.

Signals from 0.5V (min.) to

1.0V (max.) can be supported.

IN1 and IN2 are selected by the

control register.

Leave these pins open when not

used.

RGB input and YCbCr input can be

selected by the control register.

∗

1

The clamp level typical values are

as follows.

In case RGB is input

2.2V + Vf (0.8V) =

approximately 3V

In case YCbCr is input

G/YIN:

2.2V + Vf (0.8V) =

approximately 3V

R/CrIN, B/CbIN:

2.7V + Vf (0.8V) =

approximately 3.5V

Clamp period: A clamp current of

±1.2mA (max.) flows.

Signal period: A base current of

0.5µA flows to the IC.

139

R/CrIN1

I

∗

1

141

R/CrIN2

I

∗

1

124

G/YIN1

I

∗

1

126

G/YIN2

I

∗

1

133

B/CbIN1

I

∗

1

136

B/CbIN2

I

∗

1

130

R/CrCLP

—

∗

2

128

G/YCLP

—

∗

2

129

B/CbCLP

—

∗

2

Clamp capacitor connector for

brightness.

Connect 0.1µF ceramic capacitors

between these pins and GND.

∗2

Typical levels of the clamp are as

follows.

In case RGB is input

SUB BRIGHTNESS

00H: 2.68V

80H: 2.81V

FFH: 2.94V

In case YCbCr is input

G/YCLP is the same as above.

R/Cr, B/CbCLP are as follows.

CbCr Offset

00H: 3.04V

20H: 3.07V

3FH: 3.102V

Clamp period: A clamp current of

±1.2mA (max.) flows.

Signal period: A base current of

0.5µA flows to the IC.

AVCCAMP

AGNDAMP 400µ 100µ

500

100

25k

25k

250

100

124

126

133

136

139

141

AVCCAMP

AGNDAMP

100µ

100k250

500

300

100

128

129

130

Pin

No.

Symbol I/O

Typical

signal

Equivalent circuit Description

– 14 –

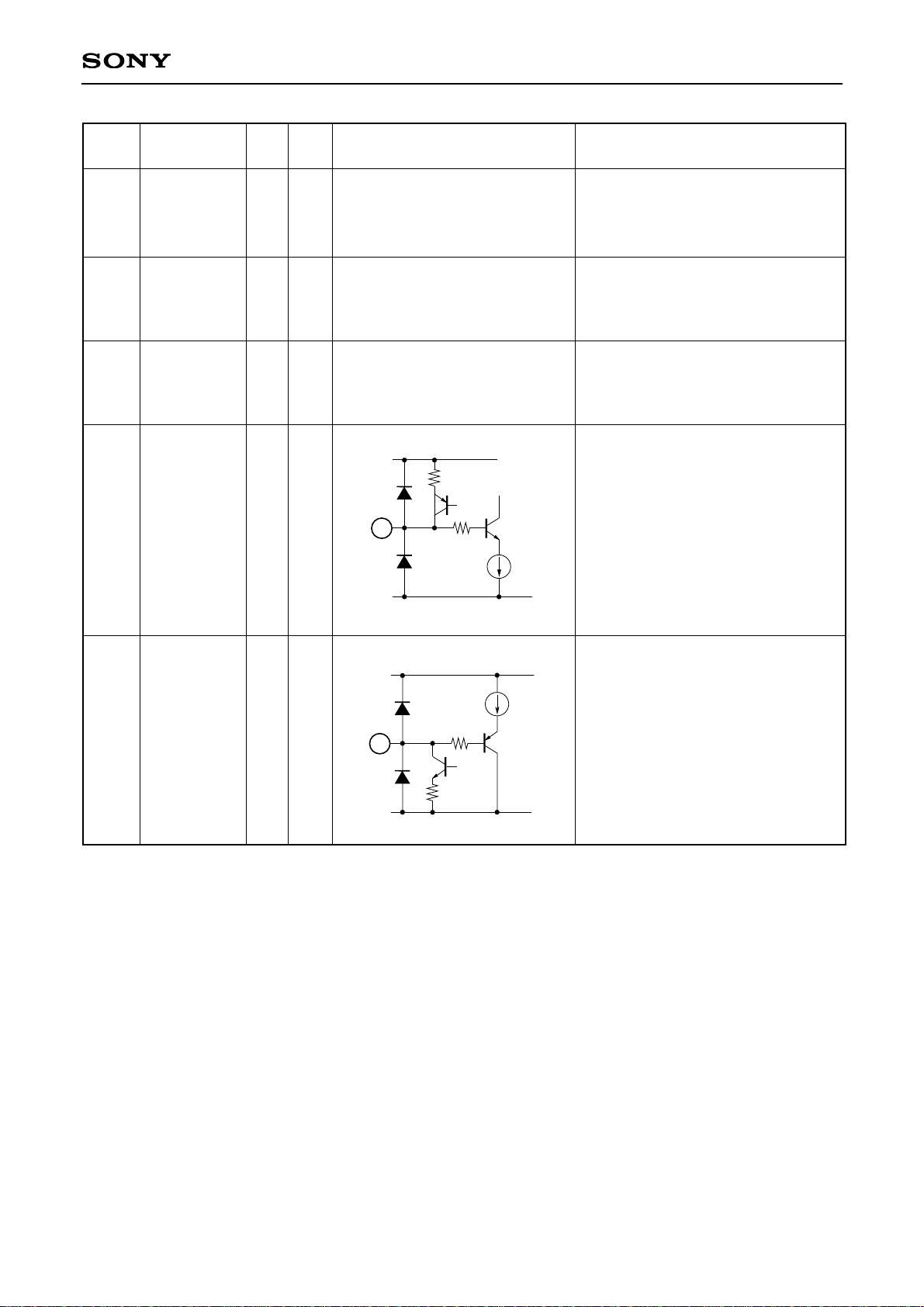

CXA3506R

CLK output.

Output the same frequency CLK as

that of ADC sampling.

These are complemental TTL levels.

These pins can be independently

controlled on and off (power save)

by the control register.

1/2CLK output.

Output a half frequency CLK of that

of ADC sampling.

These are complemental TTL levels.

These pins can be independently

controlled on and off (power save)

by the control register.

Data output for R-channel

port A side.

Data output for R-channel

port B side.

Data output for G-channel

port A side.

Data output for G-channel

port B side.

Data output for B-channel

port A side.

Data output for B-channel

port B side.

21, 22,

24 to 28,

31

34 to 41

68 to 75

78,

81 to 85,

87, 88

45 to 49,

51 to 53

56 to 58,

60 to 64

RA0 to RA7

RB0 to RB7

GA0 to GA7

GB0 to GB7

BA0 to BA7

BB0 to BB7

O

O

O

O

O

O

TTL

TTL

TTL

TTL

TTL

TTL

15

95

16, 94

29, 80

18, 92

91

AV

CCADREF

AGNDADREF

AVCCAD3

AGNDAD3

DVCCAD3

DVCCAD

—

—

—

—

—

—

5V

GND

3.3V

GND

3.3V

5V

Reference power supply for A/D converter.

Reference GND for A/D converter.

Analog power supply for A/D converter.

Analog GND for A/D converter.

Digital power supply for A/D converter.

Digital power supply for A/D converter.

Clamp pulse input for the signal of

analog input clamp and brightness

clamp.

Both positive and negative polarity

inputs are supported.

The polarity is selected by the control

register.

The input pulse width should be

200ns or more.

1.5V

192

1.5k

DV

CCPLL

DGNDPLL

113

A/D converter block

113

CLPIN

I

99

O

TTL

CLK

TTL

98

O

XCLK

TTL

101

O

1/2CLK

TTL

100

O

1/2XCLK

TTL

DGNDPLL

100k

DV

CCPLLTTL

DGNDPLLTTL

98

99

100101

100k

DV

CCADTTL

DGNDADTTL

DGNDAD3

Pin

No.

Symbol I/O

Typical

signal

Equivalent circuit Description

– 15 –

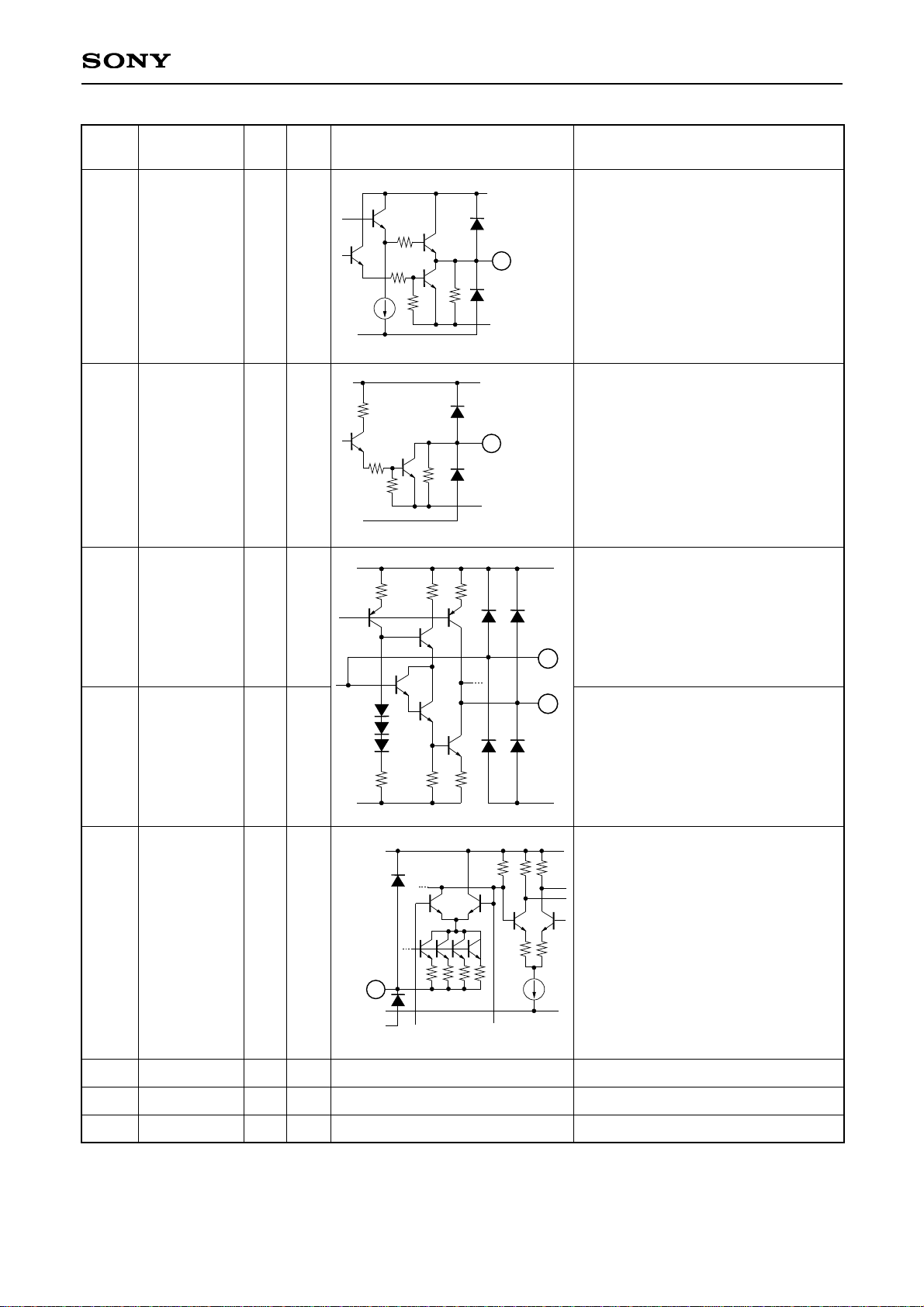

CXA3506R

Top reference voltage output for A/D

converter input dynamic range.

Connect to AVCCAD3 via a 1µF

ceramic capacitor.

Bottom reference voltage output for

A/D converter input dynamic range.

Connect to AV

CCAD3 via a 1µF

ceramic capacitor.

Digital GND for A/D converter.

TTL output power supply for A/D

converter.

TTL output GND for A/D converter.

DGNDAD3

DVCCADTTL

DGNDADTTL

—

—

—

GND

5V

GND

23, 30,

43, 50,

59, 66,

79, 86

19, 32,

42, 54,

65, 76,

90

20, 33,

44, 55,

67, 77,

89

VRT

O

2.9V

17

VRB

O

1.9V

93

AVCCADREF

AGNDADREF

2k

20µ

90

17

AVCCADREF

AGNDADREF

4k

20µ

80

93

Pin

No.

Symbol I/O

Typical

signal

Equivalent circuit Description

– 16 –

CXA3506R

PLL block

Input SYNC signal at TTL level.

The input polarity is switched by the

control register.

Leave this pin open when not used.

Input SYNC signal at TTL level.

The input polarity is switched by the

control register.

Leave this pin open when not used.

Input signal for phase comparison

HOLD.

Phase comparison is stopped, and

VCO oscillation frequency is held.

When not be hold, fix the pin as

follows.

When HOLDPOL register is "1", fix

this pin to low level.

When HOLDPOL register is "0", leave

this pin open or fix to high level.

Input the signal used to invert the

A/D converter sampling CLK.

Low: EVEN mode

High: ODD mode

Normally fix it to low level.

Programmable counter reset.

Normally fix it to high level or leave

open.

In programmable counter test mode,

set it to low level to call up the register

contents.

When not used, leave this pin open

or fix to high level.

1.5V

192

40k

DV

CCPLL

DGNDPLL

112

111

107

108

106

DGNDPLL

DVCCPLL

14k

500

500

14k

110

109

CLK input for ADC operation check.

Input PECL level signal

complementally.

When using this pin, set CLK to

external input by the control register.

Leave this pin open when not used.

SYNCIN1

SYNCIN2

HOLD

EVEN/ODD

XTLOAD

I

I

I

I

I

TTL

TTL

TTL

TTL

TTL

111

112

106

108

107

110

109

CLKIN

XCLKIN

IIPECL

PECL

Pin

No.

Symbol I/O

Typical

signal

Equivalent circuit Description

– 17 –

CXA3506R

This pin can output either DSYNC

signal or DIVOUT signal.

It can be selected by the control

register.

In addition, the output polarity can be

selected by the control register.

External pin for PLL loop filter.

External pin for PLL loop filter.

Connect an external resistor (3kΩ)

to supply a stabilized current to the

inside of the IC. (charge pump

current, etc.)

Connect this pin to GND via 0.1µF

ceramic capacitor connected as

close to the pin as possible.

The band gap voltage is output.

DSYNC/

DIVOUT

O

TTL

103

DGNDPLL

100k

DV

CCPLL

DVCCPLLTTL

DGNDPLLTTL

103

UNLOCK signal output.

Make a discrimination between lock

and unlock in the analog manner by

connecting the external circuit.

Leave this pin open when not used.

Do not connect this pin to neither

power supply nor GND.

UNLOCK

—

—

104

RC1

—

2.1V

118

RC2

—

2 to

4.5V

119

IREF

I

1.2V

121

100k

DGNDPLL

DGNDPLLTTL

DV

CCPLLTTL

104

AVCCIR

AGNDIR DPGND

118

119

DPGND

AGNDIR

AV

CCIR

121

114

115

96

DVCCPLL

DGNDPLL

DVCCPLLTTL

Digital power supply for PLL.

Digital GND for PLL.

TTL output power supply for PLL.

—

—

—

5V

GND

5V

Pin

No.

Symbol I/O

Typical

signal

Equivalent circuit Description

– 18 –

CXA3506R

Input control register data.

Switching between the I2C and

3-wire bus mode is performed by the

3WIRE/I2C pin.

Control register block

9

I

SDA

—

9

DGNDREG

DVCCREG

200k

4k

Input control register CLK.

Switching between the I2C and

3-wire bus mode is performed by the

3WIRE/I2C pin.

10

I

SCL

—

10

DGNDREG

DVCCREG

200k

4k

10k

Set slave address when using I2C

bus mode.

Slave address: 1 0 0 1 1 S2 S1 0

Connect this pin to GND during

3-wire bus mode.

2

I

ADD

—

DGNDREG

DVCCREG

1k

15µ

15µ

15µ

2

97

120

123

116

117

DGNDPLLTTL

AVCCIR

AGNDIR

AVCCVCO

AGNDVCO

TTL output GND for PLL.

Analog power supply for IREF.

Analog GND for IREF.

Analog power supply for PLL VCO.

Analog GND for PLL VCO.

—

—

—

—

—

GND

5V

GND

5V

GND

VCC to 3/4VCC

3/4VCC to 2/4VCC

2/4VCC to 1/4VCC

1/4VCC to GND

0

1

1

0

1

1

0

0

S2 S1

Pin

No.

Symbol I/O

Typical

signal

Equivalent circuit Description

– 19 –

CXA3506R

When using the read mode of 3-wire

bus mode, the register information

written once is output in series order

from the LSB of the setting sub

address data.

GND for register.

Power supply for register.

7

8

——GND

5V

DGNDREG

DV

CCREG

Inputs enable signal for 3-wire bus.

High level: Control disabled

Low level: Control enabled

Connect this pin to GND when using

I

2

C.

XSENABLE

I

TTL

11

11

DGNDREG

DVCCREG

200k

4k

Selection of input between I2C bus

and 3-wire bus.

3WIRE/I2C

I

—

13

DGNDREG

DVCCREG

100k

100k

100k

15µ15µ

13

SEROUT

O

TTL

12

DGNDREG

DV

CCREG

100k

12

XPOWER

SAVE

I

TTL

6

DGNDREG

DVCCREG

10µ

1k

6

VCC to 2/3VCC

2/3VCC to 1/3VCC

1/3VCC to GND

I

2

C 3V mode

I2C 5V mode

3-wire bus mode

Power save for all functions including

the control register block.

High level: Normal operation

Low level: Power save

Pin

No.

Symbol I/O

Typical

signal

Equivalent circuit Description

– 20 –

CXA3506R

14, 102,

122, 131,

138

4

5

DPGND

NC

NC

—

—

—

GND

—

—

This pin is connected to the die pad.

Connect to the specified GND in

Application Circuit.

Not used. Leave this pin open or

connect to GND.

Not used. Leave this pin open or

connect to GND.

DAC test output for control register

of amplifier block.

Current is output by open collector.

Normally connect to AVCC.

DAC TEST

OUT

O

5V

144

DGNDREG

DV

CCREG

144

Pin

No.

Symbol I/O

Typical

signal

Equivalent circuit Description

– 21 –

CXA3506R

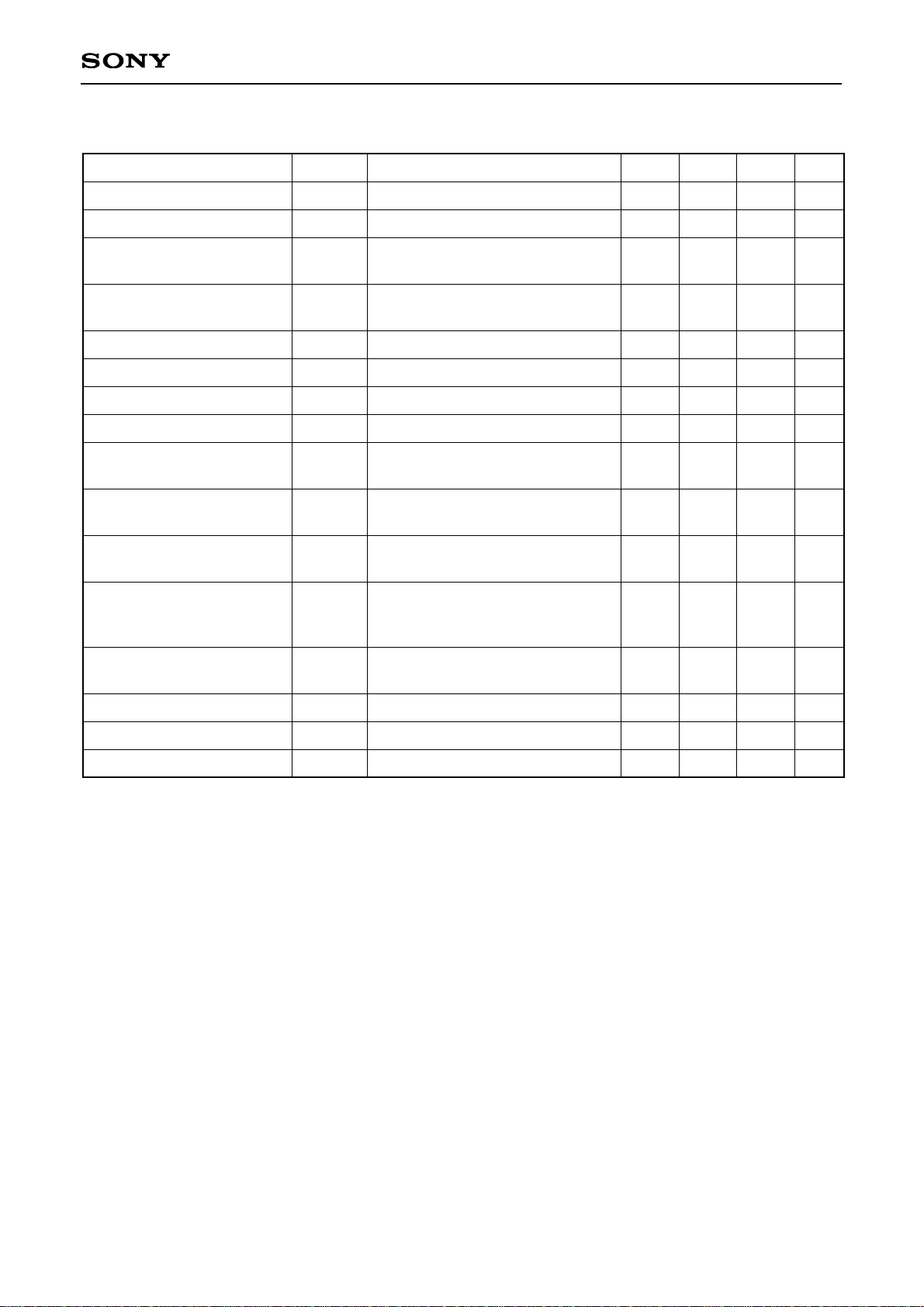

Electrical Characteristics (Ta = 25°C, AVCC, DVCC = 5V, AVCC3, DVCC3 = 3.3V)

Supply Current

Current during operating

5V current consumption

3.3V current consumption

Register control power save current

5V power save current

consumption

3.3V power save current

consumption

XPOWER SAVE pin control power save current

5V power save current

consumption

3.3V power save current

consumption

CLK = DC

CLK = DC

—

—

—

—

—

—

180

180

26

3.0

9.0

3.0

240

226

42

7.2

22

7.2

mA

mA

mA

mA

mA

mA

ICC5

ICC3

ICC5PS

ICC3PS

ICC5XPS

ICC3XPS

3-wire control bus (SDA, SCL, SENABLE)

High level input voltage

Low level input voltage

High level input current

Low level input current

Threshold voltage

High → Low

Threshold voltage

Low → High

Input capacitance

SCL clock frequency

XSENABLE setup time

XSENABLE hold time

XSENABLE

high level pulse width

SDA setup time

SDA hold time

SDA delay time

in WRITE/READ mode

in WRITE/READ mode

in WRITE/READ mode

in WRITE/READ mode

in WRITE/READ mode

in WRITE/READ mode

in READ mode

2.0

0

–2.0

–5.0

—

—

—

—

3

0

300

3

0

—

—

—

—

—

1.3

1.65

—

—

10

10

—

10

10

11

5.0

0.8

0

0

—

—

10

10

—

—

—

—

—

—

V

V

µA

µA

V

V

pF

MHz

ns

ns

ns

ns

ns

ns

V

IH

VIL

IIH

IIL

V

THHL1

V

THLH1

C

I

F

SCL1

T

ENS

T

ENH

T

ENPW

T

DS

T

DH

TD

Register

Item Symbol

Measurement conditions

Min. Typ. Max. Unit

Item Symbol

Measurement conditions

Min. Typ. Max. Unit

– 22 –

CXA3506R

I2C control bus (SDA, SCL)

High level input voltage

Low level input voltage

High level input current

Low level input current

Threshold voltage

High → Low

Threshold voltage

Low → High

High level input voltage

Low level input voltage

High level input current

Low level input current

Threshold voltage

High → Low

Threshold voltage

Low → High

SDA low level output voltage

Input capacitance

SCL clock frequency

Bus free-time

STOP → START

Hold time (resend)

Hold time in SCL clock

at Low state

Hold time in SCL clock

at High state

Setup time under resend

START condition

Data hold time

Data setup time

Rise time

Fall time

Setup time under STOP

condition

Capacitive load of each

bus line

I

OH = 3mA

START condition:

After this period, first clock is

generated.

2.3

0

–2.0

–5.0

—

—

2.0

0

–1.0

–5.0

—

—

0

—

0

4.7

4.0

4.7

4.0

4.7

0

250

—

—

4.0

—

—

—

—

—

1.6

1.95

—

—

—

—

1.3

1.65

0.15

—

50

5.0

5.0

5.0

5.0

5.0

5.0

5000

—

—

5.0

—

5.0

1.0

0

0

—

—

5.0

0.8

0

0

—

—

0.5

10

100

—

—

—

—

—

—

—

1000

300

—

400

V

V

µA

µA

V

V

V

V

µA

µA

V

V

V

pF

kHz

µs

µs

µs

µs

µs

µs

ns

ns

ns

µs

pF

VIH

VIL

IIH

IIL

VTHHL2

VTHLH2

VIH

VIL

IIH

IIL

VTHHL3

VTHLH3

VOL

CI

FSCL2

TBUF

THD;STA

TLOW

THIGH

TSU;STA

THD;DAT

TSU;DAT

TR

TF

TSU;STO

Cb

Register (Cont.)

I

2

C (High) modeI

2

C (Low) mode

Item Symbol

Measurement conditions

Min. Typ. Max. Unit

– 23 –

CXA3506R

Brightness characteristics

Brightness level H

(ADC OUT)

Brightness level L

Brightness level M

Brightness level H

Brightness level

Low side variable range

Brightness level

High side variable range

Clamp characteristics

Cb, Cr clamp level M

(ADC OUT)

Cb, Cr clamp level L

Cb, Cr clamp level M

Cb, Cr clamp level H

Cb, Cr clamp level

Low side variable range

Cb, Cr clamp level

High side variable range

Clamp pulse minimum width

Contrast characteristics

Main contrast control L

Main contrast control M

Main contrast control H

Sub contrast control L

Sub Brightness G, B, R = 255

ADC output conversion level

Sub Brightness G, B, R = 0

G, B, R OUT pin voltage

Sub Brightness G, B, R = 128

G, B, R OUT pin voltage

Sub Brightness G, B, R = 255

G, B, R OUT pin voltage

V

BRL – VBRM

VBRH – VBRM

Cb, Cr offset = 32

ADC output conversion level

Cb, Cr offset = 0

B, R OUT pin voltage

Cb, Cr offset = 32

B, R OUT pin voltage

Cb, Cr offset = 63

B, R OUT pin voltage

VCLL – VCLM

VCLH – VCLM

Main Contrast = 0

Sub Contrast = 128

Vin = 1.2Vp-p

RGB/YUV mode, G, B, R OUT

Main Contrast = 128

Sub Contrast = 128

Vin = 0.6Vp-p

RGB/YUV mode, G, B, R OUT

Main Contrast = 255

Sub Contrast = 128

Vin = 0.45Vp-p

RGB/YUV mode, G, B, R OUT

Main Contrast = 128

Sub Contrast = 0

Vin = 0.85Vp-p

RGB/YUV mode, G, B, R OUT

53

1.388

1.63

1.86

—

—

120

1.94

1.99

2.03

—

—

200

0.62

1.23

1.79

0.96

61

1.588

1.83

2.06

–242

230

128

2.23

2.28

2.34

–60

60

—

0.78

1.53

2.24

1.2

69

1.788

2.03

2.26

—

—

136

2.46

2.51

2.58

—

—

—

0.94

1.84

2.69

1.44

LSB

V

V

V

mV

mV

LSB

V

V

V

mV

mV

ns

times

times

times

times

VBRHAD

VBRL

VBRM

VBRH

VCLMAD

VCLL

VCLM

VCLH

TWCLP

VMCL

VMCM

VMCH

VSCL

AMP

Item Symbol

Measurement conditions

Min. Typ. Max. Unit

– 24 –

CXA3506R

Sub contrast control H

Gain difference among

RGB

Frequency response

Cross talk characteristics

Cross talk between

channels

Cross talk among RGB

Main Contrast = 128

Sub Contrast = 255

Vin = 0.55Vp-p

RGB/YUV mode, G, B, R OUT

Main Contrast = 128

Sub Contrast = 128

Vin = 0.6Vp-p

RGB/YUV mode, G, B, R OUT

Main Contrast = 128

Sub Contrast = 128

Vin = 0.6Vp-p

RGB/YUV mode, G, B, R OUT

Main Contrast = 128

Sub Contrast = 128

fin = 100MHz, Vin = 0.6Vp-p

Main Contrast = 128

Sub Contrast = 128

fin = 100MHz, Vin = 0.6Vp-p

1.48

–8

—

—

—

1.85

0

220

–35

–30

2.22

8

—

—

—

times

%

MHz

dB

dB

V

SCH

∆Gain

FC – 3dB

CTC

CTB

AMP (Cont.)

SYNC SEP input characteristics

SYNC TIP input minimum

amplitude

SYNC TIP input minimum

duty

SYNC SEP

threshold voltage

SYNC SEP

hysteresis voltage

SYNC SEP V

TH = 1000

SYNC SEP VHYS = 10

SYNC SEP VTH = 1000

SYNC SEP VHYS = 10

0.2

5

116

36

—

—

145

45

—

—

174

54

Vp-p

%

mV

mV

V

SYN

DSYN

VTH

VHYS

SYNCSEP

Item Symbol

Measurement conditions

Min. Typ. Max. Unit

Item Symbol

Measurement conditions

Min. Typ. Max. Unit

– 25 –

CXA3506R

Hold characteristics

RC1 pin leak current

SYNC signal input characteristics

SYNC signal input

frequency range

VCO characteristics

Clock frequency

Clock frequency

Clock frequency

Clock frequency

VCO lock range

VCO gain 1

VCO gain 2

VCO gain 3

VCO gain 4

Jitter characteristics

SYNC input signal –

Clock output jitter

(NTSC)

SYNC input signal –

Clock output jitter

(VGA)

SYNC input signal –

Clock output jitter

(SVGA)

SYNC input signal –

Clock output jitter

(XGA)

Delay sync –

Clock output jitter

VCO frequency divider DIV = 1/1

VCO frequency divider DIV = 1/2

VCO frequency divider DIV = 1/4

VCO frequency divider DIV = 1/8

VCO frequency divider DIV = 1/1

VCO frequency divider DIV = 1/2

VCO frequency divider DIV = 1/4

VCO frequency divider DIV = 1/8

Triggered at SYNC

Fsync = 15.73kHz

Fclk = 12.27MHz

N = 780

Triggered at SYNC

Fsync = 31.47kHz

Fclk = 25.18MHz

N = 800

Triggered at SYNC

Fsync = 48.08kHz

Fclk = 50.00MHz

N = 1040

Triggered at SYNC

Fsync = 56.48kHz

Fclk = 75.00MHz

N = 1328

Triggered at DSYNC

—

10

80

40

14

5

2.0

300

150

75

37.5

2.4

1.6

1.3

0.9

—

—

—

—

—

—

—

—

—

—

—

—

2.7

1.8

1.4

1.0

—

1.0

100

120

80

40

14

4.5

500

250

125

62.5

3

2.0

1.5

1.1

0.1

nA

kHz

MHz

MHz

MHz

MHz

V

Mrad/sv

Mrad/sv

Mrad/sv

Mrad/sv

ns

ns

ns

ns

ns

Ileak

FSYNC

FCLK1

FCLK2

FCLK3

FCLK4

Vlock

KVCO1

KVCO2

KVCO3

KVCO4

Tj1p-p

Tj2p-p

Tj3p-p

Tj4p-p

Tj7p-p

PLL

Item Symbol

Measurement conditions

Min. Typ. Max. Unit

– 26 –

CXA3506R

Resolution

DC characteristics

Integral linearity error

Differential linearity error

Reference voltage

Top reference voltage

Bottom reference voltage

Input dynamic range

AC characteristics

Maximum conversion

frequency of Straight Data

out Mode

Maximum conversion

frequency of DMUX

Parallel Data out Mode

Maximum conversion

frequency of DMUX

Interleaved Data out Mode

Maximum conversion

frequency of 4:2:2 Data

out D2 Mode

Maximum conversion

frequency of 4:2:2 Data

out Special Mode

AVccAD3 as a reference

AVccAD3 as a reference

VRT – VRB

—

—

—

–0.3

–1.3

0.9

100

120

120

100

100

8

1.0

0.4

–0.4

–1.4

1.0

—

—

—

—

—

—

—

0.7

–0.6

–1.6

1.1

—

—

—

—

—

bit

LSB

LSB

V

V

V

MSPS

MSPS

MSPS

MSPS

MSPS

ILE

DLE

VRT

VRB

VTB

Fc

Fc

Fc

Fc

Fc

ADC

Item Symbol

Measurement conditions

Min. Typ. Max. Unit

– 27 –

CXA3506R

Digital input (PECL)

Digital input voltage: H

Digital input voltage: L

Digital input current: H

Digital input current: L

Digital input (TTL)

Digital input voltage: H

Digital input voltage: L

Threshold voltage

Digital input current: H

Digital input current: L

Digital output (TTL)

Digital output voltage: H

Digital output voltage: L

DVccPLL as a reference

DVccPLL as a reference

V

IH1 = DVCCPLL – 0.8V

VIL1 = DVCCPLL – 1.6V

VIH = 3.5V

VIL = 0.2V

IOH = –2mA

IOH = –2mA

IOH = –2mA

IOH = –2mA

IOL = 1mA

–1.15

—

–100

–200

2.0

—

—

–10

–20

2.4

2.3

2.05

1.85

—

—

—

—

—

—

—

1.5

—

—

2.95

2.7

2.45

2.2

0.2

—

–1.5

100

0

—

0.8

—

–5

0

3.3

3.0

2.75

2.5

0.5

V

V

µA

µA

V

V

V

µA

µA

V

V

V

V

V

VIH1

VIL1

IIH1

IIL1

VIH2

VIL2

VTH

IIH2

IIL2

VOH1

VOH2

VOH3

VOH4

VOL

I/O

Item Symbol

Measurement conditions

Min. Typ. Max. Unit

– 28 –

CXA3506R

Clock output rise time

Clock output fall time

Delay sync output

rise time

Delay sync output

fall time

Data output rise time

Data output fall time

HOLD signal setup time

HOLD signal hold time

Delay sync delay time

coarse delay

Delay sync delay time

fine delay

Clock output delay from

SYNC input signal

Delay time between clock

output and DSYNC/DIVOUT

signal

DIVOUT signal output

delay time

Clock – 1/2 clock

1/2 clock – Data

Clock – Data

0.8 to 2.0V (CLK, 1/2CLK)

2.0 to 0.8V (CLK, 1/2CLK)

0.8 to 2.0V

(DSYNC, DIVOUT, SOGOUT)

2.0 to 0.8V

(DSYNC, DIVOUT, SOGOUT)

0.8 to 2.0V

2.0 to 0.8V

CL = 9pF

CL = 9pF

Difference between delay sync

signal and DIVOUT signal

0.8

1.0

0.8

1.0

0.9

0.9

20

20

3

1/32

6.0

0.8

4

0.9

2.3

2.2

1.4

1.5

1.4

1.5

1.2

1.2

—

—

—

—

7.0

1.0

—

1.2

2.6

2.8

2.3

2.8

2.3

2.8

2.0

2.0

—

—

6

64/32

8.0

1.3

5

1.6

3.2

3.8

ns

ns

ns

ns

ns

ns

ns

ns

CLK

CLK

ns

ns

CLK

ns

ns

ns

T

R_CLK

TF_CLK

T

R_DSYNC

TF_DSYNC

TR_DATA

TF_DATA

Ths

Thh

Td_1

Td_2

Td_3

Td_4

Td_5

Td_6

Td_7

Td_8

Item Symbol

Measurement conditions

Min. Typ. Max. Unit

Timing Characteristics

– 29 –

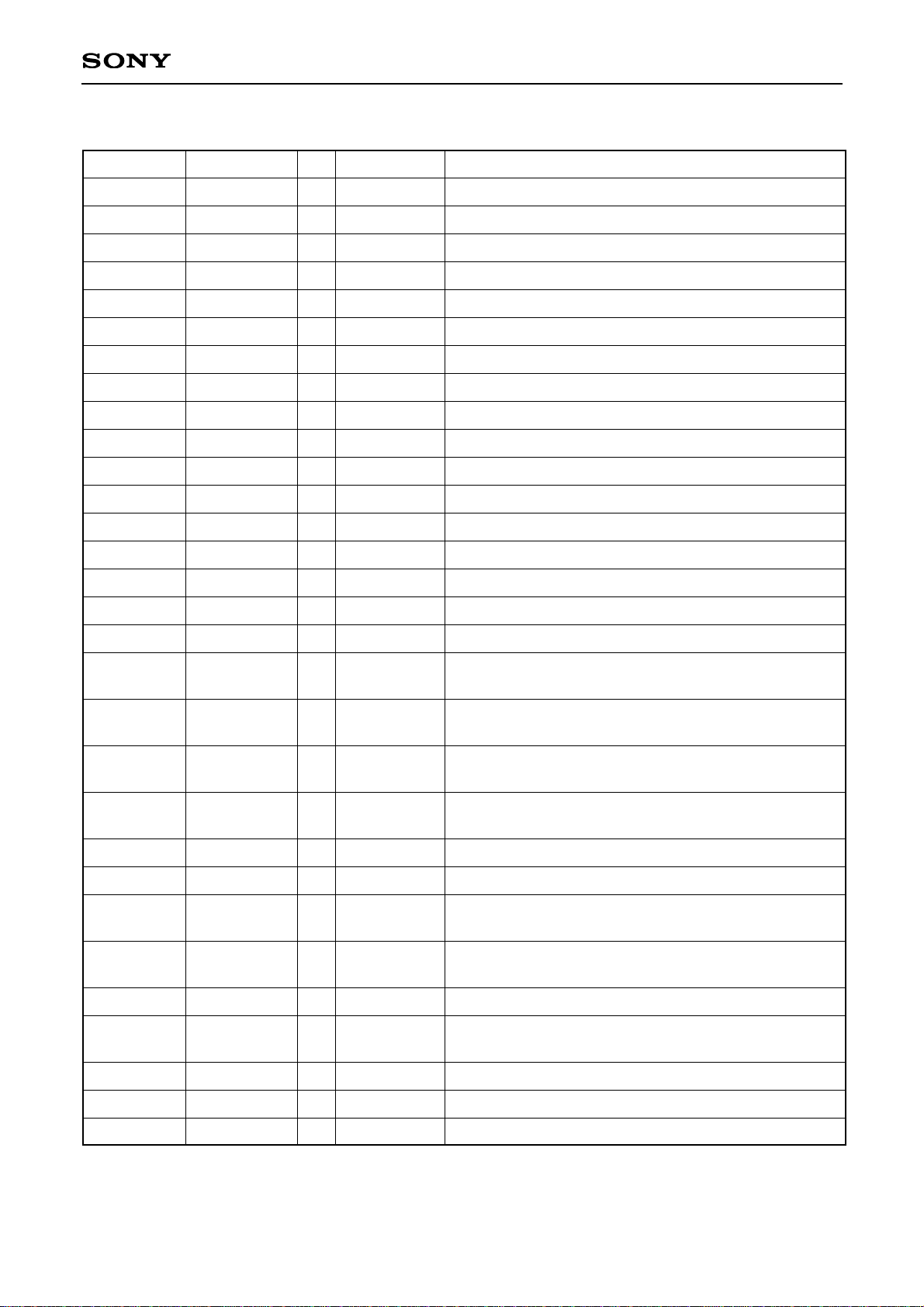

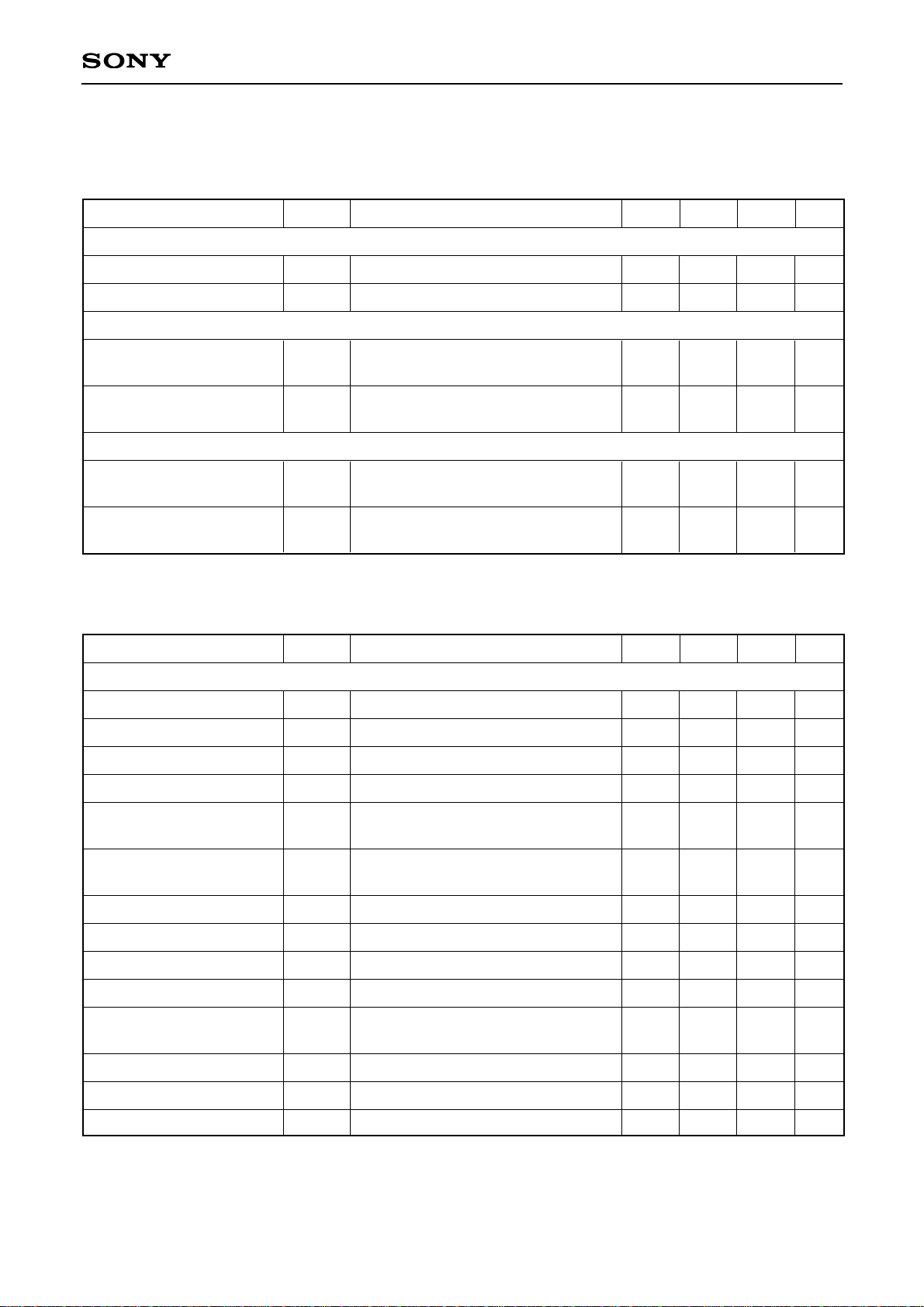

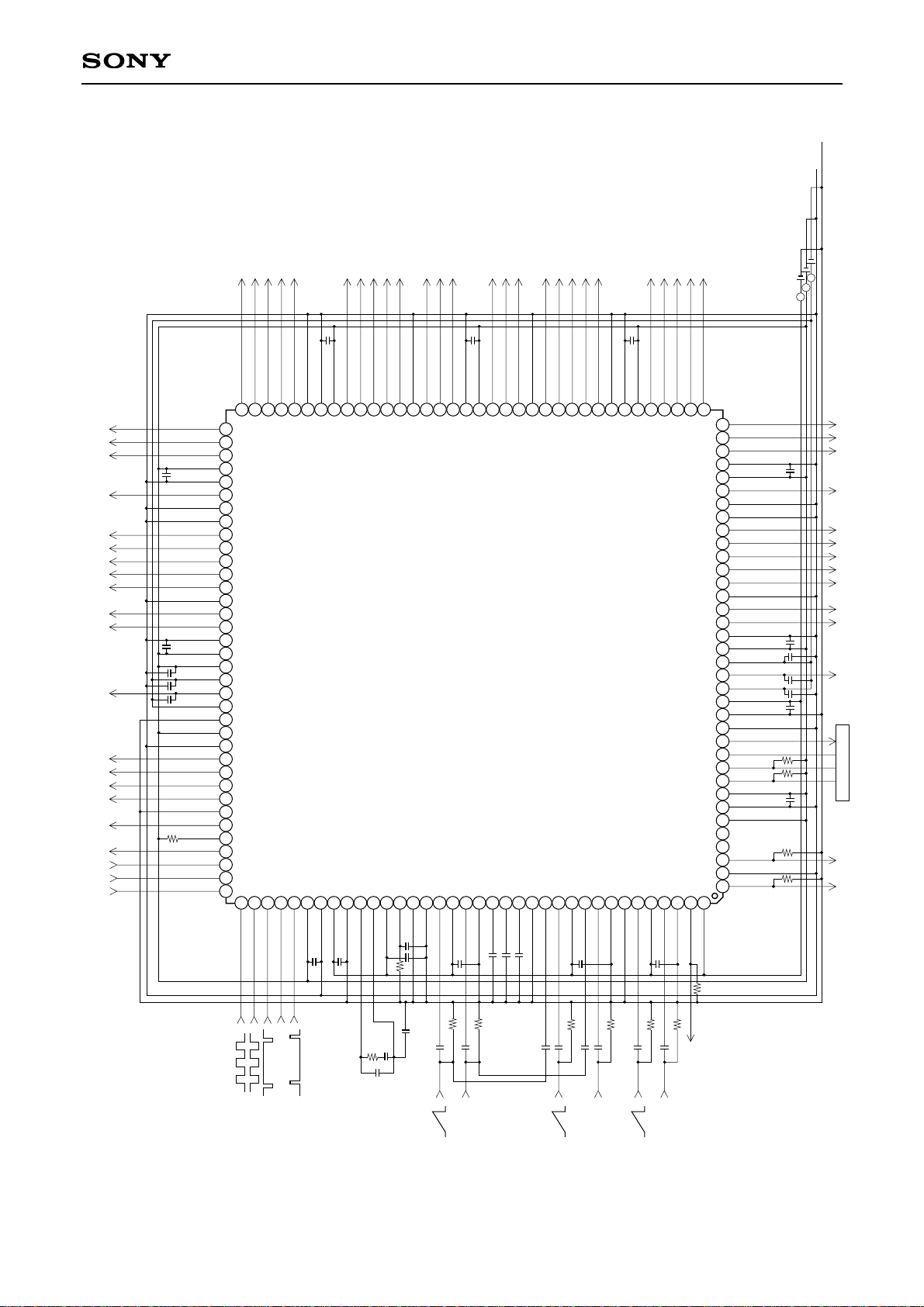

CXA3506R

Electrical Characteristics Measurement Circuit

(3-wire Control)

0.1µ

75

820

0.1µ

75

0.1µ

75

0.1µ

75

0.1µ750.1µ

1µ

100p

0.33µ

3.3k

3k

330p

75

5k

0.1µ

0.1µ

4.7k

4.7k

820

820

AVCC5V

DV

CC5V

3.3V

DGND

AGND

1µ

ANALOG

SIGNAL

ANALOG

SIGNAL

ANALOG

SIGNAL

BUS CONTROLER

37

A

A

A

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74757677

78

79

80

81

828384

85

868788899091

92

93

949596979899

100101

102

103104105106107108

133

134

135

136

137

138

139

140

141

1 2 3 4

121

122

123

124

125

126

127

128

129

130

131

132

142

143

144

110

109

111

112

113

114

115

116

117

118

119

120

5 6 7 8 9 10 12 13 14 15 16 17 18 19 20 22 23 24 25 26 27 28 29 30 32 33 34 35 3611 21 31

B/CbOUT

ADDRESS

R/CrOUT

NC

NC

XPOWER SAVE

DGNDREG

DVCCREG

SDA

SCL

XSENABLE

SEROUT

3WIRE/I

2

C

DPGND

AVCCADREF

AVCCAD3

VRT

DVCCAD3

DVCCADTTL

DGNDADTTL

RA0

RA1

DGNDAD3

RA2

RA3

RA4

RA5

RA6

AGNDAD3

DGNDAD3

RA7

DVCCADTTL

DGNDADTTL

RB0

RB1

RB2

GA4

GA3

GA2

GA1

GA0

DGNDADTTL

DGNDAD3

DVCCADTTL

BB7

BB6

BB5

BB4

BB3

GNDAD3

BB2

BB1

BB0

DGNDADTTL

DVCCADTTL

BA7

BA6

BA5

DGNDAD3

BA4

BA3

BA2

BA1

BA0

DGNDADTTL

DGNDAD3

DVCCADTTL

RB7

RB6

RB5

RB4

RB3

EVEN/ODD

XTLOAD

HOLD

SOGOUT

UNLOCK

DSYNC/DIVOUT

DPGND

1/2CLK

1/2XCLK

CLK

XCLK

DGNDPLLTTL

DVCCPLLTTL

AGNDADREF

AVCCAD3

VRB

DVCCAD3

DVCCAD

DVCCADTTL

DGNDADTTL

GB7

GB6

DGNDAD3

GB5

GB4

GB3

GB2

GB1

AGNDAD3

DGNDAD3

GB0

DGNDADTTL

DVCCADTTL

GA7

GA6

GA5

XCLKIN

CLKIN

SYNCIN1

SYNCIN2

CLPIN

DVCCPLL

DGNDPLL

AVCCVCO

AGNDVCO

RC1

RC2

AVCCIR

IREF

DPGND

AGNDIR

G/YIN1

AVCCAMPG

G/YIN2

AGNDAMPG

G/YCLP

B/CbCLP

R/CrCLP

DPGND

SOGIN1

B/CbIN1

AVCCAMPB

SOGIN2

B/CbIN2

AGNDAMPB

DPGND

R/CrIN1

AVCCAMPR

R/CrIN2

AGNDAMPR

G/YOUT

DACTESTOUT

CLAMP

PULSE

HSYNC

EXT CLK

EXT XCLK

– 30 –

CXA3506R

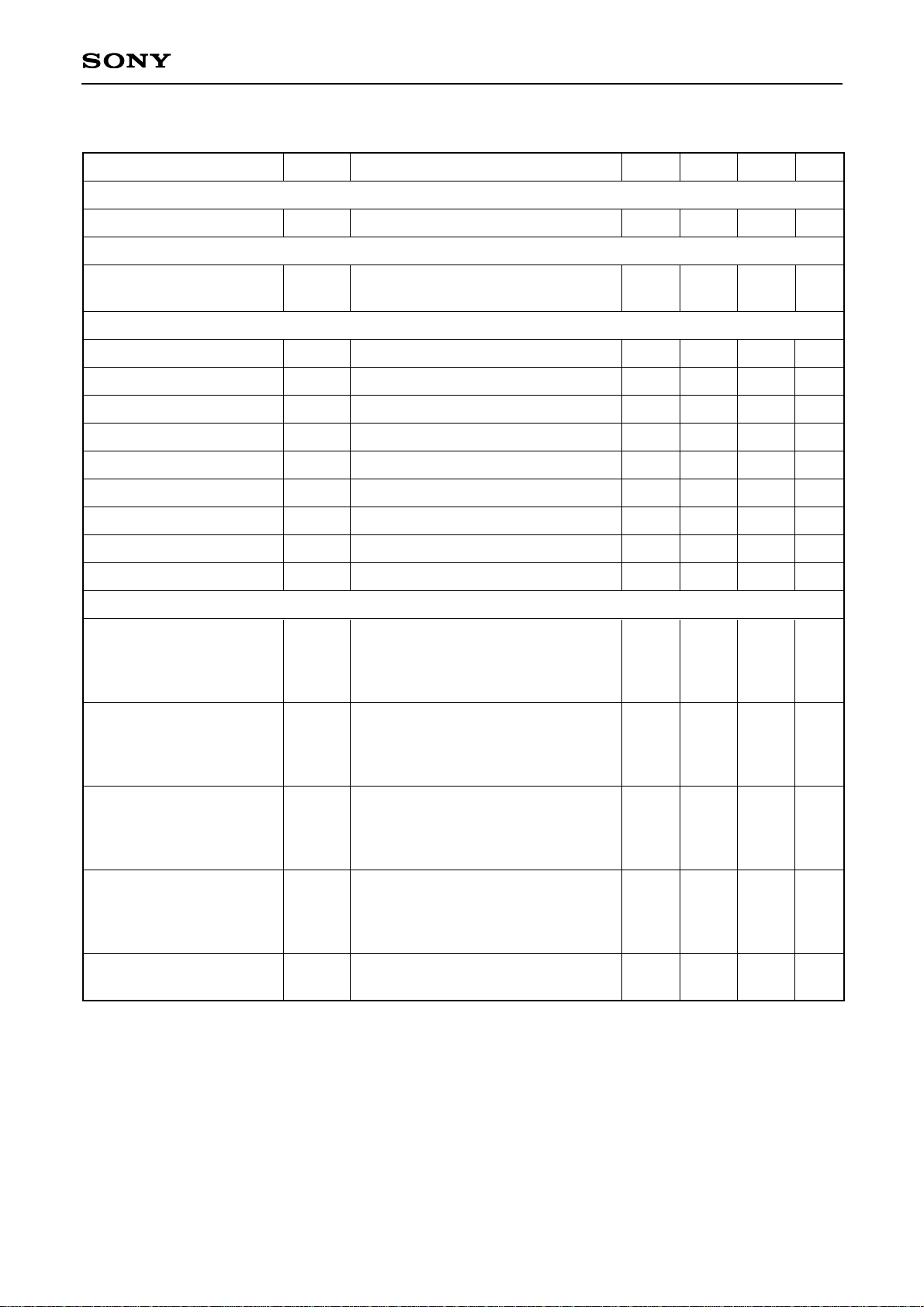

Control Register Functions Table

Block

Function

Feedback programmable

counter control

VCO frequency divider

control

Delay control

(lower order)

Delay control

(higher order)

Charge pump current

control

DIVOUT signal pulse

width control

DIVOUT signal delay

control

Delay sync output polarity

control

Hold input polarity control

12

2

6

2

3

2

1

1

1

0

1

1

2

2

3

3

3

4

4

m4

O

m3

O

m2

O

O

O

m1

O

O

O

m0

m8

O

O

n2

m7

O

O

n1

m6

O

O

O

n0

m5

O

O

O

VCO DIV

DIV1, 2, 4, 8

FINE DELAY

COARSE

DELAY

Charge.Pump

DIVOUT WIDTH

DIVOUT DELAY

DSYNC POL

HOLD POL

Frequency division ratio =

(m + 1) × 8 + n

00: 1/1

01: 1/2

10: 1/4

11: 1/8

000000: 1/32CLK

111111: 64/32CLK

00: 3CLK

01: 4CLK

10: 5CLK

11: 6CLK

000: 100µA

001: 200µA

010: 300µA

011: 400µA

100: 500µA

101: 600µA

110: 700µA

111: 800µA

00: 1CLK

01: 2CLK

10: 4CLK

11: 8CLK

0: 4CLK

1: 5CLK

0: NEGATIVE

1: POSITIVE

0: NEGATIVE

1: POSITIVE

bit

Register

No.

PLL

PLL

PLL

PLL

PLL

PLL

PLL

PLL

PLL

Data

D7 D6 D5 D4 D3 D2 D1 D0

Register Name

Control Range (typ.)

Loading...

Loading...