Sony CXA3086Q Datasheet

6-bit 140MSPS Flash A/D Converter

Description

The CXA3086Q is an 6-bit high-speed flash A/D

converter capable of digitizing analog signals at the

maximum rate of 140MSPS. ECL, PECL or TTL can

be selected as the digital input level in accordance

with the application. The TTL digital output level

allows 1:2 demultiplexed output.

Features

• Differential linearity error: ±0.2LSB or less

• Integral linearity error: ±0.2LSB or less

• High-speed operation with a maximum conversion

rate of 140MSPS

• Low input capacitance: 7pF

• Wide analog input bandwidth: 200MHz

• Low power consumption: 358mW

• Low error rate

• Excellent temperature characteristics

• 1:2 demultiplexed output

• 1/2 frequency divided clock output

(with reset function)

• Compatible with ECL, PECL and TTL digital input levels

• Single +5V power supply operation available

• Surface mounting package

CXA3086Q

48 pin QFP (Plastic)

Structure

Bipolar silicon monolithic IC

Applications

• Magnetic recording (PRML)

• Communications (QPSK, QAM)

• LCDs

• Digital oscilloscopes

RESETN/T

RESET/E

9

10

27

28

CLK/T

2

CC

DV

29

2

CC

DV

DGND2

8

7

30

DGND2

P2D3

P2D4

P2D5 (MSB)

6

5

33

32

31

P1D2

P1D1

P1D0 (LSB)

P2D2

4

P1D3

3

34

P2D1

35

P1D4

DGND2

P2D0 (LSB)

2

48

47

46

45

44

43

42

41

40

39

38

37

36

DGND2

P1D5 (MSB)

DVCC2

DV

CC1

DGND1

N.C.

PS

CLKOUT

INV

SELECT

N.C.

DGND1

DVCC1

DV

CC2

Pin Configuration (Top View)

RESETN/E

12 1

11

13

DV

EE3

14

AGND

15

VRBS

16

V

RB

17

AVCC

18

N.C.

19

IN

V

20

AVCC

21

VRT

VRTS

22

23

AGND

DGND3

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

24

25

CLK/E

26

CLKN/E

– 1 –

E95619C77

CXA3086Q

Absolute Maximum Ratings (Ta = 25°C)

Unit

• Supply voltage AVCC, DVCC1, DVCC2 –0.5 to +7.0 V

DGND3 –0.5 to +7.0 V

DVEE3 –7.0 to +0.5 V

DGND3 – DVEE3 –0.5 to +7.0 V

• Analog input voltage VIN VRT – 2.7 to AVCC V

• Reference input voltage VRT 2.7 to AVCC V

VRB VIN – 2.7 to AVCC V

|VRT – VRB| 2.5 V

∗

• Digital input voltage ECL (∗∗∗/E

1

)DVEE3 to +0.5 V

PECL (∗∗∗/E) –0.5 to DGND3 V

TTL (∗∗∗/T, INV, PS) –0.5 to DVCC1V

other (SELECT) –0.5 to DVCC1V

VID∗2(|∗∗∗/E – ∗∗∗N/E|) 2.7 V

• Storage temperature Tstg –65 to +150 °C

• Allowable power dissipationPD 1.2 W

(when mounted on a glass fabric base epoxy board with 76mm x 114mm, 1.6mm thick)

Recommended Operating Conditions

With a single power supply With dual power supplies Unit

Min. Typ. Max. Min. Typ. Max.

• Supply voltage DVCC1, DVCC2, AVCC +4.75 +5.0 +5.25 +4.75 +5.0 +5.25 V

DGND1, DGND2, AGND –0.05 0 +0.05 –0.05 0 +0.05 V

DGND3 +4.75 +5.0 +5.25 –0.05 0 +0.05 V

DVEE3 –0.05 0 +0.05 –5.5 –5.0 –4.75 V

• Analog input voltage VIN VRB VRT VRB VRT V

• Reference input voltage VRT +2.9 +4.1 +2.9 +4.1 V

VRB +1.4 +2.6 +1.4 +2.6 V

|VRT – VRB| 1.5 2.1 1.5 2.1 V

• Digital input voltage ECL (∗∗∗/E) : VIH DGND3 – 1.05 DGND3 – 0.5 V

: VIL DGND3 – 3.2 DGND3 – 1.4 V

PECL (∗∗∗/E) : VIH DGND3 – 1.05 DGND3 – 0.5 V

: VIL DGND3 – 3.2 DGND3 – 1.4 V

TTL (∗∗∗/T, INV, PS): VIH 2.0 2.0 V

: VIL 0.8 0.8 V

other (SELECT) : VIH DVCC1DVCC1V

: VIL DGND1 DGND1 V

VID∗2(|∗∗∗/E – ∗∗∗N/E|) 0.4 0.8 0.4 0.8 V

• Maximum conversion rate Fc (Straight mode) 100 100 MSPS

(DMUX mode) 140 140 MSPS

• Ambient temperature Ta –20 +75 –20 +75 °C

∗1

∗∗∗/E and ∗∗∗/T indicate CLK/E and CLK/T, etc. for the pin name.

∗2

VID: Input Voltage Differential

ECL and PECL switching level

VID

– 2 –

DGND3

VIH (max.)

IL

V

VTH (DGND3 – 1.2V)

V

IH

V

IL (min.)

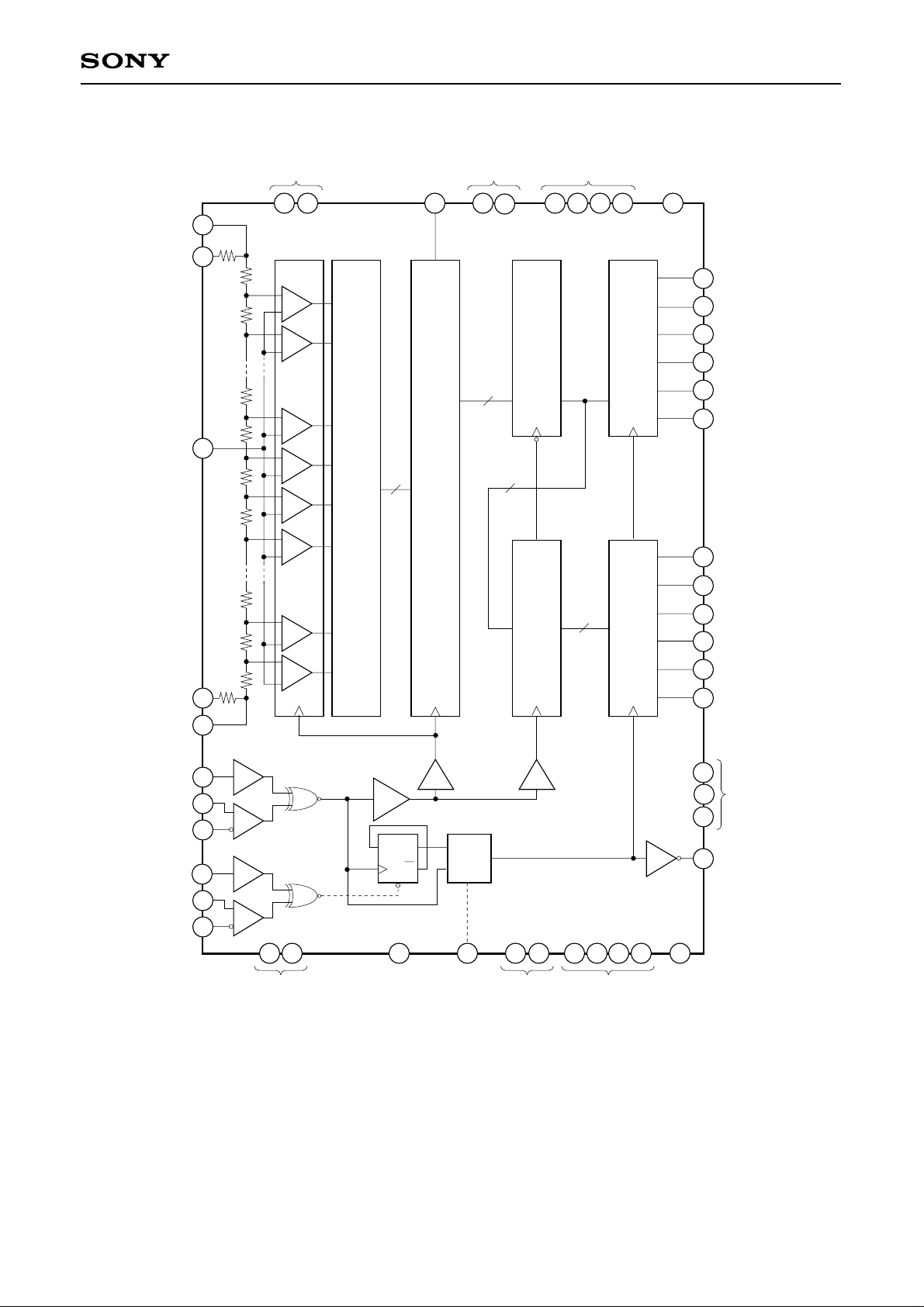

Block Diagram

CXA3086Q

VRTS

V

RT

VIN

VRB

VRBS

19

16

15

22

21

AVCC DVCC2

17

20

INV DGND3

42

DVCC1

38

47

37

9

28

48

24

r1

(MSB)

r

1

r

2

•

•

•

r

30

r

31

r

32

r

33

•

•

•

r

6bit

ENCODER

6bit

6bit LATCH

LATCHA

6bit

TTLOUT

6bit

62

r

r2

63

r

LATCHB

TTLOUT

35

34

33

32

31

30

7

6

5

4

3

2

P1D5

P1D4

P1D3

P1D2

P1D1

P1D0

(LSB)

(MSB)

P2D5

P2D4

P2D3

P2D2

P2D1

P2D0

(LSB)

CLK/T

CLK/E

CLKN/E

RESETN/T

RESETN/E

RESET/E

10

12

27

25

26

11

14

AGND

23

Delay

DQ

44

Q

Select

46

41

SELECTPS DVEE3

39

DGND1

1

DGND2

8

29

36

13

18

40

45

43

N.C.

CLKOUT

– 3 –

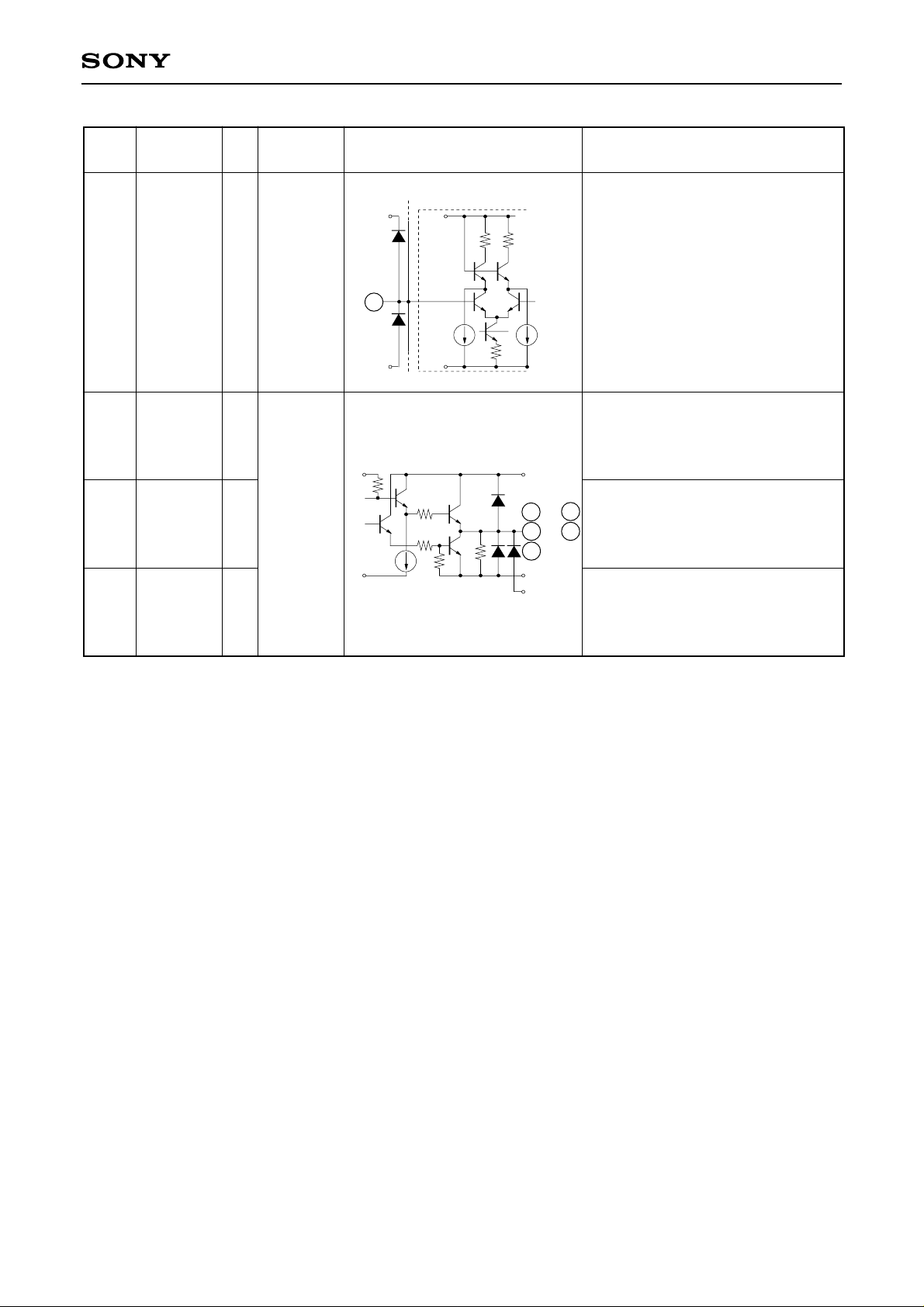

Pin Description and I/O Pin Equivalent Circuit

CXA3086Q

Pin

No.

14, 23

17, 20

1, 8,

29, 36,

39, 46

9, 28,

37, 38,

47, 48

24

Symbol

AGND

AVCC

DGND1

DGND2

DVCC1

DVCC2

DGND3

Standard

I/O

voltage level

GND

+5V

(typ.)

GND

+5V

(typ.)

+5V (typ.)

(With a

single

power

supply)

GND

(With dual

power

supplies)

Equivalent circuit Description

Analog ground.

Separated from the digital ground.

Analog power supply.

Separated from the digital power

supply.

Digital ground.

Digital power supply.

Digital power supply.

Ground for ECL input.

+5V for PECL and TTL input.

13

18, 40,

45

25

26

12

11

DVEE3

N.C.

CLK/E

CLKN/E

RESETN/E

RESET/E

GND

(With a

single

power

supply)

–5V (typ.)

(With dual

power

supplies)

I

I

ECL/

PECL

I

I

DGND3

12

11

DV

EE3

25

26

1.2V

r

r r

Digital power supply.

–5V for ECL input.

Ground for PECL and TTL input.

No connected pin.

Not connected with the internal

circuits.

Clock input.

CLK/E complementary input.

When left open, this pin goes to the

threshold potential.

Only CLK/E can be used for

r

operation, but complementary input

is recommended to attain fast and

stable operation.

Reset input.

When the input is set to low level,

the built-in CLK frequency divider

circuit can be reset.

RESETN/E complementary input.

When left open, this pin goes to the

threshold voltage. Only RESETN/E

can be used for operation.

– 4 –

CXA3086Q

Pin

No.

Symbol I/O

27 CLK/T

10

RESETN/T

INV

42

44

PS

Standard

voltage level

I

TTL

I

I

TTL

I

Equivalent circuit Description

DVCC1

27

10

DGND1

DVEE3

r/2

1.5V

r

Clock input.

Reset input.

When left open, this input goes to

high level. When the input is set to

low level, the built-in CLK frequency

divider circuit can be reset.

Data output polarity inversion input.

DVCC1

When left open, this input goes to

high level.

(See Table 1. I/O Correspondence

Table.)

Power saving input.

42

44

When the input is set to low level,

the power saving mode is set.

In this time the all TTL outputs go

DGND1

DVEE3

into the high-impedance state.

Normally, set to high level or left

open.

SELECT

41

VRTS

22

21 VRT

VRB

16

15

VRBS

O

I

I

O

Vcc

or

GND

+4.0V

(typ.)

VRTS

+r1 x Iref

VRBS

–r2 x Iref

+2.0V

(typ.)

DVCC1

41

DGND1

DVEE3

22

21

16

15

Data output mode selection.

(See Table 2. Operating Mode

Table.)

Reference voltage sense.

1

r

r

Comparator 1

r

r

Comparator 2

r

r

Comparator 62

r

r

Comparator 63

r

2

r

By-pass to AGND with a 0.1µF chip

capacitor.

Top reference voltage.

By-pass to AGND with a 1µF tantal

capacitor and a 0.1µF chip

capacitor.

Bottom reference voltage.

By-pass to AGND with a 1µF tantal

capacitor and a 0.1µF chip

capacitor.

Reference voltage sense.

By-pass to AGND with a 0.1µF chip

capacitor.

– 5 –

CXA3086Q

Pin

No.

Symbol I/O

19 VIN

P1D0

30

to

35

2

to

7

to

P1D5

P2D0

to

P2D5

43 CLKOUT

Standard

voltage level

I

O

O

O

VRT

to

VRB

TTL

AVCC

19

DVEE3

DVCC1

DGND1

Equivalent circuit Description

Comparator

AVCC

Analog input.

Vref

AGND

Port 1 side data output.

DVCC2

7

to

100k

2

30

43

DGND2

DVEE3

Port 2 side data output.

to

35

Clock output.

(See Table 2. Operating Mode Table.)

– 6 –

Electrical Characteristics

(DVCC1, 2, AVCC, DGND3 = +5V, DGND1, 2, AGND, DVEE3 = 0V, VRT = 4V, VRB = 2V, Ta = 25°C)

Item Symbol Min. Typ. Max. UnitConditions

CXA3086Q

Resolution

DC characteristics

Integral linearity error

Differential linearity error

Analog input

Analog input capacitance

Analog input resistance

Analog input current

Reference input

Reference resistance

Reference current

Residual resistance r1

Digital input (ECL, PECL)

Digital input voltage: High

: Low

Threshold voltage

Digital input current: High

: Low

Digital input capacitance

Digital input (TTL)

Digital input voltage: High

: Low

Threshold voltage

Digital input current: High

: Low

Digital input capacitance

6

EIL

EDL

CIN

RIN

IIN

∗3

Rref

∗4

Iref

r1

r2

r2

VIH

VIL

VTH

IIH

IIL

VIN = 2Vp-p, Fc = 5MSPS

VIN = +3.0V + 0.07Vrms

VIH = DGND3 – 0.8V

VIL = DGND3 – 1.6V

16

0

160

6.5

3.0

3.0

DGND3 – 1.05

DGND3 – 3.2

DGND3 – 1.2

–50

–75

7

225

9.0

4.2

4.2

±0.2

±0.2

150

125

308

12.5

5.7

5.7

DGND3 – 0.5

DGND3 – 1.4

+50

0

5

VIH

VIL

VTH

IIH

IIL

VIH = 3.5V

VIL = 0.2V

2.0

–50

–500

0.8

1.5

0

0

5

bits

LSB

LSB

pF

kΩ

µA

Ω

mA

Ω

Ω

V

V

V

µA

µA

pF

V

V

V

µA

µA

pF

Digital output (TTL)

Digital output voltage

Leak current during output off

: High

: Low

VOH

VOL

IOZ

IOH = –2mA

IOL = 1mA

Power saving mode

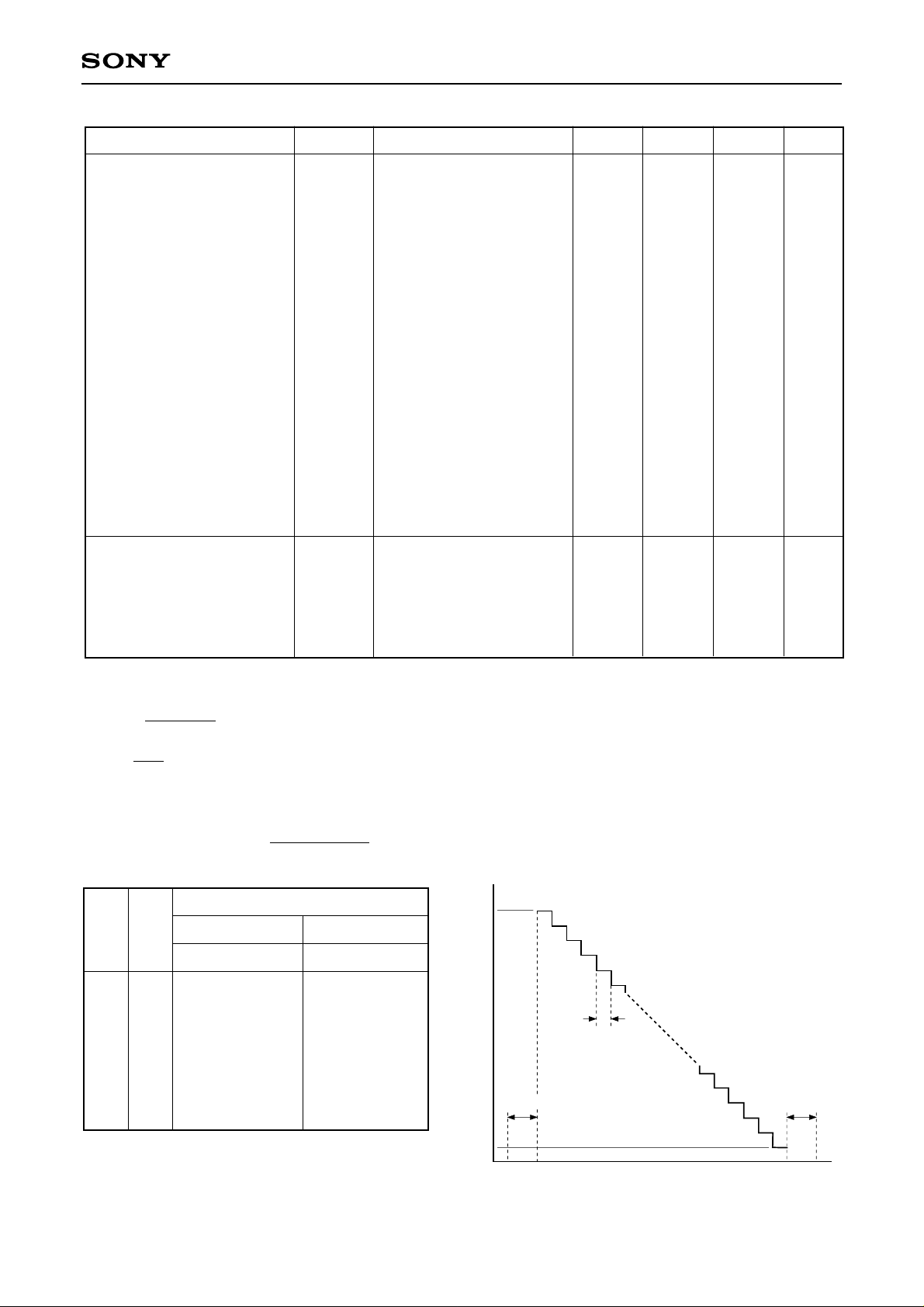

Switching characteristics

Maximum conversion rate

Aperture jitter

Sampling delay

Clock high pulse width

Clock low pulse width

RESET Signal setup time

RESET Signal hold time

CLKOUT output delay

Data output delay

Output rise time

Output fall time

These characteristics are for PECL input, unless otherwise specified.

∗

Fc

Taj

Tds

Tpw1

Tpw0

T_rs

T_rh

Td_clk

Tdo1

Tdo2

Tr

Tf

DMUX mode

CLK

CLK

RESETN – CLK

RESETN – CLK

(CL = 5pF)

DMUX mode (CL = 5pF)

(CL = 5pF)

0.8 to 2.0V (CL = 5pF)

0.8 to 2.0V (CL = 5pF)

2.4

–15

140

3

2.9

2.9

3.5

0

4.5

∗5

T

6.5

10

4.5

7

T + 1

8

2

2

0.5

70

6

8

T + 2

10

V

V

µA

MSPS

ps

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

– 7 –

Item Symbol Min. Typ. Max. UnitConditions

Dynamic characteristics

Input bandwidth

S/N ratio

Error rate

VIN = 2Vp-p, –3dB

Fc = 140MSPS,

fin = 1kHz Fs

{

DMUX mode

Fc = 140MSPS,

fin = 34.999MHz Fs

{

DMUX mode

Fc = 140MSPS,

fin = 1kHz Fs

DMUX mode

{

Error > 4LSB

Fc = 140MSPS,

fin = 34.999MHz Fs

DMUX mode

{

Error > 4LSB

Fc = 100MSPS,

fin = 24.999MHz Fs

straight mode

{

Error > 4LSB

200

37.0

34.5

10

10

10

–12

–9

–9

CXA3086Q

MHz

dB

dB

∗6

TPS

TPS

TSP

Power supply

Supply current

Supply current

Power consumption

Supply current

Power consumption

∗3

Rref: Resistance value between VRT and VRB

∗4

∗5

∗6

∗7

VIN

VRTS

VRBS

VRT – VRB

Iref =

T =

TPS: Times Per Sample

Pd = (ICC + IEE) · VCC +

Rref

1

Fc

Step

D5 D0 D5 D0

63

1 1 1 1 1 1

62

1 1 1 1 1 0

:

32

1 0 0 0 0 0

31

0 1 1 1 1 1

:

1

0 0 0 0 0 1

0

0 0 0 0 0 0

Table 1. I/O Correspondence Table

1

:

:

ICC

IEE

∗7

Pd

ICC + IEE

Pd

(VRT – VRB)

Rref

INV

0 0 0 0 0 0

0 0 0 0 0 1

0 1 1 1 1 1

1 0 0 0 0 0

1 1 1 1 1 0

1 1 1 1 1 1

Power saving mode

Power saving mode

2

0

:

:

Step

63

62

61

60

59

58

·

·

·

·

·

·

·

5

4

3

2

1

0

54.0

0.4

290

2.0

28

1LSB

r1 × Iref

V

RTSVRT VRBS VRB

67.5

VIN

0.6

360

90

0.8

470

8.0

58

mW

mW

r

2 × Iref

mA

mA

mA

– 8 –

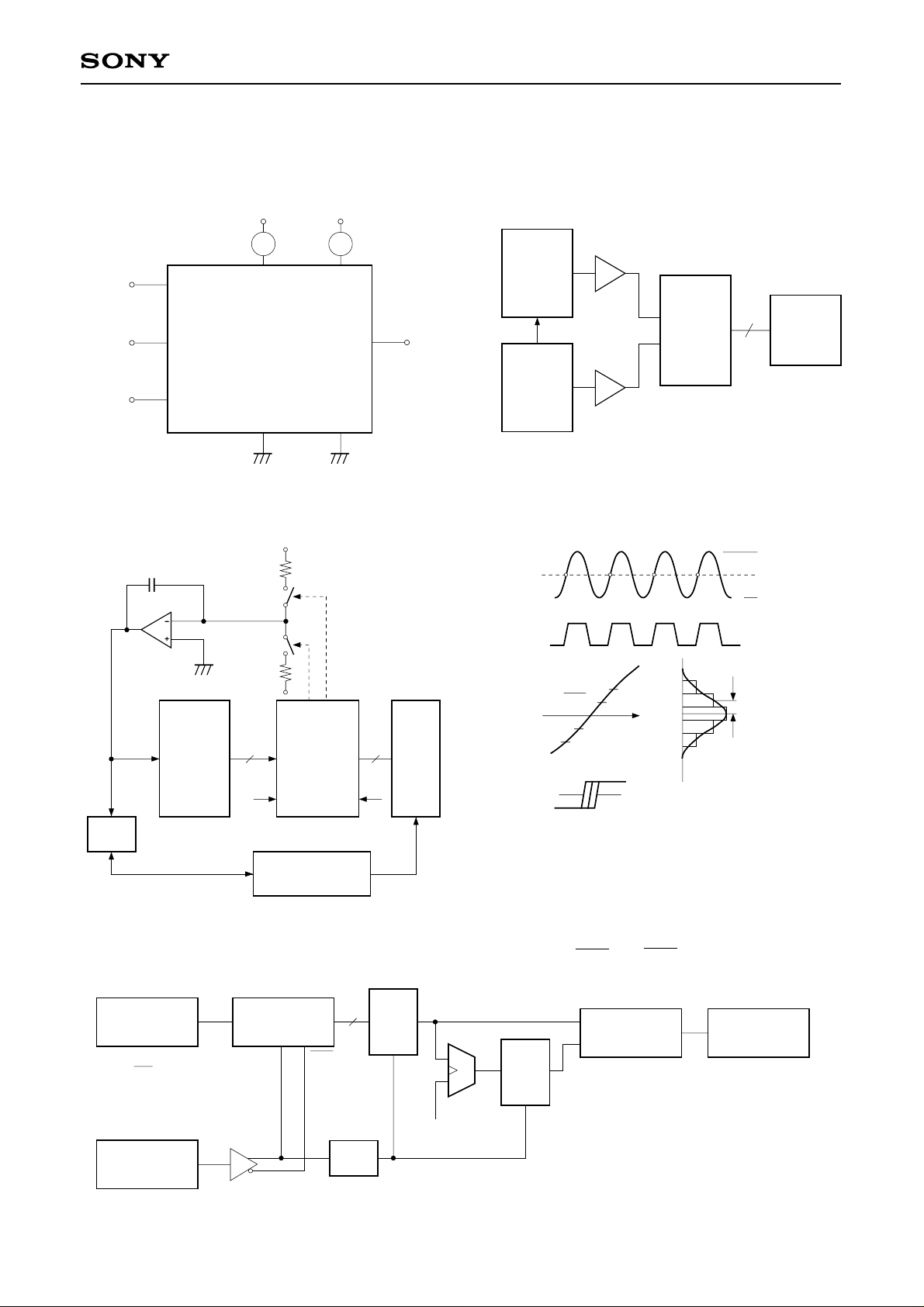

Electrical Characteristics Measurement Circuit

Current Consumption Measurement Circuit

CXA3086Q

Sampling Delay Measurement Circuit

Aperture Jitter Measurement Circuit

5V 5V

A A

4V

1.95V

2V

VRT

VIN

VRB

Icc

AVCC

DVCC1

DVCC2

DGND2

DGND1

AGND

DGND3

CLK/E

EE3

DV

I

EE

5MHz PECL

Integral Linearity Error Measurement Circuit

Differential Linearity Error Measurement Circuit

+V

S2

S1: ON when A < B

S1

S2: ON when A > B

100MHz

Amp

OSC1

φ: Variable

V

fr

OSC2

100MHz

IN

CXA3086Q

CLK

ECL

Buffer

6

Aperture Jitter Measurement Method

VIN

CLK

Logic

Analizer

1024

samples

VRT

VRB

–V

A < B A > B

Comparator

IN

DVM

V

CXA3086Q

6 6

A6

to

A1

A0

Controller

Error Rate Measurement Circuit

Signal

Source

C

F

– 1kHz

4

2Vp-p Sin Wave

VIN

CXA3086Q

CLK CLK

B6

B1

B0

∆υ

∆ t

IN

V

“1”“0”

Latch

Buffer

4LSB

00···0

to

11···0

CLK

Where σ (LSB) is the deviation of the output codes when

the largest slew rate point is sampled at the clock which

has exactly the same frequency as the analog input

signal, the aperture jitter Taj is:

Taj = σ/ = σ/ ( )

+

Latch

∆υ

∆t

A

B

Comparator

A > B

to

6

33

32

31

30

29

Sampling timing fluctuation

(= aperture jitter)

64

× 2πf

2

σ (LSB)

Pulse

Counter

Signal

Source

F

C

1/8

– 9 –

Loading...

Loading...