Sony CXA3067M Datasheet

—1—

E97657A89-TE

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

Absolute Maximum Ratings (Ta=25 °C)

• Supply voltage VCC –0.3 to +5.5 V

• Storage temperature Tstg –55 to +150 °C

Operating Conditions

• Supply voltage VCC 4.75 to 5.3 V

• Operating temperature Topr –25 to +75 °C

Description

The CXA3067M is an integrated circuit designed

for CATV wide band FSK receiver. This monolithic

IC is composed of local oscillator, double balanced

mixer, limiter, FM detector, data shaper and PLL

circuit in a single chip.

Features

• Built in PLL

• 3 bits 3 states frequency selection

• Applied for 4 reference frequency

(7.15625/7.15909/14.3125/14.31818 MHz)

• Compatible with external reference clock and X’tal

oscillator

• Balanced oscillator and double balanced mixer for

low L.O. leakage

• Low power consumption

• SOP 30 pin package

Function

• Oscillator

• Mixer

• PLL

• Limiter

• FSK detector

• Data shaper

Applications

FSK receiver for CATV

Structure

Bipolar silicon monolithic IC

Wide Band FSK Receiver

30 pin SOP (Plastic)

CXA3067M

—2—

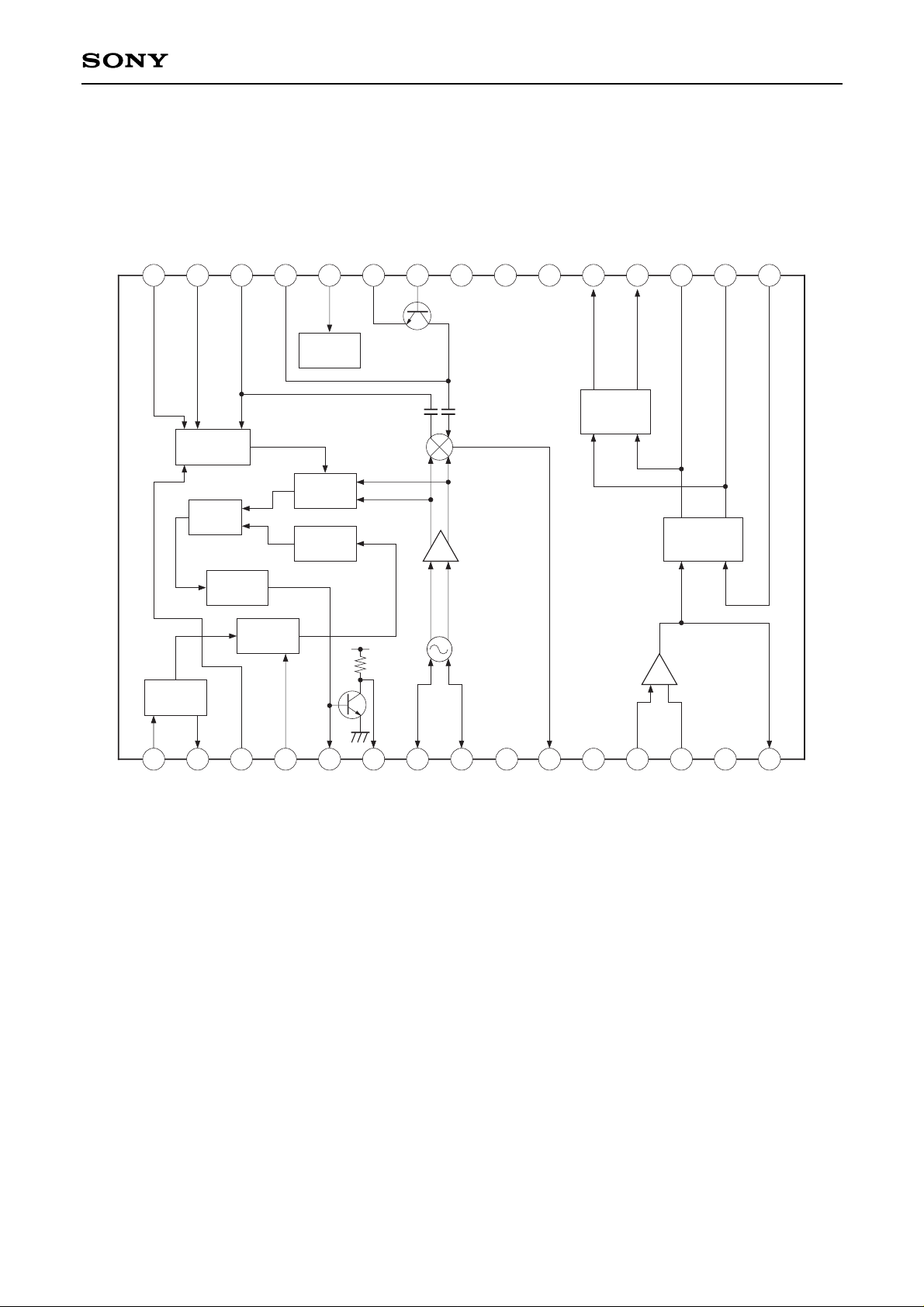

CXA3067M

Pin configuration and Block diagram

8 91 2 10 11 12 13 14 15654 73

22 21 20 19 18 1727 26 23 1629 2830 25 24

FSET2

FSET3

REFSW

MIXIN

RFVCC

RFEM

RFIN

RFGND

IFGND

IFVCC

NOUT

POUT

LF2

LF1

DETIN

REFIN

XTAL

FSET1

RDSW

CPLF

VT

OSC1

OSC2

DGND

MIXOUT

DVCC

LIMIN

BYP

GND

LIMOUT

V.REG

FREQ

SELECT

PHASE

DET

MAIN

DIVIDER

REF

DIVIDER

CHARGE

PUMP

SCALER

REF

OSC

DATA

SHAPER

DET

MIX

OSC

LIM

—3—

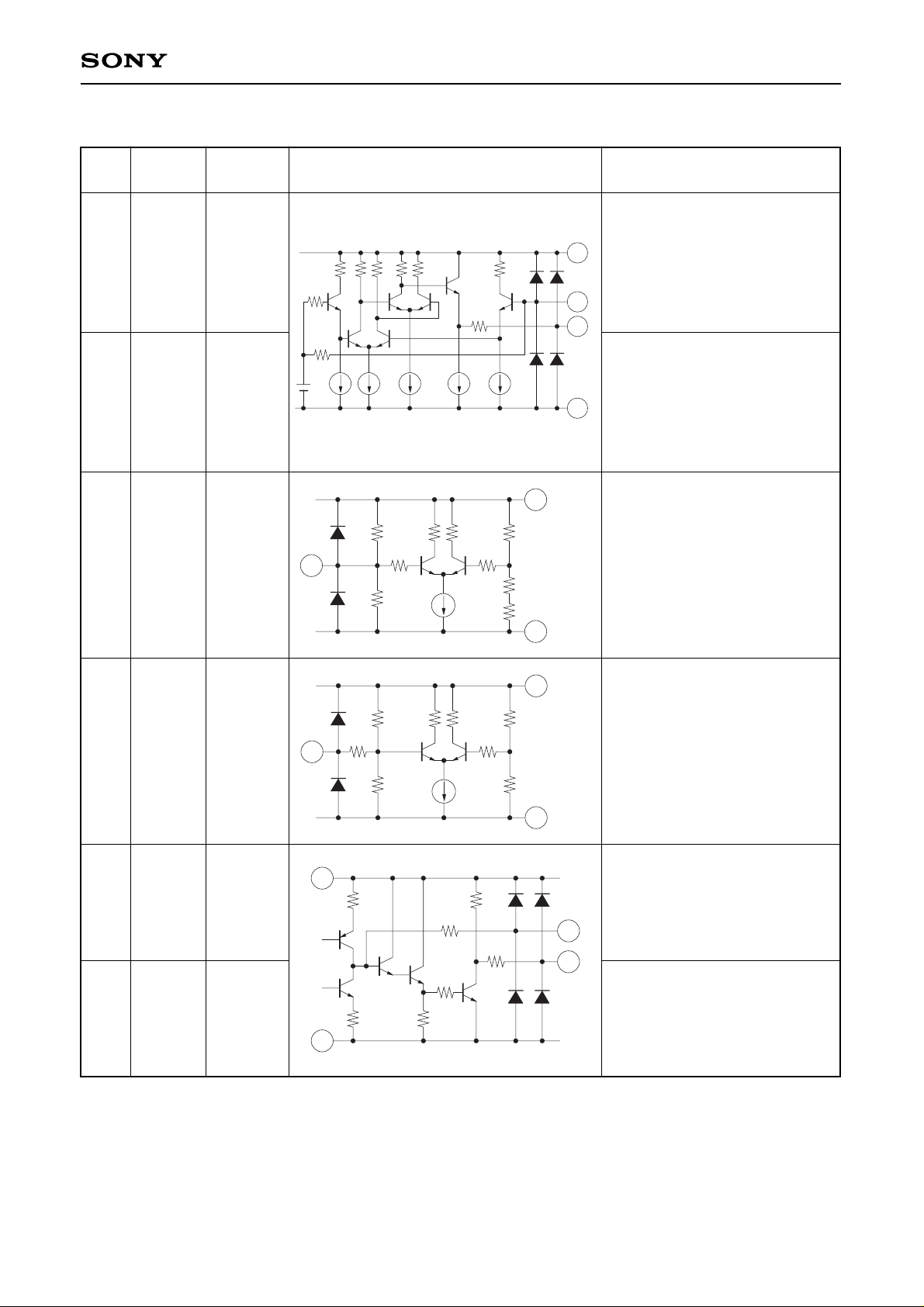

CXA3067M

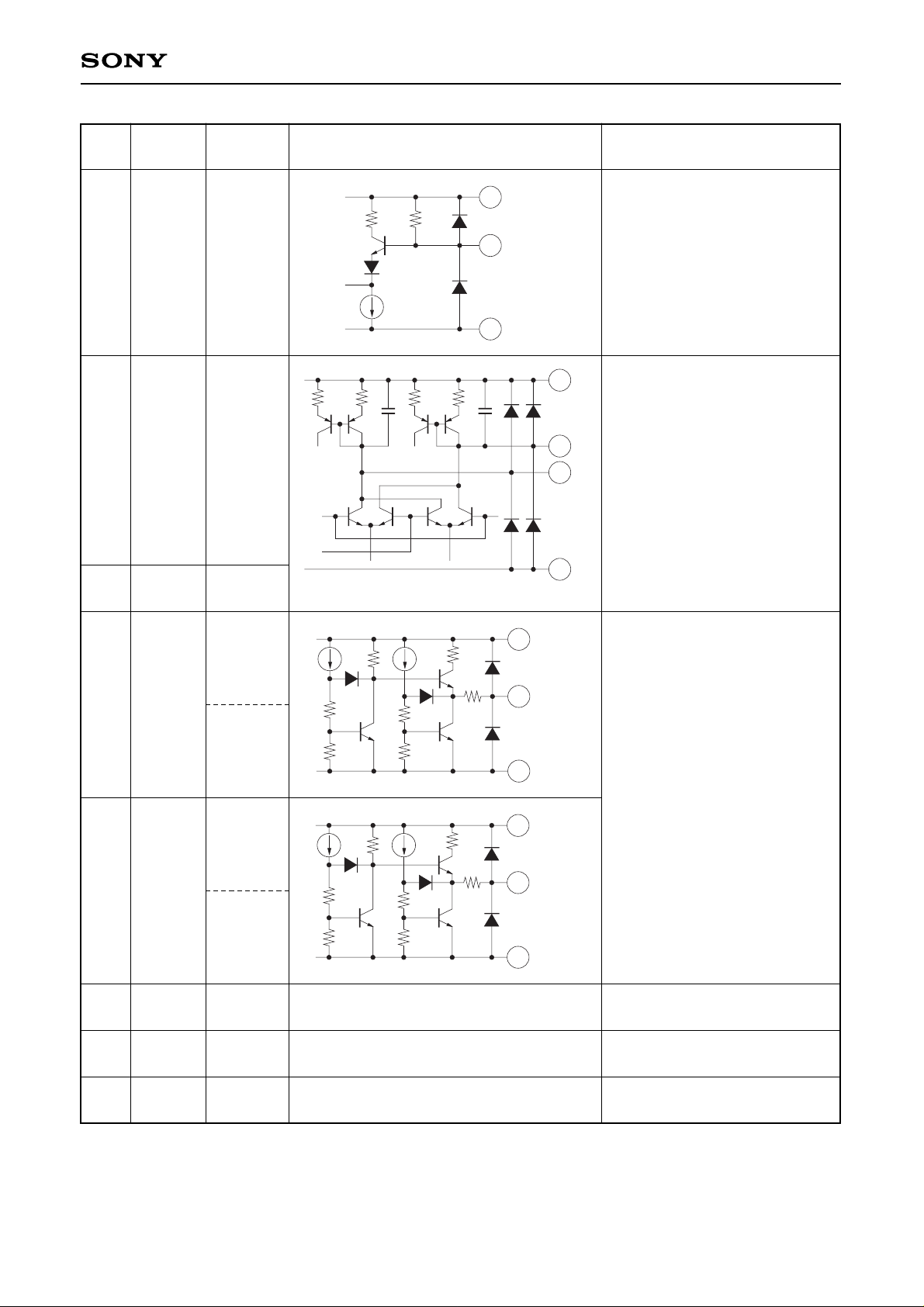

Pin Description and Equivalent Circuit

Pin

Symbol

Typical

Equivalent circuit Description

No. voltage (V)

1

2

3

4

5

6

REFIN

XTAL

FSET1

RDSW

CPLF

VT

3.4

4.0

2.5

(OPEN)

3.0

(OPEN)

2.0

0.3 to VCC

500

DVCC

1

2

11

9

DGND

3

11

9

20k

20k

DVCC

DGND

11

4

9

25k

20k

30k

DVCC

DGND

DVCC

5

6

10k

100

100

11

9

DGND

External clock input

and X’tal connection for

reference oscillator.

X’tal connection for

reference oscillator.

The pin for channel selection.

The condition of pin 3 has

3 states.

Connect to 5 V source for “Hi”

selection and connect to GND for

“Low” selection and leave open.

Reference frequency selection.

Connect to GND when reference

frequency is 14.3125 MHz or

14.31818 MHz and leave open

when reference frequency is

7.15625 MHz or 7.15909 MHz.

Charge pump output.

Connect to loop filter.

Connect to loop filter.

OSC tuning voltage output.

—4—

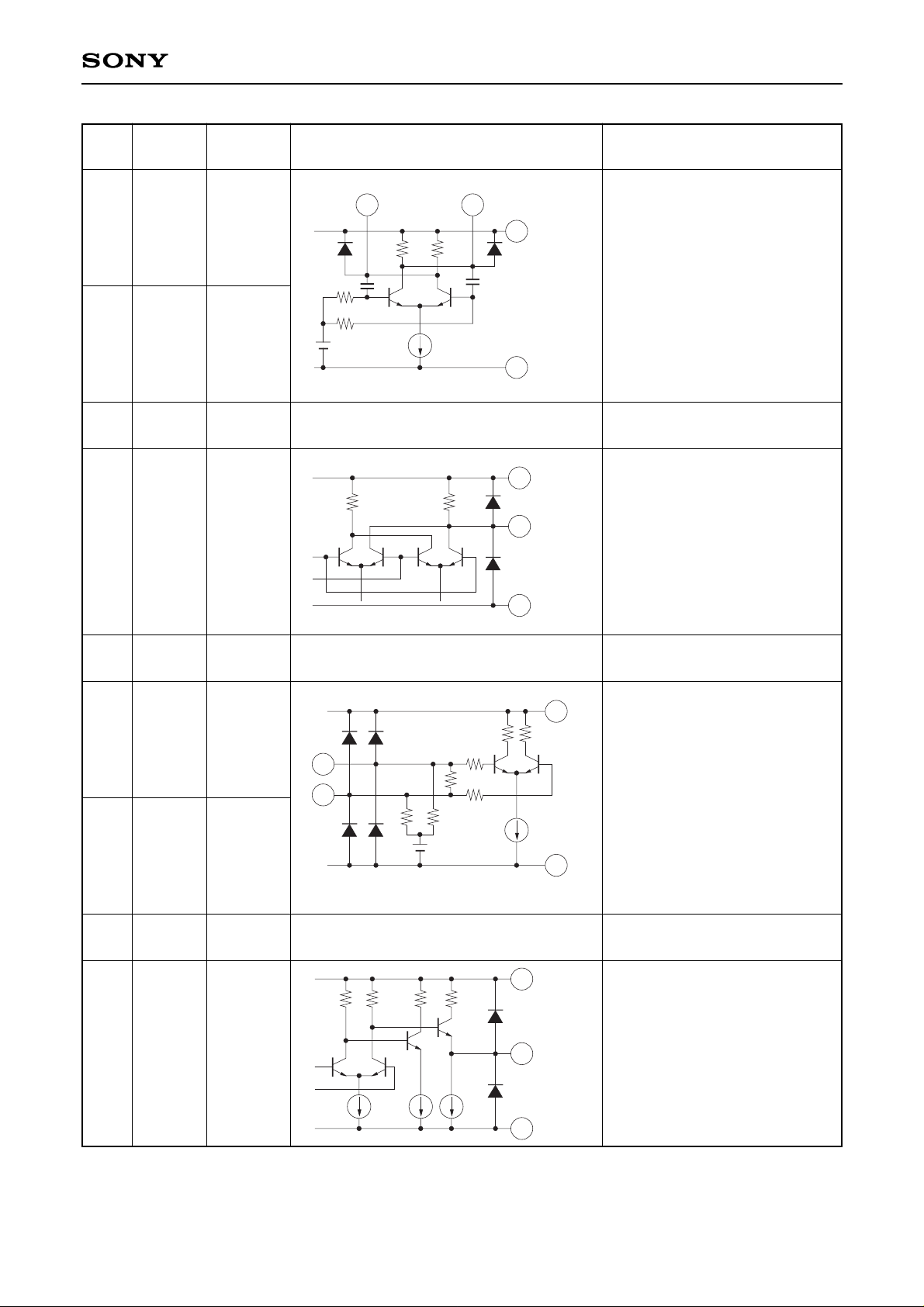

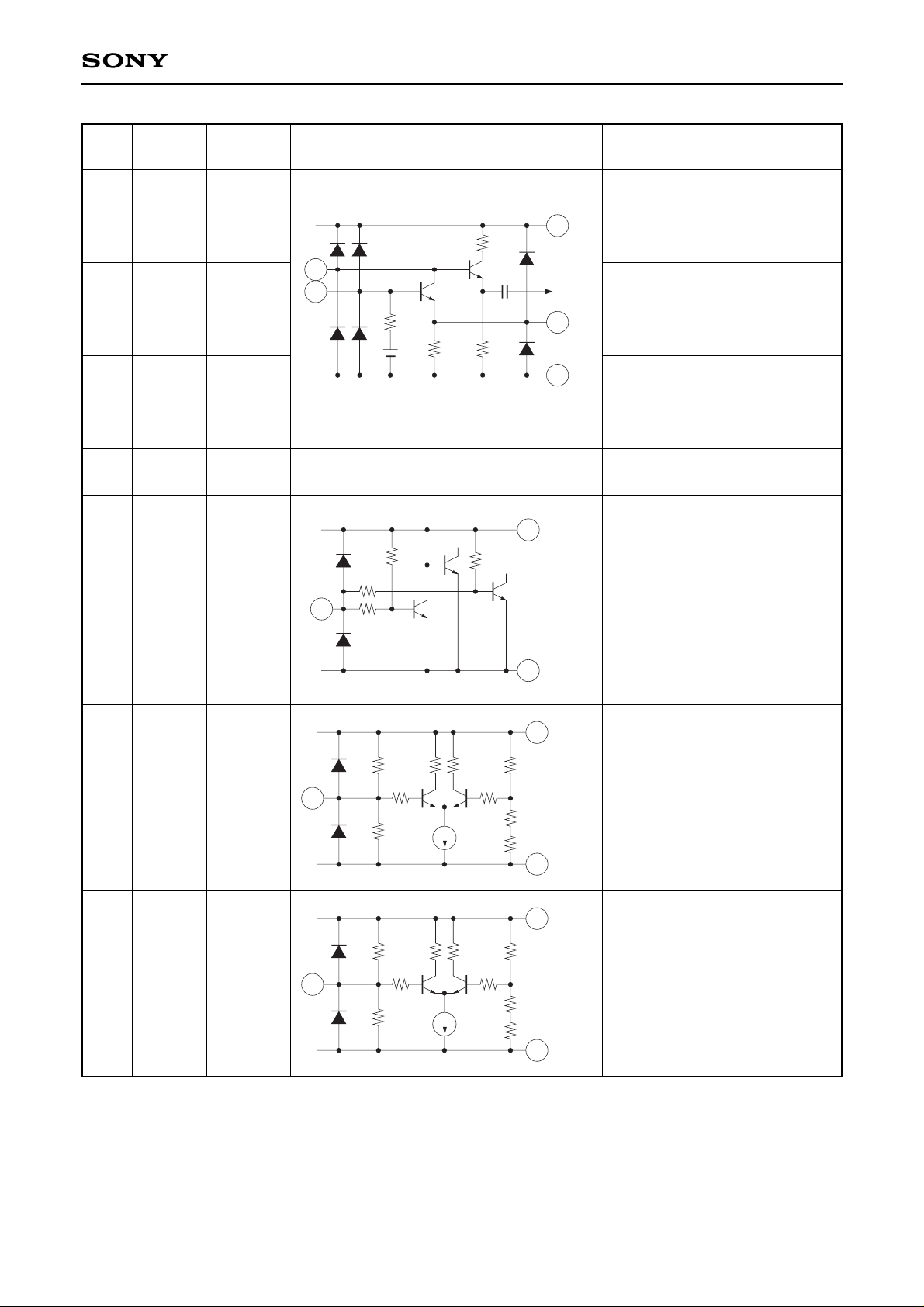

CXA3067M

Pin

Symbol

Typical

Equivalent circuit Description

No. voltage (V)

7

8

9

10

11

12

13

14

15

OSC1

OSC2

DGND

MIXOUT

DVCC

LIMIN

BYP

GND

LIMOUT

3.7

3.7

0

4.0

5

2.4

2.4

0

3.1

26

87

23

RFVCC

RFGND

700 700

3k

3k

26

10

23

330 330

RFVCC

RFGND

12

13

10k

330

10k

21

IFVCC

22

IFGND

IFVCC

21

15

IFGND

22

Oscillator.

PLL circuit GND.

Mixer output.

Output impedance is 330 Ω.

PLL circuit power supply.

Limiter input.

Input impedance is 330 Ω.

GND.

Limiter output.

—5—

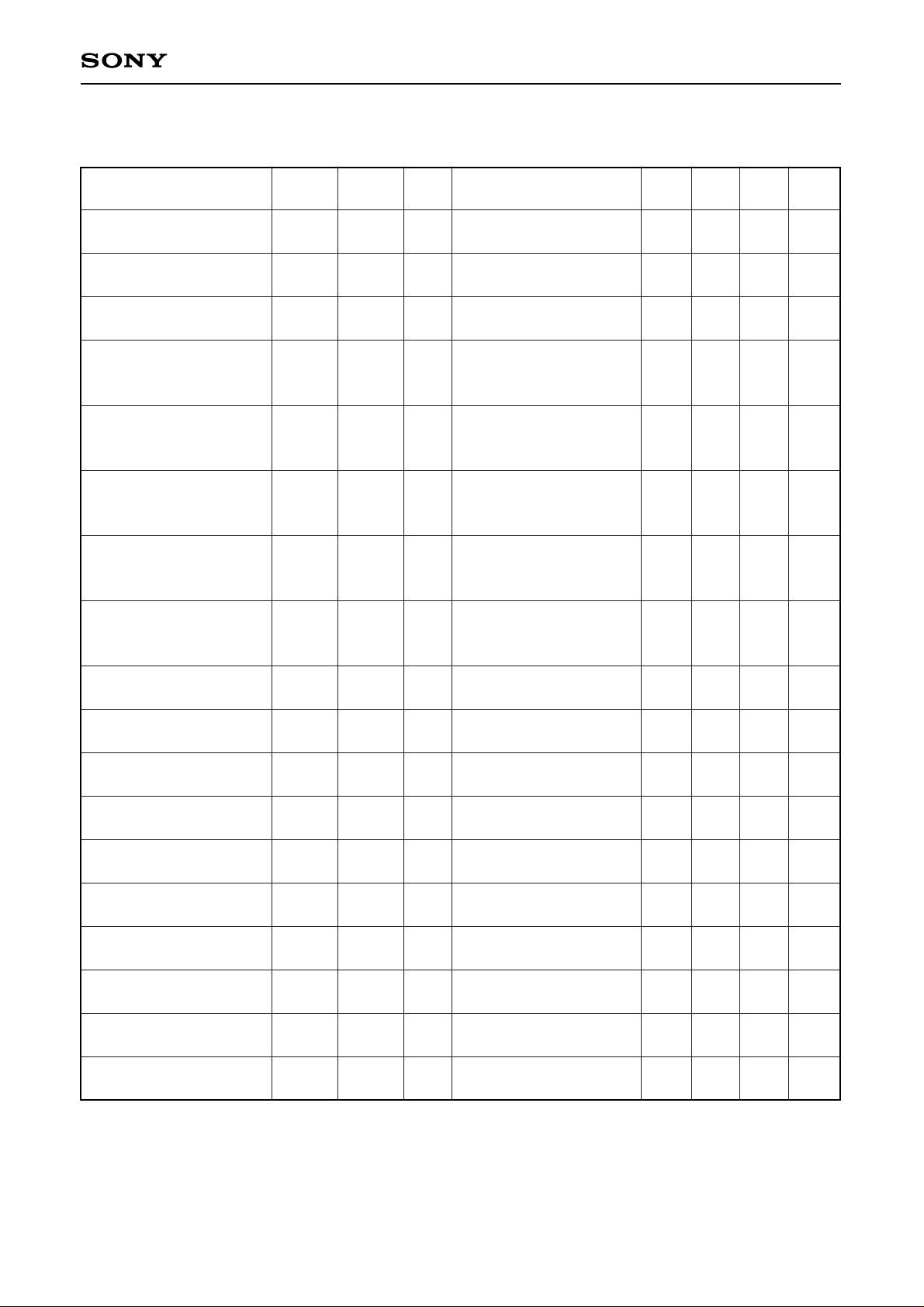

CXA3067M

Pin

Symbol

Typical

Equivalent circuit Description

No. voltage (V)

16

17

18

19

20

21

22

23

DETIN

LP1

LP2

POUT

NOUT

IFVCC

IFGND

RFGND

5.0

4.2

4.2

4.1

(Hi)

0.22

(Low)

4.1

(Hi)

0.22

(Low)

5.0

0

0

21

IFVCC

16

32k

22

IFGND

21

18

17

IFVCC

IFGND

12p 12p

22

21

19

IFVCC

IFGND

22

50

21

20

22

IFVCC

IFGND

50

Detector input.

Connect to a discriminator.

The capacitor is connected

between pins 17 and 18 for

the filter.

FSK data output.

Pins 19 and 20 are each

other reversal condition.

Power supply for limiter, detector,

data shaper circuit.

GND for limiter, detector,

data shaper circuit.

GND for RFamp, Mixer,

oscillator circuit.

—6—

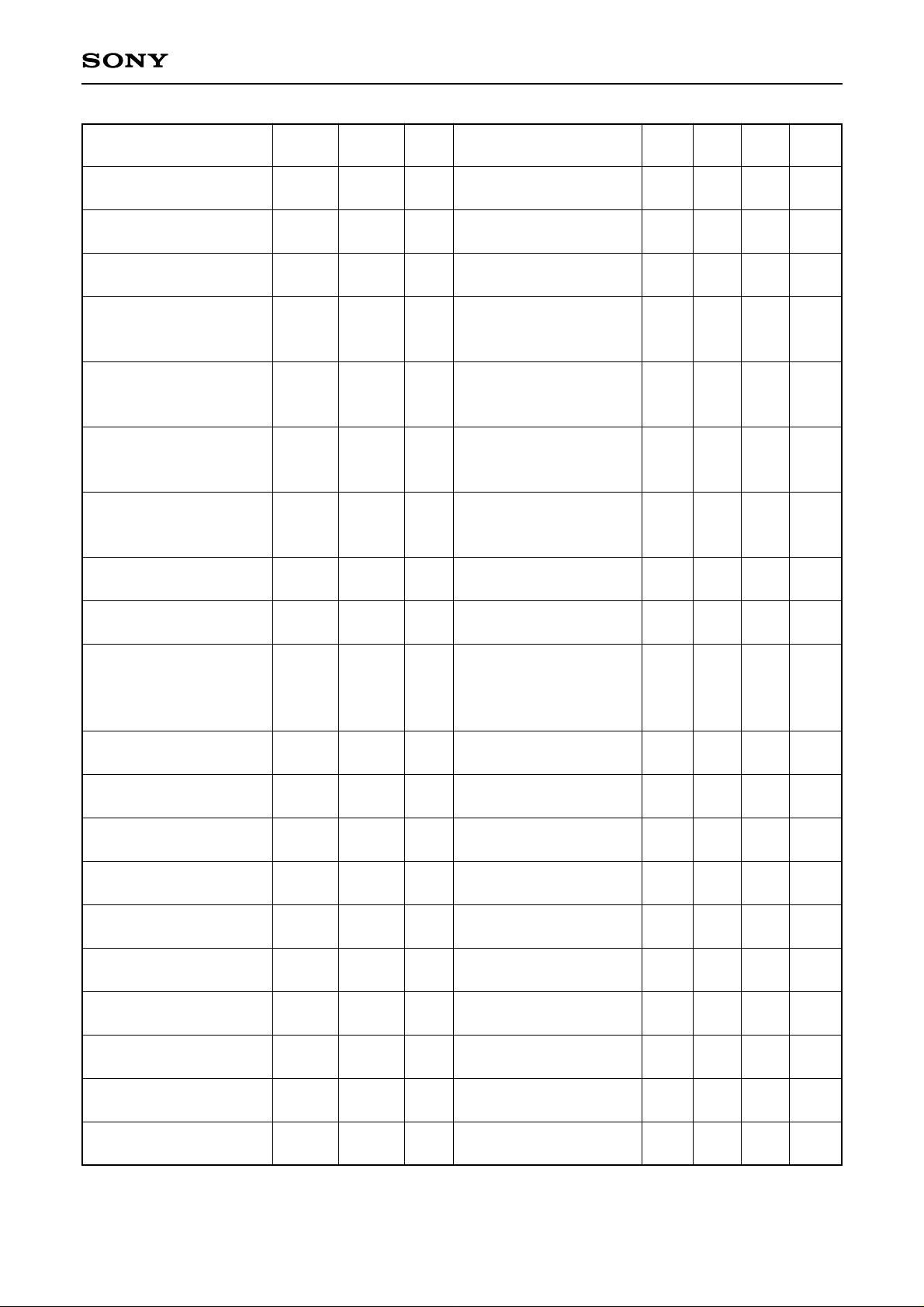

CXA3067M

Pin

Symbol

Typical

Equivalent circuit Description

No. voltage (V)

24

25

27

26

28

29

30

RFIN

RFEM

MIXIN

RFVCC

REFSW

FSET3

FSET2

1.9

1.1

5.0

5.0

0.7

(OPEN)

2.5

(OPEN)

2.5

(OPEN)

RFVCC

26

MIX

25

27

233

5k

24

RFGND

23

11

29

9

20k

20k

DVCC

DGND

28

DVCC

DGND

11

9

11

9

20k

20k

DVCC

DGND

30

RFamp input.

Gain adjustment.

Normally, by-pass capacitor is

connected at pin 25 to GND.

RFamp output and mixer input.

Power supply for RFamp, mixer,

oscillator circuit.

Reference frequency selection.

Decoupling capacitor is

connected at pin 28 to GND

when reference frequency is

7.15909 MHz or 14.31818 MHz

and pin 28 is connected to GND

directly when reference

frequency is 7.15625 MHz or

14.3125 MHz.

The pin of channel selection.

The condition of pin 29 has

3 states.

Connect to 5 V source for “Hi”

selection and connect to GND for

“Low” selection and leave open.

The pin of channel selection.

The condition of pin 30 has

3 states.

Connect to 5 V source for “Hi”

selection and connect to GND for

“Low” selection and leave open.

—7—

CXA3067M

Electrical Characteristics

See Electrical Characteristics Test Circuit (VCC=5.0 V, Ta=+25 °C)

Item Symbol Pin No.

Circuit

Conditions Min. Typ. Max. Unit

No.

RFVCC

Current consumption

IFVCC

Current consumption

DVCC

Current consumption

Input sensitivity 1

Input sensitivity 2

Input level

Local OSC leakage

from RF input 1

Local OSC leakage

from RF input 2

RFamp bias current

RFamp voltage gain 1

RFamp voltage gain 2

RFamp voltage gain 3

RFamp input resistance

RFamp input capacitance

Mixer input resistance

Mixer input capacitance

Mixer voltage gain

RFamp+Mixer noise figure

RFI

CC

IFICC

DICC

Vi1

Vi2

Vil

LOleak1

LOleak2

Irf

Grf1

Grf2

Grf3

rπ (rf)

Cπ (rf)

rπ (mix)

Cπ (mix)

Gmix

NF

rfmix

26, 27

21

11

24

24

27

24

→27

24→27

24→27

24

24

27

27

27→10

24→10

RFV

CC

V1=5 V

IFV

CC

V2=5 V

DV

CC V4=1 V

V3=5 V

Measurement on RFIN pin

SW1 : ON

RF=53.35 M to 169.5 MHz

Measurement on RFIN pin

SW1 : ON

RF=221.95 M to 302 MHz

RFV

CC

V1=5 V

RF=53.35 M to 169.5 MHz

RF=221.95 M to 229.8 MHz

RF=302 MHz

I=4.8 mA, RF=100 MHz

Load Resistance=510 Ω

l=4.8 mA, RF=100 MHz

Load Resistance=510 Ω

RF=100 MHz

RF=100 MHz

RF=108.5 MHz→

IF=10.7 MHz

RF=108.5 MHz→

IF=10.7 MHz ∗

1

fMOD=10 kHz, fDEV=±75 kHz

Jitter is 1 % for f

MOD

50 Ω Termination

RF=53.35 M to 169.5 MHz

f

MOD=10 kHz, fDEV=±75 kHz

Jitter is 1 % for f

MOD

50 Ω Termination

RF=221.95 M to 302 MHz

f

MOD=10 kHz, fDEV=±75 kHz

Jitter is 1 % for f

MOD

50 Ω Termination

RF=53.35 M to 302 MHz

14 24 34 mA

3 6.7 10 mA

3.5 7 10 mA

–32 dBmV

–25 dBmV

+10 dBmV

–10 dBmV

+5 dBmV

3 4.8 7 mA

24 30 34 dB

22 25 28 dB

16 19 22 dB

670 Ω

4.7 pF

1.7 kΩ

5.7 pF

9 13 17 dB

7 dB

Note) 0 dBmV=1 mV, 0 dBµV=1 µV

∗

1

) Noise figure is uncorrected for image.

0 dBmV=60 dBµV

0 dBm=47 dBmV

1

1

1

2

2

2

2

2

1

3

3

3

4

5

—8—

CXA3067M

Item Symbol Pin No.

Circuit

Conditions Min. Typ. Max. Unit

No.

Mixer output resistance

Limiter input resistance

Limiter voltage gain

FSK Data

output voltage “H”

FSK Data

output voltage “L”

FSK Data output rise time

FSK Data output fall time

Oscillation frequency

VT output voltage range

Charge pump current

REFCLOCK input level 1

REFCLOCK input level 2

REFOSC loop gain

FSET1/2/3 “Hi” level

input voltage

FSET1/2/3 “Low” level

input voltage

FSET1/2/3 “Hi” level

input current

FSET1/2/3 “Low” level

input current

RDSW “Low” level

input voltage

RDSW “Low” level

input current

REFSW “Low” level

input voltage

r

L (mix)

rπ (lim)

Glim

OUTH

OUTL

Tr

Tf

OSC

VT

Icp

CLK 1

CLK 2

Gref

FSETVH

FSETVL

FSETIH

FSETIL

RDVL

RDIL

REFVL

10

12

15

19, 20

19, 20

19, 20

19, 20

7, 8

6

5

1

1

1, 2

3, 29, 30

3, 29, 30

3, 29, 30

3, 29, 30

4

4

28

IF=10.7 MHz

IF=10.7 MHz

IF=10.7 MHz

Load Capacitance=2 pF

Load Resistance=10 kΩ,

f

MOD=10 kHz, fDEV=±75 kHz

Load Capacitance=2 pF

Load Resistance=10 kΩ,

f

MOD=10 kHz, fDEV=±75 kHz

Load Capacitance=2 pF

Load Resistance=10 kΩ,

f

MOD=10 kHz, fDEV=±75 kHz

Road Capacitance=2 pF

Road Resistance=10 kΩ,

f

MOD=10 kHz, fDEV=±75 kHz

Source current

→ SW2 : OFF

SW3 : OFF

Sink current → SW2 : ON

SW3 : ON

Sin wave input

Square wave input

Vin2=14 MHz

FSET “Hi”=V5=5 V

FSET “Low”=V5=0 V

RDSW “L”=V6=0 V

222 332 442 Ω

222 332 442 Ω

70 dB

3.8 4.1 V

0.22 0.6 V

12 30 nsec

12 30 nsec

40 315 MHz

0.3 2.5 V

CC V

±25 ±50 ±75 µA

0.3 0.4 3.0 Vp-p

0.3 0.4 3.0 Vp-p

30 dB

3.8 V

CC V

0 0.4 V

120 250 380 µA

–380 –250 –120 µA

0 0.4 V

–122 –83 –43 µA

0 0.4 V

6

2

2

2

2

7

3

1

1

1

1

1

1

1

Loading...

Loading...