Sony CXA3038N Datasheet

—1—

E97650A84-TE

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

Absolute Maximum Ratings (Ta=25 °C)

• Supply voltage VCC –0.3 to 5.5 V

• Storage temperature Tstg –55 to +150 °C

Operating Conditions

• Supply voltage VCC 4.75 to 5.30 V

• Operating temperature Topr –25 to +75 °C

Description

The CXA3038N is an IC for IQ-detection of DSS,

DVB, and other digital satellite broadcast QPSK

modulation signals in the 480 MHz band. It consists

of an AGC amplifier circuit, oscillator circuit, phase

shifter circuit, and phase comparison circuit. In

addition, the chip has a PLL circuit for frequency

control and built-in control data. It realizes highaccuracy oscillator frequencies through use of a lowcost LC resonance circuit.

Features

• Built-in PLL for controlling oscillator frequency.

• Oscillator frequency based at 479.5 MHz is

adjustable in ±4 steps of 50 kHz using the voltage

of the control pin.

• Reference OSC allows switching to 4 MHz or 10

MHz.

• Built-in output buffer for reference OSC.

• Low-impedance IQ output.

• AGC gain variation 35 dB.

Applications

Digital satellite broadcast tuner

Structure

Bipolar silicon monolithic IC

IQ Detection IC for Digital Satellite Broadcast Tuner

24 pin SSOP (Plastic)

CXA3038N

—2—

CXA3038N

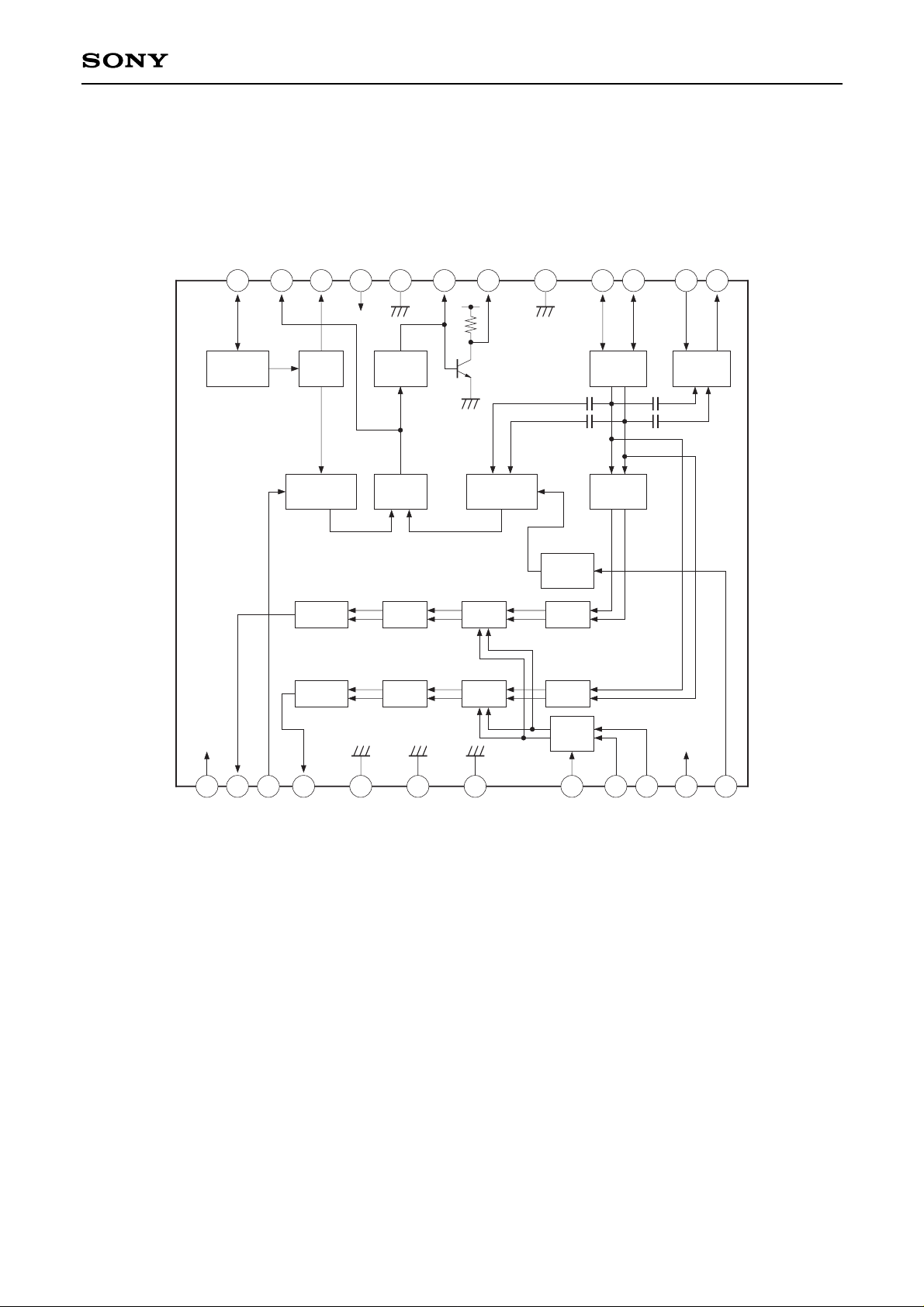

Block Diagram and Pin Configuration

Ref OSC Buffer

Charge

Pump

OSC

Prescaler

1/32

Divider

1/80, 1/200

Phase

DET

Divider

10bit+4bit

Phase

Shifter

Comparator

BufferLPFDC AMP

BufferLPFDC AMP

AGC

AMP

7 9

10

821 3 4 5 6

11 12

16 15 14 1324 23 22 21 20 19 18 17

XTAL

LOCK

REFOUT

DV

CC

DGND

LPF

VC

OSCGND

OSC1

OSC2

PSV

CC

LOOUT

IQV

CC

QOUT

XCONT

IOUT

IQGND

GND

RFGND

AGC

RFIN2

RFIN1

RFV

CC

NSET

IMIX

QMIX

—3—

CXA3038N

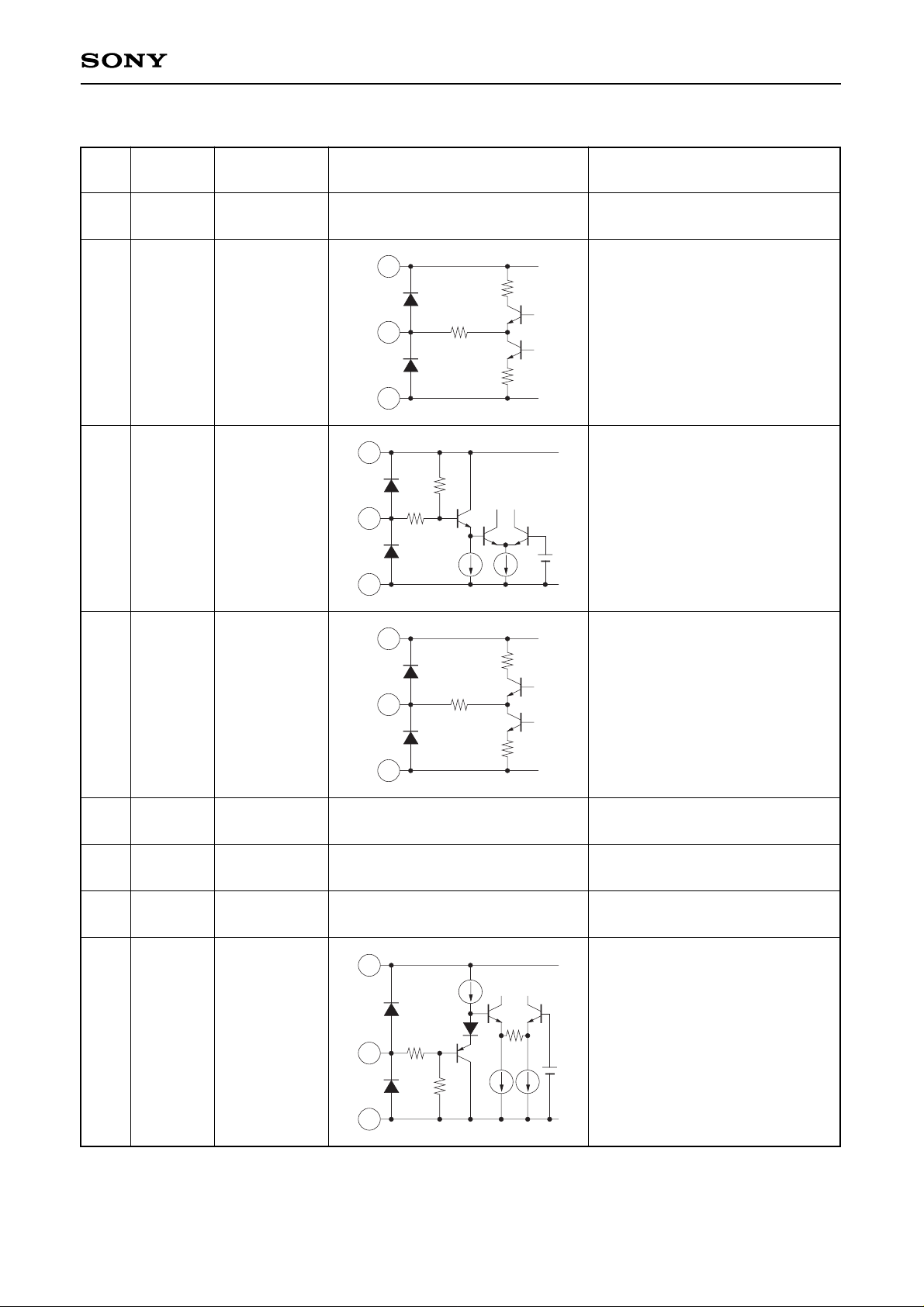

Pin Description

Pin

Symbol

Typical pin

Equivalent circuit Description

No. voltage

1

2

3

4

5

6

7

8

IQVCC

QOUT

XCONT

IOUT

IQGND

GND

RFGND

AGC

5 V

2.7 V

Open or 5 V

when using

4 MHz crystal ;

0 V when using

10 MHz crystal.

2.7 V

0 V

0 V

0 V

0 to 4 V

1

2

5

20

90k

21

3

20

10k

1

4

5

20

20k

20k

11

8

7

IQ output circuit VCC.

Q output.

Switching pin for reference divider

frequency-division ratio.

This is set to 80 frequency

divisions when open or connected

to VCC; 200 frequency divisions

when connected to GND.

I output.

IQ output circuit GND.

GND.

RF circuit (AGCAmp, MIXER)

GND.

AGCAmp gain adjustment.

—4—

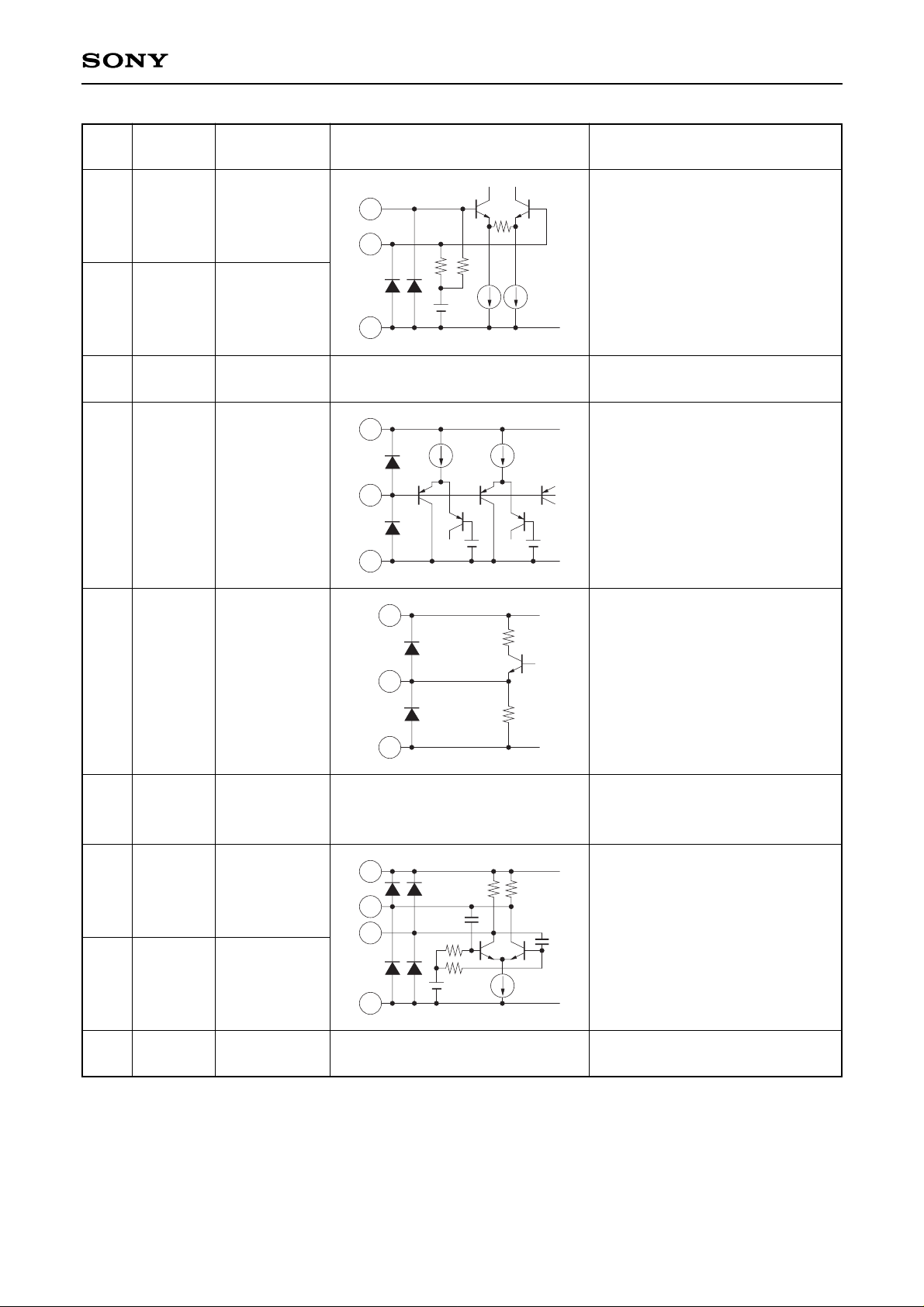

CXA3038N

Pin

Symbol

Typical pin

Equivalent circuit Description

No. voltage

9

10

11

12

13

14

15

16

17

RFIN2

RFIN1

RFVCC

NSET

LOOUT

PSVCC

OSC2

OSC1

OSCGND

2.1 V

2.1 V

5 V

1.6 V

4 V

5 V

3.7 V

3.7 V

0 V

5k

9

10

7

2.2V

5k

21

12

20

14

13

20

8k

11

17

16

15

700 700

3p

3p

RF signal inputs.

RF circuit (AGCAmp, MIXER,

OSC) VCC.

OSC frequency fine-adjustment.

The oscillator frequency based at

479.5 MHz is adjustable in ±4

steps of 50 kHz by applying a

voltage of 0 to 5 V.

Output for OSC frequency signal

divided into 32 frequency divisions.

VCC for 32 frequency division

circuit. This is set to open when

activating the built-in PLL.

OSC pins.

These pins connect the varicap

diode and coil resonance circuit.

OSC circuit and phase shifter

circuit GND.

—5—

CXA3038N

Pin

Symbol

Typical pin

Equivalent circuit Description

No. voltage

18

19

20

21

22

23

24

VC

LPF

DGND

DVCC

REFOUT

LOCK

XTAL

0.3 V to 5 V

1.8 V to 3.7 V

0 V

5 V

4.1 V

0.01 V when

unlocked; 3.2 V

when locked

4.4 V

100

21

18

20

10k

100

21

19

20

21

22

20

21

23

20

200k

21

20

24

60k

20p

20p

Voltage output for varicap diode

making up the VCO.

Phase comparison output.

This pin connects the loop filter.

PLL circuit GND.

PLL circuit VCC.

REFOSC output.

PLL lock/unlock monitor.

Crystal connection.

Loading...

Loading...