Sony CXA2571N Datasheet

RF Matrix Amplifier

Description

The CXA2571N is an IC developed for the RF

signal processing of compact disc players.

Features

• Wide band RF signal processing

• RF system VCA circuit

• RF system equalizer (supports CAV mode)

• Supports pickups with built-in RF summing amplifier

• Low power consumption mode (EQ Pass mode)

• RW/ROM switching mode

• Center error amplifier

• Output DC level shift circuit

Functions

• RFAC summing amplifier, equalizer, VCA

• RFDC summing amplifier

• Focus error amplifier

• Tracking error amplifier

• Automatic power control

• VC buffer amplifier (analog system, digital system)

Applications

CD-ROM/RW compatible systems

Structure

Bipolar silicon monolithic IC

Absolute Maximum ratings

• Supply voltage Vcc 7 V

• Operating temperature Topr –20 to +75 °C

• Storage temperature Tstg –65 to +150 °C

• Allowable power dissipation

PD 620 mW

Operating Conditions

• Supply voltage Vcc – GND 3.0 to 5.5 V

• Operating temperature Topr –20 to +75 °C

– 1 –

E98260A98-PS

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

CXA2571N

30 pin SSOP (Plastic)

– 2 –

CXA2571N

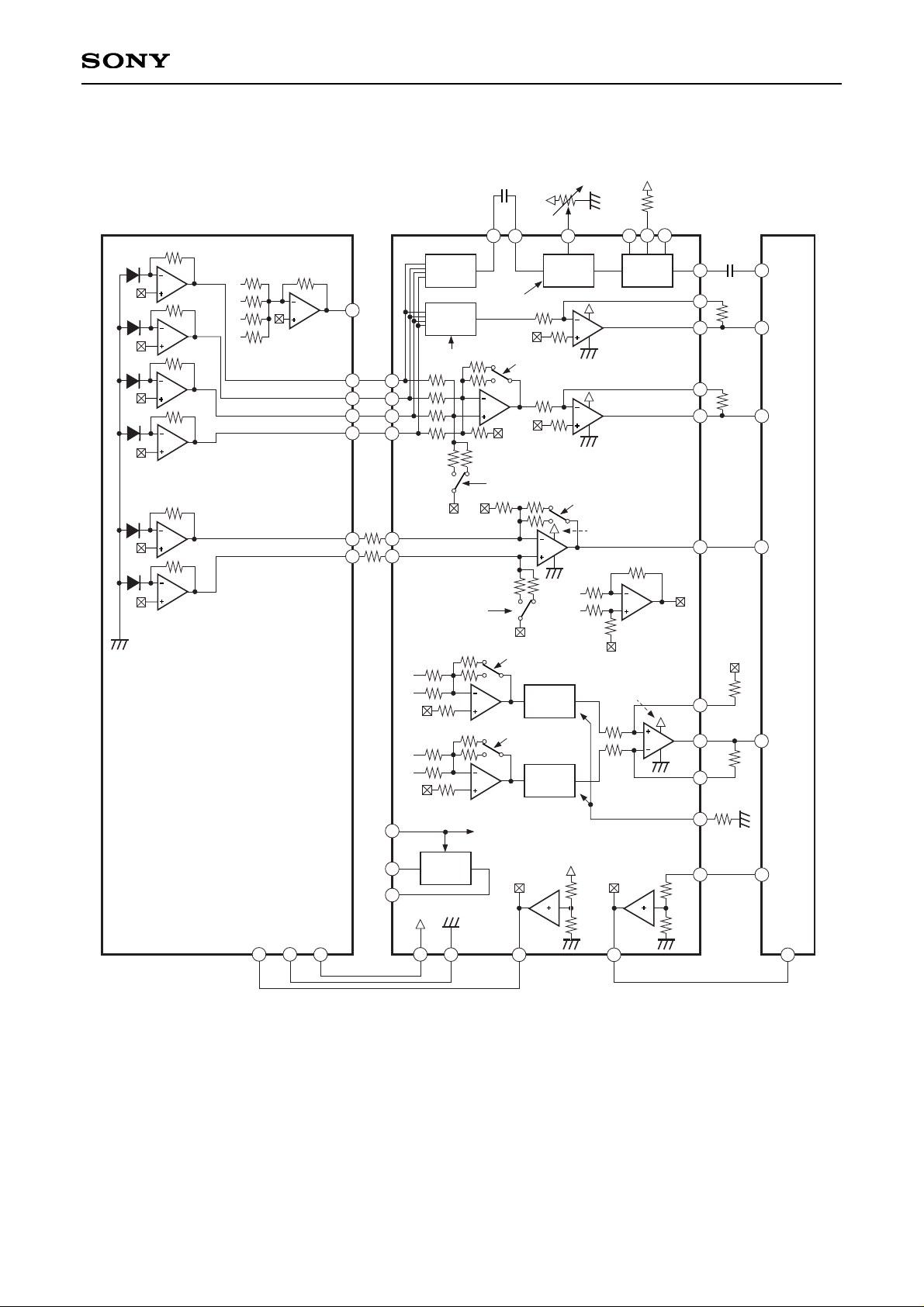

Connected Circuit Diagram

VC

RF

VC

A

A

B

C

D

A

B

C

D

A

B

C

D

AC

SUM

DC

SUM

VC

B

VC

VC

FE

FE

FEI

100k

DVC

C

VC

D

VC

F F

E

F

E

VC

E

RFDCI

RFAC

RFAC

RFDCO

RFDC

5.1k

DVC

ACG

RW/ROM RW/ROM

RW/ROM

DV

CC

DVCC

DVCC

RW/ROM

VOFST

VOFST

VOFST

Rfc Vfc

5.1k

<DSP>

<OP>

EQIACSUM BST

VCC

DVCC

TE

TE

V

CC

0.1µ

AC

VCA

EQ

AVC

RW/ROM

RW/ROM

10k

10k

APC

Bottom

Hold

PD

LD

SW

APC-OFF (Hi-Z)

RW/ROM

(H/L)

VC

VC VCCGND

VCC

AVC

VCC

VCC

CE

CE

CEP

CEM

CET

VCC GND

DVCC

DVC

AVC

AVC

DVC

r_adj

VC

A

D

RW/ROM

Bottom

Hold

VC

B

C

RW/ROM

DVC

DVC

– 3 –

CXA2571N

Pin Description

Pin

NO.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

LD

PD

EQ_IN

AC_SUM

GND

A

B

C

D

E

F

SW

CET

CEP

DVCC

RFAC

DVC

FE

FEI

TE

CE

CEM

VCC

RFG

BST

VFC

RFC

VC

RFDCO

RFDCI

Out

In

In

Out

In

In

In

In

In

In

In

In

In

—

In

Out

Out

Out

—

Out

Out

—

In

In

In

In

In

Out

Out

—

APC amplifier output.

APC amplifier input.

RFAC system VCA block and EQ block input.

RFAC system RF SUM output.

Ground.

A signal input.

B signal input.

C signal input.

D signal input.

E signal input.

F signal input.

Mode switching signal input.

CE system hold time constant adjustment.

CE amplifier non-inverted input.

DVCC.

RFAC signal output.

DVC output.

Focus error signal output.

FE amplifier virtual ground.

Tracking error signal output.

Center error signal output.

CE amplifier virtual ground.

VCC.

RFAC system VCA block low-frequency gain adjustment.

EQ boost amount adjustment range.

EQ cut-off frequency adjustment.

EQ cut-off frequency adjustment.

VC voltage output.

RFDC signal output.

RFDC amplifier virtual ground.

Symbol I/O Description

– 4 –

CXA2571N

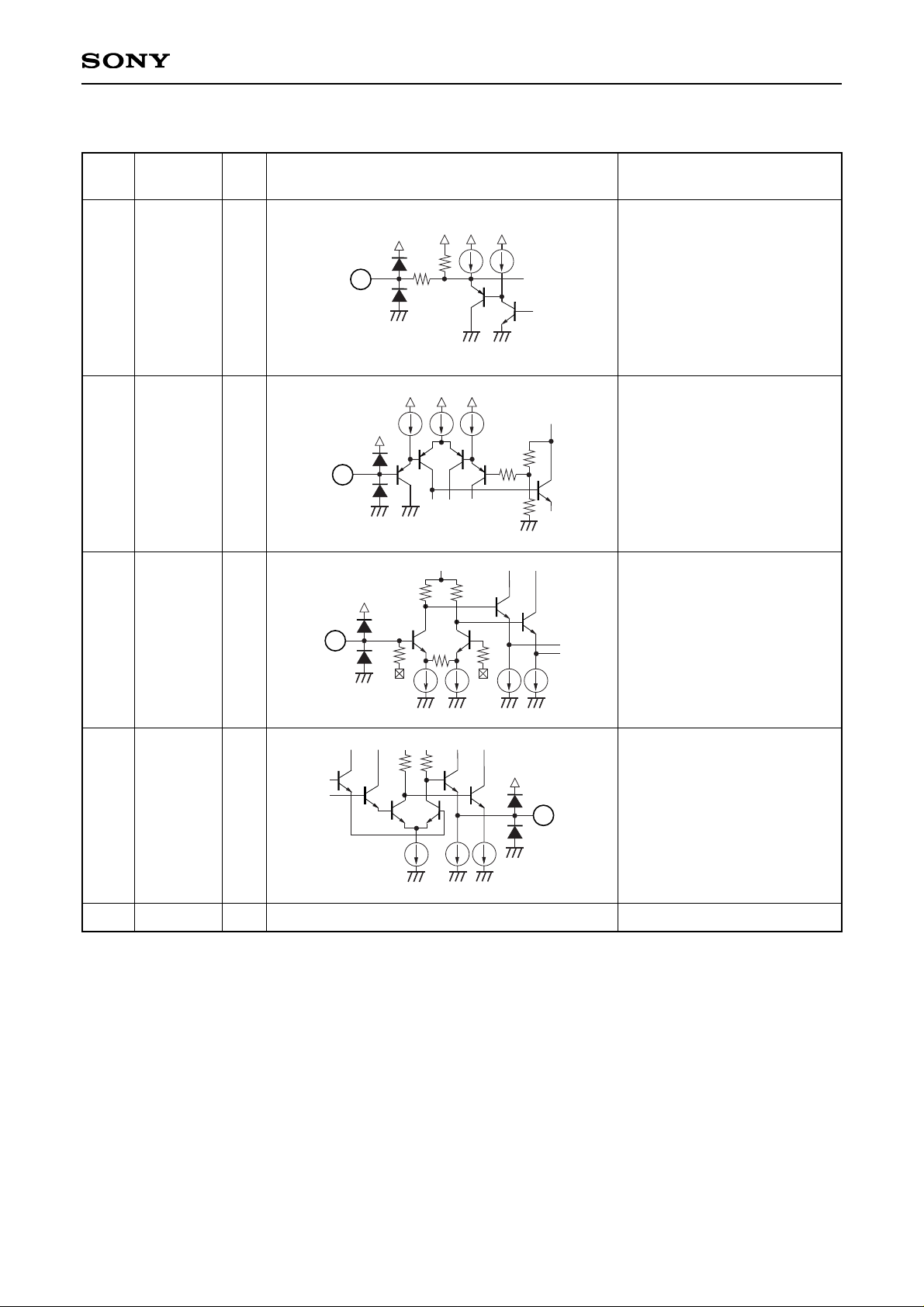

Pin Description and Equivalent Circuit

Pin

No.

1

2

3

4

5

O

I

I

O

— —

APC amplifier output.

APC amplifier input.

Equalizer circuit input.

RFAC summing amplifier

output.

Ground.

LD

PD

EQ_IN

AC_SUM

GND

Symbol I/O Equivalent circuit Description

10k

1k

1

20k

55k

20k

2

VCVC

1.2k

5k5k

1.1k1.1k

3

1.6k

1.6k

4

– 5 –

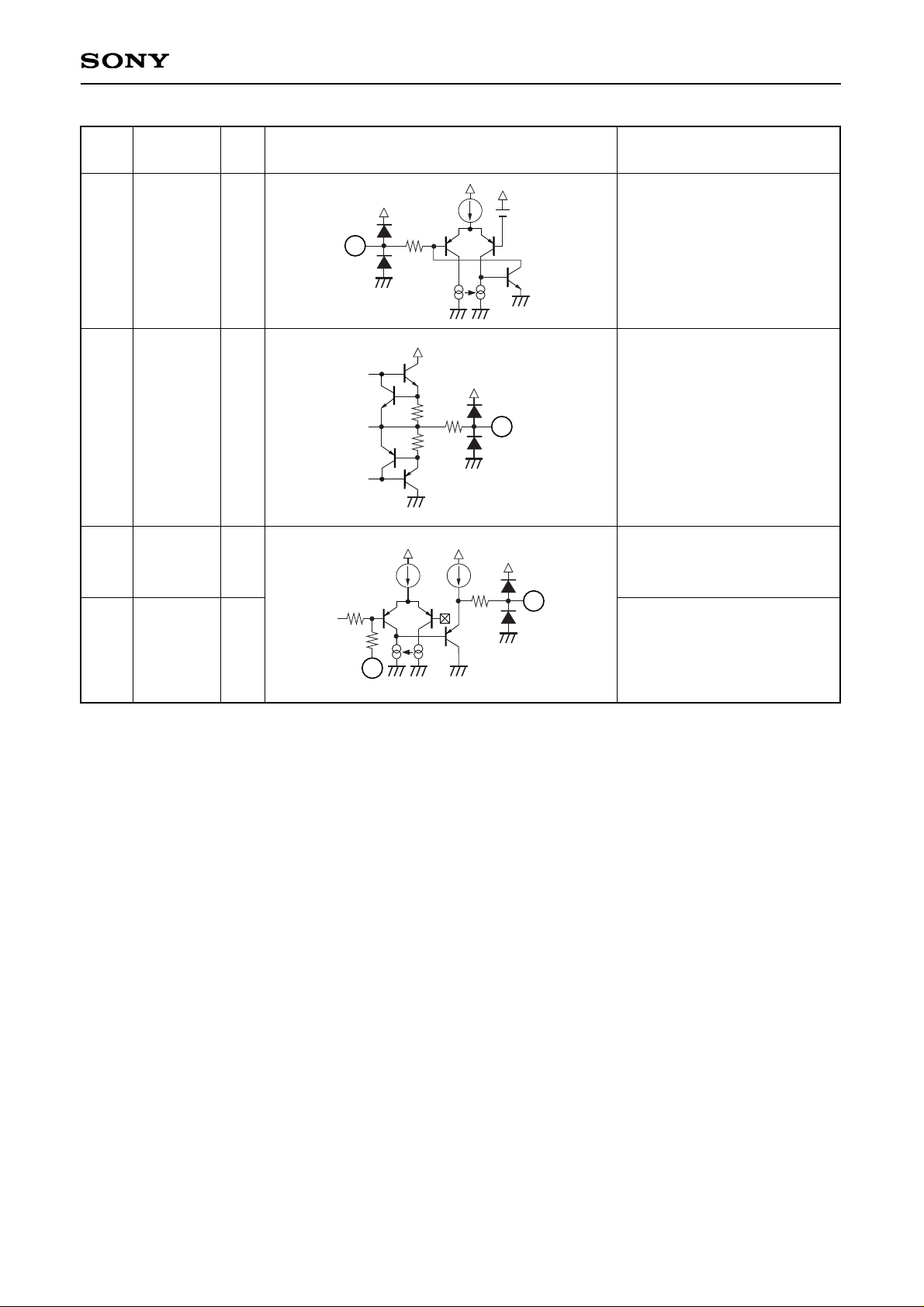

CXA2571N

6 I

RF summing amplifier and

focus error amplifier input.

A

7 IB

8 IC

9 ID

10 I

Tracking error amplifier input.

E

11 I

Tracking error amplifier

output.

F

20 OTE

CD-ROM/RW switching input.

RW when connected to VCC,

ROM when connected to

GND.

12

I

SW

RFAC amplifier output.

16ORFAC

VC

47k

47k

15k

7

30k

100µA

100µA

100µA

100µA

6

8

9

27k 27k

124

10

11

20

200k

12

200k

200k

100

2mA

16

(DVCC + GND)/2 voltage

output.

17 ODVC

25

150k

150k

17

Power supply.

15

— —VCC

Pin

No.

Symbol I/O Equivalent circuit Description

– 6 –

CXA2571N

18

O

Focus error amplifier output.

FE

19

I

Focus error amplifier gain

adjustment. The gain is

adjusted by the external

resistance value connected

between this pin and Pin 18.

FEI

VC

50k

124

124

18

19

13

I

Center error amplifier time

constant adjustment.

CET

12476k

4k

13

14

I

Center error amplifier noninverted input.

CEP

21

O

Center error amplifier input.

CE

22

I

Center error amplifier inverted

input.

CEM

23 — —

VCC. (AVCC)

VCC

24

I

Sets the RFAC low-frequency

gain.

RFG

14

21

22

124

40k

40k

124

124

100µA

VC

20k

24

25

I

Input for adjusting the

equalizer circuit boost amount.

BST

20k

50µA

VC

25

26

I

Input for adjusting the

equalizer circuit boost

frequency with the control

voltage.

VFC

100µA

VC

20k

26

Pin

No.

Symbol I/O Equivalent circuit Description

– 7 –

CXA2571N

27

I

Input for adjusting the

equalizer circuit boost

frequency with external

resistance.

RFC

124

1.0V

27

28

O (VCC + GND)/2 voltage output.VC

25

150k

150k

28

29

O

RFDC amplifier output. This

pin serves as the eye pattern

check point.

RFDC

30

I

RFDC amplifier gain

adjustment. The gain is

adjusted by the external

resistance value connected

between this pin and Pin 29.

RFDCI

124

VC

1mA

1.5k

124

29

30

Pin

No.

Symbol I/O Equivalent circuit Description

Loading...

Loading...