Sony CXA2161R Datasheet

CXA2161R

I2C Bus Compatible Audio Video (AV) Switch & Electronic Volume Control

Description

The Sony CXA2161R is an Audio/Video switch

designed primarily for application in Digital Set Top

Boxes. It provides video and audio routing from the

digital encoder source to the TV and VCR scart (peritelevision) connectors. In addition, the TV audio

output has a programmable volume control. The chip

is programmed by means of an I2C interface and can

operate from a single or dual power supply.

Target specifications: Canal+, BSkyB, TPS, NorDig,

and ECCA Euro-Box

Features

Supply

• Single: 0V, +5V, +12V

• Dual: 0V, –5V, +5V and +12V

(Low number of external parts required)

Video

• 2 scart switching (VCR, TV)

• VCR input supports RGB mode

• Integrated 75Ω drivers for direct video connection

• Y/C mixer with trap for RF modulators

• Switchable clamps on inputs

• Adjustable gain on RGB outputs

• Video output shutdown for low power modes

• Fast blanking switch

• Slow blanking switch for TV and VCR output

• SVHS switch on VCR output

• Y/C auxiliary input

Audio

• Four stereo audio inputs

• Volume control (–56dB to +6dB in 2dB steps)

• Additional switchable gain on audio DAC inputs

• Audio overlay facility

• Volume bypass for TV and Phono outputs

• Mono switching on TV, VCR outputs

• High drive capability (600Ω loads possible)

• Switchable audio limiter function

• Switchable Mono output for RF modulators

• Audio output disable

I2C and Logic

• Fast mode compatible I2C bus

• Function monitor with loop through

• Interrupt output for function monitor

• Logic output pin

• Sync detector for Y/CVBS inputs

Applications

• Digital Set Top Box

• Integrated digital television

Structure

Bipolar silicon monolithic IC

Absolute Maximum Ratings (Ta = 25°C)

unless stated

• Supply voltage VCC 14 V

• Storage temperature Tstg –65 to +150 °C

• Allowable power dissipation

PD 1.1 W

(when mounted on the board)

Operating Conditions

• Single supply 12 ± 0.6 V

5 ± 0.25 V

• Dual supply –5 ± 0.25 V

5 ± 0.25 V

12 ± 0.6 V

• Operating temperature Topr –20 to +75 °C

– 1 –

E00202-PS

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

56 pin LQFP (Plastic)

– 2 –

CXA2161R

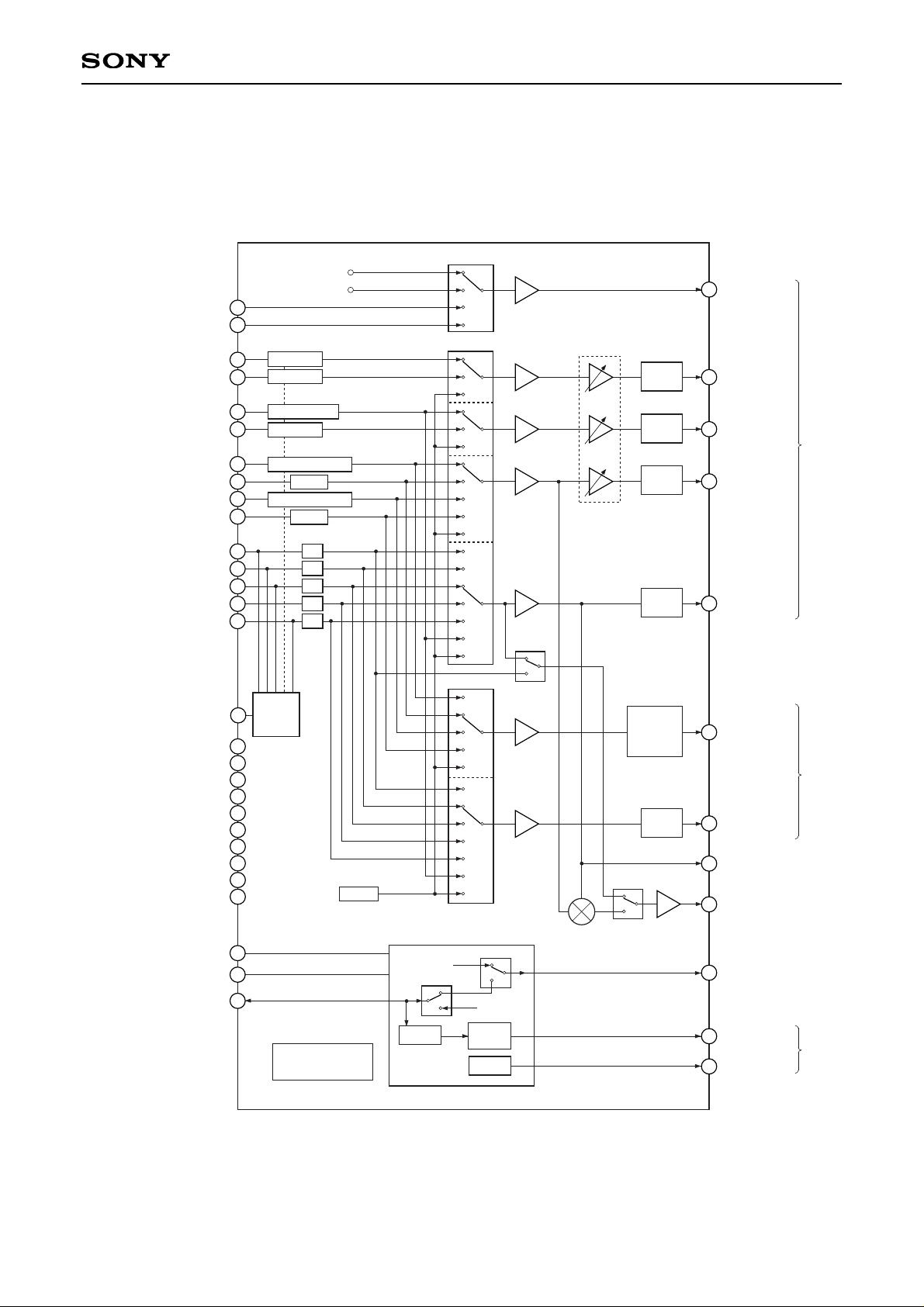

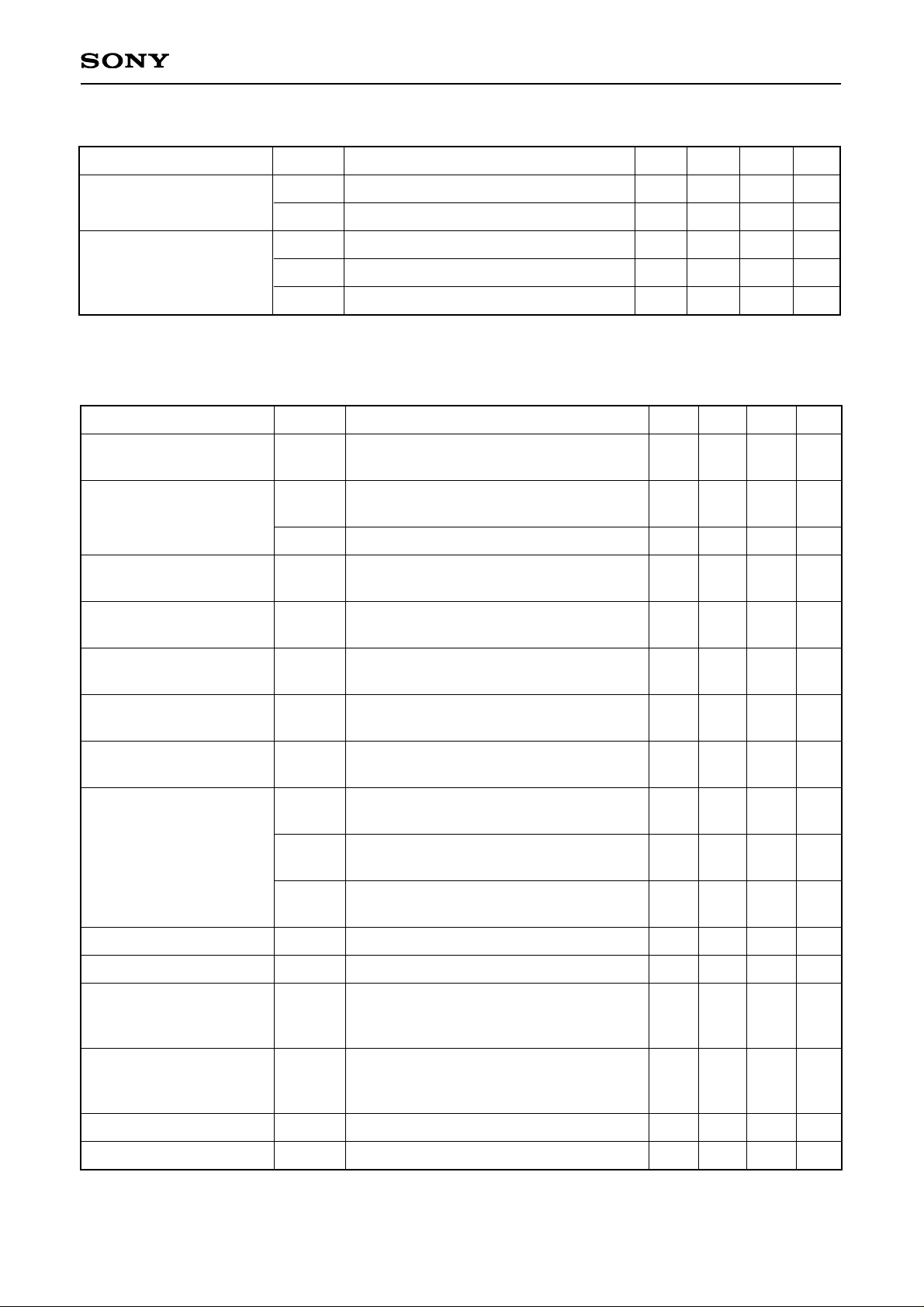

Block Diagram

(1) Video and Digital Section

Note) All video outputs contain 75Ω drivers, except VOUT_7 (Pin 38).

0/6/12V

0/6/12V

2

8

9

11

10

12

13

14

15

18

21

24

33

34

35

36

37

38

39

40

41

43

44

45

46

47

48

49

7

50

6

51

1

5

52

53

3

4

54

55

56

FBLK_SW

VIDEO SWITCH1 (TV)

RGB Gain Control

(+1, 2, 3dB)

VIDEO SWITCH2 (VCR)

DC Restore

DC Restore

DC Restore/Tip

DC Restore/C bias

C bias

DC Restore/C bias

C bias

Clamp Cntl

Tip

Tip

Tip

Tip

Tip

Bias

Mute

Sync

Detect

DC Restore

Monitor

3.3V or 5V

Fast Mode

Compatible

Logic

Interrupt

Control

×2

Output

disable

×2

Output

disable

×2

Output

disable

×2

Output

disable

×2

Output

disable &

Bi-drection

Control

×2

Output

disable

×2

MIX_SW

MIX_SW

TV_FBLK

FBLK_IN1

+3.5V

0V

FBLK_IN2

VIN_1

VIN_2

VIN_3

VIN_4

VIN_5

VIN_6

VIN_7

VIN_13

VIN_8

VIN_9

VIN_10

VIN_11

VIN_12

SYNC_ID

AUD_BIAS

VID_BIAS

+5V/12V_V

CCA

–5V_GNDA

+5V_DIG

GND_DIG

+5V_VOUT

GND_VID

+5V_VID

+12V_DIG

SDA

SCL

FNC_VCR

DIG

VCR

DIG BLUE

VCR BLUE

DIG GREEN/CVBS

VCR GREEN

DIG RED/CHROMA

DIG CHROMA

VCR RED/CHROMA

AUX CHROMA

DIG CVBS/LUMA

DIG CVBS/LUMA

VCR CVBS/LUMA

TV CVBS

AUX Y/CVBS

VCR

Typical Connection

↓

Typical Connection

↓

VOUT_1

TV BLUE

VOUT_2

TV GREEN

TV

VCR

RF MOD

TV

MICRO

VOUT_3

TV RED/C

VOUT_4

TV CVBS/Y

VOUT_5

VCR CHROMA

VOUT_6

VCR CVBS/Y

TRAP

VOUT_7

(CVBS)

FNC_TV

INTRUPT

LOGIC

– 3 –

CXA2161R

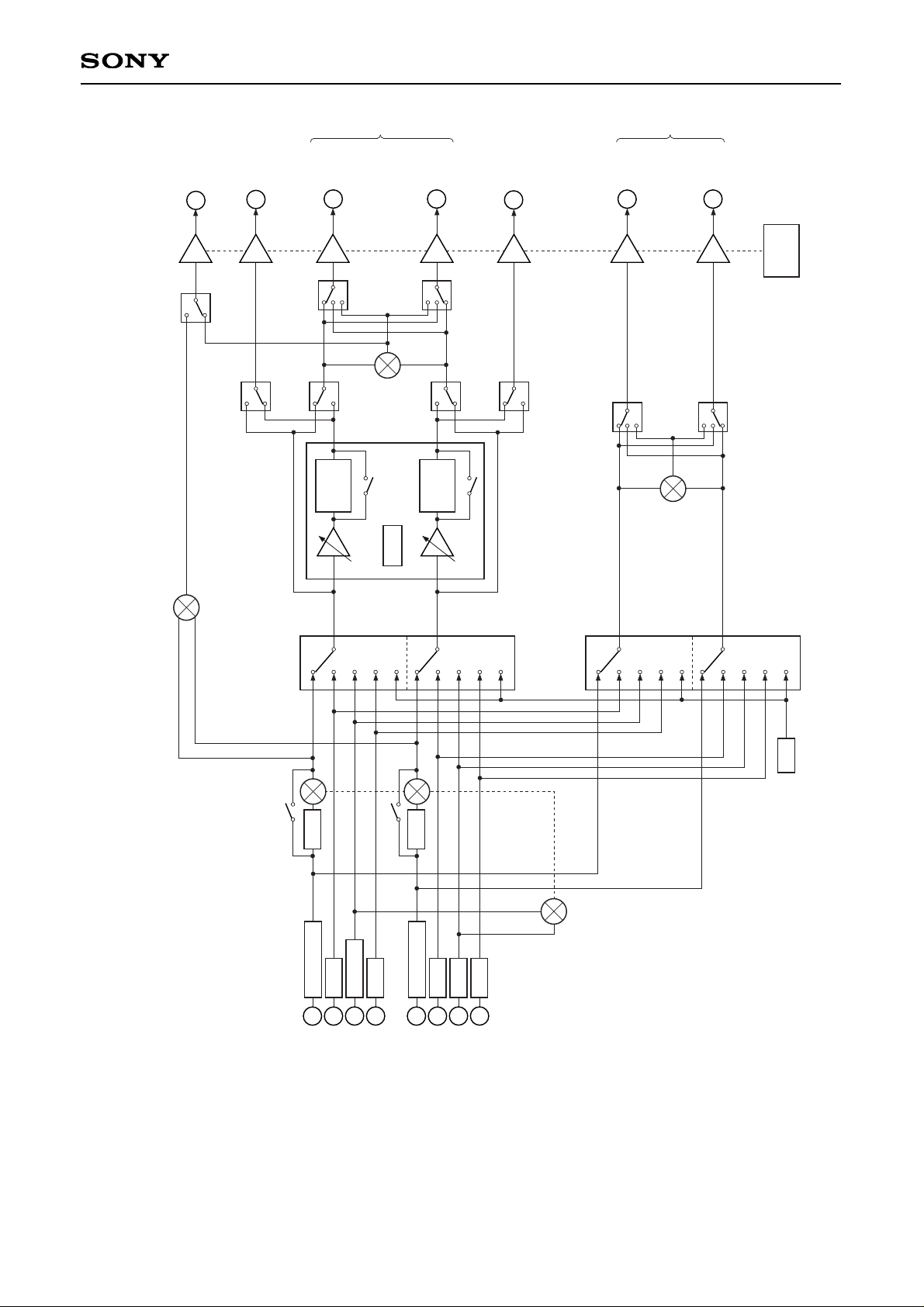

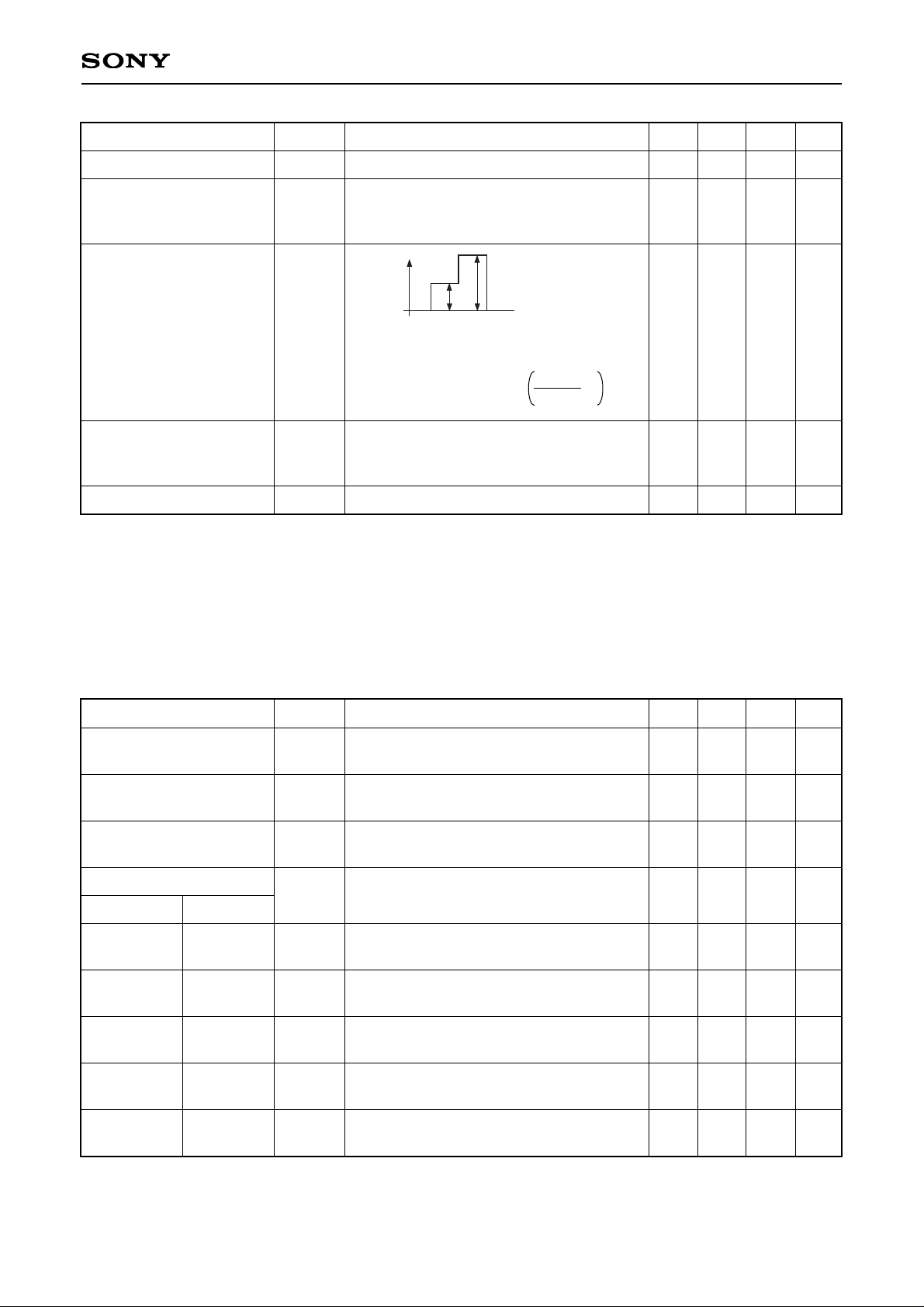

(2) Audio section

27

6dB

Vol Bypass

(TV)

AUDIO SWITCH1 (TV)

17

20

23

26

25

30

31

32

42

–6/–3/0/+3dB

–6dB

–6dB

–6/–11dB

16

19

22

29

–6/–3/0/+3dB

–6dB

–6dB

–6dB

AUDIO SWITCH2 (VCR)

RIN_1 (DIG)

MONO

To RF Modulator

PHONO_R

RTV

LTV

PHONO_L

ROUT1

LOUT1

VCR

RIN_2 (VCR)

RIN_3 (TV/OVERLAY)

RIN_4 (AUX)

LIN_1 (DIG)

LIN_2 (VCR)

LIN_3 (TV/OVERLAY)

LIN_4 (AUX)

–16dB

Overlay on/off

–16dB

Tone mix

Overlay on/off

Bias

Mute

Limiter

2.2Vrms

Output

Disable

2dB

Limiter

2.2Vrms

2dB

Volume Control

+6 to –56dB

ZCD

Vol Bypass

(Phono)

Mono Switch

Mono and

R/L Switch

Mono and R/L

Switch

Vol Bypass

(TV)

Vol Bypass

(Phono)

6dB

6dB

6dB

6dB

6dB

6dB

TV

28

– 4 –

CXA2161R

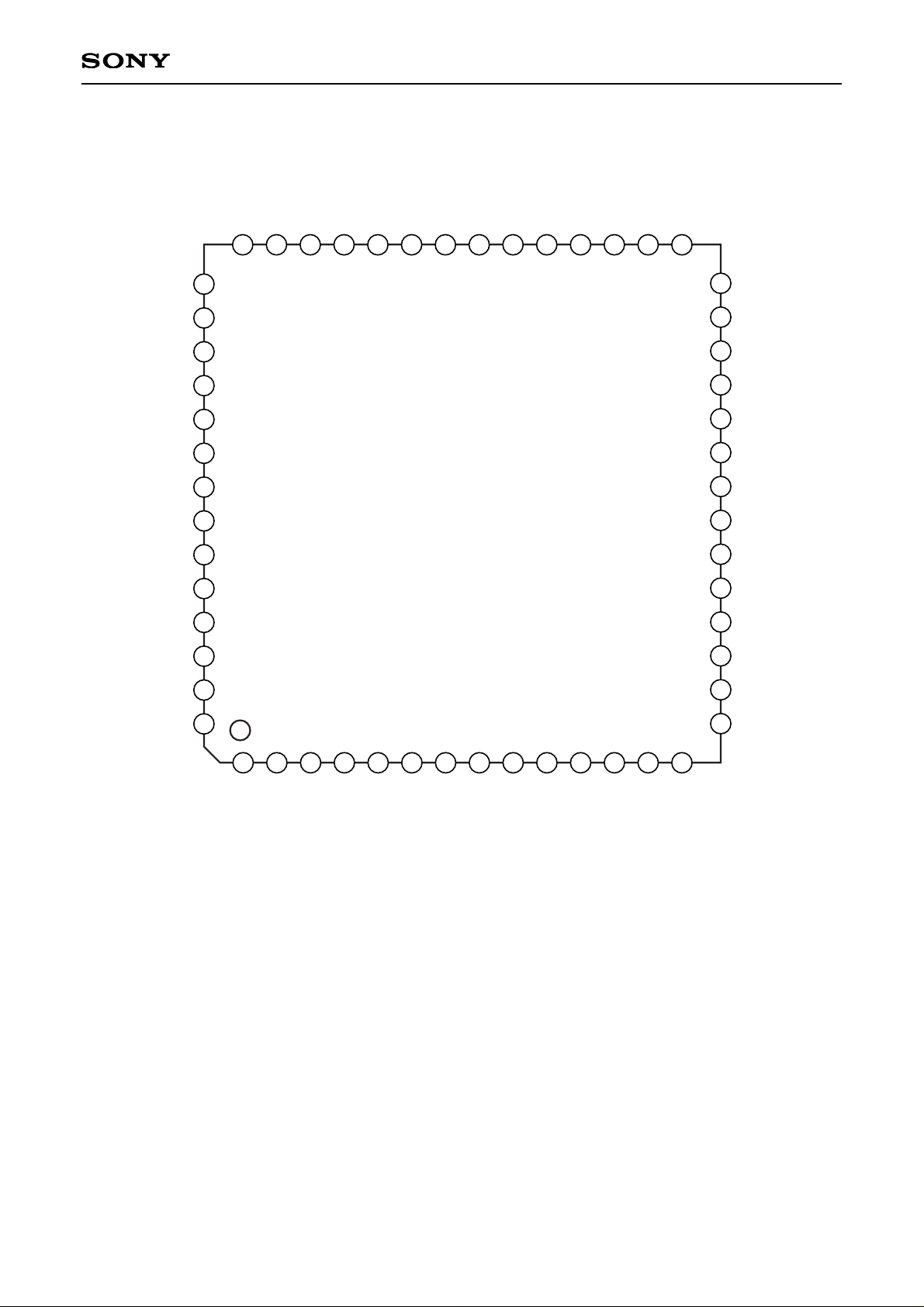

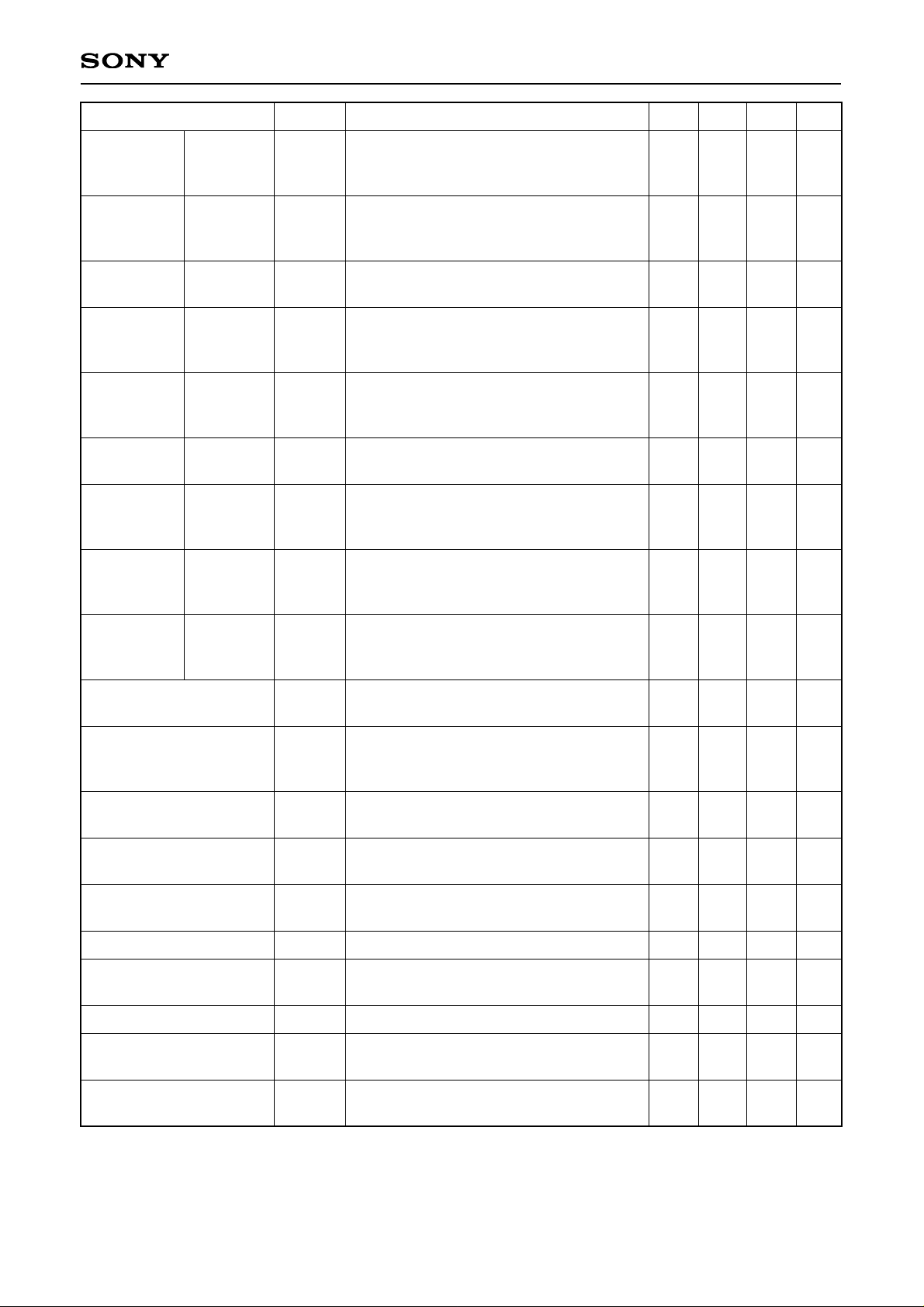

Pin Configuration

VOUT_4

+5V_VOUT

VOUT_3

VOUT_2

VOUT_1

+5V_VID

VID_BIAS

VIN_1

VIN_3

VIN_5

VIN_6

VIN_8

VIN_9

VIN_12

VIN_13

SYNC_ID

VIN_11

VIN_10

VIN_7

VlN_4

VIN_2

GND_DIG

TV_FBLK

FBLK_IN1

FNC_TV

FBLK_IN2

FNC VCR

+5V_DIG

RIN_4

VOUT_5

GND_VID

VOUT_6

VOUT_7

TRAP

INTRUPT

SCL

SDA

LOGIC

MONO

PHONO_R

PHONO_L

LlN_4

1 2 3 4 5 6 7 8 9 11 12 13 14

15

16

17

18

19

21

22

23

24

25

26

27

28

293132333435363738394142

43

44

45

46

47

48

49

50

51

52

53

54

55

56

10

20

3040

ROUT1

LOUT1

RTV

LTV

+5V/12V_V

CCA

RIN_1

LIN_1

–5V_GNDA

RIN_2

LIN_2

AUD_BIAS

RIN_3

LIN_3

+12V_DIG

– 5 –

CXA2161R

Pin Description

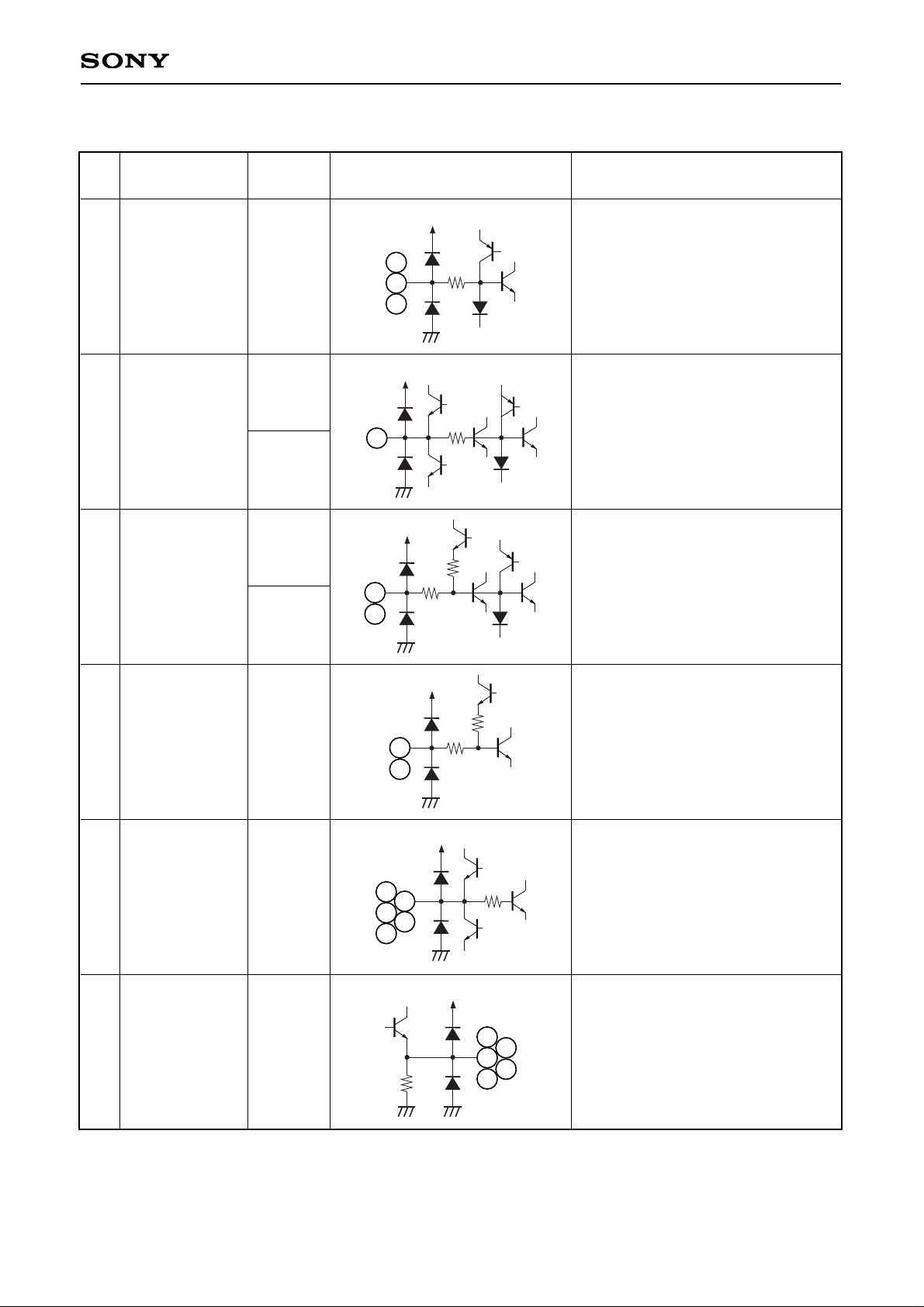

Pin

No.

Symbol

Pin

voltage [V]

Equivalent circuit Description

VCC

150

6

7

50

VIN_1

VIN_2

VIN_4

2.4

RGB signal inputs

50

7

6

VCC

150

51

VIN_3

2.4

2.35

RGB signal input

or

CVBS/Luminance signal input

51

VCC

150

20k

5

52

VIN_5

VIN_7

2.4

3.0

RGB signal inputs

or

Chrominance signal inputs

52

5

VCC

150

20k

1

53

VIN_6

VIN_13

3.0

Chrominance signal inputs

53

1

150

3

4

54

55

56

V

CC

VIN_8

VIN_9

VIN_10

VIN_11

VIN_12

2.35

CVBS/Luminance signal inputs

54

55

4

3

56

VCC

39

43

45

46

47

12k

VOUT_1

VOUT_2

VOUT_3

VOUT_4

VOUT_6

—

RGB/CVBS signal outputs

(See description of operation for pin

voltages)

47

46

45

43

39

– 6 –

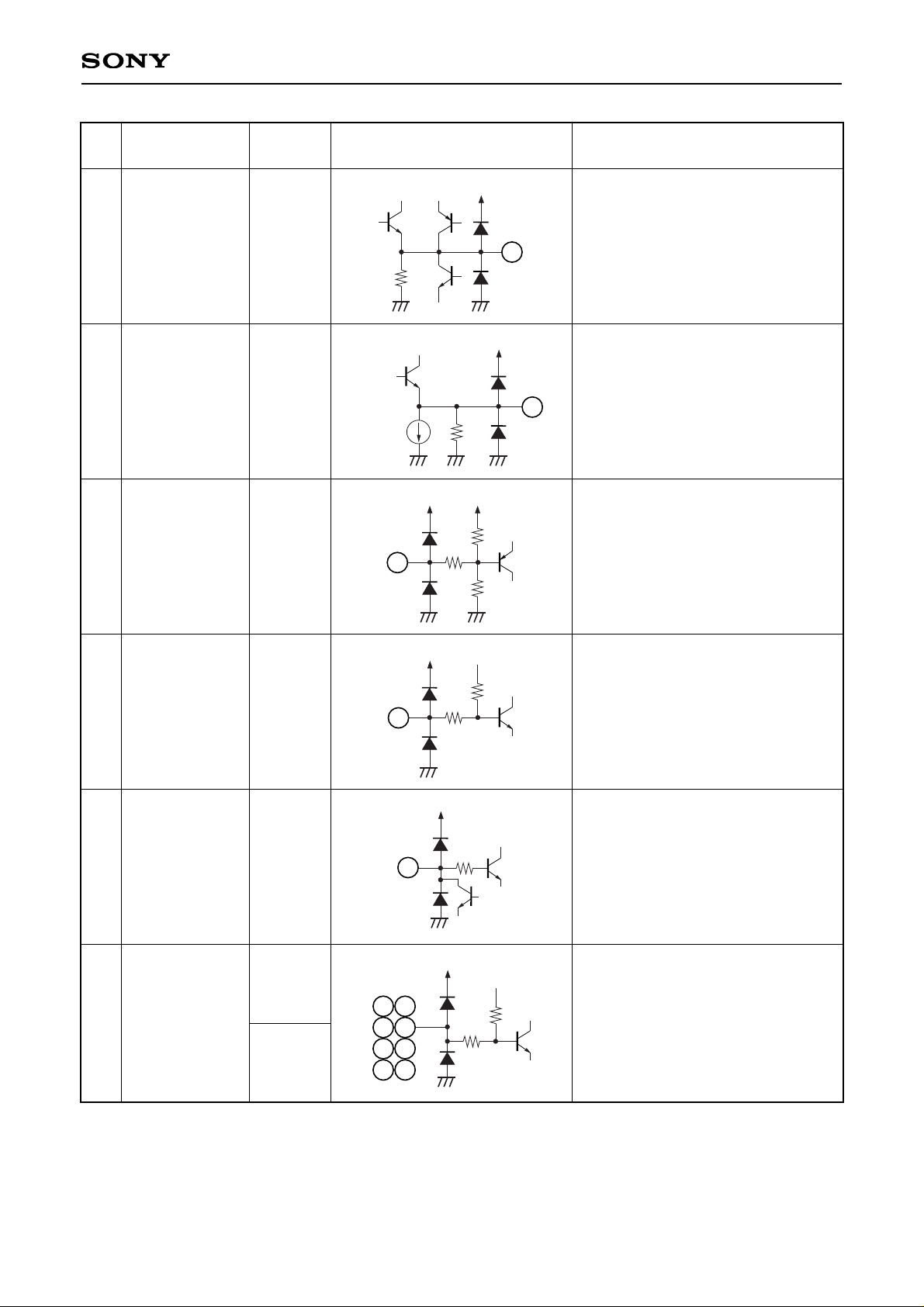

CXA2161R

Pin

No.

Symbol

Pin

voltage [V]

Equivalent circuit Description

VCC

12k

41

VOUT_5

1.8

Chrominance signal output

41

VCC

12k

0.75mA

38

VOUT_7

0.4

Typically

RF modulator signal output

Minimum load resistance = 20kΩ

38

VCC VCC

150

40.8k

18.3k

49

VID_BIAS

0.9

Internal reference bias for video

circuits. A capacitor is connected

from this pin to GND.

Typically 100nF

49

VCC

200

2k

37

TRAP

2.3

Connects trap circuit for subcarrier

37

VCC

150

2

SYNC_ID

2.5

Sync detect circuit time constant,

resistor and capacitor connection pin

2

VCC

VCC/2

60k

60k

16

17

19

20

22

23

29

42

LIN_1

RIN_1

LIN_2

RIN_2

LIN_3

RIN_3

LIN_4

RIN_4

6.0

(Single)

0.0

(Dual)

Audio signal inputs

22

23

19

20

16

17

29

42

– 7 –

CXA2161R

Pin

No.

Symbol

Pin

voltage [V]

Equivalent circuit Description

VCC

20k

25

26

27

28

30

31

32

LTV

RTV

LOUT1

ROUT1

PHONO_L

PHONO_R

MONO

6.0

(Single)

0.0

(Dual)

Audio signal outputs

Capacitor

connected to GND.

(Typically 22µF)

Connected

directly to GND.

25

26

27

28

30

31

32

VCC VCC

150

40k

40k

18

AUD_BIAS

Internal reference

bias for audio

circuits.

18

VCC

150

10

12

FBLK_IN1

FBLK_IN2

—

Fast blanking signal inputs

10

12

VCC

9

TV_FBLK

—

Fast blanking signal output

9

13

120k

FNC_VCR

—

SCART function pin 8 input/output to

VCR

13

VCC

11

FNC_TV

—

SCART function pin 8 output to TV

11

6.0

(Single)

0.0

(Dual)

– 8 –

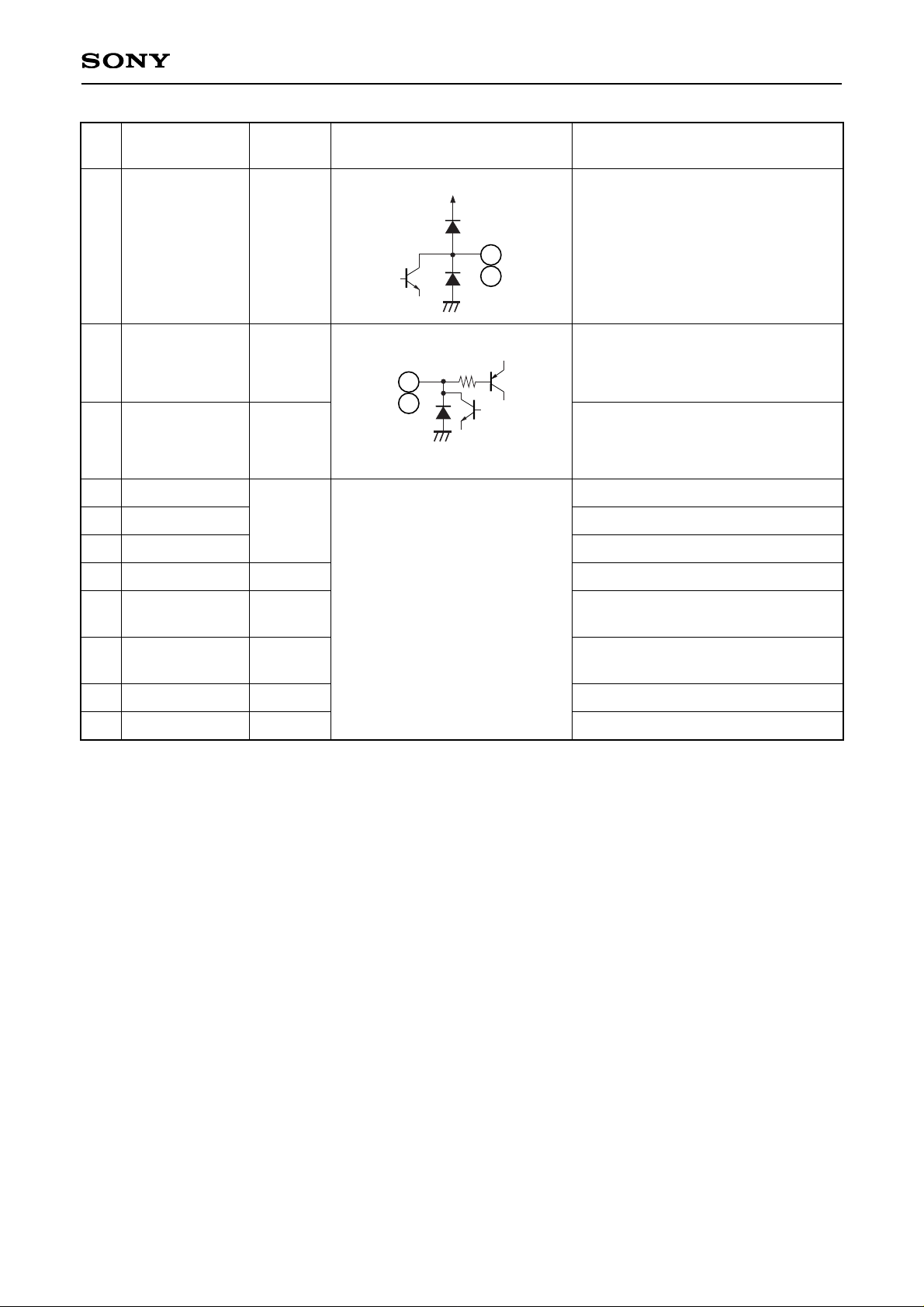

CXA2161R

Pin

No.

Symbol

Pin

voltage [V]

Equivalent circuit Description

VCC

33

36

LOGIC

INTRUPT

—

Open collector logic outputs

Typically connect to +5V through

10kΩ resistor.

33

36

8k

34

35

I2C bus clock line

I2C bus data line

+5V_DIG

+5V_VOUT

+5V_VID

+12V_DIG

–5V_GNDA

+5V/+12V_VCCA

GND_DIG

GND_VID

5.0

12.0

–5.0 (Dual)

0.0 (Single)

5.0 (Dual)

12.0 (Single)

0.0

0.0

Digital supply

Video output supply

Video supply

Digital supply

Audio supply or Audio ground

Audio supply

Digital ground

Video ground

14

44

48

15

21

24

8

40

SCL

—

—

35

SDA

34

– 9 –

CXA2161R

Electrical Characteristics

Nominal conditions (Ta = 25°C)

+12 supply, no signal, no load

+5 supply, no signal, no load

+12 supply, no signal, no load

+5 supply, no signal, no load

–5 supply, no signal, no load

Current consumption

(Single ended supply)

Current consumption

(Dual supply)

ICC1

ICC2

ICC3

ICC4

ICC5

—

—

—

—

—

22

50

2

70

20

45

80

6

115

45

mA

mA

mA

mA

mA

Item Symbol Conditions Min. Typ. Max. Unit

Video System

Nominal conditions single supply (Ta = 25°C, +5V/12V_VCCA = +12V, –5V_GNDA = 0V,

+5V_VID = +5V, +5V_VOUT = +5V, +5V_DIG = +5V, GND_VID = 0V)

Sync tip clamp voltage at

input

Chrominance bias input

voltage

RGB dc restore input

voltage

Sync tip clamp voltage at

output

Chrominance bias output

voltage

RGB dc restore output

voltage

Gain (Vout1 to 6)

Gain (Vout1, 2, 3)

Gain (Vout7) Mixer off

Gain (Vout7) Mixer on

Bandwidth (Vout1 to 6)

Bandwidth (Vout7)

Mixer on – No trap

components

Input dynamic range

Output dynamic range

Vclmp1

Cbias1

Cbias2

RGB1

Vclmp2

Cbias3

RGB2

GVv

GVRGB1

GVRGB2

GVRGB3

GVYC

GVYC

fV3dB

fV3dB

VDRVI

VDRVO

—

—

—

—

—

—

—

5.5

6.5

7.5

8.5

5.5

5.5

15

8

1.4

2.8

2.4

3

2.35

2.4

0.3

1.8

0.6

6.0

7.0

8.0

9.0

6.0

5.75

22

18

—

—

—

—

—

—

—

—

—

6.5

7.5

8.5

9.5

6.5

6.5

—

—

—

—

V

V

V

V

V

V

V

dB

dB

dB

dB

dB

dB

MHz

MHz

Vp-p

Vp-p

Item Symbol Conditions Min. Typ. Max. Unit

Vin3, Vin8, Vin9, Vin10, Vin11, Vin12

inputs. (Vin3 set to CVBS mode) (Fig. 1)

Vin5, Vin7 inputs. Clamps set to

Chrominance bias mode. (Fig. 1)

Vin6, Vin13 inputs. (Fig. 1)

Vin1, Vin2, Vin3, Vin4, Vin5, Vin7 inputs.

(Vin3 & Vin5 set to RGB mode) (Fig. 1)

Vout4, Vout6 outputs (Fig. 1)

Vout3, Vout5 outputs (Fig. 1)

Vout1, Vout2, Vout3 outputs (Fig. 1)

f = 200kHz, 0.3Vp-p input ,

RGB Gain = 0dB (Fig. 2)

f = 200kHz, 0.3Vp-p input ,

RGB Gain = +1dB (Fig. 2)

f = 200kHz, 0.3Vp-p input ,

RGB Gain = +2dB (Fig. 2)

f = 200kHz, 0.3Vp-p input ,

RGB Gain = +3dB (Fig. 2)

f = 200kHz, 0.3Vp-p input (Fig. 2)

f = 200kHz, 0.3Vp-p input (Fig. 2)

0.3Vp-p input, frequency where output

level is –3dB with 200kHz serving as 0dB

(Fig. 2)

0.3Vp-p input, frequency where output

level is –3dB with 200kHz serving as 0dB

(Fig. 2)

200kHz input applied to any video (Fig. 2)

200kHz input applied to any video (Fig. 2)

– 10 –

CXA2161R

Cross talk

S/N ratio

Non-linearity

Differential gain

Differential phase

Vctv

S/NV

Lin

DG

DP

—

—

–3

–3

–3

—

74

0

0

0

–50

—

3

3

3

dB

dB

%

%

deg

Item Symbol Conditions Min. Typ. Max. Unit

f = 4.43MHz, 1Vp-p input (Fig. 2)

Ratio of 0.7Vp-p white video signal to

black line noise. Weighted using CCIR

567. HPF@5kHz, LPF@5MHz. (Fig. 2)

V1 = Pin voltage + 0.5V,

V2 = Pin voltage + 1V

At output, non-linearity = –1 × 100

(Fig. 2)

1.7Vp-p 5-step modulated staircase.

(Chrominance & Burst are 150mVp-p,

4.43MHz) (Fig. 2)

As above.

Input pin V

plus

V1

V2

V2

V1 × 2

Audio System

Unless otherwise stated: input coupling capacitor 1µF; output coupling capacitor 10µF; load 10kΩ.

Nominal conditions single supply (Ta = 25°C, +5V/12V_VCCA = +12V, –5V_GNDA = 0V, +5V_VID = +5V,

+5V_VOUT = +5V, +5V_DIG = +5V, GND_VID = 0V)

Nominal conditions dual supply (Ta = 25°C, +5V/12V_VCCA = +5V, –5V_GNDA = –5V, +5V_VID = +5V,

+5V_VOUT = +5V, +5V_DIG = +5V, GND_VID = 0V)

Input/output pin voltage

(Single supply)

Input/output pin voltage

(Dual supply)

Output pin voltage when

disabled (Dual supply)

Input

Rin1 or Lin1

Rin1 or Lin1

Rin1 or Lin1

Rin1 or Lin1

Rin1 or Lin1

VAPIN1

VAPIN2

VAPIN3

GVA1

GVA2

GVA3

GVA4

GVA5

—

—

—

–0.5

2.5

5.5

8.5

–0.5

6

0

0

0

3

6

9

0

—

—

—

0.5

3.5

6.5

9.5

0.5

V

V

V

dB

dB

dB

dB

dB

Item Symbol

Conditions

Min. Typ. Max. Unit

No signal, no load (Fig. 3)

No signal, no load (Fig. 3)

No signal, no load (Fig. 3)

f = 1kHz, 0.5Vrms input. TV volume set to

0dB, RIN_1/LIN_1 amplifier = –6dB (Fig. 4)

f = 1kHz, 0.5Vrms input. TV volume set to

0dB, RIN_1/LIN_1 amplifier = –3dB (Fig. 4)

f = 1kHz, 0.5Vrms input. TV volume set to

0dB, RIN_1/LIN_1 amplifier = 0dB (Fig. 4)

f = 1kHz, 0.5Vrms input. TV volume set to

0dB, RIN_1/LIN_1 amplifier = +3dB (Fig. 4)

f = 1kHz, 1Vrms input. TV volume set to

0dB, RIN_1/LIN_1 amplifier = –6dB (Fig .4)

Output

TV or

Phono

TV or

Phono

TV or

Phono

TV or

Phono

VCR

Gain

– 11 –

CXA2161R

Rin1 + Lin1

Rin1 + Lin1

Rin2, 3, 4 or

Lin2, 3, 4

Rin1 + Lin1

Rin2 + Lin2

Rin3 + Lin3

Rin4 + Lin4

Rin2, 3, 4

Lin2, 3, 4

Rin2 + Lin2

Rin3 + Lin3

Rin4 + Lin4

Rin3

Lin3

Audio frequency response

Frequency bandwidth

Distortion

Input dynamic range

Rin1, 2, 3, 4/Lin1, 2, 3, 4

Cross talk

(Channel separation)

DC offset

Input impedance

Rin1, 2, 3, 4/Lin1, 2, 3, 4

Output impedance

Phase difference

S/N ratio

GVA6

GVA7

GVA9

GVA8

GVA10

GVA11

GVA12

GVA13

GVA14

FAF

FBWA1

THD

VdA1

VctA

Voff

Zin1

Zout

Vpda

S/NA

–0.5

–0.5

–0.5

–0.5

–0.5

–0.5

–0.5

–5.5

–0.5

–0.3

—

—

2.5

—

–30

—

—

—

80

0

0

0

0

0

0

0

–5

0

0

1

0.005

2.9

—

0

120

10

0.05

93

0.5

0.5

0.5

0.5

0.5

0.5

0.5

–4.5

0.5

0.3

—

0.2

—

–76

30

—

—

—

—

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

MHz

%

Vrms

dB

mV

kΩ

Ω

deg

dB

Item Symbol

Conditions

Min. Typ. Max. Unit

f = 1kHz, 0.5Vrms stereo input. TV volume

set to 0dB, RIN_1/LIN_1 amplifier = –6dB.

TV mono switch on. (Fig. 4)

f = 1kHz, 1Vrms stereo input. TV volume

set to 0dB, RIN_1/LIN_1 amplifier = –6dB.

(Note 1) (Fig. 4)

f = 1kHz, 1Vrms input, TV volume set to

0dB (Fig. 4)

f = 1kHz, 1Vrms stereo input. RIN_1/LIN_1

amplifier = –6dB. VCR mono switch on.

(Fig 4)

f = 1kHz, 1Vrms stereo input. TV volume

set to 0dB (Note 2) (Fig 4)

f = 1kHz, 1Vrms input (Fig 4)

f = 1kHz, 1Vrms stereo input. VCR mono

switch on. (Fig 4)

f = 1kHz, 1Vrms input, Lin3 has no signal

Audio overlay enabled with –11dB

attenuation at input RIN_3 (Fig 4)

f = 1kHz, 1Vrms input

Audio overlay enabled. (Fig 4)

0.3Vp-p input. Output/input gain at 30kHz

with 1kHz serving as 0dB (Fig 4)

0.3Vp-p input; frequency where output

level is –3dB with 1kHz serving as 0dB.

No load attached (Fig 4)

f = 1kHz, 0.5Vrms, unweighted response;

LPF@400Hz, HPF@80kHz (Fig 4)

f = 1kHz, RIN_1/LIN_1 input amplifier set

to –6dB. Dual supply mode used. (Fig 4)

f = 1kHz, 1Vrms input on one input,

measure on any other audio output (Fig 4)

Offset voltage between input and output

(excluding any external series resistor)

(excluding any external series resistor)

f = 1kHz, 1Vrms input to two channels.

Phase difference of stereo output measured

f = 1kHz, 1Vrms input (at 0dB volume).

HPF@20Hz, LPF@20kHz. (Fig 4)

TV

(mono mix)

MONO

TV or

Phono

VCR

(mono mix)

MONO

VCR

VCR

(mono mix)

RTV,

ROUT1,

Phono_R

LTV,

LOUT1,

Phono_L

Note 1) Mono switch set to mix of Rin1 & Lin1 inputs.

Note 2) Mono switch set to mix of RTV & LTV after volume control.

– 12 –

CXA2161R

Electronic Volume Control

Volume attenuation step

Mute

TV I/P MUTE or

VCR I/P MUTE

Audio limiter level

AEVC

Amute

Alimit

1.6

—

—

2

–90

6.5

2.4

–76

—

dB

dB

Vp-p

Item Symbol

Conditions

Min. Typ. Max. Unit

f = 1kHz, 0.5Vrms input. Set by I2C (Fig 4)

f = 1kHz, 1Vrms input (Fig 4)

f = 1kHz, 2.5Vrms input. Measure TVp-p

output with limiter switched on. (Fig 4)

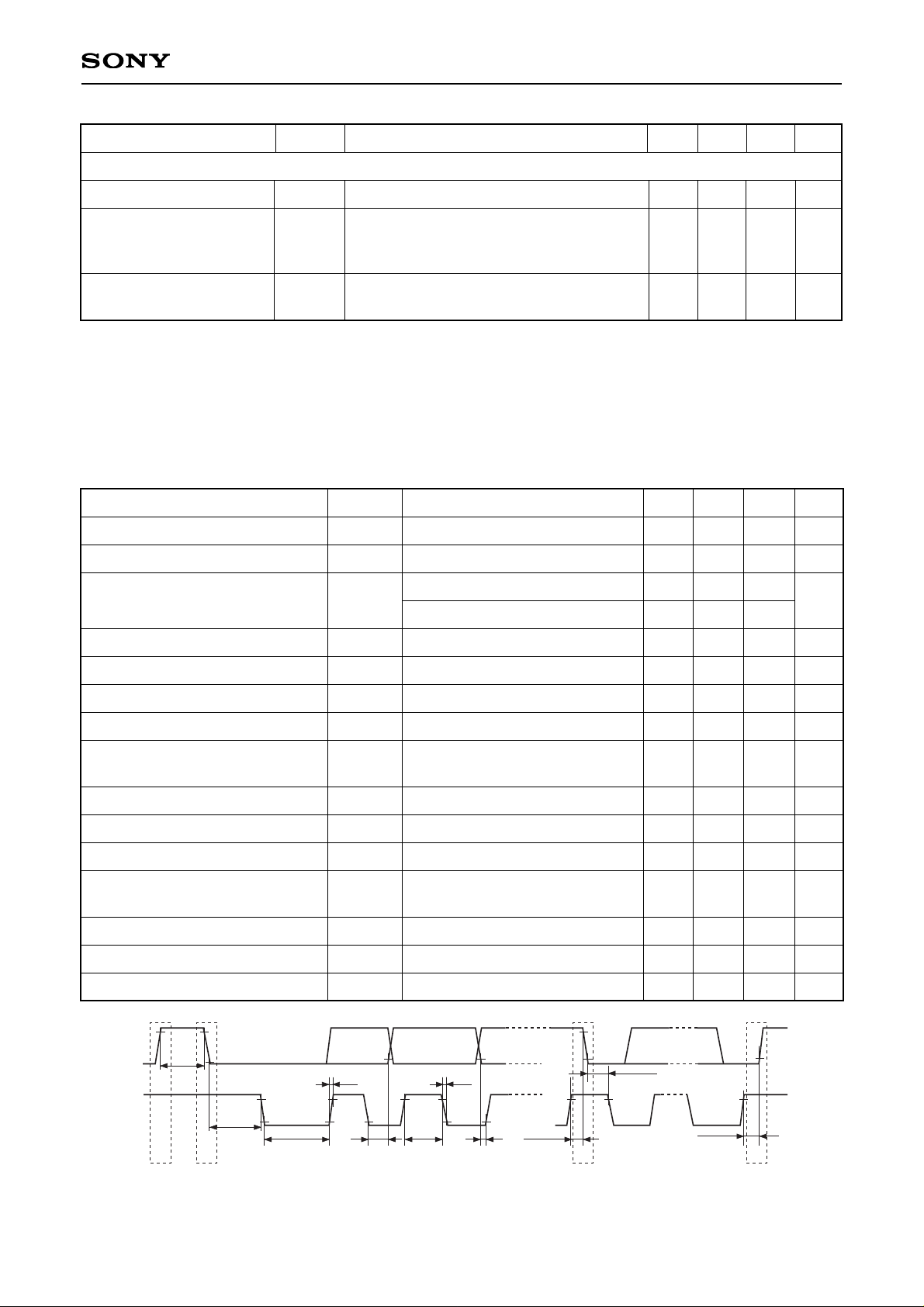

Digital Characteristics

I2C Interface

The I2C interface is compliant with Philips I2C Fast Mode specification (date April 1995). The interface is also

capable of interfacing to +3.3V or +5V logic levels.

SymbolItem Condition Min. Typ. Max. Unit

VIH

VIL

VOL

VHYST

tSP

tF

tSCL

tBUF

tHD;STA

tLOW

tHIGH

tSU;SDA

tHD;DAT

tSU;DAT

tSU;STO

High level input voltage

Low level input voltage

Low level output voltage

Hysteresis of schmitt trigger input

Spike suppression

Fall time for SDA line

SCL clock frequency

Bus free time between a stop and

start

Hold time (repeated start condition)

Low period of SCL clock

High period of SCL clock

Setup time for a repeated start

condition

Data hold time

Data setup time

Setup time for stop condition

With SDA, 3mA current supplied

With SDA, 6mA current supplied

VIH – VIL

400pF bus load

I2C Bus line requirement

I2C Bus line requirement

I2C Bus line requirement

I2C Bus line requirement

I2C Bus line requirement

I2C Bus line requirement

I2C Bus line requirement

I2C Bus line requirement

I2C Bus line requirement

2.3

0

0

0

—

—

—

0

1.3

0.6

1.3

0.6

0.6

0

100

0.6

—

—

—

—

0.5

—

—

—

—

—

—

—

—

—

—

—

5.5

1.5

0.4

0.6

—

50

300

400

—

—

—

—

—

0.9

—

—

V

V

V

V

ns

ns

kHz

µs

µs

µs

µs

µs

µs

ns

µs

tBUF

tHD;STA

SP

tLOW

tR

tHIGH tSU;DAT

tSU;STA

tSU;DAT

P

Sr

tSU;STO

tF

tHD;STA

– 13 –

CXA2161R

Logic/Interrupt Output

These outputs are open collector type and normally connected to +5V through a 10kΩ resistor.

Output low voltage DIGVOUTL — 0.15 0.4 V

Item Symbol

Conditions

Min. Typ. Max. Unit

IOL = 1mA

Loading...

Loading...