LCD Signal Processor (Gamma Correction)

Description

The CXA2111R is a signal processor IC developed

for LCD panels. Gamma correction, gain and bias,

etc., can be adjusted using the I2C bus and external

adjustment pins. The output of this IC is ideal as the

input of the CXA2112R (LCD sample-and-hold

driver IC), and the sample-and-hold position, etc.,

can also be adjusted using the I2C bus.

CXA2111R

52 pin LQFP (Plastic)

Features

• Independent R, G and B gamma adjustment

• Three-point gamma gain and position adjustment

(one white side point, two black side points)

• Independent R, G and B output amplifier gain and

bias adjustment

• Various I2C bus-based controls and adjustment of

various characteristics by external DC input

• Input signal clamp function (variable clamp voltage)

• Black side limiter adjustment

• CXA2112R adjustment output

• Precharge output (for CXA2112R)

• High frequency response

• High slew rate output

Applications

• Liquid crystal projectors

• Compact liquid crystal monitors

Structure

Bipolar silicon monolithic IC

Absolute Maximum Ratings

• Supply voltage VCC –0.3 to +5.5 V

• Input voltage VI –0.3 to VCC + 0.3 V

• Storage temperature Tstg –65 to +150 °C

• Allowable power dissipation

PD 1000 mW

Operating Conditions

• Supply voltage VCC 4.75 to 5.25 V

• Digital input voltage high VH 2.2 to VCC V

• Digital input voltage low VL 0 to 0.8 V

• Operating temperature Topr –20 to +70 V

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

– 1 –

E97448-PS

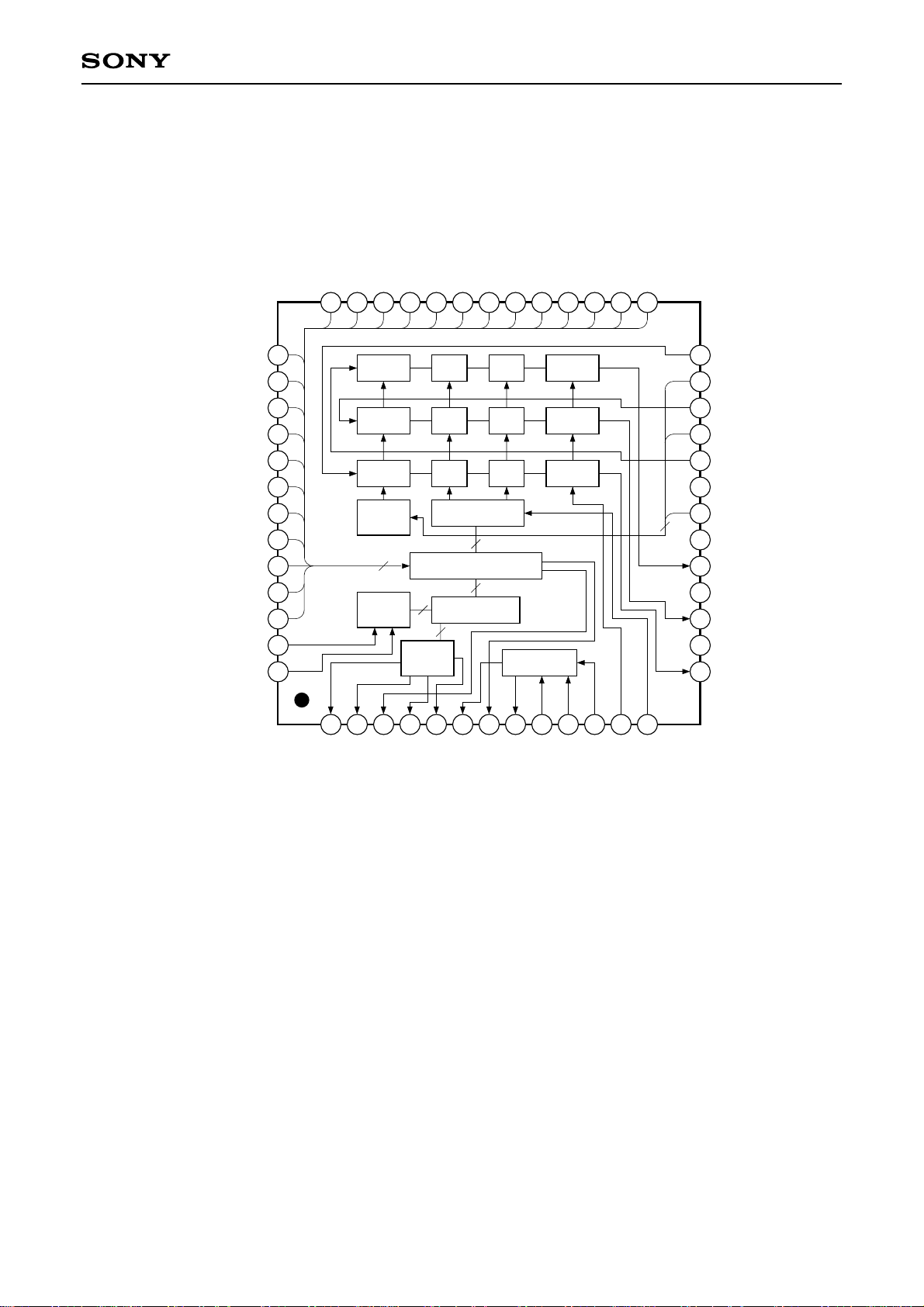

Pin Configuration and Block Diagram

GAMR_B2P

39

GAMG_B1P

GAMB_B1P

37

38

GAMB_WHP

GAMR_B1P

35

36

GAMR_WHP

GAMG_WHP

33

34

AMPGBIAS

AMPBBIAS

32

31

AMPBGAIN

AMPRBIAS

30

29

AMPRGAIN

AMPGGAIN

27

28

CXA2111R

GAMG_B2P BIN

GAMB_B2P CLPLEV

GAMR_WHG GIN

GAMG_WHG ATT

GAMB_WHG RIN

GAMR_B1G V

GAMG_B1G CLPPLS

GAMB_B1G GND

GAMR_B2G ROUT

GAMG_B2G PVCC

GAMB_B2G GOUT

40

41

42

43

44

45

46

47

48

49

50

SCL PGND

51

SDA BOUT

52

CLAMP DRIVERAMP

CLAMP DRIVERAMP

CLAMP DRIVERAMP

CLAMP

Control

Input

I/F

1

2

3

DLY_CNT

POS_CNT2

POS_CNT1

γ • AMP Adjust

Output

I/F

5

4

INV_CNT

DIR_CNT

γ

γ

γ

DAC/Control

6bit × 25

I2C Bus

6

7

SIDOUT

DATEST

PRG/SID

9

8

V33

SIDLEV

10

PRGPLS

11

PRGLEV

12

BLKLIM

13

23

20

18

16

GAMOFF

26

25

24

22

21

19

17

15

14

CC

– 2 –

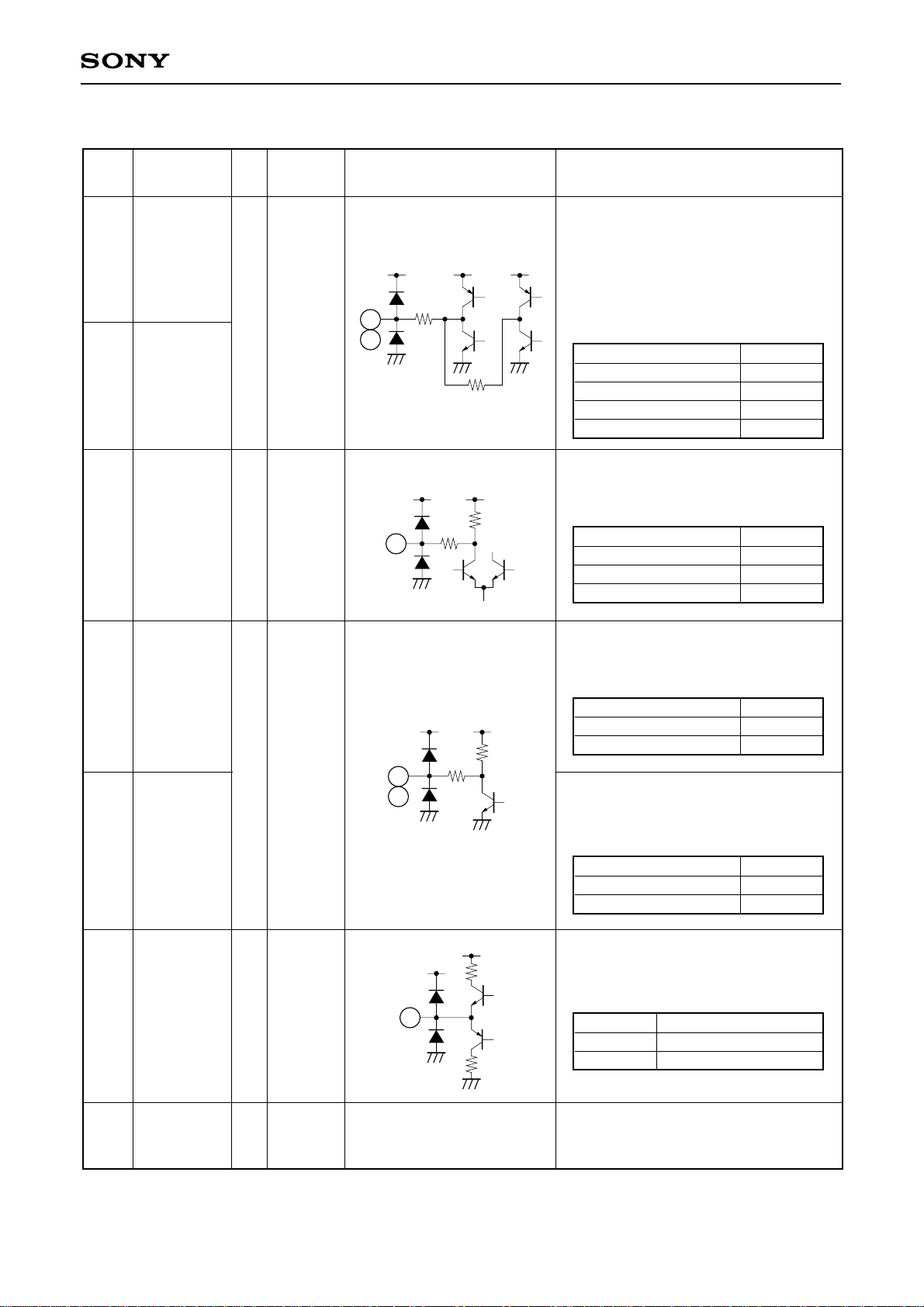

Pin Description

CXA2111R

Pin

No.

1

2

3

Symbol

POS_CNT1

POS_CNT2

DLY_CNT

I/O

O

O

Typical

pin voltage

0 to 5V

(4 value)

3 to 5V

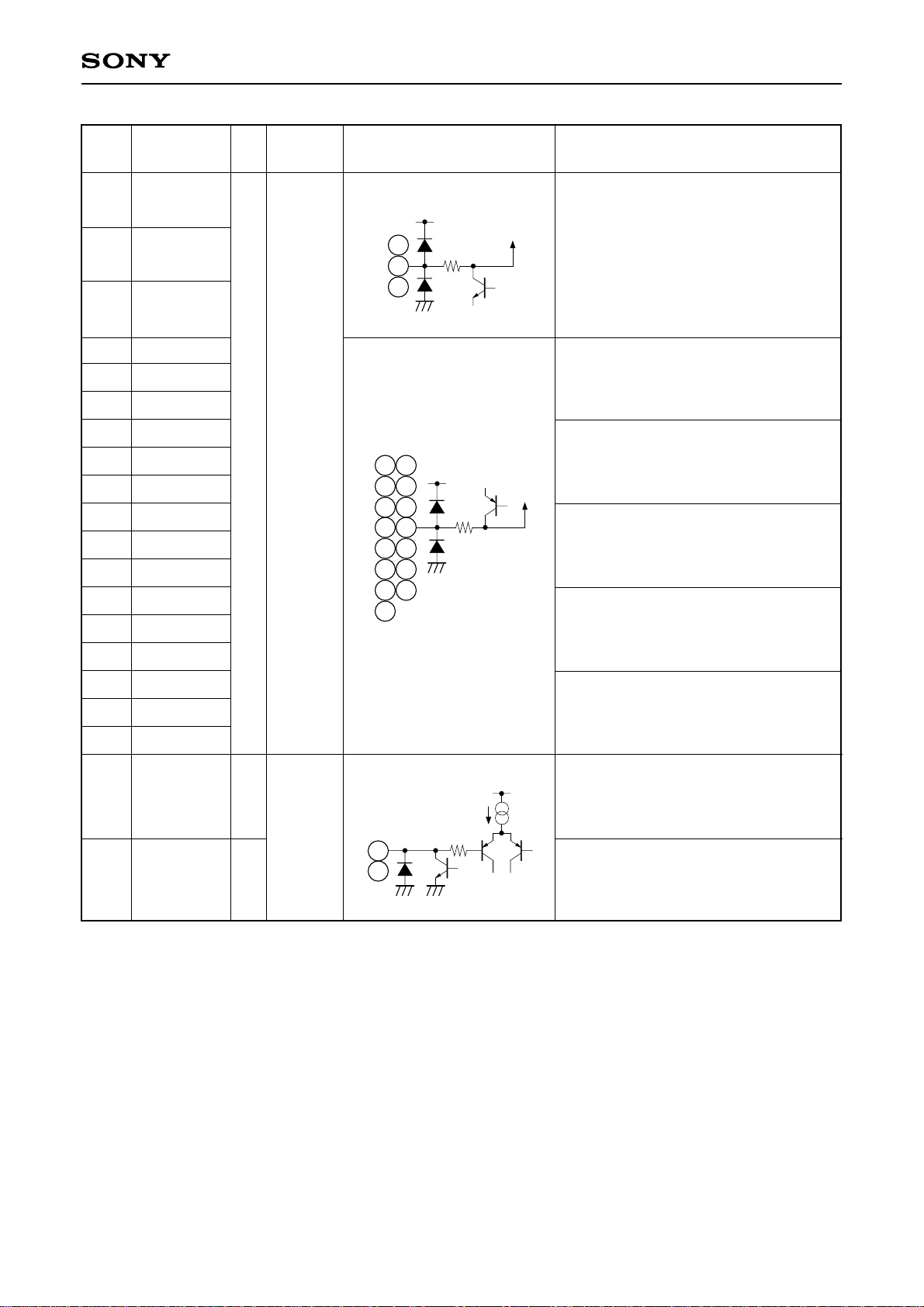

Equivalent circuit

V

CC

1

2

300

VCC

300

3

VCC VCC

70k

VCC

25k

Description

CXA2112R control.

The sample-and-hold position is

determined by the I2C data.

POS_CNT1 is the low-order 4-value

output and POS_CNT2 is the highorder 4-value output for a total of 16value control.

I2C data input (2 bits)

00

01

10

11

Pin output

L

↓

↓

H

CXA2112R control.

The clock delay time is controlled by

output analog value using I2C data.

I2C data input (6 bits)

all 0

↓

all 1

Pin output

5V

↓

3V

4

5

6

DIR_CNT

INV_CNT

SIDOUT

O

(0V/5V)

2.3 to 3.3V

O

L/H

CXA2112R control.

The scan direction is determined by

the I2C data.

CC

300

VCC

20k

V

4

5

I2C data input (1 bit)

0

1

CXA2112R control.

Pin output

H

L

The clock polarity is determined by the

I2C data.

I2C data input (1 bit)

0

1

VCC

VCC

Pin output

H

L

Output for CXA2112R.

This pin outputs the precharge signal.

6

Pin 10 input

H

L

Pin 6 output

Level controlled by Pin 11

Level controlled by Pin 9

7

DATEST

DAC test output.

Set the I2C data to "1". This pin is

normally open.

– 3 –

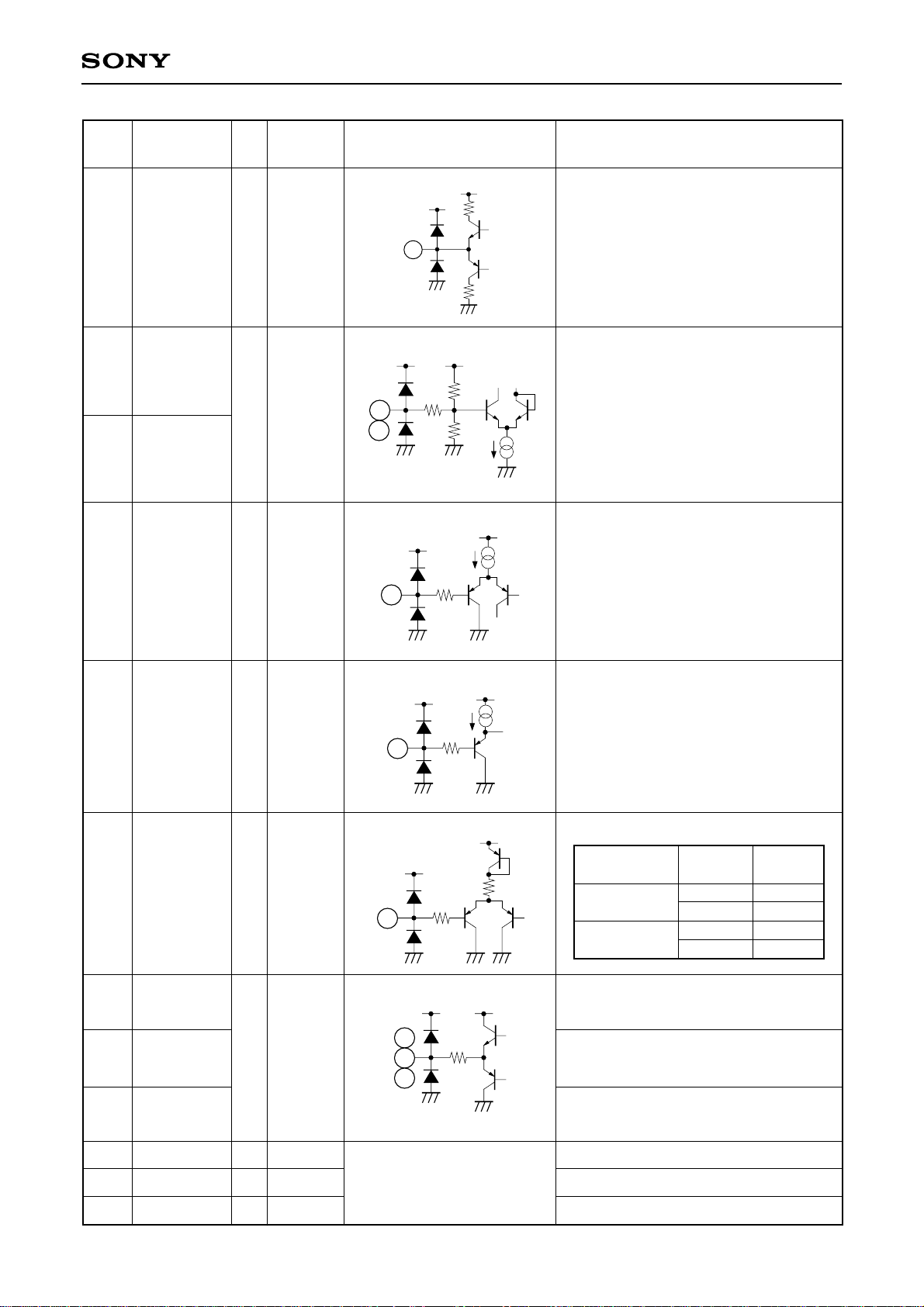

CXA2111R

Pin

No.

8

9

11

10

Symbol

V33

SIDLEV

PRGLEV

PRGPLS I

Typical

I/O

pin voltage

O

I

L: 0 to 0.8V

H: 2.2 to 5V

3.3V

0 to 5V

L/H

Equivalent circuit

VCC

8

VCC

9

11

10

VCC

50k

VCC

300

VCC

50k

75k

VCC

25µ

Description

Output for CXA2112R.

This pin outputs 3.3V.

These pins determine the Pin 6 output

level.

See Pin 6.

100µ

This pin determines the Pin 6 output.

See Pin 6.

Set to low or high when using SIDOUT

(Pin 6) as a DC output.

BLKLIM

12

13

GAMOFF I

BOUT

14

GOUT

16

ROUT

18

I

1 to 5V

L: 0 to 0.8V

H: 2.2 to 5V

O

1.8 to 3.3V

L/H

13

12

18

14

16

VCC

VCC

PV

1.6k

300

CC

50

VCC

VCC

PVCC

GND

750µ

50k

Output black level (low level side) limit

voltage control.

Apply voltage of 1V DC or more.

Gamma characteristics ON/OFF setting.

I2C data input

(1bit)

0

1

Pin 13 input

H

L

H

L

γ mode

γ ON

γ OFF

γ OFF

γ OFF

B channel output.

G channel output.

R channel output.

15

17

19

PGND

PVcc

GND

GND

5V

GND

GND.

5V

GND.

– 4 –

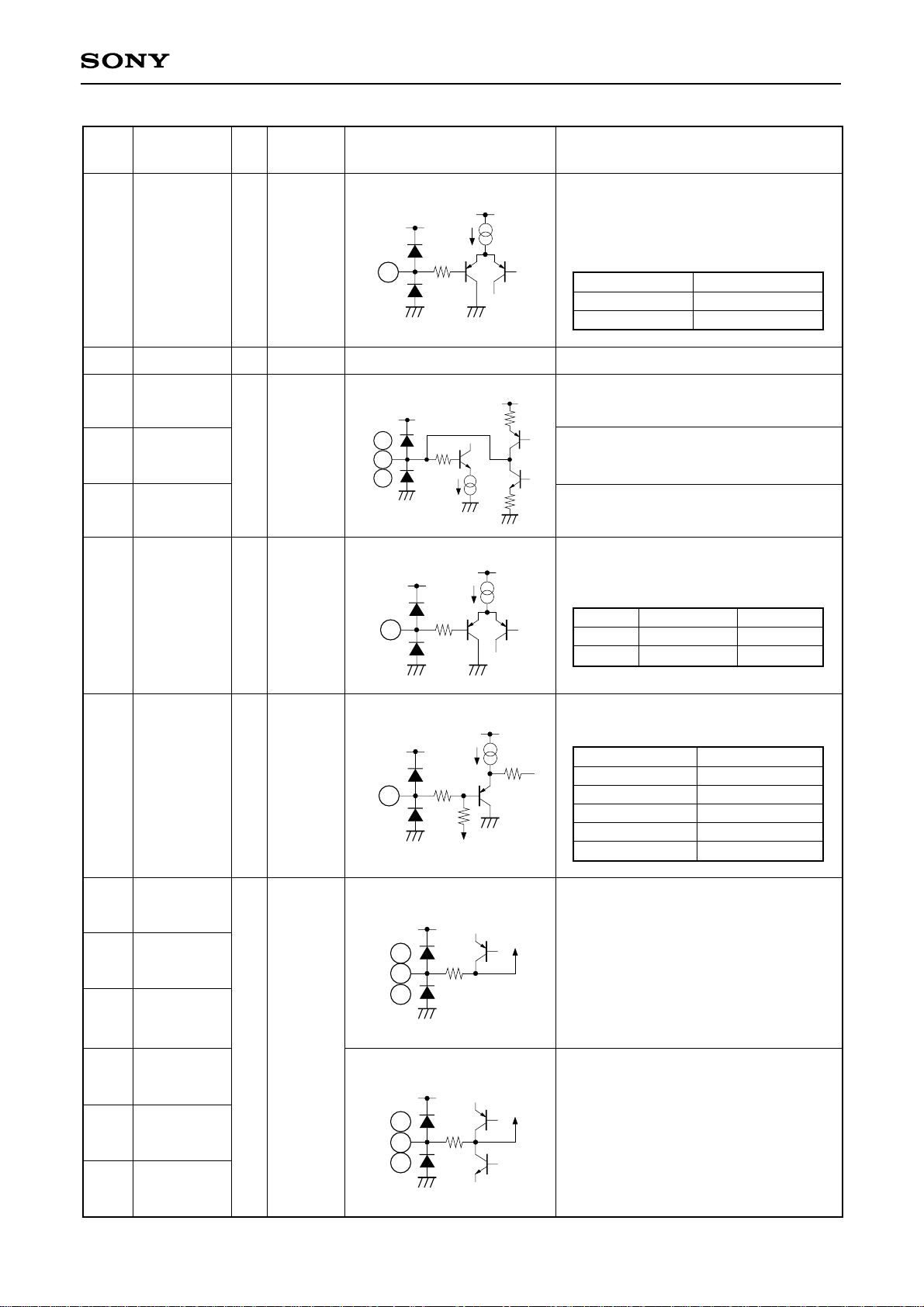

CXA2111R

Pin

No.

20

21

22

24

26

23

Symbol

CLPPLS

Vcc

RIN

GIN

BIN

ATT

Typical

I/O

pin voltage

I

L: 0 to 0.8V

H: 2.2 to 5V

5V

1.5 to 3.5V

I

I

L: 0 to 0.8V

H: 2.2 to 5V

L/H

L/H

Equivalent circuit

VCC

20

22

24

26

23

300

VCC

300

VCC

300

VCC

170µ

VCC

50µ

VCC

50µ

Description

Input signal clamp pulse input.

Set to low when not using the clamp

function.

Pin input

H

L

Clamp function

ON

OFF

5V

R channel input.

G channel input.

B channel input.

Input signal gain control.

This pin also supports 2Vp-p input.

Pin input

H

L

Clamp block gain

0dB

–6dB

Signal level

For 1Vp-p

For 2Vp-p

25

27

28

29

30

31

32

CLPLEV

AMPRGAIN

AMPGGAIN

AMPBGAIN

AMPRBIAS

AMPGBIAS

AMPBBIAS

I

I

0 to 5V

0 to 5V

25

27

28

29

30

32

31

VCC

VCC

VCC

60k

20k

2.5V

25k

25k

VCC

50µ

2.5V

2.5V

Clamp voltage control during clamp

operation.

Pin input

5V

↓

2.5V (open)

↓

0V

Clamp voltage

2.5V

↓

2.0V

↓

1.5V

Amplifier gain control.

Independent control for R, G and B.

Equivalent to 2.5V input when open.

Amplifier bias control.

Independent control for R, G and B.

Equivalent to 2.5V input when open.

– 5 –

CXA2111R

Pin

No.

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

Symbol

GAMR_WHP

GAMG_WHP

GAMB_WHP

GAMR_B1P

GAMG_B1P

GAMB_B1P

GAMR_B2P

GAMG_B2P

GAMB_B2P

GAMR_WHG

GAMG_WHG

GAMB_WHG

GAMR_B1G

GAMG_B1G

GAMB_B1G

I/O

I

Typical

pin voltage

0 to 5V

Equivalent circuit

VCC

33

34

35

43

44

45

46

47

48

49

50

36

37

38

39

40

41

42

25k

VCC

25k

2.5V

2.5V

Description

Gamma white position control.

Independent control for R, G and B.

Equivalent to 2.5V input when open.

Gamma black 1 position control.

Independent control for R, G and B.

Equivalent to 2.5V input when open.

Gamma black 2 position control.

Independent control for R, G and B.

Equivalent to 2.5V input when open.

Gamma white gain control.

Independent control for R, G and B.

Equivalent to 2.5V input when open.

Gamma black 1 gain control.

Independent control for R, G and B.

Equivalent to 2.5V input when open.

48

49

50

51

52

GAMR_B2G

GAMG_B2G

GAMB_B2G

SCL

SDA

I/O

I

L/H

(0V/5V)

51

52

Gamma black 2 gain control.

Independent control for R, G and B.

Equivalent to 2.5V input when open.

VCC

I2C bus clock input.

50µ

4k

I2C bus data input.

– 6 –

Loading...

Loading...