Sony CXA2078Q Datasheet

CXA2078Q

I2C Bus-Compatible Audio/Video Switc h with Electronic Volume

Description

The CXA2078Q is an I2C programmable audio,

video switch designed for set top box applications. It

interfaces from digital encoder sources to TV, VCR

and auxilliary scart connectors.

Features

• 3 scart independent audio/video switching (TV, VCR,

AUX)

• 0 to –63dB volume control with click noise reduction

• 5 stereo audio inputs

• I2C control with two address setting

• Scart Function Switching input and output

• Scart Fast Blanking for OSD

• RF modulator output with Y/C mix option

• On-chip +12V to +9V voltage regulator

• 4 logic outputs

64 pin QFP (Plastic)

Applications

Audio/Video switch featuring I2C bus compatibility

for set top box

Structure

Bipolar silicon monolithic IC

Absolute Maximum Ratings

• Supply voltage VCC 12 V

• Operating temperature Topr –20 to +75 °C

• Storage temperature Tstg –65 to +150 °C

• Allowable power dissipation

PD 500 mW

Operating Conditions

• Supply voltage +10.7 to +12 V

• Operating voltage 9 ± 0.5 V

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

– 1 –

E97843-PS

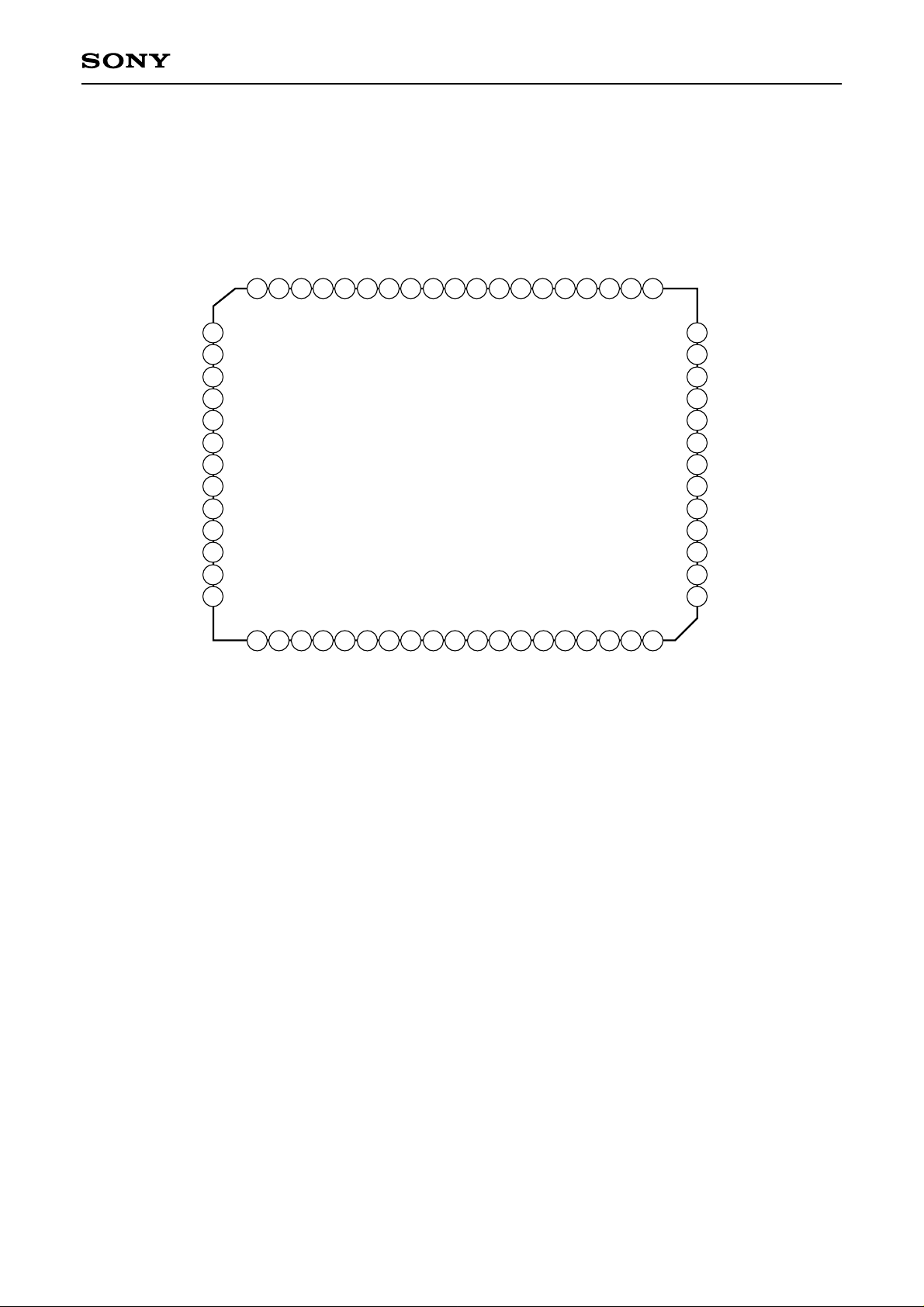

Pin Configuration

CXA2078Q

CC

VOUT2

FBLK_OUT

VOUT1

CC_12V

V

VREG_9V

VREG_BASE

VIDEO_V

CC

RIN5

FBLK_IN2

LIN5

VIN1

RIN1

VIN3

52

53

54

55

56

57

58

59

60

61

62

63

64

51

1

RTV

50

2

LIN1

LTV

VOUT3

49

48

4

3

VIN5

BIAS_VIDEO

DIG_V

VOUT4

47

5

VIN9

FNC_VCR

LOG_1

46

6

VIN6

LOG_3

LOG_2

45

44

8

7

VIN10

FNC_AUX

DIG_GND

LOG_4

43

41

42

9

10

11

SCL

VIDEO_GND

FBLK_IN1

LIN4

HW MUTE

40

39

13

12

SDA

ADR

AUDIO_GND

FNC_TVA

37

38

14

15

VIN7

TRAP

RIN4

FNC_TVB

35

36

17

16

LIN2

RIN2

VIN11

MONO

34

18

VIN2

VOUT8

33

19

RIN3

32

ROUT1

31

VOUT5

30

LOUT1

29

VOUT6

28

ROUT2

27

VOUT7

26

LOUT2

25

AUDIO_V

24

VIN12

23

BIAS_AUDIO

22

VIN8

21

LIN3

20

VIN4

CC

– 2 –

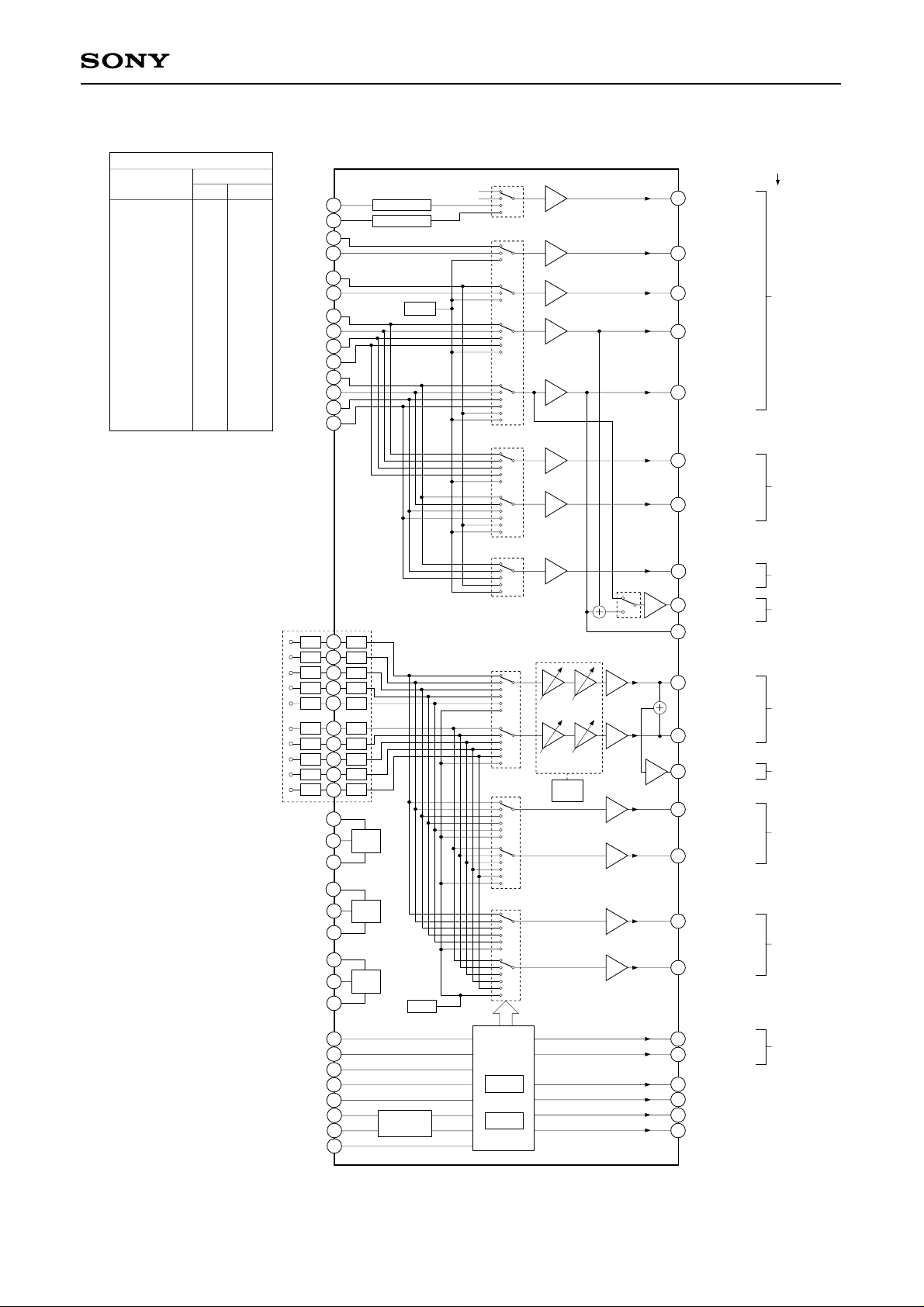

Block Diagram

CXA2078Q

TYPICAL CONFIGURATION

SOURCE

AUX

ENC

DIGITAL (OSD)

AUX

DIGITAL (OSD)

AUX

DIGITAL (OSD)

DIGITAL (NO OSD)

VCR

AUX

DIGITAL (OSD)

DIGITAL (NO OSD)

VCR

AUX

(OSD = On-Screen Display)

MODE1 MODE2

BLUE

BLUE

GREEN

GREEN

RED

RED

CVBS

CVBS

CVBS

CVBS

OUTPUT

CVBS

CHROMA

CHROMA

CHROMA

CHROMA

LUMA

LUMA

LUMA

LUMA

FBLK_IN1

FBLK_IN2

VIN10

VIN11

VIN12

RIN1

RIN2

RIN3

RIN4

RIN5

LIN1

LIN2

LIN3

LIN4

LIN5

V

CC_12V

VREG_BASE

VREG_9V

VIN1

VIN2

VIN3

VIN4

VIN5

VIN6

VIN7

VIN8

VIN9

41

60

62

18

64

20

2

6

14

22

4

8

16

24

6k

63

6k

15

6k

19

6k

36

6k

59

6k

1

6k

17

6k

21

6k

39

6k

61

55

57

56

Comparator

Comparator

Mute

BIAS

Input attenuation = 6dB

with 6k external resistor.

Att.

Att.

Att.

Att.

Att.

Att.

Att.

Att.

Att.

Att.

9V

REG

FBLK_SW

5V

0V

VIDEO

SWITCH1 (TV)

VIDEO

SWITCH2 (VCR)

VIDEO

SWITCH3 (AUX)

AUDIO

SWITCH1 (TV)

AUDIO

SWITCH2 (VCR)

× 2

× 2

× 2

× 2

× 2

× 2

× 2

Y/C MIXER

VOLUME CONTROL

& MUTE

8dB

1dB

step

step

8dB

1dB

step

step

Z.C.D

Logic

MIX_SW

× 2

× 2

× 2

× 2

× 2

53

FBLK_OUT

VOUT1

54

(BLUE)

52

VOUT2

(GREEN)

50

VOUT3

(RED/CHROMA)

VOUT4

48

(CVBS/LUMA)

31

VOUT5

(CHROMA)

VOUT6

29

(CVBS/LUMA)

VOUT7

27

(CVBS)

VOUT8

33

(CVBS)

35

TRAP

51

RTV

49

LTV

34

MONO

32

ROUT1

30

LOUT1

TYPICAL LOAD

TV

VCR

AUX

RF MOD

TV

RF MOD

VCR

VIDEO_V

BIAS_VIDEO

VIDEO_GND

AUDIO_V

BIAS_AUDIO

AUDIO_GND

DIG_V

DIG_GND

SDA

SCL

ADR

FNC_VCR

FNC_AUX

HW MUTE

58

CC

CC

CC

4.05V

BIAS

3

1

9

25

4.5V

BIAS

23

2

13

47

42

11

10

12

5

7

40

BIAS

4.5V

MONITOR

Mute

AUDIO

SWITCH3 (AUX)

I2C

INTERFACE

LOGIC

P.O.D

× 2

× 2

28

26

38

37

46

45

44

43

ROUT2

LOUT2

FNC_TVA

FNC_TVB

LOG_1

LOG_2

LOG_3

LOG_4

AUX

TV

– 3 –

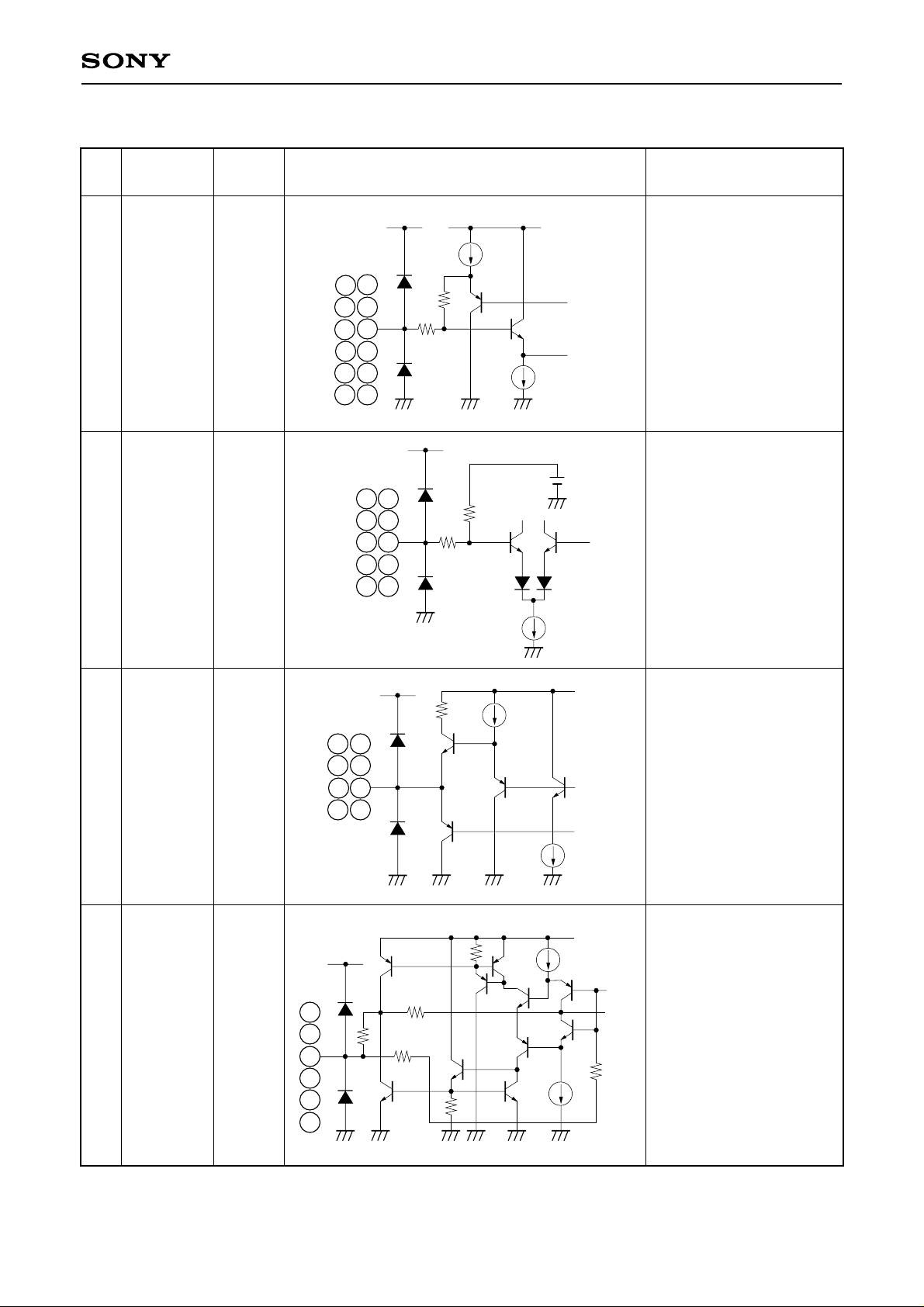

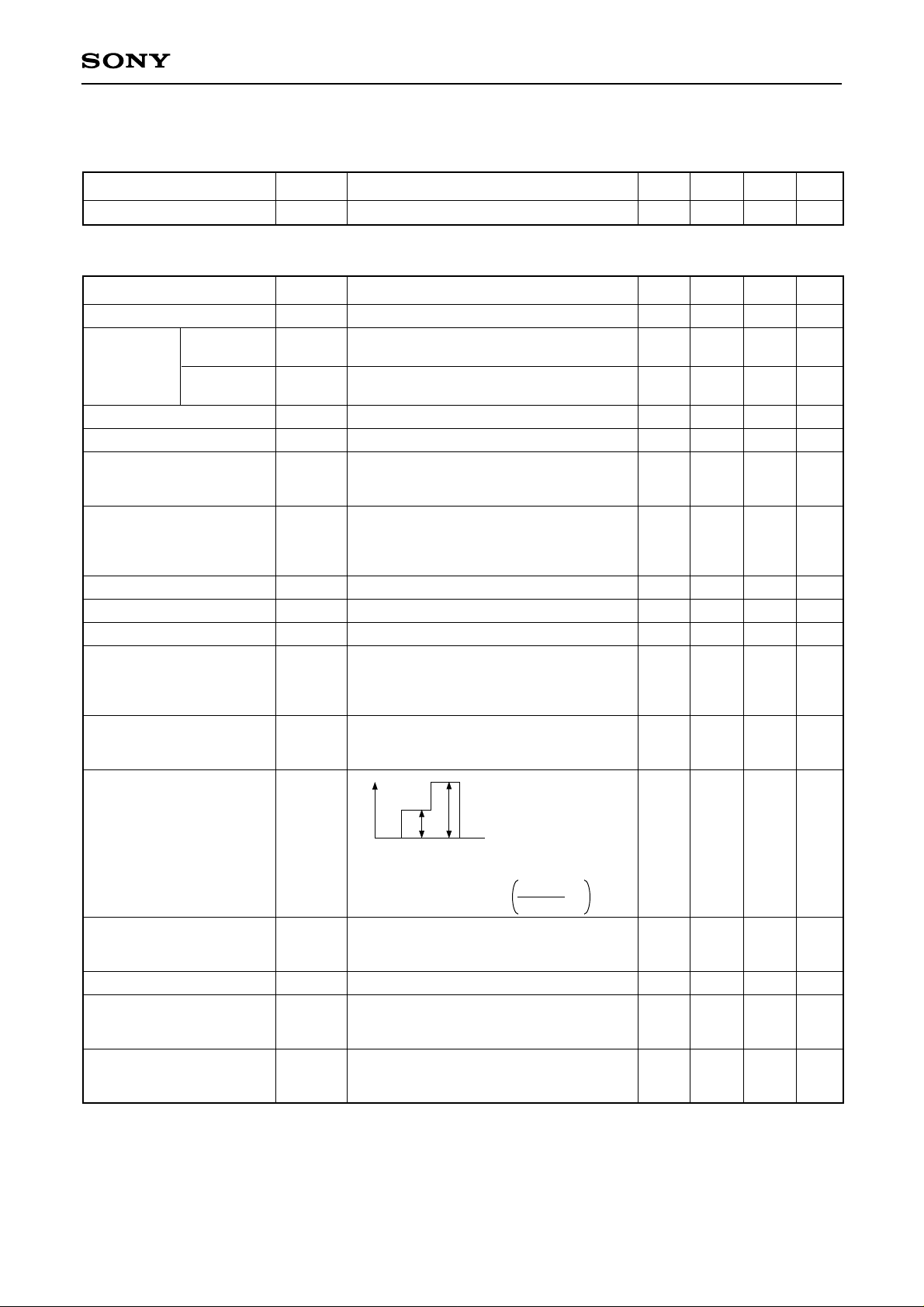

Pin Description

CXA2078Q

Pin

No.

62

18

64

20

2

6

14

22

4

8

16

24

63

15

19

36

59

1

17

21

39

61

Symbol

VIN1

VIN2

VIN3

VIN4

VIN5

VIN6

VIN7

VIN8

VIN9

VIN10

VIN11

VIN12

RIN1

RIN2

RIN3

RIN4

RIN5

LIN1

LIN2

LIN3

LIN4

LIN5

Pin

voltage

4.6V

4.5V

VCC = 12V

14

62

18

22

4

64

8

20

2

16

6

24

VCC = 12V

63

15

19

36

59

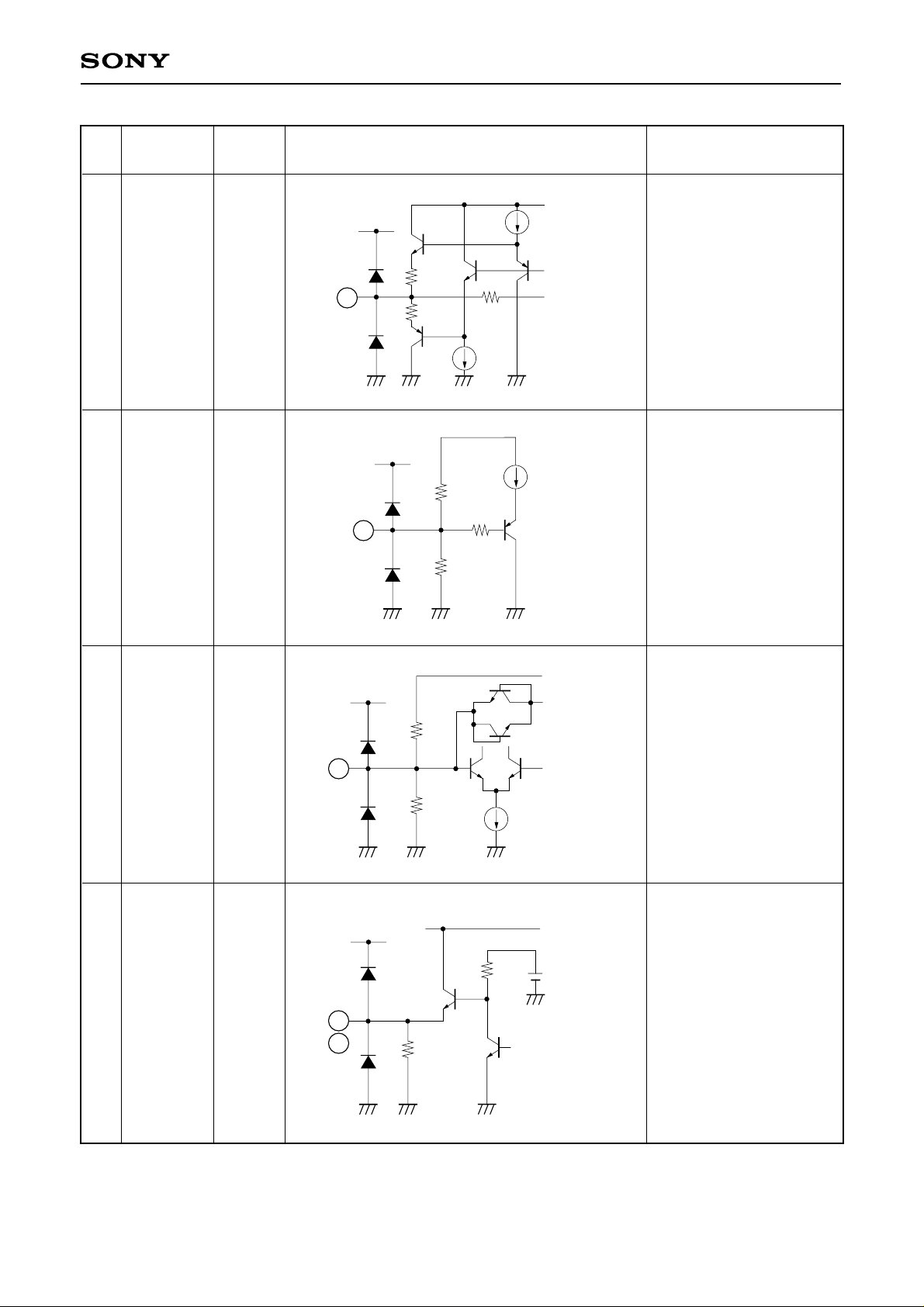

Equivalent circuit Description

VCC = 9V

14µA

120k

Video signal inputs.

Input impedance typically

120kΩ.

Audio signal inputs.

Input impedance typically

60kΩ.

17

61

21

39

147

60µA

4.5V

1

33k

27k

7µA

54

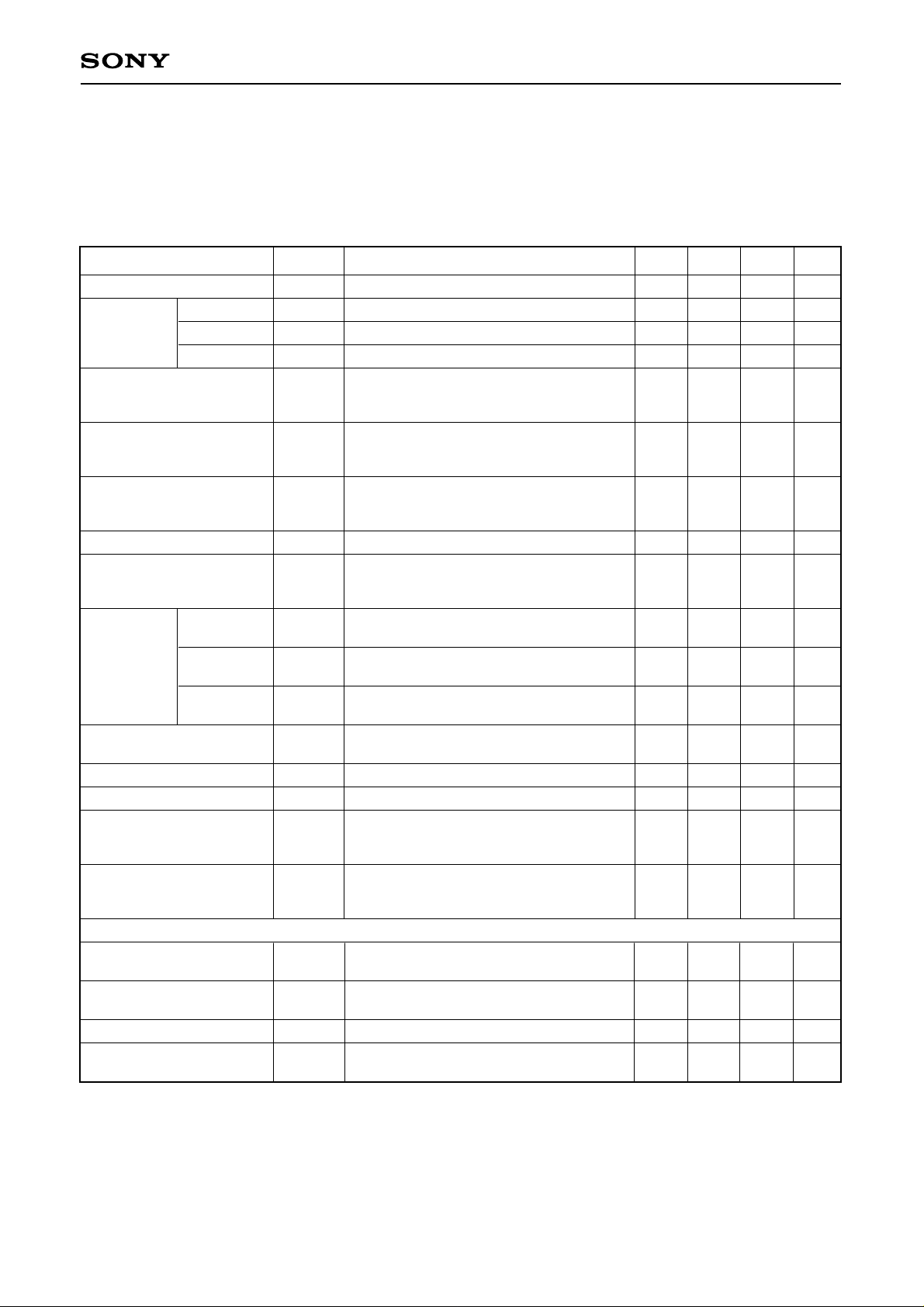

52

50

48

31

29

27

33

51

32

28

49

30

26

VOUT1

VOUT2

VOUT3

VOUT4

VOUT5

VOUT6

VOUT7

VOUT8

RTV

ROUT1

ROUT2

LTV

LOUT1

LOUT2

3.9V

4.5V

VCC = 12V

48

VCC = 12V

51

32

28

49

30

26

54

52

50

31

29

27

33

55

20k

200

22k

VCC = 9V

140µF

Video signal outputs.

280µA

VCC = 9V

33µA

Audio signal outputs.

20k

33µA

– 4 –

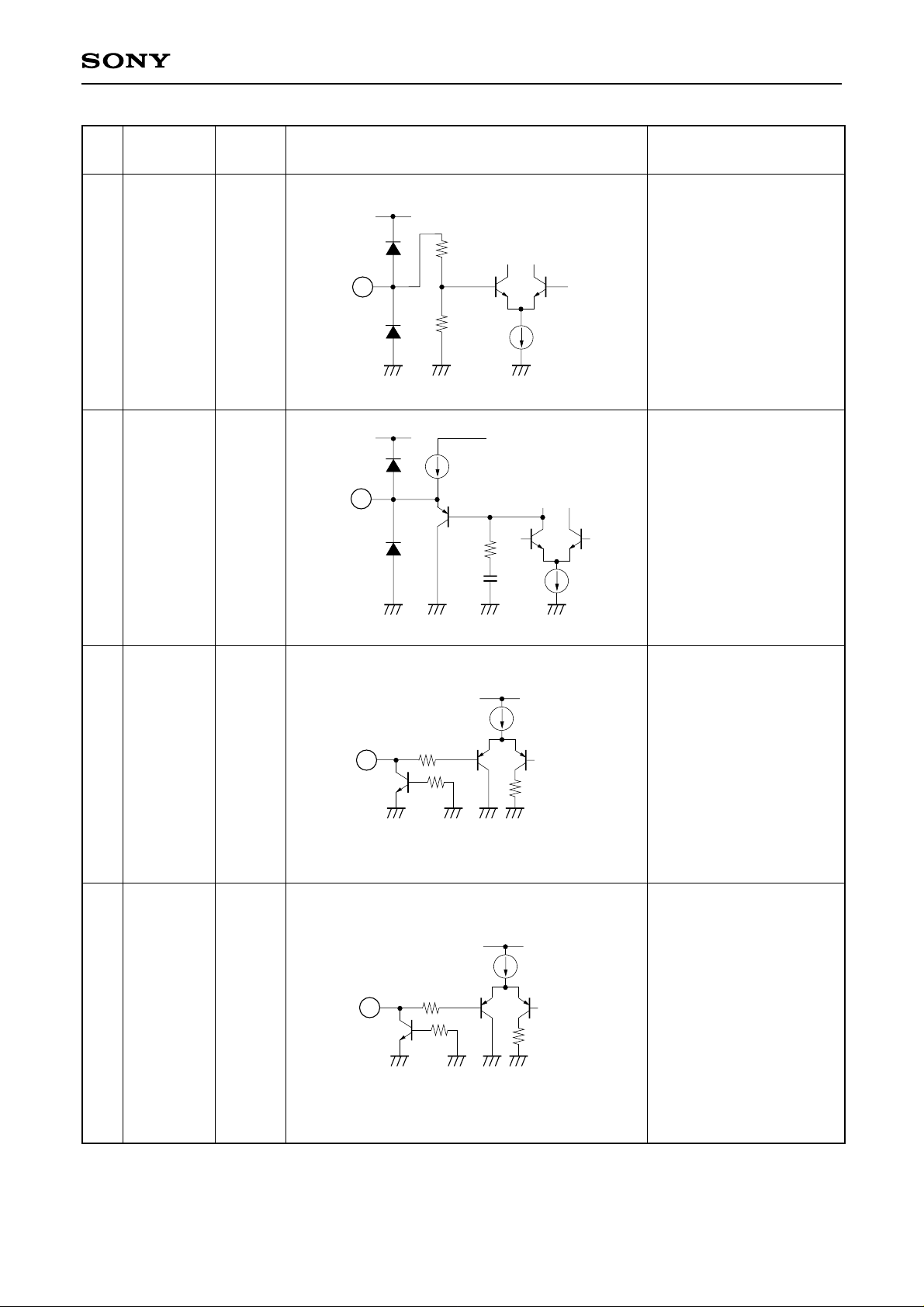

CXA2078Q

Pin

No.

34

3

Symbol

MONO

BIAS_

VIDEO

Pin

voltage

4.5V

3.9V

VCC = 12V

34

VCC = 12V

3

Equivalent circuit Description

VCC = 9V

75µA

200

Audio mono signal output.

11k

20k

75µA

VCC = 9V

14µA

Reference Bias for video

200

circuit.

200

9k

Connected to GND with

capacitor.

23

37

38

BIAS_

AUDIO

FNC_TVB

FNC_TVA

4.5V

—

VCC = 12V

23

VCC = 12V

37

38

20k

20k

20k

40k

7µA

VCC = 9V

VCC = 9V

2.7V

Reference Bias for audio

circuit.

Connected to GND with

capacitor.

I2C controlled output

giving 0/2V.

Maximum load current

= 800µA

– 5 –

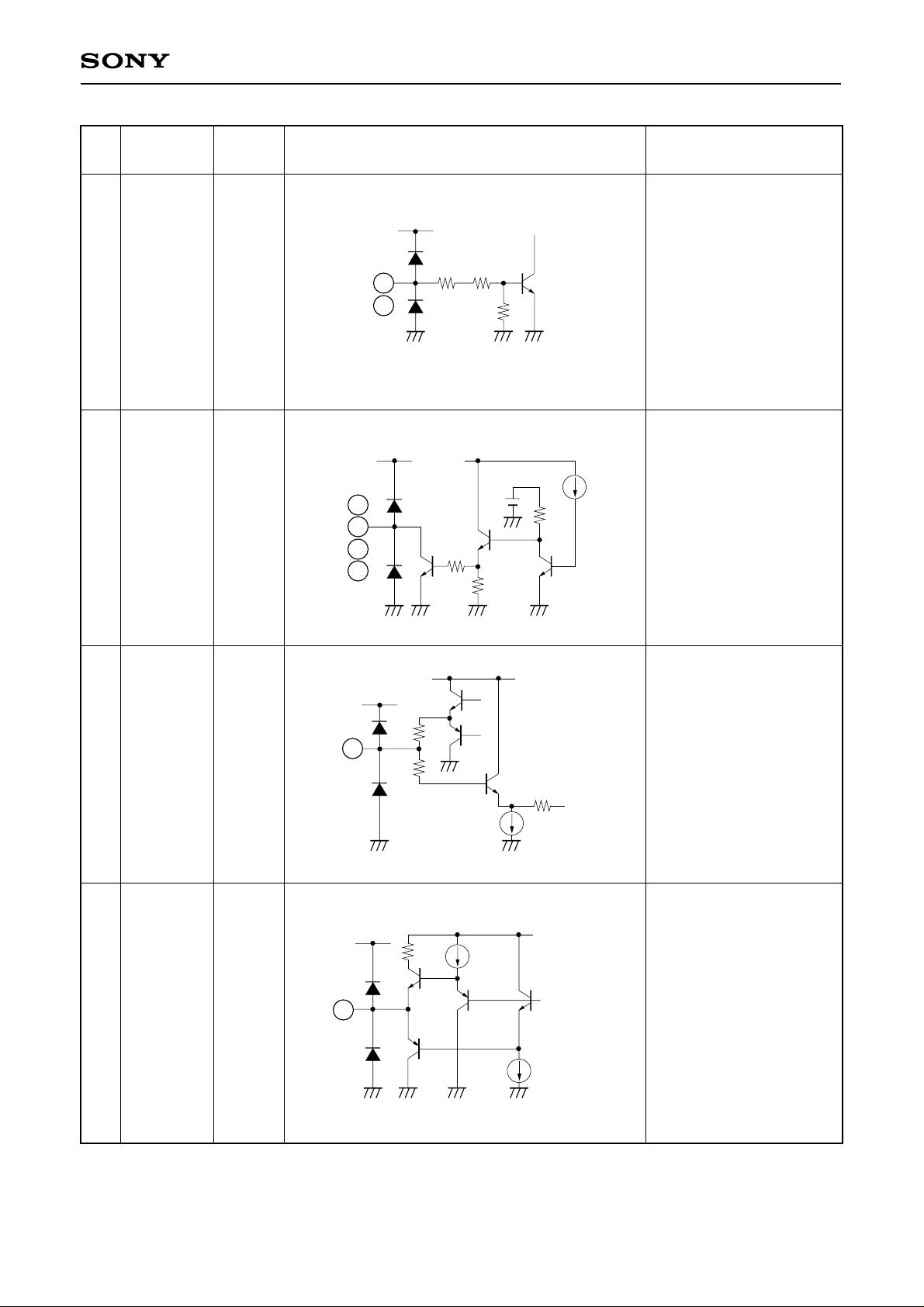

CXA2078Q

Pin

No.

56

57

Symbol

VREG_9V

VREG_

BASE

Pin

voltage

9V

9.7V

56

VCC = 12V

57

Equivalent circuit Description

VCC = 12V

77.7k

Pin connected to emitter

of external regulator

transistor.

13.5k

1mA

120µA

VCC = 12V

Connection to base of

external regulator

413

15p

120µA

transistor.

10

11

SCL

SDA

—

—

10

11

4k

4k

10k

4.5k

40µA

40µA

V

CC = 9V

40k

VCC = 9V

40k

I2C Clock Input.

VIL = 1.5V (max)

VIH = 3.0V (min)

I2C Data input/output.

VIL = 1.5V (max)

VIH = 3.0V (min)

VOL = 0.4V (max)

– 6 –

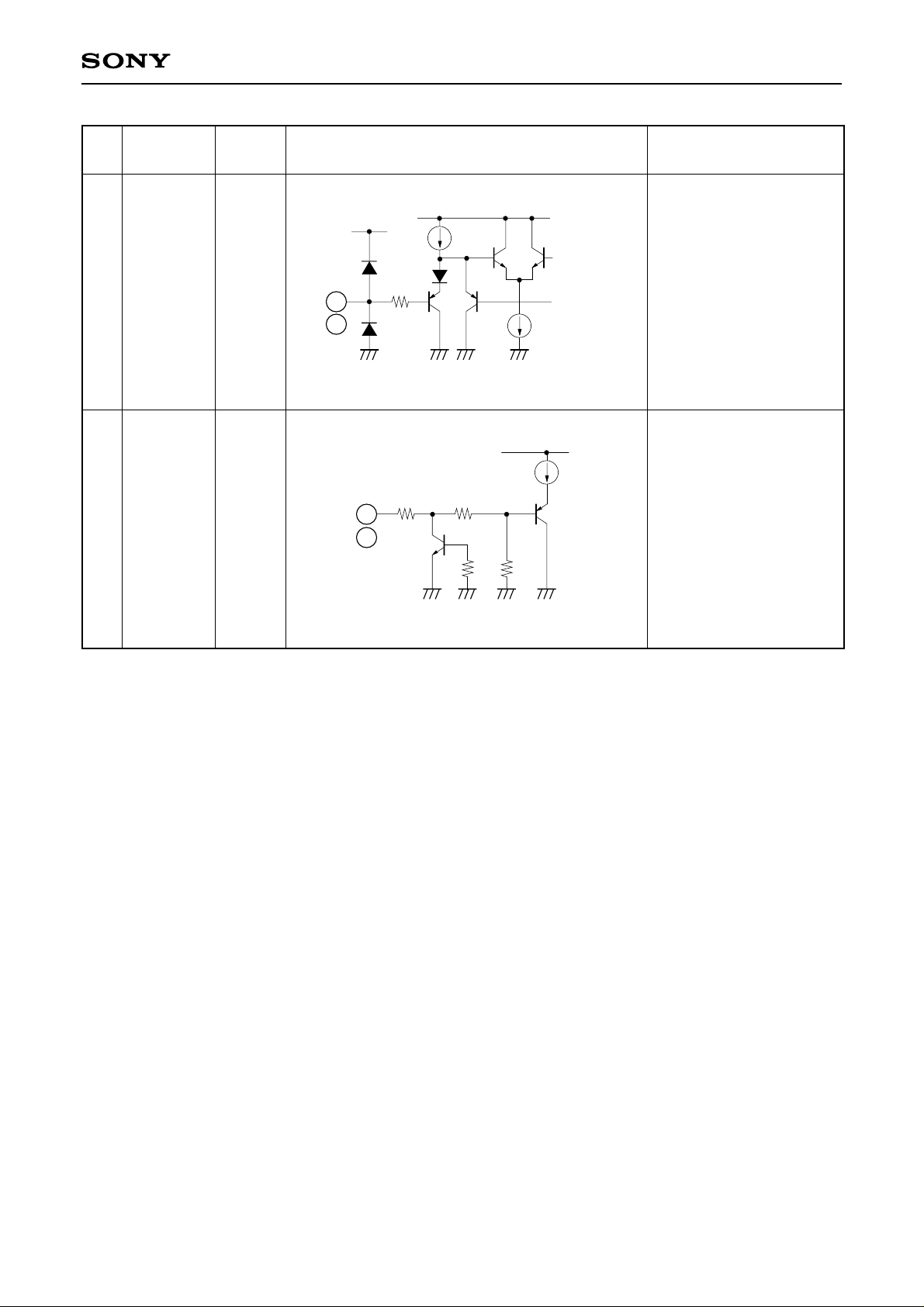

CXA2078Q

Pin

No.

12

40

43

44

45

46

Symbol

ADR

HW MUTE

LOG_4

LOG_3

LOG_2

LOG_1

Pin

voltage

—

—

12

40

VCC = 12V

43

44

45

46

Equivalent circuit Description

HW MUTE: This pin is

VCC = 12V

active high > 2.5V.

When high, audio outputs

72k

147

RTV, LTV and MONO are

muted.

28k

ADR: Selects the I2C

address for the IC.

< 1.5V = Low Add = 90H

> 2.5V = High Add = 92H

VCC = 9V

40k

8µA

Open collector logic Pins.

3V

Maximum current sink

= 1mA

4.5k

7.5k

35

53

TRAP

FBLK_

OUT

3.9V

—

VCC = 12V

35

VCC = 12V

53

1k

147

100

100µA

VCC = 9V

470µA

VCC = 9V

100µA

Connection to external

trap circuit.

Trap components should

be kept as close as

possible to this pin.

Fast Blank output set by

I2C, FBLK_IN1 or

FBLK_IN2.

High = 5.1V

Low = 1.2V

Connected to external

emitter follower.

Maximum load current

= 800µA

– 7 –

CXA2078Q

Pin

No.

41

60

5

7

Symbol

FBLK_IN1

FBLK_IN2

FNC_VCR

FNC_AUX

Pin

voltage

—

—

VCC = 12V

41

60

5

7

Equivalent circuit Description

V

CC = 9V

50µA

Fast Blank inputs.

147

Low = < 0.4V

High = > 1.0, < 3.0

90µA

VCC = 9V

80µA

50k

50k

Function switching input

(Scart pin 8).

Typical levels

= 0V/6V/12V

10k

100k

– 8 –

CXA2078Q

Electrical Characteristics

Absolute Maximum Ratings

Supply Voltage Vcc_12V 12 V

Operating Conditions

• Supply Voltage Vcc_12V 12 to 10.7 V

• Voltage Regulation Vreg_9V 9 ± 0.45 V (from 12V supply)

• Operating Voltage Video_Vcc, Dig_Vcc, 9 ± 0.5 V

Audio_Vcc 9 ± 0.5 V

FNC_TVA (pin 38) and FNC_TVB (pin 39) are static sensitive.

Precaution should be taken (note 8 in "Notes on Operation").

Operation of the CXA2078Q using a 9V supply connected directly to the VCC_12V, Video_VCC, AUDIO_VCC

and Dig_VCC pins is possible but not recommended. (The unused on-chip voltage regulator is then forced to

have pins Vreg_base and Vreg_9V floating.)

– 9 –

CXA2078Q

Electrical Characteristics

Nominal conditions (Ta = 25°C)

Item Symbol Conditions Min. Typ. Max. Unit

Current Consumption ICC 30 50 70 mA

VCC_12V = 12V, No signal, no load

Video system Nominal conditions (Ta = 25°C, Vcc_12V = 12V)

Item Symbol Conditions Min. Typ. Max. Unit

Input pin voltage

Output pin

voltage

Vout1 – 8

Vout8 (mix)

Gain (except Y/C mixer)

Gain of Y/C mixer

Bandwidth

(except Y/C mixer)

VVPin

VVPout

VVPoutm

GVv

GVYC

fV3dB

No signal, no load (Fig.1)

No signal,no load,Y/C mix inactive

(Fig.1)

No signal, no load, Y/C mix active

(Fig.1)

f = 200kHz, 0.3Vp-p input (Fig.2)

f = 200kHz, 0.3Vp-p input (Fig.2)

0.3Vp-p input, frequency where output

level is –3dB with 200kHz serving as

0dB (Fig. 2)

4.3

3.6

3.5

5.5

5.4

15

4.6

3.9

3.8

6.0

6.0

20

4.9

4.2

4.2

6.5

6.4

V

V

V

dB

dB

MHz

0.3Vp-p input, frequency where output

Bandwidth of Y/C Mixer

fYC3dB

level is –3dB with 200kHz serving as

0dB. No trap connected. (See note below)

7

15

—

MHz

(Fig.2)

Input dynamic range

Output dynamic range

Cross talk

VDRVI

VDRVO

Vctv

200kHz input (Fig.2)

200kHz, 2.5Vp-p input (Fig.2)

f = 4.43MHz, 1Vp-p input (Fig.2)

2.5

5.0

—

—

—

—

—

—

–50

Vp-p

Vp-p

dB

Ratio of 0.7Vp-p white video signal to

S/N ratio

S/NV

black line noise. Weighted using

CCIR 567. HPF @ 5kHz,

—

72

—

dB

LPF @ 5MHz. (Fig.2)

1Vrms 1kHz input through 56kΩ.

Input Impedance

ZinV

Attenuation measured to calculate ZinV

94

120

kΩ

(Fig.3)

V2

V1

(Fig.4)

–3

–0.4

+3

%

Non-linearity

Input/V

Lin

V1 = Pin Voltage +0.5V

V2 = Pin Voltage +1V

At output, non-linearity = –1 × 100

V2

V1 × 2

1.7Vp-p 5-step modulated staircase.

Differential Gain

DG

(Chroma and Burst are 150mVp-p

1.5

%

4.43MHz) (Fig.2)

Differential Phase

DP

as above. (Fig.2)

1

Deg

Percentage reduction in sync pulse

Sync crush

SC

(0.4Vp-p), with tip at –1.2V input offset.

0.2

3

%

(Fig.4)

Delay of Luma over

Chroma through mixer

tcld

0.4Vp-p square wave input. Input to

output edge delay measured. No trap.

(Fig.2)

15

40

ns

Note) Input output path from Vin9 – 12 to Vout 8 through mixer has BW reduced by external stray capacitance

on TRAP pin.

– 10 –

CXA2078Q

Electrical Characteristics

Audio system

Unless otherwise stated: input coupling capacitor 1µF in series with 6kΩ resistor; output coupling capacitor of

10µF; load of 10kΩ. Nominal conditions (Ta = 25°C, Vcc_12V = 12V)

Item Symbol Conditions Min. Typ. Max. Unit

Input pin voltage

R/LOUT1, 2

Gain

RTV, LTV

MONO

Audio frequency

response

VAPIN

GVA

GVATV

GVAM

FAF

No signal, no load (Fig. 5)

f = 1kHz, 1Vrms input. (Fig. 6)

f = 1kHz, 1Vrms input. (Fig. 6)

f = 1kHz, 1Vrms "stereo" input. (Fig. 6)

0.3Vp-p input. Output level at 30kHz

with 1kHz serving as 0dB. 6kΩ

removed. (Fig. 7)

4.2

–0.5

–0.65

–0.65

–0.3

4.5

0

0

0

0

4.8

+0.5

+0.35

+0.45

+0.3

V

dB

dB

dB

dB

0.3Vp-p input; frequency where output

Frequency B/W

FBWA1

level is –3dB with 1kHz serving as

—

1

—

MHz

0dB. 6kΩ removed. No load (Fig. 7)

f = 1kHz, 0.5Vrms, unweighted

Distortion

THD

response; LPF @400Hz,

—

0.004

0.2

%

HPF @ 80KHz. (Fig. 6)

Input Dynamic Range

Cross talk

(Channel separation)

R/LOUT1, 2

Ripple

rejection

RTV, LTV

MONO

DC Offset -R/Lout1, 2

Input impedance

Output Impedance

VdA

VctA

RRA

RRATV

RRAM

Voff

Zin

Zout

f = 1kHz (Fig. 6)

f = 1kHz, 1Vrms input on one input,

measure on any other audio output.

(Fig.6)

f = 100Hz, 0.3Vp-p applied to Vcc_aud

(Fig. 8)

f = 100Hz, 0.3Vp-p applied to Vcc_aud

(Fig. 8)

f = 100Hz, 0.3Vp-p applied to Vcc_aud

(Fig. 8)

Offset voltage between any audio input

and R/Lout1, 2 (Fig. 5)

(excluding series external 6kΩ)

(excluding any external series resistor)

2

—

—

—

—

–30

48

—

—

–88

–62

–75

–44

+2

60

10

—

–76

—

—

—

+30

72

—

Vrms

dB

dB

dB

dB

mV

kΩ

Ω

f = 1kHz, 1Vrms input to two channels.

Phase Difference

Vpda

Phase difference of stereo output

—

0.05

—

Deg

measured

S/N ratio

S/NA

f = 1kHz, 1Vrms input (at maximum

volume).

72

95

—

dB

HPF @ 20Hz, LPF @ 20kHz. (Fig. 6)

Electronic Volume Control

Fine volume attenuation

step

Coarse volume

attenuation step

Mute

DC Offset -RTV, LTV

AEVC

AEVF

Amute

VoffTV

f = 1kHz, 0.5Vrms input. Set by I2C

(Fig.6)

f = 1kHz, 0.5Vrms input. Set by I2C

(Fig.6)

f = 1kHz, 1Vrms input. (Fig.6)

Offset voltage between any audio input

and RTV, LTV outputs (Fig.5)

0.6

7.5

–30

1

8

>80

+2

1.4

8.5

+30

dB

dB

dB

mV

– 11 –

Loading...

Loading...