Sony CXA2050S Datasheet

CXA2050S

Y/C/RGB/D for PAL/NTSC Color TVs

Description

The CXA2050S is a bipolar IC which integrates the

luminance signal processing, chroma signal

processing, RGB signal processing, and sync and

deflection signal processing functions for PAL/NTSC

system color TVs onto a single chip. This IC includes

deflection processing functions for wide-screen TVs,

and is also equipped with a SECAM decoder

interface, making it possible to construct a TV

system that supports multiple color systems.

Features

• I2C bus compatible

• Compatible with both PAL and NTSC systems

(also compatible with SECAM if a SECAM decoder is connected)

• Built-in deflection compensation circuit capable of supporting various wide modes

• Countdown system eliminates need for H and V oscillator frequency adjustment

• Automatic identification of 50/60Hz vertical frequency (forced control possible)

• Non-interlace display support (even/odd selectable)

• Automatic identification of PAL, NTSC, and SECAM color systems (forced control possible)

• Automatic identification of 4.43MHz/3.58MHz crystal (forced control possible)

• Non-adjusting Y/C block filter

• One CV input, one set of Y/C inputs, two sets of analog RGB inputs (one set of which can serve as both

analog and digital inputs)

• Built-in AKB circuit

• Support for forcing YS1 off

64 pin SDIP (Plastic)

Applications

Color TVs (4:3, 16:9)

Structure

Bipolar silicon monolithic IC

Absolute Maximum Ratings (Ta = 25°C, SGND, DGND = 0V)

• Supply voltage SVCC1, 2, DVCC1, 2 –0.3 to +12 V

• Operating temperature Topr –20 to +65 °C

• Storage temperature Tstg –65 to +150 °C

• Allowable power consumption PD 1.7 W

• Voltages at each pin –0.3 to SVCC1, SVCC2,

DVCC1, DVCC2 + 0.3 V

Operating Conditions

Supply voltage SVCC1, 2 9.0 ± 0.5 V

DVCC1, 2 9.0 ±0.5 V

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

– 1 –

E96403-PS

CXA2050S

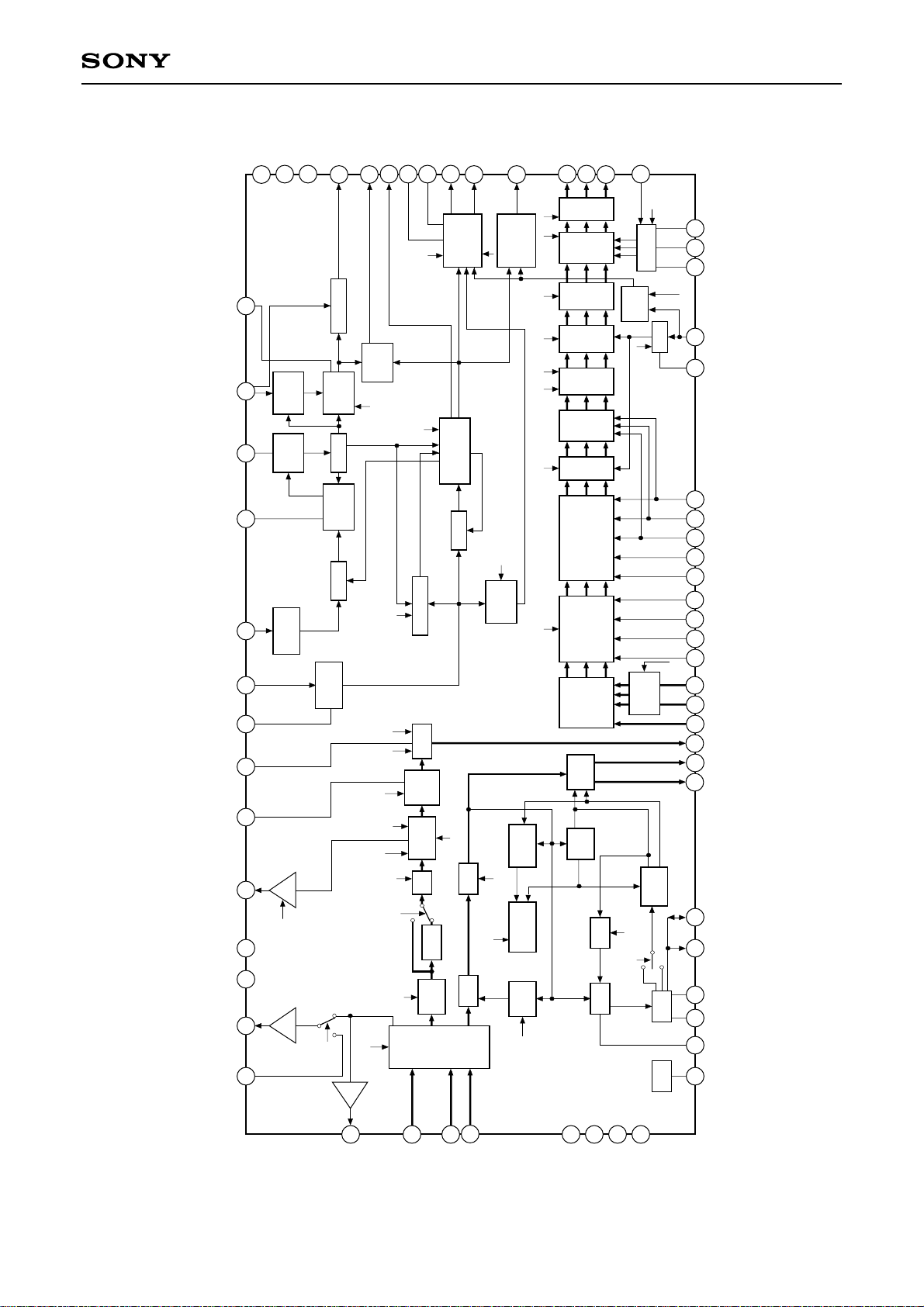

Block Diagram

CC2DVCC1

DV

42

50

L2FIL

45

HOFF

AFCPIN/

44

PHASE

CERA

47

32fH

AFCFIL

46

HSIN

53

H SYNC

VSIN

52

VSFIL

51

BLHOLD

59

DCTRAN

61

VM

55

SCL

SDA

SYNCOUT

EXT SYNC IN

VM

56

57

2Vp-p

54

63

DET

VCO

SEP

6dB

DGND

48

V SYNC

EXT

HD OUT

43

H.DRIVE

SHIFT

PHASE

1/32

2fH

DET.

PHASE

GATE

SEP

DC

CV/YC

SYNC

58

VIDEO OUT

VTIM

SCPOUT

12

36

Sand

Castle

AFC

H POSI

V FREQ

D PICAGING

TRAN

SHP f0

SHARP

DL

TRAP OFF

SUB CONT

SAWOSC

VAGCSH

VD + OUT

40

38

41

WIDE

VPOSI, VOFF,

VSIZE

CD MODE

Count Down

50/60 ID

D PIC

DC

CLP

TRAN

NESS

SHARP

DL

TRAP

SUB

CONT

SW

VIDEO

1Vp-p

60

62

YIN

CVIN

VD – OUT

/VPROT

/VPROT

37

VLIN, SCORR

Gen.

Sawtooth

525/625

GATE

INTER

PRE/OVER

TOT

TOT

COLOR SW

ACC

64

CIN

E-WOUT

39

LIMIT

Gen.

WIDE

Parabola

GB CUT

GB DRV

BRT

γ

D-COL

PIC

INTERLACE

-LACE

YS1 OFF

1Vp-p

DET

KILLER

IDENT

SYSTEM

DET

ACC

SUB COLOR

ROUT

28

BLK

CUT

GB

BRT

D-

COL

OSD

PIC

YM/YS2

YS1

Y/C

DEM

ID

PAL

1

CC1SVCC2

SV

GOUT

30

OFF

DRV

γ

MIX

SW

SW

MIX

APC HUE

26

BOUT

32

8

SGND1

IKIN

33

HV

COMP

ABL

COLOR

fsc R-Y

HUE

XTAL

16

SGND2

AKB OFF

AKB

ABL

& AXIS

DEM

AXIS

VCO

IREF

EHT H, V

COL

fsc B-Y

BSH

31

GSH

29

RSH

27

VCOMP

ABLIN/

34

35

25

24

23

22

21

20

19

18

17

15

14

13

11

10

9

7

6

3

4

2

49

ABLFIL

B2IN

G2IN

R2IN

YM

YS2

B1IN

G1IN

R1IN

YS1/VM

– (B-Y) IN

– (R-Y) IN

YRET

YOUT

– (B-Y) OUT

– (R-Y) OUT

SECAM REF

FSCOUT

X443

X358

APCFIL

IREF

– 2 –

Pin Configuration

CXA2050S

EXT SYNC IN

CIN

63

64

1

2

1

CC

SV

APCFIL

62

3

YIN

61

4

X443

CVIN

DCTRAN

60

59

6

5

X358

TEST

BLHOLD

VIDEO OUT

57

58

8

7

FSC OUT

SECAM REF

SCL

SDA

55

56

9

10

SGND1

– (R-Y) OUT

HSIN

SYNCOUT

VM

53

52

54

13

12

11

YOUT

SCPOUT

– (B-Y) OUT

VSIN

51

14

YRET

2

CC

DV

VSFIL

49

50

15

16

– (B-Y) IN

– (R-Y) IN

DGND

IREF

48

17

SGND2

YS1/VM

CERA

47

18

R1IN

AFCFIL

46

19

G1IN

AFCPIN/HOFF

L2FIL

45

44

21

20

YS2

B1IN

HD OUT

43

42

23

22

YM

1

CC

DV

41

24

R2IN

VAGCSH

SAWOSC

40

39

26

25

B2IN

G2IN

VTIM

VD – OUT/VPROT

VD + OUT/VPROT

E-WOUT

37

38

36

27

28

29

2

CC

RSH

GSH

ROUT

SV

ABLIN/VCOMP

ABLFIL

35

34

31

30

BSH

GOUT

IKIN

33

32

BOUT

– 3 –

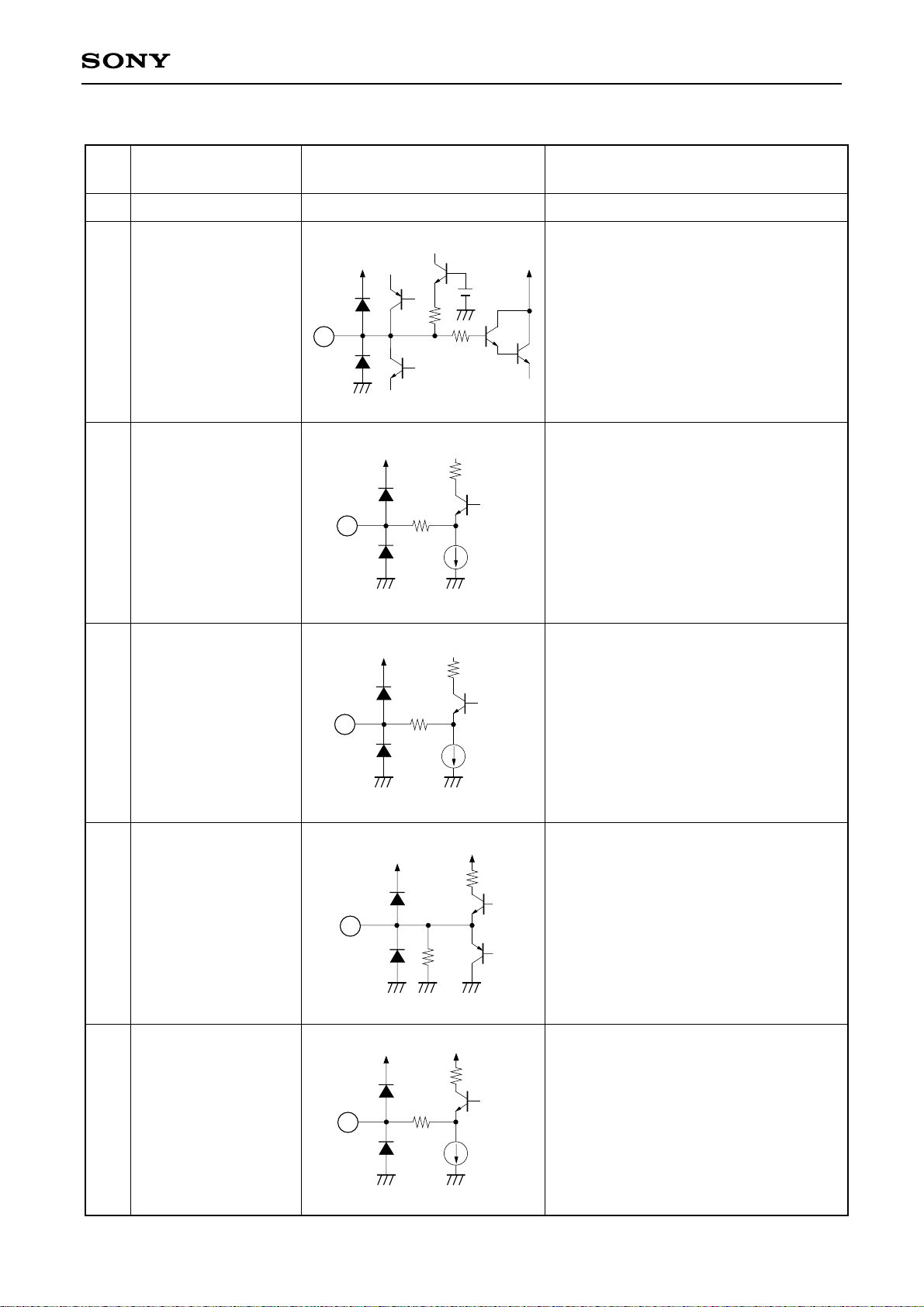

Pin Description

CXA2050S

Pin

No.

1

SVCC1 Power supply for Y/C block.

2

APCFIL

3

X443

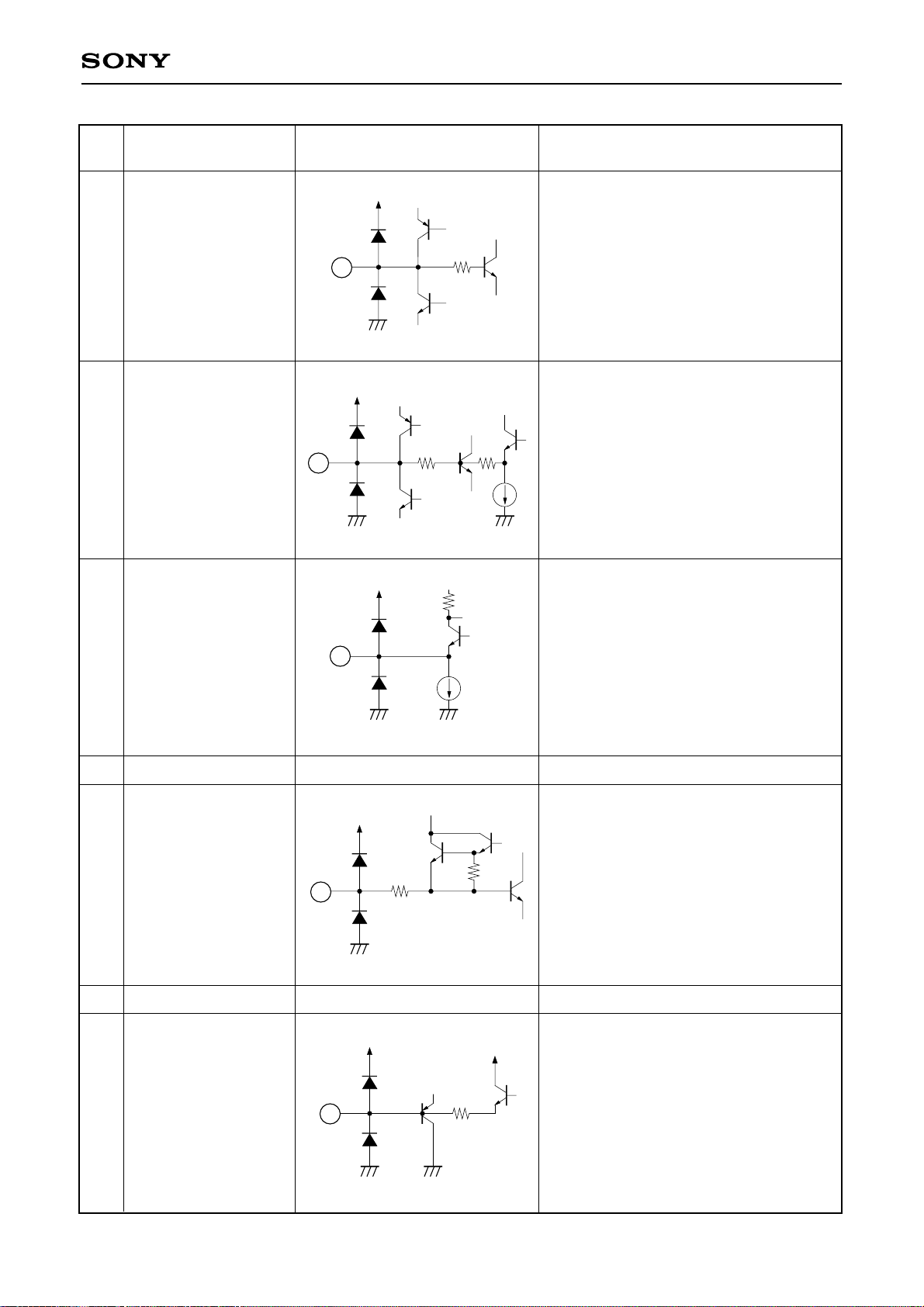

Symbol Equivalent circuit Description

4.6V

1.2k

2

3

1.2k

4k

500

200µA

CR connection for the chroma APC laglead filter.

Connect a 4.433619MHz crystal oscillator.

4k

X358 Connect a 3.579545MHz crystal oscillator.

4

4

500

200µA

1k

Test pin.

5

6

TEST

FSCOUT

5

15k

1.2k

6

147

280µA

Outputs a 0 to 3V V-SYNC SEP with

positive polarity. If not used, leave this

pin open.

Subcarrier output.

Output level: 5.2VDC, 0.4Vp-p

– 4 –

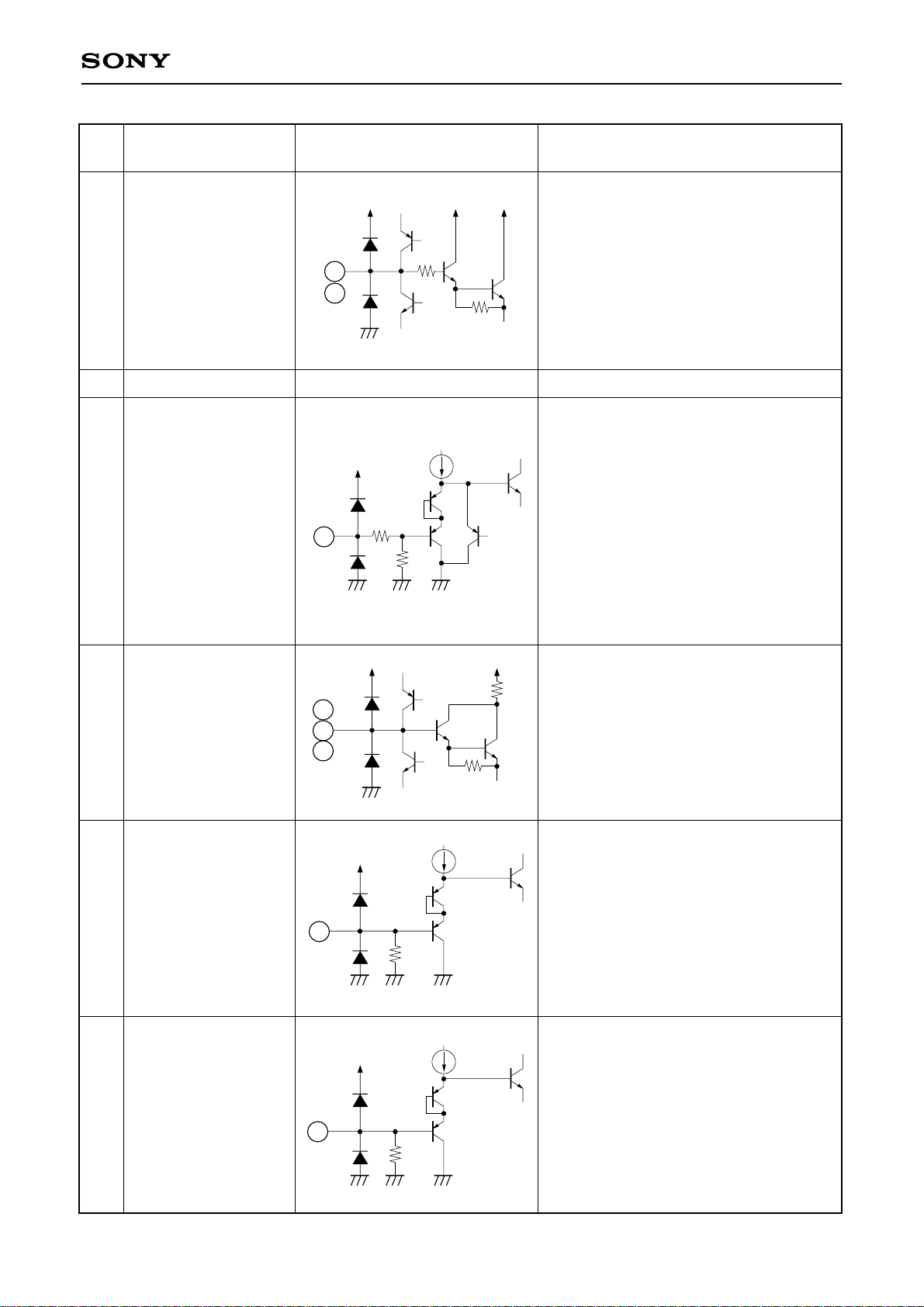

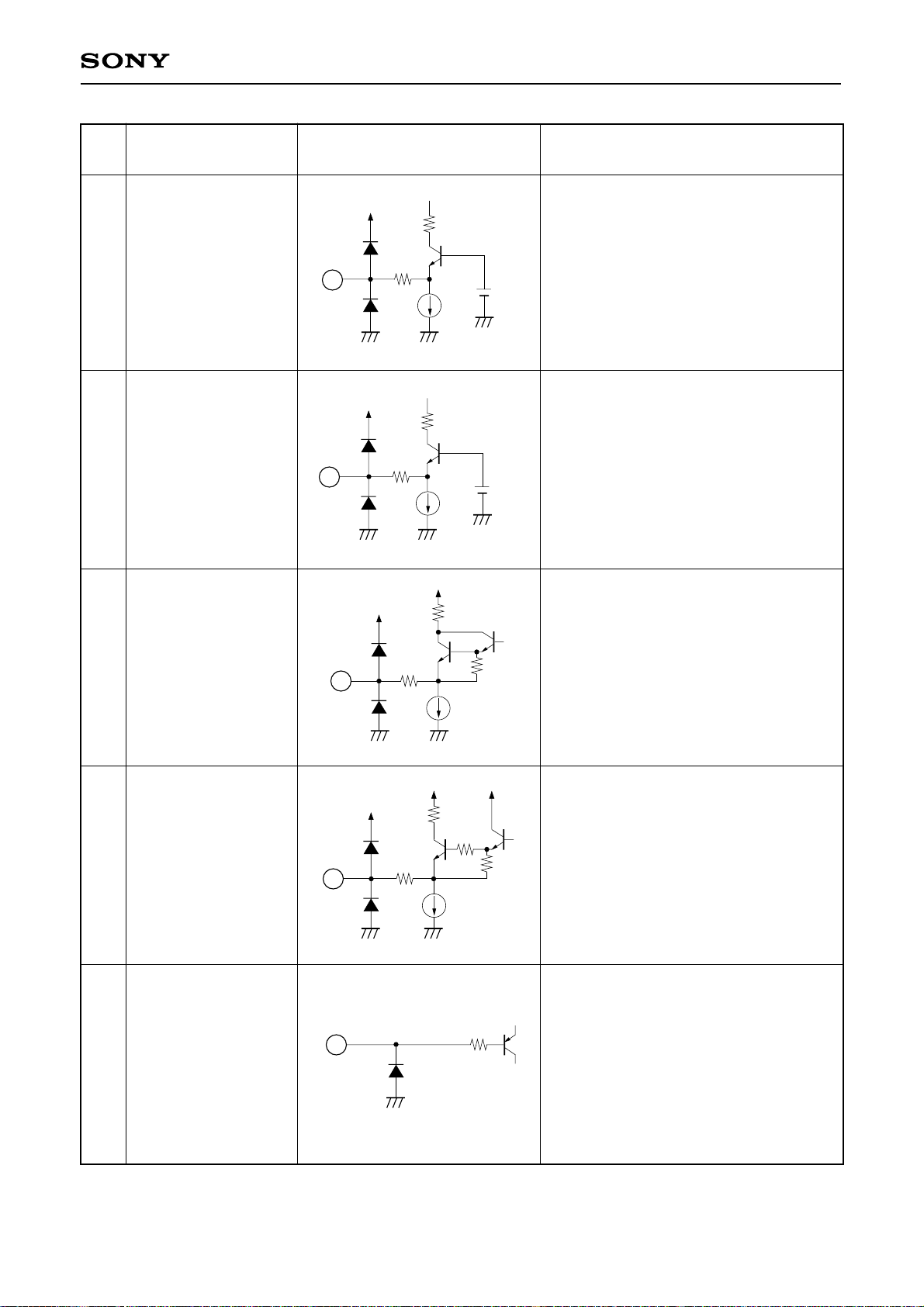

CXA2050S

Pin

No.

Symbol Equivalent circuit Description

20p

6k

SECAM decoder interface. This pin

SECAMREF

7

SGND1 GND for Y/C block.

8

7

250µA

7.2V

—

serves as both a 4.43MHz output and as

a SECAM identification input/output pin.

Color difference signal outputs. Go to

high impedance when the SECAM

system is detected.

Standard output levels for 75% CB:

B-Y: 0.665Vp-p

9

10

– (R-Y) OUT

– (B-Y) OUT

200µA

9

10

R-Y: 0.525Vp-p

5.7VDC when killer is ON.

11

12

13

YOUT

SCPOUT

YRET

13

11

12

1.5k

500

400µA

10k

30k

1k

1k

70k

Luminance signal output.

Black level is 3.5VDC.

Standard output level for 100 IRE input:

1Vp-p

Sand castle pulse output. The 0 to 5V

BGP pulse, the phase of which is

controlled through the bus, is

superimposed with the 0 to 2V H and

VBLK pulse for output.

Luminance signal input.

Clamped to 4.8V at the burst timing.

Standard input level for 100 IRE input:

1Vp-p

– 5 –

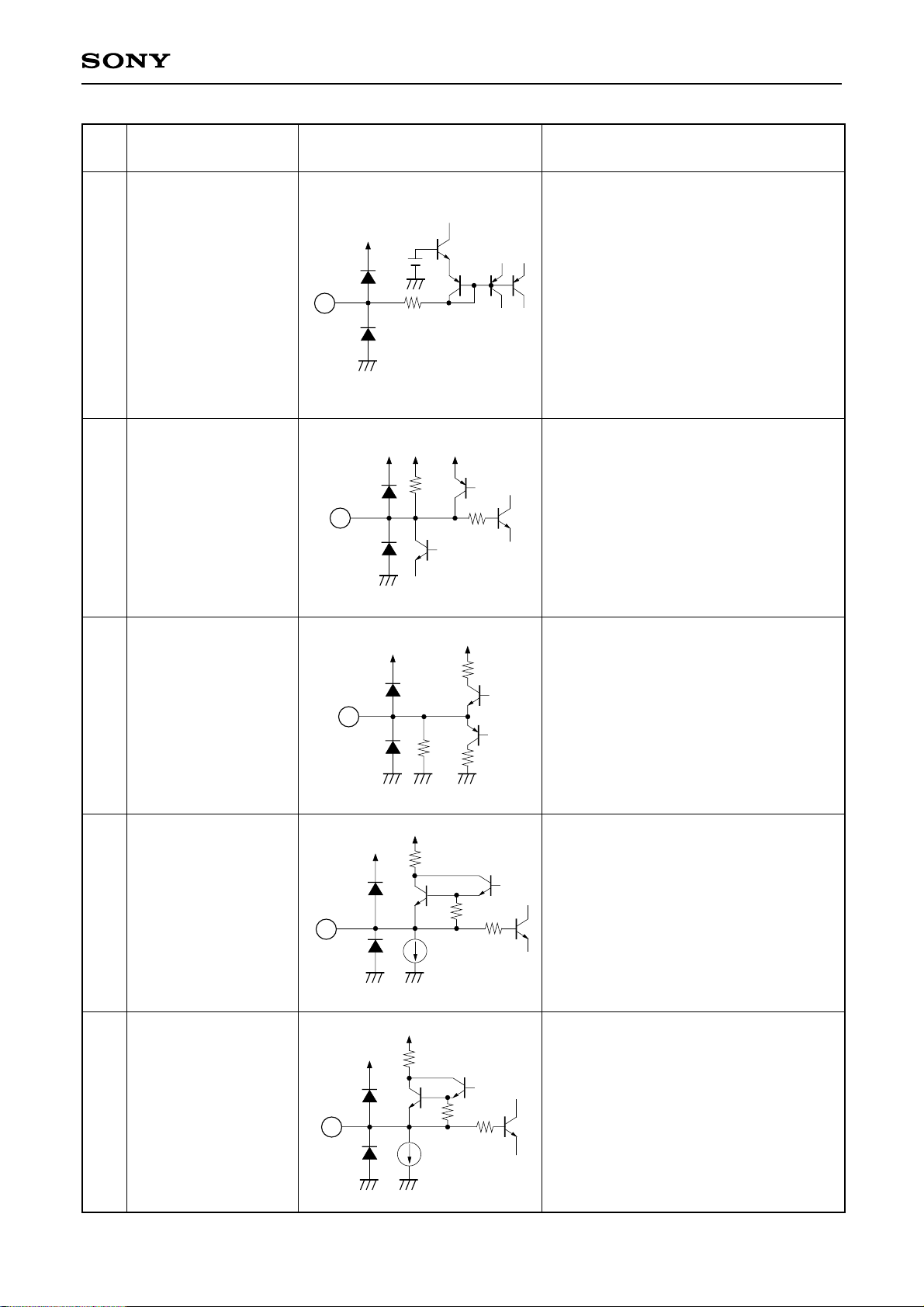

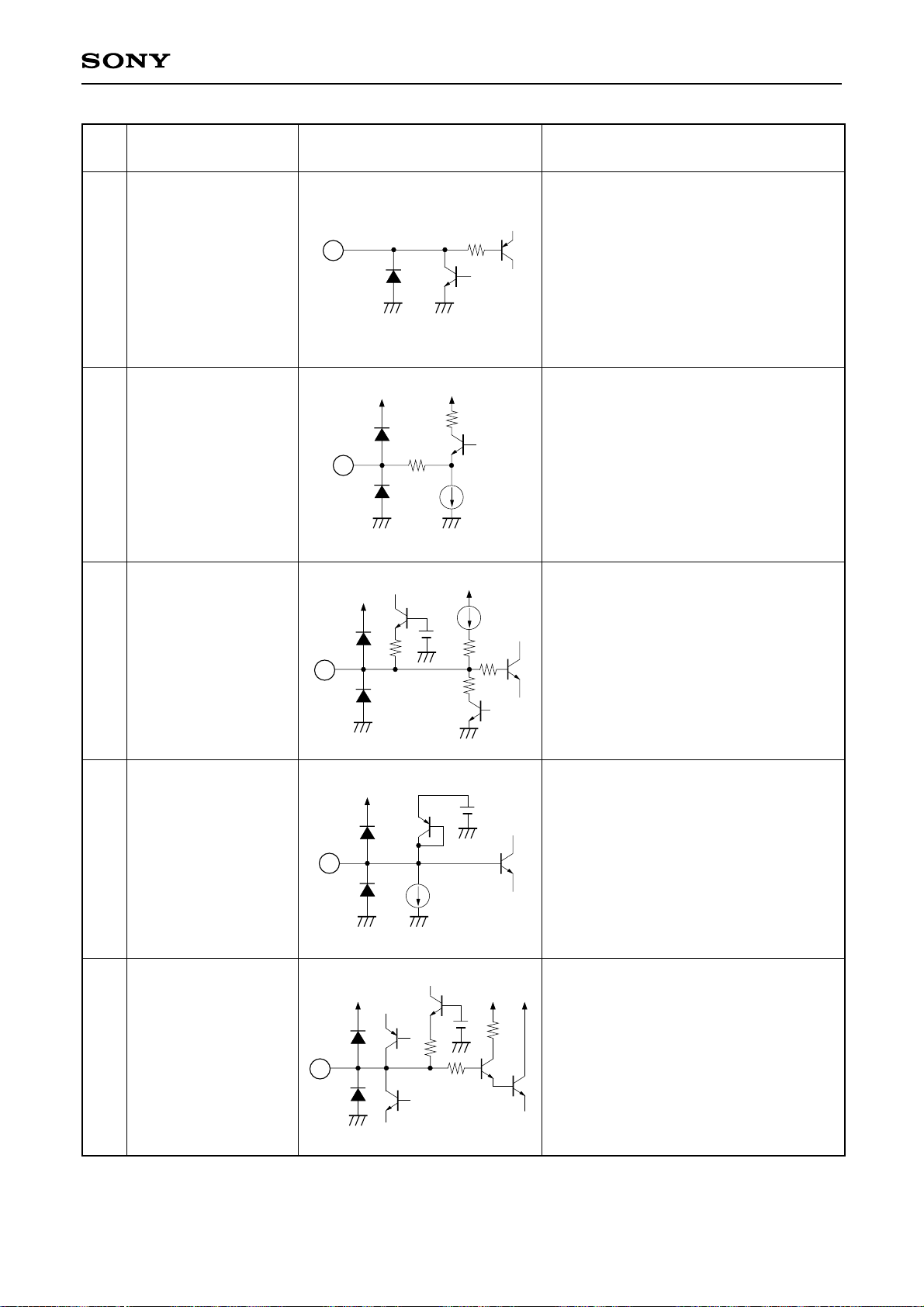

CXA2050S

Pin

No.

Symbol Equivalent circuit Description

Color difference signal inputs.

14

15

– (R-Y) IN

– (B-Y) IN

14

15

1.5k

Clamped to 5.5V at the burst timing.

Standard input levels for 75% CB:

B-Y: 1.33Vp-p

R-Y: 1.05Vp-p

70k

SGND2 GND for the RGB block.

16

Input which combines YS1SW control with

VM circuit ON/OFF function. Supports

100µA

with ternary.

VMSW (VthVM = 0.9V)

VILVM ≤ 0.3V VM circuit ON

17

YS1/VM

10k

17

20k

VIHVM ≥ 1.5V VM circuit OFF

YS1SW (VthYS1 = 2.5V)

VILYS1 ≤ 1.7V Y/color difference input

VIHYS1 ≥ 3.3V RGB1 input selected

Setting YS1OFF of I2C bus to 1, input for

this pin is invalid.

selected

18

19

20

21

22

R1IN

G1IN

B1IN

YS2

YM

21

22

18

19

20

40k

40k

30k

100µA

100µA

Analog R, G and B signal inputs.

200

Input a 0.7Vp-p (no sync, 100 IRE) signal

via a capacitor.

The signal is clamped to 5.7V at the burst

timing of the signal input to the HSIN

input (Pin 53).

YM/YS2SW YS2 control input.

When YS2 is high, the RGB2 block signal

is selected; when YS2 is low, the YS1SW

output signal is selected.

VILMAX = 0.4V

VIHMIN = 1.0V

YM/YS2 SW YM control input.

When YM is high, the YS1SW output

signal is attenuated by 6dB.

VILMAX = 0.4V

VIHMIN = 1.0V

– 6 –

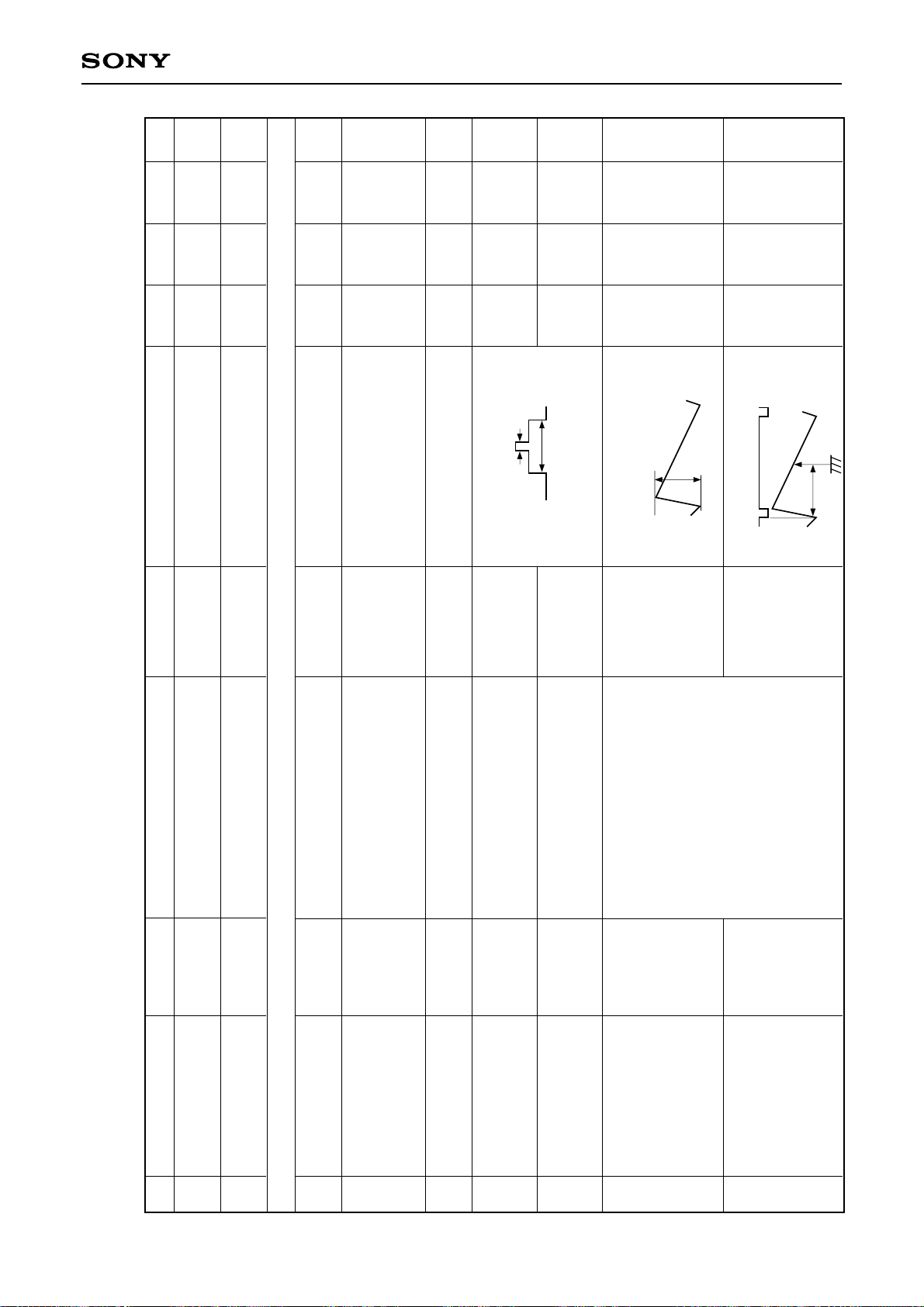

CXA2050S

Pin

No.

23

24

25

26

27

29

31

R2IN

G2IN

B2IN

SVCC2

RSH

GSH

BSH

Symbol Equivalent circuit Description

Analog/digital (dual-purpose) RGB signal

inputs.

The input signals are input via capacitors.

100µA

200

23

24

25

30k

When using analog input, input a 0.7Vp-p

signal (no sync, 100 IRE); when using

digital input, input a signal of at least

1.5Vp-p (Vth = 1.2V).

The display level is 78 IRE. When using

digital input, digital input is selected

regardless of the YS2 setting.

In addition, the VM output is turned off.

These pins are clamped to 5.7V at the

burst timing of the signal input to the

HSIN input (Pin 53).

Power supply for RGB block.

200

27

29

31

Sample-and-hold for R, G and B AKB.

Connect to GND via a capacitor.

When not using AKB (manual CUTOFF

mode), R, G and B cut-off voltage can be

controlled by applying a control voltage to

each pin. The control voltage is 4.5 ± 1V.

28

30

32

33

ROUT

GOUT

BOUT

IKIN

33

30

28

32

200

1.1mA

1k

12k

50µA

R, G and B signal outputs.

2.5Vp-p is output during 100% white

input.

Input the signal converted from the CRT

beam current (cathode current Ik) to a

voltage via a capacitor. The V blanking

part is clamped to 2.7V at the V retrace

timing.

The input for this pin is the reference

pulse return, and the loop operates so

that the Rch is 1Vp-p and the G and Bch

are 0.81Vp-p. The G and Bch can be

varied by ±0.5V by the bus CUTOFF

control. When not using AKB, this pin

should be open.

– 7 –

CXA2050S

Pin

No.

ABLIN/VCOMP

34

ABLFIL

35

Symbol Equivalent circuit Description

ABL control signal input and VSAW high

voltage fluctuation compensation signal

input.

1.5V

High voltage compensation has linear

control characteristics for the pin voltage

34

147

range of about 8V to 1V. The control

characteristics can be varied through

EHT-V control of the bus. ABL begins to

have effect below a threshold voltage of

about 1.2V.

ABL functions as average value type.

100k

35

1.2k

Connect a capacitor to form the LPF of

the ABL control signal.

VTIM

36

VD – OUT/VPROT

37

38

VD + OUT/VPROT

37

38

36

10k

700

400µA

700

400µA

30k

30k

1k

1k

24k

24k

V timing pulse output.

Outputs the timing pulse from V sync

identification to the end of V blanking.

Pulses are positive polarity from 1 to 6V.

During zoom mode, the V blanking pulse

which has been expanded before and

after the V sync is superimposed and

output as the 1 to 3V pulse.

V sawtooth wave output and V protect

signal input.

When a large current (3mA) is drawn

from this pin, the RGB outputs are all

blanked and “1” is output to the status

register VNG.

Serves as both a V sawtooth wave output

with the reverse polarity of VD – OUT,

and a Vprotect signal input. The Vprotect

function can even be applied to this pin.

– 8 –

CXA2050S

Pin

No.

39

40

Symbol Equivalent circuit Description

E-WOUT

VAGCSH

39

40

1.4k

800µA

1.2k

15k

V parabola wave output.

78k

Sample-and-hold for AGC which

maintains the V sawtooth wave at a

constant amplitude.

Connect to GND via a capacitor.

Connect a capacitor to generate the V

SAWOSC

41

42

DVCC1 Power supply for the V deflection block.

41

300

100

sawtooth wave. For the capacitor, use an

MPS (metalized polyester capacitor), etc.,

with a small tan δ.

H drive signal output.

43

HD OUT

43

147

20k

This signal is output with the open

collector.

H deflection pulse input for H AFC.

Input an about 5Vp-p pulse via a

capacitor. Set the pulse width to 10 to

12µs. This pin is also used as the hold-

44

AFCPIN/HOFF

44

147

10k

68k

down signal input for the HD output, and

if this pin is 1V or less for a 7V cycle or

4.2V

longer, the hold-down function operates

10k

and the HD output is held to 9VDC. In

addition, the RGB outputs are all blanked.

Outputs “1” to the status register XRAY.

– 9 –

CXA2050S

Pin

No.

45

46

L2FIL

AFCFIL

Symbol Equivalent circuit Description

Filter for H AFC.

Connect to GND via a capacitor.

The H phase can also be controlled from

45

100

this pin by leading current in and out of

this capacitor.

As the pin voltage rises, the picture shifts

to the left; as the pin voltage drops, the

picture shifts to the right.

46

1.2k

46k

CR connection for the AFC lag-lead filter.

10k

47

48

CERA

DGND

47

400µA

Connect the 32 × FH VCO ceramic

oscillator.

GND for the deflection block.

Internal reference current setting.

49

IREF

49

147

20k

Connect to GND via a resistor with an

error of less than 1% (such as a metal

film resistor).

50

DVCC2 Power supply for the H deflection block.

51

VSFIL

51

1k

– 10 –

Filter for V sync separation.

Connect to GND via a capacitor.

CXA2050S

Pin

No.

52

53

VSIN

HSIN

Symbol Equivalent circuit Description

15k

Sync signal input for V sync separation.

Input a 2Vp-p Y signal (or a 0.6Vp-p

sync signal).

52

147

20µA

14k

4.1V

Sync signal input for H sync separation.

53

147

3.2V

10µA

Input a 2Vp-p Y signal (or a 0.6Vp-p sync

signal).

54

55

56

SYNCOUT

VM

SCL

55

56

54

147

147

1.2k

240µA

500

1.2k

400µA

4k

40k

30k

Sync signal output for VSIN and HSIN.

The output can be selected from the

internal sync signals (Pin 60 or Pin 62) or

the external sync signal (Pin 63) by the

I2C bus.

Output signal level: 2Vp-p

(0.6Vp-p sync only)

Input/output gain: 6dB

Outputs the differential waveform of the

VM (Velocity Modulation) Y signal.

The signal advanced for 200ns from

YOUT is output. The delay time versus

YIN is determined by the DL setting of

the I2C bus. This output level can be set

at 2.65Vp-p or 1.1Vp-p by the I2C bus.

Pedestal level is DC6.2V.

This output can also be turned off by

YS1, YM, and YS2.

I2C bus protocol SCL (Serial Clock) input.

VILMAX = 1.5V

VIHMIN = 3.5V

– 11 –

CXA2050S

Pin

No.

57

58

Symbol Equivalent circuit Description

SDA

VIDEO OUT

57

58

147

4k

1.2k

200µA

I2C bus protocol SDA (Serial Data) I/O.

VILMAX = 1.5V

VIHMIN = 3.5V

VOLMAX = 0.4V

The input signal from CVIN pin and YIN

pin is selected by I2C bus, and output

externally.

59

60

61

BLHOLD

CVIN

DCTRAN

61

59

60

4k

4k

4.6V

20k

1µA

2k

2V

9µA

20k

1.2k

4.6V

1.2k

Capacitor connection for black peak hold

of the dynamic picture (black expansion).

Composite video signal input.

Input the 1Vp-p (100% white including

sync) CV signal via a capacitor. The

sync level of the input signal is

clamped to 3.8V.

In addition, this pin detects input video

signal HSYNC, and outputs the status

via the status register CVSYNC.

Connect a capacitor that determines the

DC transmission ratio to GND.

– 12 –

CXA2050S

Pin

No.

62

63

Symbol Equivalent circuit Description

YIN

EXT SYNC IN

62

63

1µA

1µA

4.6V

4.6V

Y signal input.

Input a 1Vp-p (100% white including

sync) Y signal via a capacitor. The

sync level of the input signal is

clamped to 3.8V.

External sync signal input.

Input a 0.3Vp-p sync signal (or a 1Vp-p

CV signal or Y signal) via a capacitor.

The sync level of the input signal is

clamped to 3.8V.

64

CIN

64

30k

50k

Chroma signal input.

Input a C signal with a burst level of

5.2V

300mVp-p via a capacitor. Input signal is

biased to 4.5V internally.

– 13 –

CXA2050S

mA

90

67

mA

65

49

kHz

15.90

15.734

40

30

C Bus Register Initial Settings”.

2

Measurement contents Min. Typ. Max. Unit

Measure the pin inflow current.

Measure the pin inflow current.

15.55

HDRIVE output frequency

Hz

400

—

–400

C status register

2

H is shifted from

HLOCK is 1 (the pull-in range

when f

Confirm that I

µs

26.5

25.5

24.5

15.734kHz).

Measure the pulse width for the section

where the HDRIVE output is high.

µs

12.6

12.1

11.6

VBGPh

µs

4.15

3.75

3.35

VBLKh

V

1.1

1.0

0.9

VSp-p

V

3.1

3.0

2.9

VDRIVE+

46: VSIN in

Measure the VDRIVE output Vp-p.

VSdc

10.79ms

1, 26

42, 50

43

—

Measurement pins

C bus register as shown in “I

2

Measurement conditions

CC = 9.0V,

V

CC = 9.0V,

Bus data = center

V

Bus data = center

AFC MODE = 0h

SYNCIN: composite sync

Symbol

SICC

DICC

fHFR

∆fHR

• Measures the following after setting the I

43

SYNCIN: composite sync

HDw

12

SCP

Measure the pulse width for the section

VBLKh

12

where the BLK output is high.

SCP

Measure the pulse width for the section

where the BGP output is high.

VBGPh

37, 38

VSp-p

37, 38

SYNCIN: composite sync

VSdc

Signal block current

consumption

Sync block current

consumption

1

2

Electrical Characteristics

Setting conditions • Ta = 25°C, SVCC1, 2 = DVCC1, 2 = 9V, SGND1, 2 = DGND = 0V

No. Item

Sync deflection block items

Horizontal free-running

frequency

3

Horizontal sync pull-in

range

4

– 14 –

HD output pulse width

SCP

BLK output pulse width

5

6

SCP

7

BGP output pulse width

VDRIVE output

amplitude

8

VDRIVE output center

potential

9

CXA2050S

Unit

V

0.62

0.52

0.42

VEWp-p

Measurement contents Min. Typ. Max.

Measure the EWDRIVE output

Vp-p.

46: VSIN in

V

4.1

3.95

3.8

VEW dc

10.79ms

V

2.85

2.5

2.25

Output amplitude when a video

signal with an amplitude of

0.7Vp-p/100 IRE is input.

V1

V2

%

104

100

96

× 100

V1

Lin =

V2 × 2

dB

—

–38

—

f = 3.58MHz

Input fsc to CVIN.

Ratio of the fsc component of the

Yout amplitude when CTRAP = 1

against the Yout amplitude when

CTRAP = 0.

39

Measurement pins

Measurement conditions

SYNCIN: composite sync

VEWp-p

39

VEWdc

28, 30, 32

0.7Vp-p

/100 IRE

CVIN:

VRout1

28, 30, 32

100 IRE

50 IRE

CVIN:

Lin

28

CVIN:

fsc, 50 IRE

C-Trap3.58

TRAPOFF = 0/1

TRAP-F0 = 7h

No. Item Symbol

EWDRIVE output

amplitude

10

EWDRIVE output

center potential

11

Signal block items

R, G and B output

amplitude

12

– 15 –

R, G and B output

linearity

13

C-TRAP attenuation

(3.58MHz)

14

Loading...

Loading...