Sony CXA2027Q Datasheet

Analog signal processor IC

For the availability of this product, please contact the sales office.

Description

The CXA2027Q is an analog signal processor for

CCD linear image sensor output signal. This device

is suitable for 3 lines of full-color CCD linear image

sensor (ILX516K/ILX518K/ILX520K: 3648 pixels ×

3 lines/5363 pixels × 3 lines/7078 pixels × 3 lines).

This device has a built-in sample-and-hold, clamp,

multiplex, gain control amplifier circuits and can be

connected directly with external AD converters.

(Sony’s CXD2311AR, CXD1175AM or CXA1977R

are recommended as AD converters.)

Features

• Sample-and-hold circuit

• Pixel-clamp and line-clamp circuit

• Multiplex circuit

• ADC driver circuit

• Gain control amplifier circuit

• Offset control circuit

• Clock frequency: 1.5 to 6MHz (after multiplex)

Applications

Color image scanner

CXA2027Q

48 pin QFP (Plastic)

Absolute Maximum Ratings

• Supply voltage VCC –0.3 to 7 V

• Input voltage VI –0.3 to VCC + 0.3 V

• Output voltage VO –0.3 to VCC + 0.3 V

• Storage temperature Tstg –55 to +150 °C

• Allowable power dissipation

PD 640 mW

Operating Conditions (Typ. in parentheses)

• Supply voltage VCC 4.75 to 5.25 (5.0) V

• Digital input voltage High VIH 3.5 to VCC (VCC)V

•Digital input voltage Low VIL 0 to 0.8 (0) V

• Operating temperature Topr 0 to +70 °C

Structure

Bipolar silicon monolithic IC

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

– 1 –

E95210A78

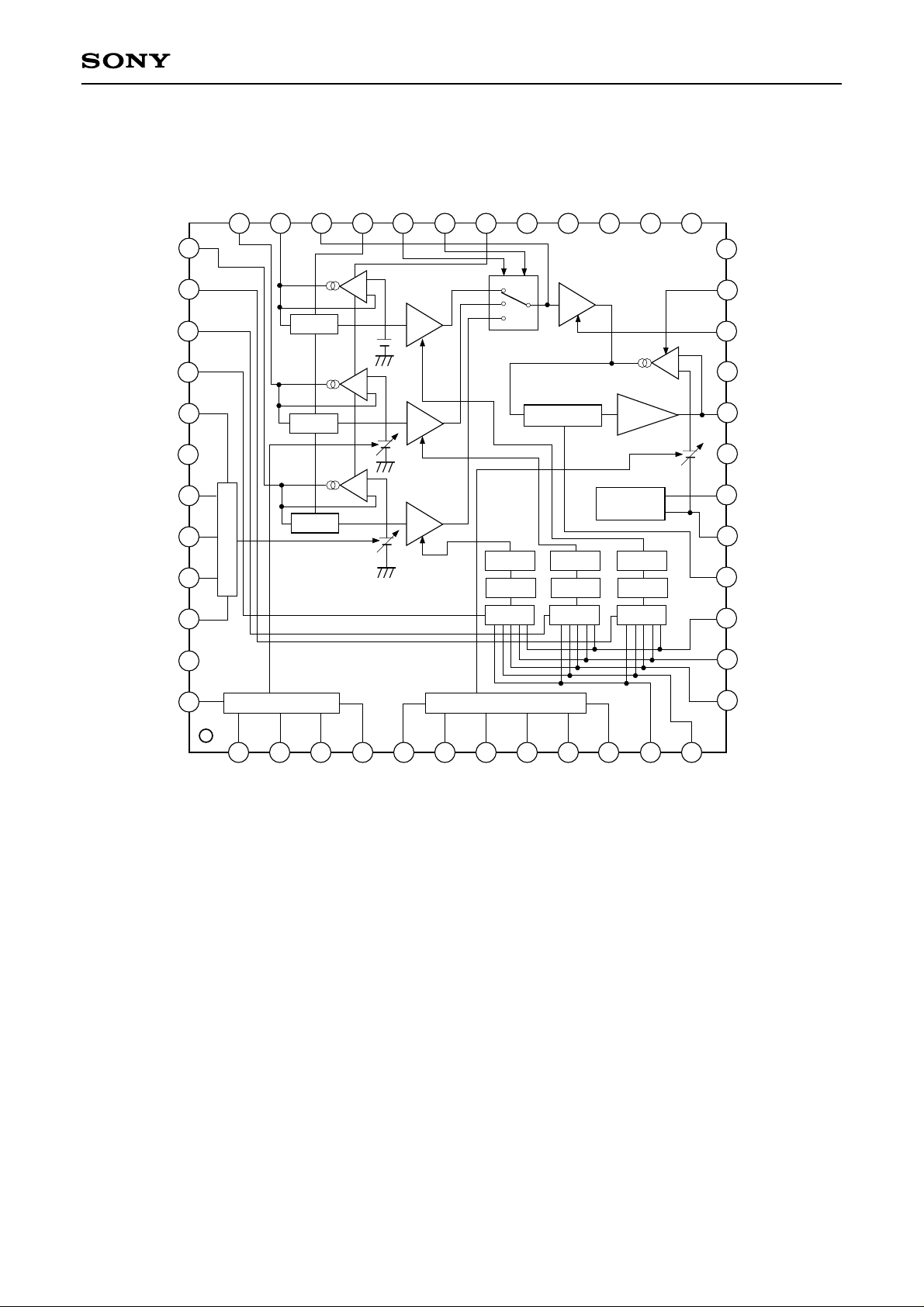

Block Diagram and Pin Configuration

CXA2027Q

B-IN

LPR

LPG

LPB

D4-0

VCCA

D4-1

D4-2

D4-3

D4-4

37

38

39

40

41

42

43

44

45

46

36

D/A

G-IN

35

R-IN

S/H

S/H

S/H

34

BUF

33

SH

32

MPX2

GCA

GCA

GCA

MPX1

31

TD3

CLP

30

29

DC shift

LOG

D/A

LATCH LATCH

TD1

TD2

27

28

GCA

Driver

VREF

LOG

D/A D/A

LOG

LATCH

26

TD5

25

TD6

24

23

22

21

20

19

18

17

16

15

TD4

LCLP

GC

VCCP

SIGOUT

GND

VRT

VRB

CLPC

LD4

VCCD

D5-0

47

48

D5-1

D/A

2

D5-2

3

D5-3

4

D5-4

5

D6-0

6

D6-1

7

D/A

D6-2

8

D6-3

9

D6-4

10

D6-5

11

LD0

14

LD3

13

LD2

121

LD1

– 2 –

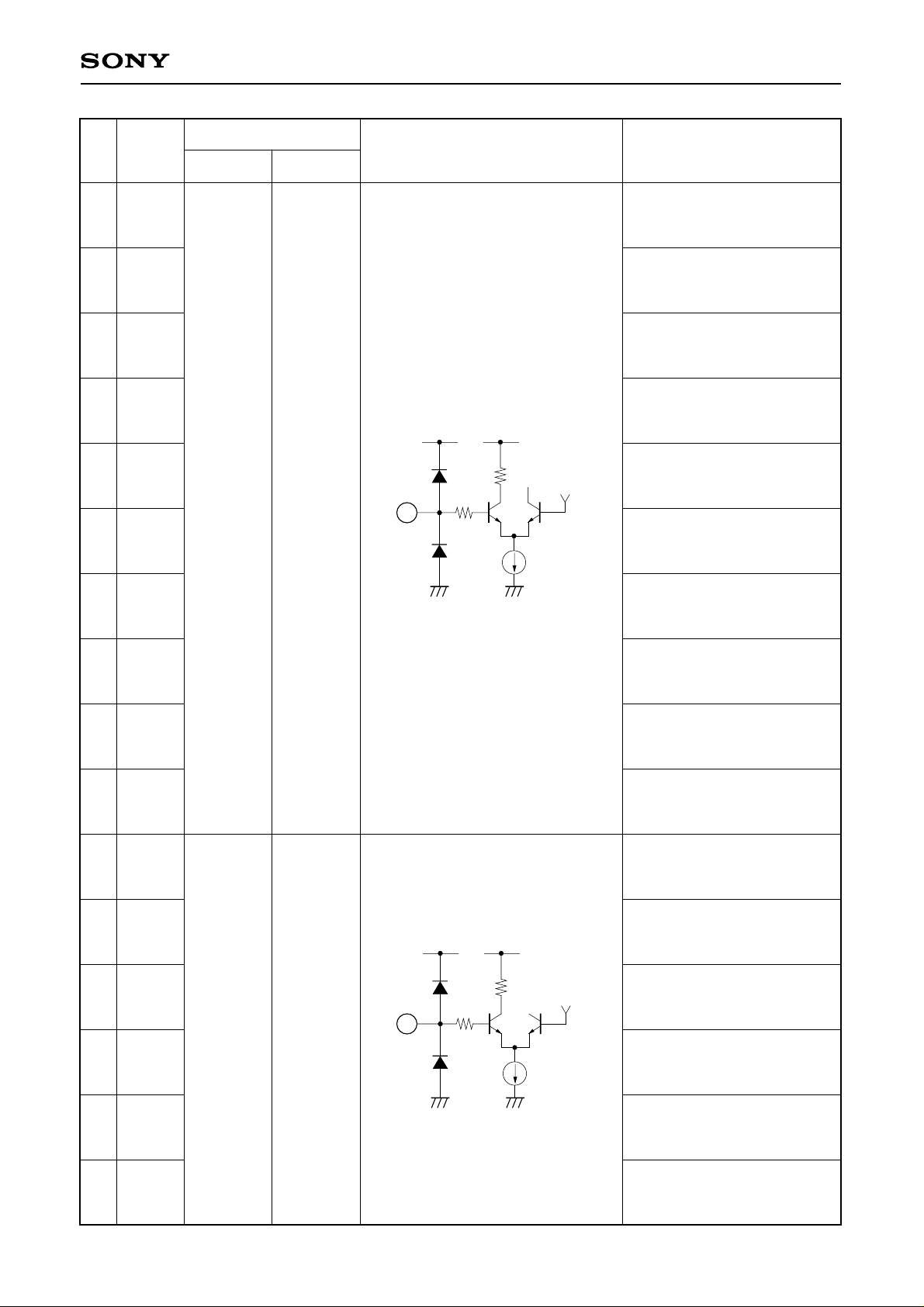

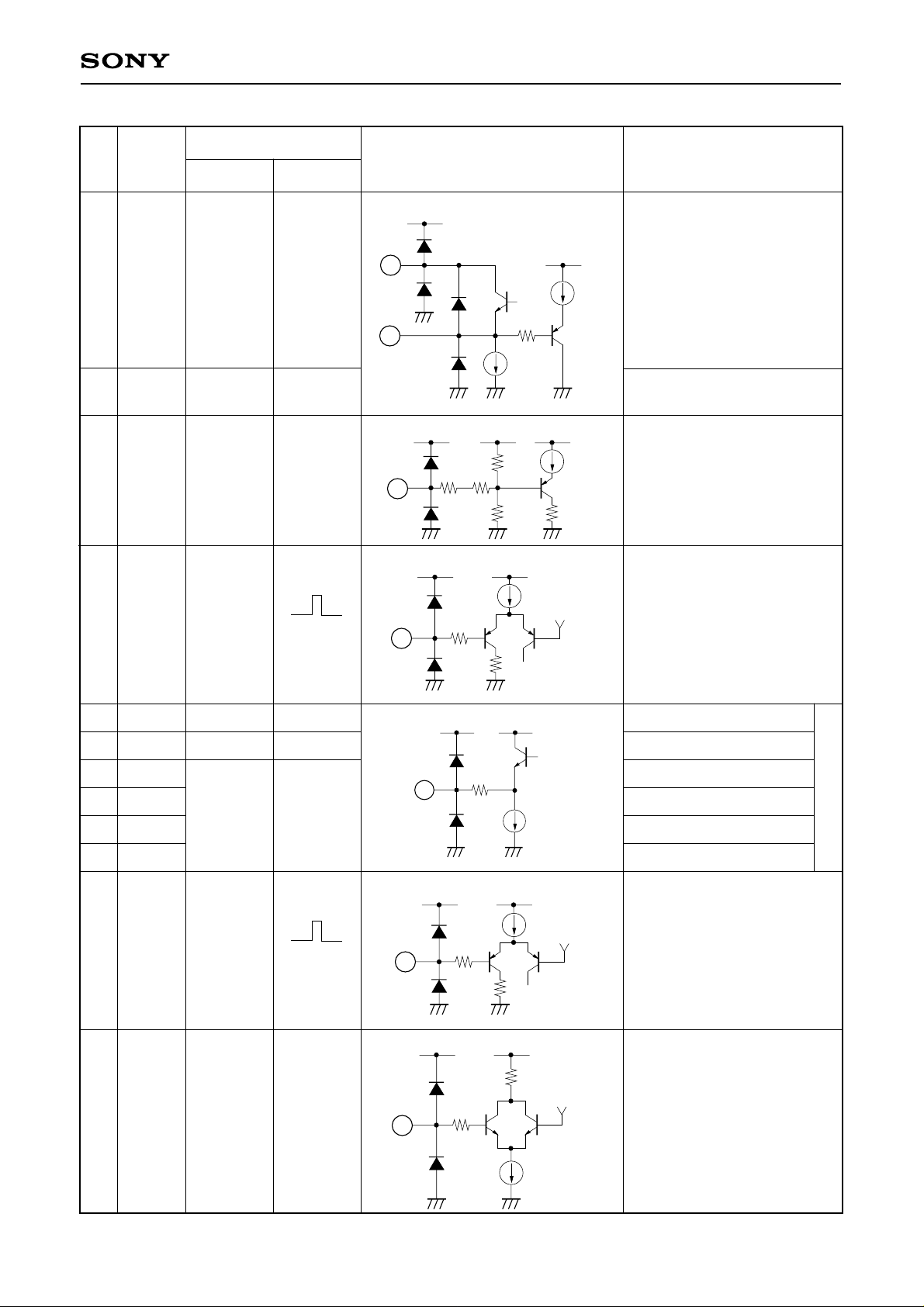

Pin Description

CXA2027Q

Pin

No.

48

1

2

3

4

41

43

Symbol

(I/O)

D5-0 (I)

D5-1 (I)

D5-2 (I)

D5-3 (I)

D5-4 (I)

D4-0 (I)

D4-1 (I)

Typical pin voltage

DC AC

Lo: 0 to 0.8V

Hi: 3.5 to 5V

Equivalent circuit Description

5-bit data input pin 1 for

G channel pixel clamp

voltage adjustment (LSB)

5-bit data input pin 2 for

G channel pixel clamp

voltage adjustment

5-bit data input pin 3 for

G channel pixel clamp

voltage adjustment

5-bit data input pin 4 for

G channel pixel clamp

VCCD VCCD

voltage adjustment

5-bit data input pin 5 for

G channel pixel clamp

voltage adjustment (MSB)

5-bit data input pin 1 for

48

129

1.5k

1.8V

B channel pixel clamp

100µ

voltage adjustment (LSB)

5-bit data input pin 2 for

B channel pixel clamp

voltage adjustment

44

45

46

5

6

7

8

D4-2 (I)

D4-3 (I)

D4-4 (I)

D6-0 (I)

D6-1 (I)

D6-2 (I)

D6-3 (I)

Lo: 0 to 0.8V

Hi: 3.5 to 5V

VCCD VCCD

5

129

1k

100µ

1.8V

5-bit data input pin 3 for

B channel pixel clamp

voltage adjustment

5-bit data input pin 4 for

B channel pixel clamp

voltage adjustment

5-bit data input pin 5 for

B channel pixel clamp

voltage adjustment (MSB)

6-bit data input pin 1 for

SIGOUT output line clamp

voltage adjustment (LSB)

6-bit data input pin 2 for

SIGOUT output line clamp

voltage adjustment

6-bit data input pin 3 for

SIGOUT output line clamp

voltage adjustment

6-bit data input pin 4 for

SIGOUT output line clamp

voltage adjustment

9

10

D6-4 (I)

D6-5 (I)

6-bit data input pin 5 for

SIGOUT output line clamp

voltage adjustment

6-bit data input pin 6 for

SIGOUT output line clamp

voltage adjustment (MSB)

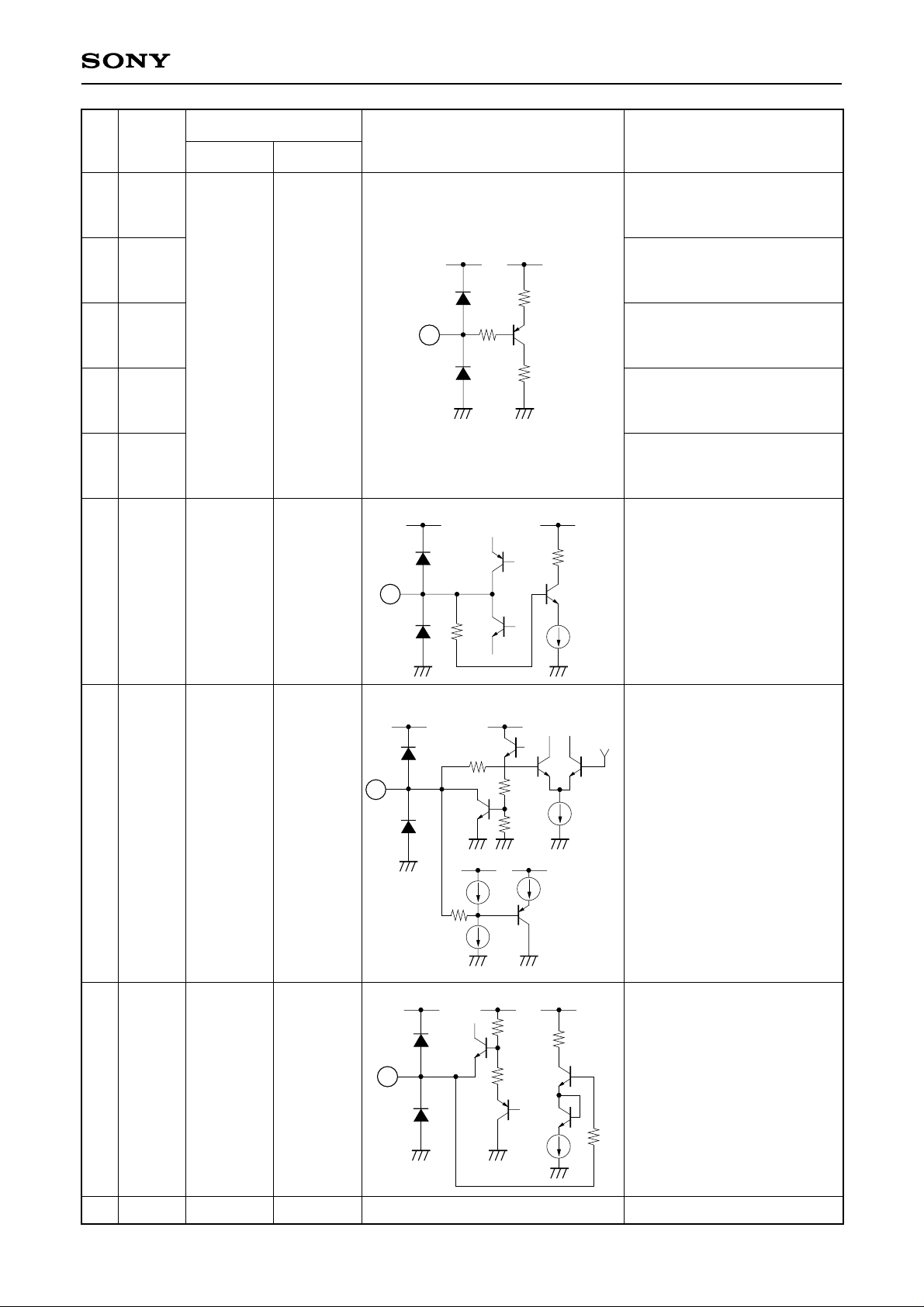

– 3 –

CXA2027Q

Pin

No.

11

12

13

14

15

16

Symbol

(I/O)

LD0 (I)

LD1 (I)

LD2 (I)

LD3 (I)

LD4 (I)

CLPC

Typical pin voltage

DC AC

Lo:

0 to 0.8V

Hi:

3.5 to 5V

Approx.

3.1V

16

Equivalent circuit Description

5-bit data input pin 1 for

pre-stage GCA gain

adjustment (LSB)

VCCD VCCD

5-bit data input pin 2 for

pre-stage GCA gain

20k

adjustment

5-bit data input pin 3 for

11

129

1.5k

pre-stage GCA gain

adjustment

5-bit data input pin 4 for

pre-stage GCA gain

adjustment

5-bit data input pin 5 for

pre-stage GCA gain

adjustment (MSB)

VCCA

VCCA

1.5k

Additional capacitance pin

for line clamp.

Add 0.47µF between this

129

6.7µ

pin and GND.

17

18

VRB (O)

VRT (O)

2.0V

4.0V

17

18

VCCA

VCCA

1k

6k

VCCA

VCCA

100µ

75µ

187.5

750

3k

2k

VCCA

100µ

100µ

VCCAVCCA

100µ

2k

2.0V

Output pin for AD converter

reference voltage VRB

Output pin for AD converter

reference voltage VRT

4k

19

GND

0V

GND pin

– 4 –

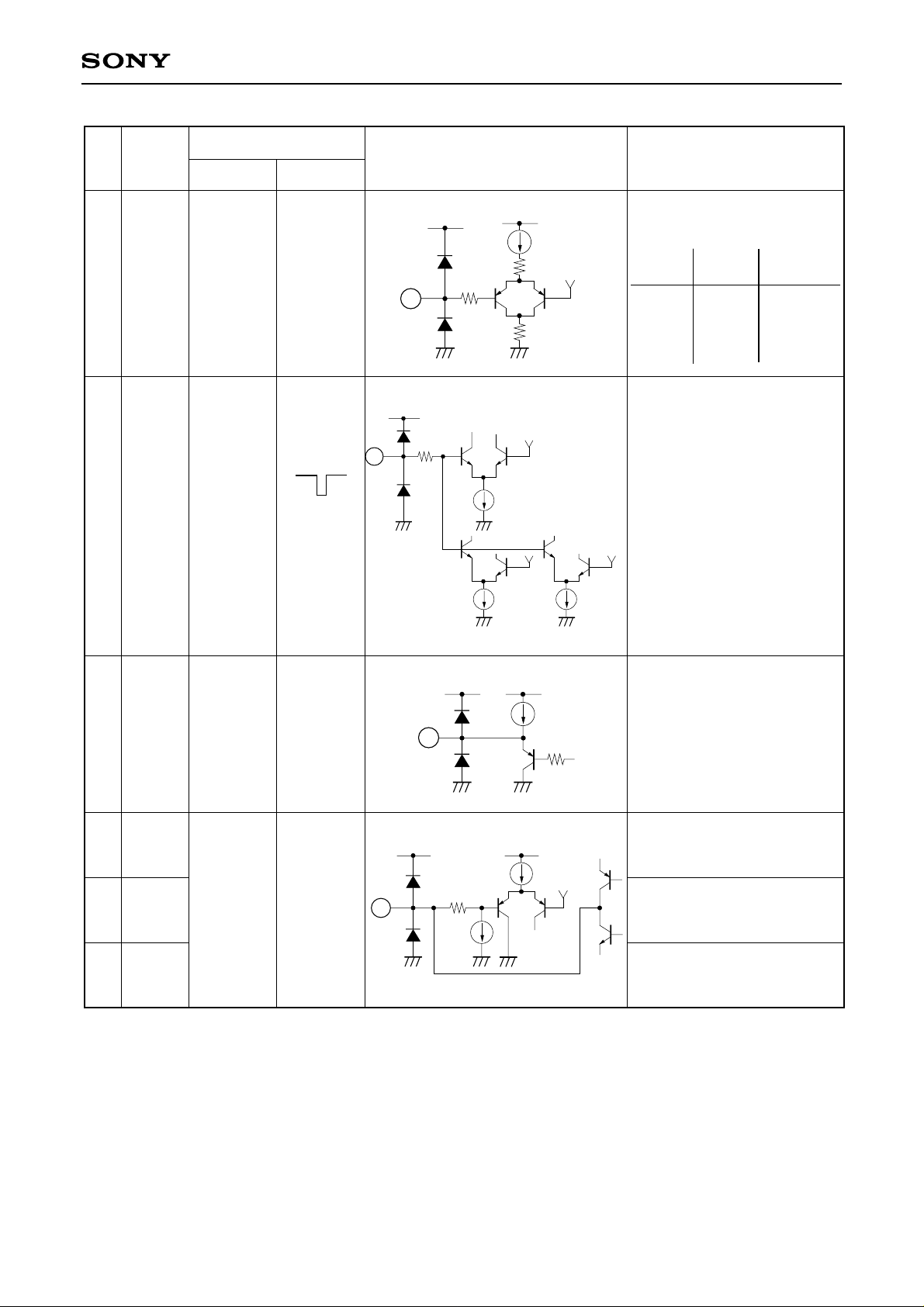

CXA2027Q

Pin

No.

20

21

22

23

Symbol

(I/O)

SIGOUT

(O)

VCCP

GC (I)

LCLP (I)

Typical pin voltage

DC AC

2.0V

+MAX1.8V

(2.0 to 3.8V)

5V

0 to 5V

Lo: 0 to 0.8V

Hi: 3.5 to 5V

Lo:

clamp OFF

Hi:

clamp ON

Equivalent circuit Description

VCCA

21

20

VCCA VCCA

129

22

VCCA VCCA

23

129

4k

2mA

20k

30k

2k

1k

100µ

VCCA

VCCA

100µ

1.5k

1.5V

100µ

Signal output pin

(to AD converter)

Power supply pin

(for signal output system)

Voltage input pin for poststage GCA gain adjustment

(Can be open; in that case

outputs 3V)

Line clamp pulse input pin

(Apply high level during the

optical black period of CCD

output)

24

25

26

27

28

29

30

31

TD4 (O)

TD6 (O)

TD5 (O)

TD1 (O)

TD2 (O)

TD3 (O)

CLP (I)

MPX1 (I)

1.7 to 3.6V

2.0 to 3.6V

1.7 to 3.6V

Lo: 0 to 0.8V

Hi: 3.5 to 5V

Lo:

clamp OFF

Hi:

clamp ON

Lo: 0 to 0.8V

Hi: 3.5 to 5V

VCCA VCCA

24

VCCA

129

30

VCCA VCCA

31

129

129

VCCA

1k

126µ

250µ

1.5k

100µ

1.5V

1.2V

DA4 analog output test pin

DA6 analog output test pin

DA5 analog output test pin

DA1 analog output test pin

DA2 analog output test pin

DA3 analog output test pin

Pixel clamp pulse input pin

(Apply high level during the

precharge period of CCD

output)

MPX channel switching

pulse input pin 1

(See high/low table under

Pin 32 in following section.)

(Use with open)

– 5 –

CXA2027Q

Pin

No.

32

33

Symbol

(I/O)

MPX2 (I)

SH (I)

Typical pin voltage

DC AC

Lo: 0 to 0.8V

Hi: 3.5 to 5V

Lo: 0 to 0.8V

Hi: 3.5 to 5V

Lo: sample

mode

Hi: hold

mode

Equivalent circuit Description

VCCA

32

VCCA

33

129

VCCA

130µ

5k

2.4V

129

1.5k

1.5V

1m

MPX channel switching pulse

input pin 2.

Pin 31 Pin 32 Pin 20

MPX1 MPX2 SIGOUT

LL

LHG

HLB

HHB

R channel

channel

channel

channel

Sample-and-hold pulse input

pin.

(Apply low level during the

effective signal period (refer

1.5V

to Note 1) of CCD output)

1.5V

1m

1m

34

35

36

37

BUF (O)

R-IN (I)

G-IN (I)

B-IN (I)

2.4V

+MAX1.8V

(2.4 to 4.2V)

CCD

effective

signal level

MAX1.5Vp-p

(Note 1)

VCCA VCCA

34

VCCA VCCA

35

129

1µ

260µ

100µ

2k

3.7V

Output test pin after MPX

(use with open)

CCD signal R channel input

pin

CCD signal G channel input

pin

CCD signal B channel input

pin

– 6 –

Loading...

Loading...