Sony CXA1992BR Datasheet

Description

The CXA1992BR is a bipolar IC developed for CD

player RF signal processing and servo control.

Features

• Automatic focus bias adjustment circuit

• Automatic tracking balance and gain adjustment

circuits

• RF level control circuit

• Interruption countermeasure circuit

• Sled overrun prevention circuit

• Anti-shock circuit

• Defect detection and prevention circuits

• RF I-V amplifier, RF amplifier

• APC circuit

• Focus and tracking error amplifier

• Focus, tracking and sled servo control circuits

• Focus OK circuit

• Mirror detection circuit

• Single power supply and dual power supplies

Applications

CD players

Structure

Bipolar silicon monolithic IC

Absolute Maximum Ratings (Ta = 25°C)

• Supply voltage VCC 12 V

• Operating temperature Topr –20 to +75 °C

• Storage temperature Tstg –65 to +150 °C

• Allowable power dissipation

PD 600 mW

Recommended Operating Conditions

Operating supply voltage VCC – VEE 4.5 to 5.5 V

– 1 –

CXA1992BR

E97216A84

RF Signal Processing Servo Amplifier

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

52 pin LQFP (Plastic)

– 2 –

CXA1992BR

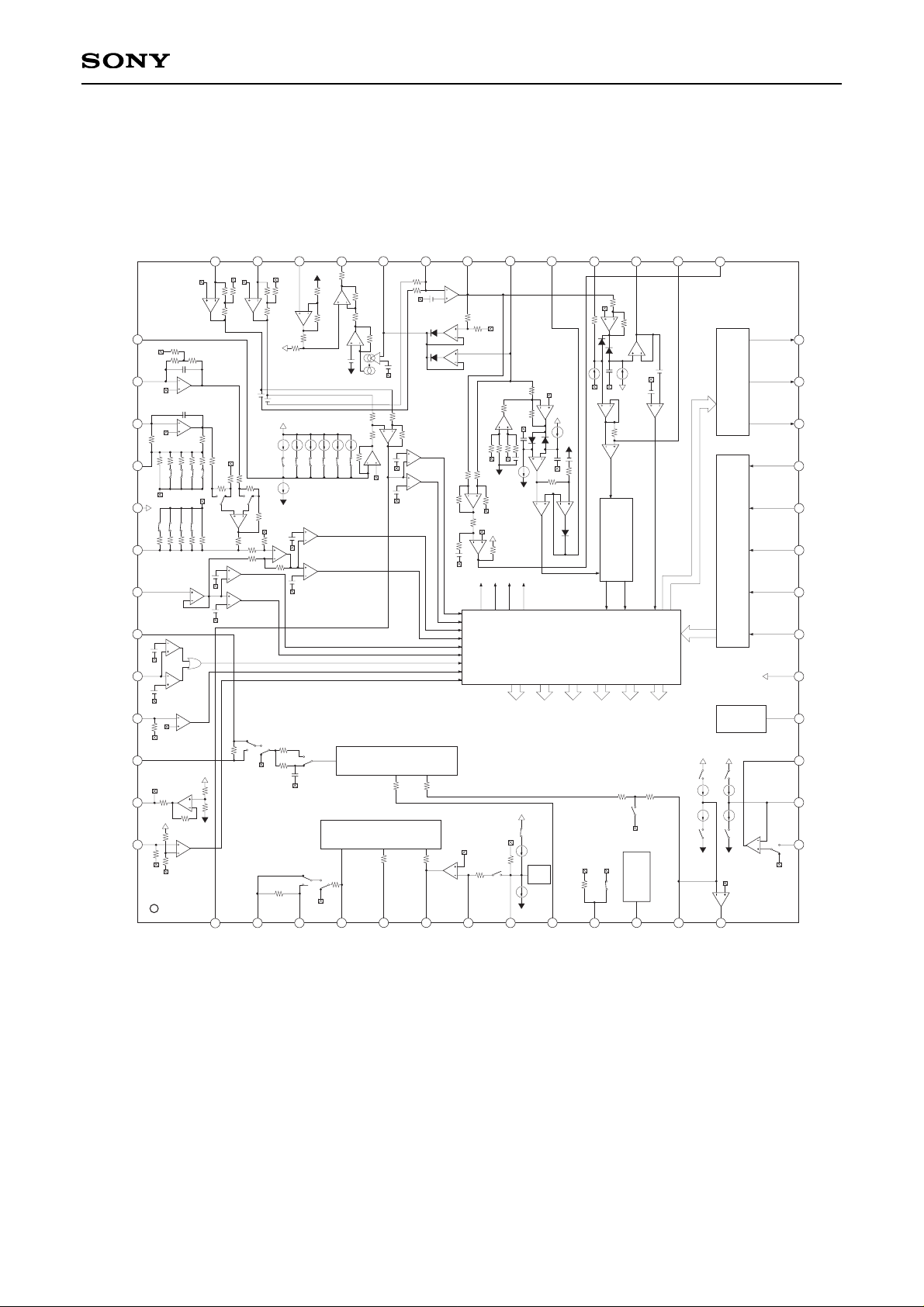

Block Diagram

PS1-4TM1-7TG1-2FS1-4IFB1-6

BAL1-4

TOG1-4

DFCTO

IFB1

VEE

FE AMP

FO. BIAS

WINDOW COMP.

TGFL

TRK. GAIN

WINDOW COMP.

TOG1

TOG2

TOG3

TOG4

E-F BALANCE

WINDOW COMP.

BAL1

F IV AMP

E IV AMP

VCC

VEE

VCC

TG1

TM1

DFCT

TRACKING

PHASE COMPENSATION

IIL DATA REGISTER

INPUT SHIFT REGISTER

ADDRESS DECODER

SENS SELECTOR

OUTPUT DECODER

FZC

VC

TDFCT

TZC

V

EE

ATSC

LPFI

TEO

TEI

V

EE

FE_BIAS

E

F

EI

FEO

FEI

FDFCT

FLB

FE_O

FE_M

TA_M

TG2

TGU

SRCH

FGD

FSET

TA_O

LD

RFTC

RF_M

RF_O

RF_I

CB

CC1

FOK

CC2

CP

PD2

PD1

PD

SL_P

SL_O

ISET

V

CC

CLK

DATA

XRST

SL_M

LOCK

C. OUT

XLT

SENS1

SENS2

PD2 IV

AMP

PD1 IV

AMP

VCC

VCC

VEE

APC

VEE

LASER POWER CONTROL

RF SUMMING AMP

VCC

VEE

LEVEL S

FZC

TZC

ATSC

BALL

BALH

TGL

TGH

FOL

FOH

LDON

LPCL

LPC

TGFL

VEE

VCC

TTL

MIRR

DFCT1

VEE

VCC

DFCT

CC1

ISET

VCC

VEE

VCC

TM5

TM6

VEE

VCC

TM3

TM4

FSET

TG2

FOCUS

PHASE COMPENSATION

TM7

VEE

VCC

FS1

Charge

up

FS2

DFCT

FS4

IIL

TTL

IIL

TTL

IIL

49

50

51

52

40

41

42

43

44

45

46

47

48

2

3

4

5

6

7

8

9

10

11

12

1

13

27

28

29

30

39

38

37

36

35

34

31

32

33

14

15

16

17

18

19

20

21

22

23

24

25

26

TM2

FZC COMP.

TZC COMP.

ATSC

WINDOW

COMP.

MIRR

↓

↓

↓

FOK

BAL2

BAL3

BAL4

IFB6

IFB5

IFB4

IFB3

IFB2

– 3 –

CXA1992BR

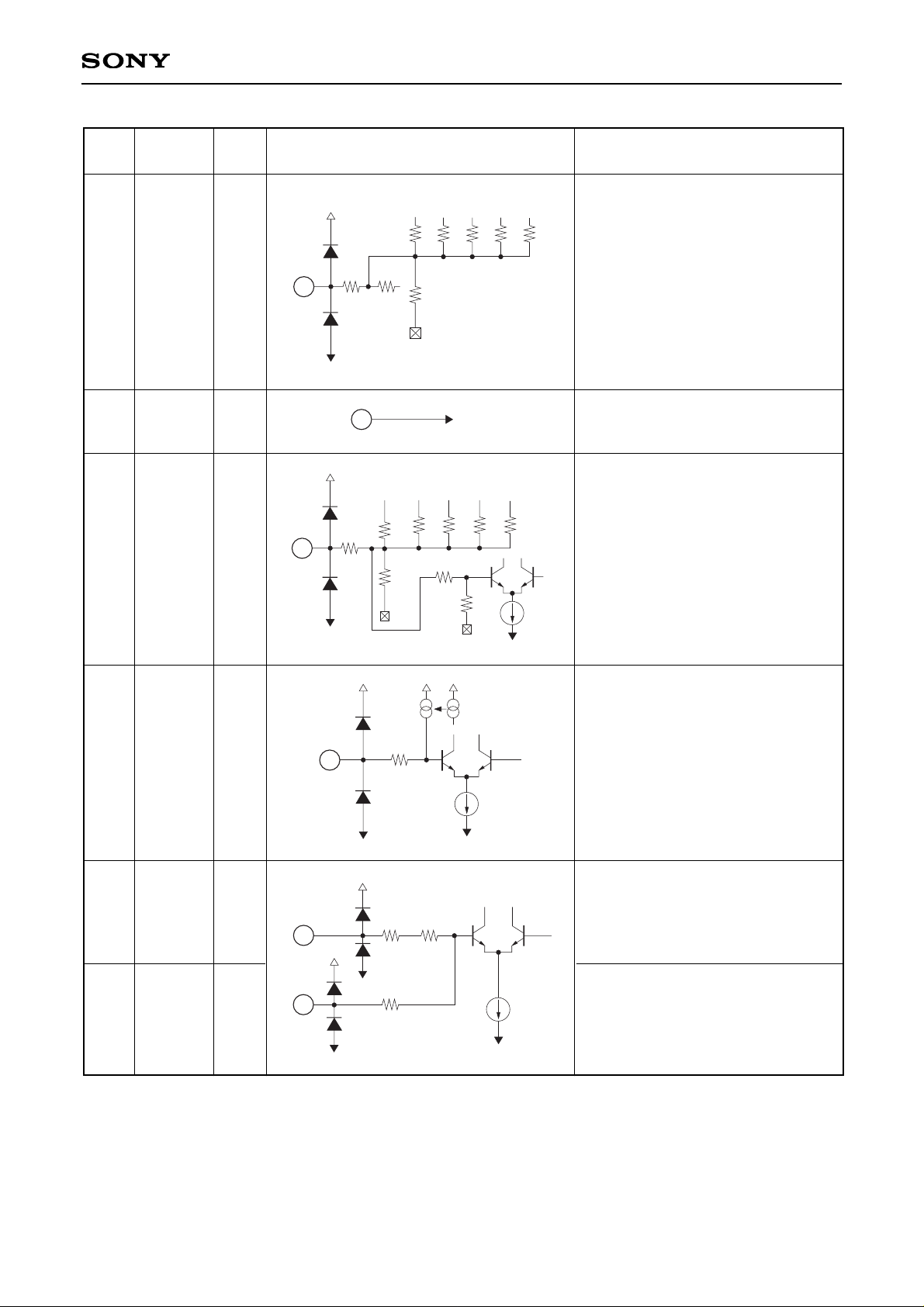

Pin Description

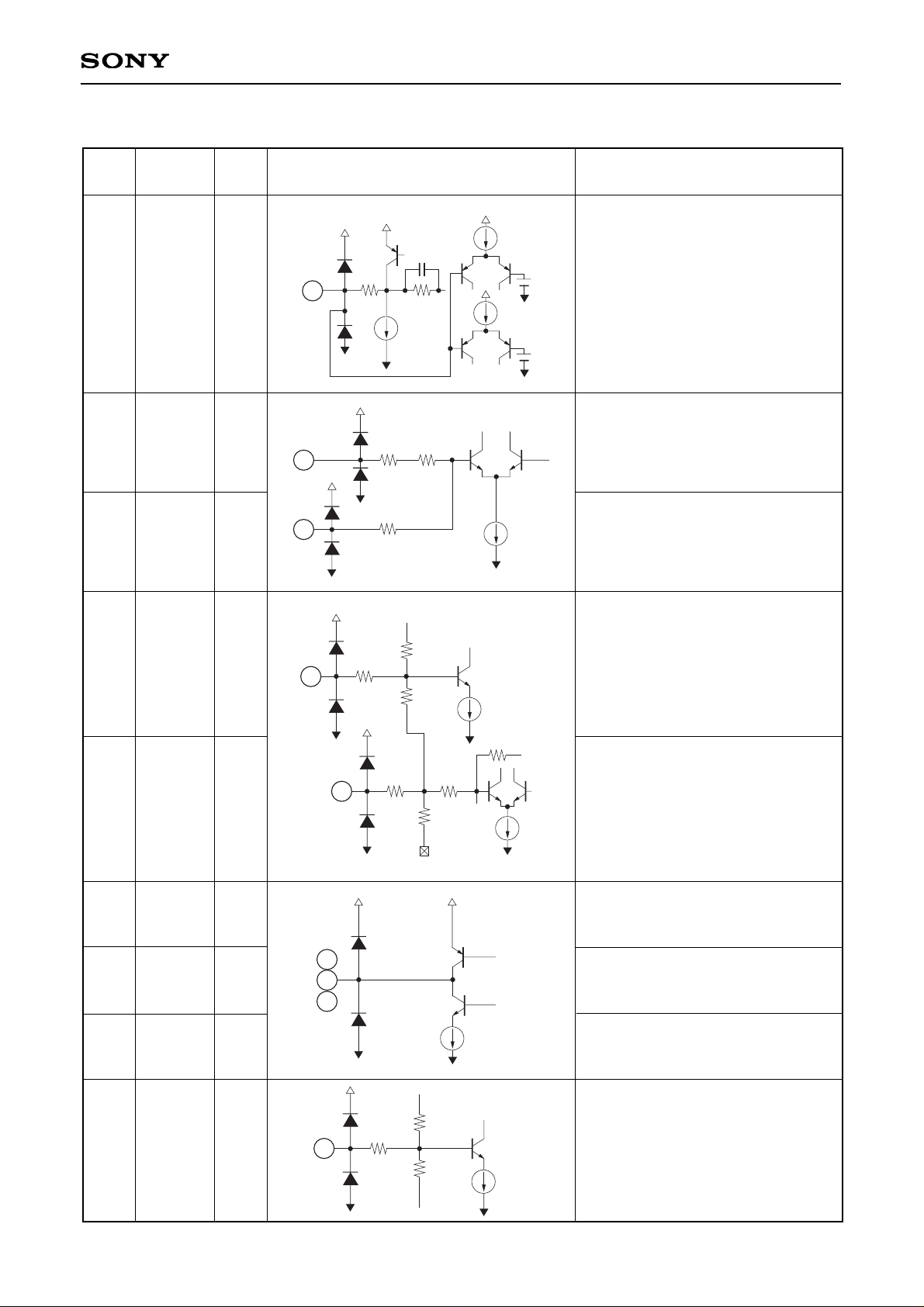

Pin

No.

Symbol

I/O

Equivalent circuit

Description

1

FEO

O

Focus error amplifier output.

Connected internally to the window

comparator input for bias

adjustment.

2

FEI

I

3

FDFCT

I

Focus error input.

Capacitor connection pin for defect

time constant.

4

FGD

I

Ground this pin through a capacitor

for cutting the focus servo highfrequency gain.

5

FLB

I

External time constant setting pin

for boosting the focus servo lowfrequency.

6

FE_O

O

13

TA_O

O

16

SL_O

O

Focus drive output.

Tracking drive output.

Sled drive output.

7

FE_M

I

Focus amplifier inverted input.

147

50k

90k

7

2µ

250µ

6

13

16

1

147

25p

174k

10µ

10µ

300µ

147

100k

147

2

3

3µ

147

130k

4

68k

4µ

40k

470k

330k

5

– 4 –

CXA1992BR

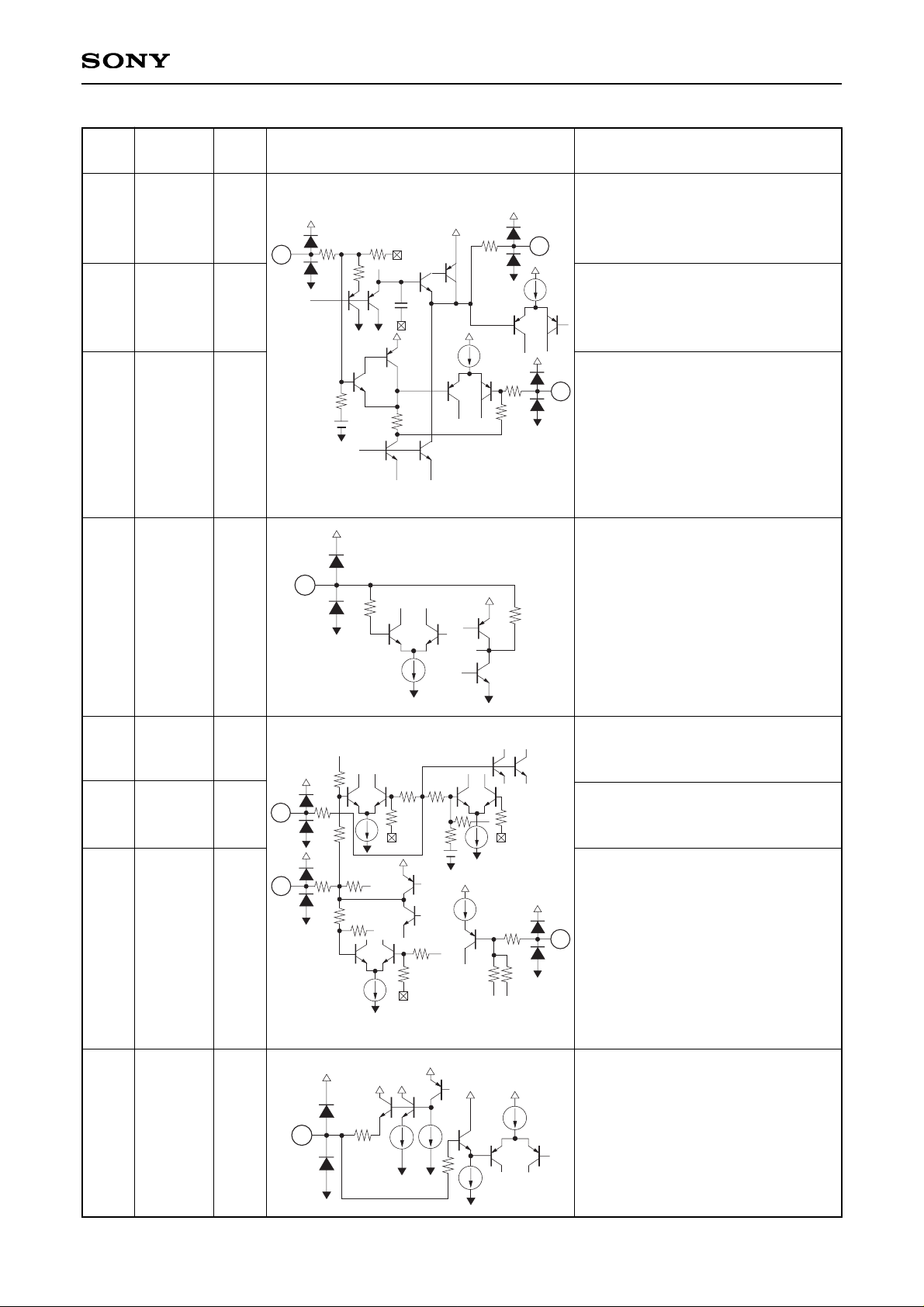

8

SRCH

I

External time constant setting pin for

generating focus search waveform.

9

TGU

I

External time constant setting pin

for switching tracking highfrequency gain.

10

TG2

I

External time constant setting pin for

switching tracking high-frequency

gain.

11

FSET

I

Peak frequency setting pin for focus

and tracking phase compensation

amplifier.

12

TA_M

I

Tracking amplifier inverted input.

14

SL_P

I

15

SL_M

I

Sled amplifier non-inverted input.

Sled amplifier inverted input.

14

147

2µ

12

147

100k

11µ

147k

11

15k 15k

147

50k

8

11µ

20k

20k

9

110k

82k

147

10

470k

147

22µ

15

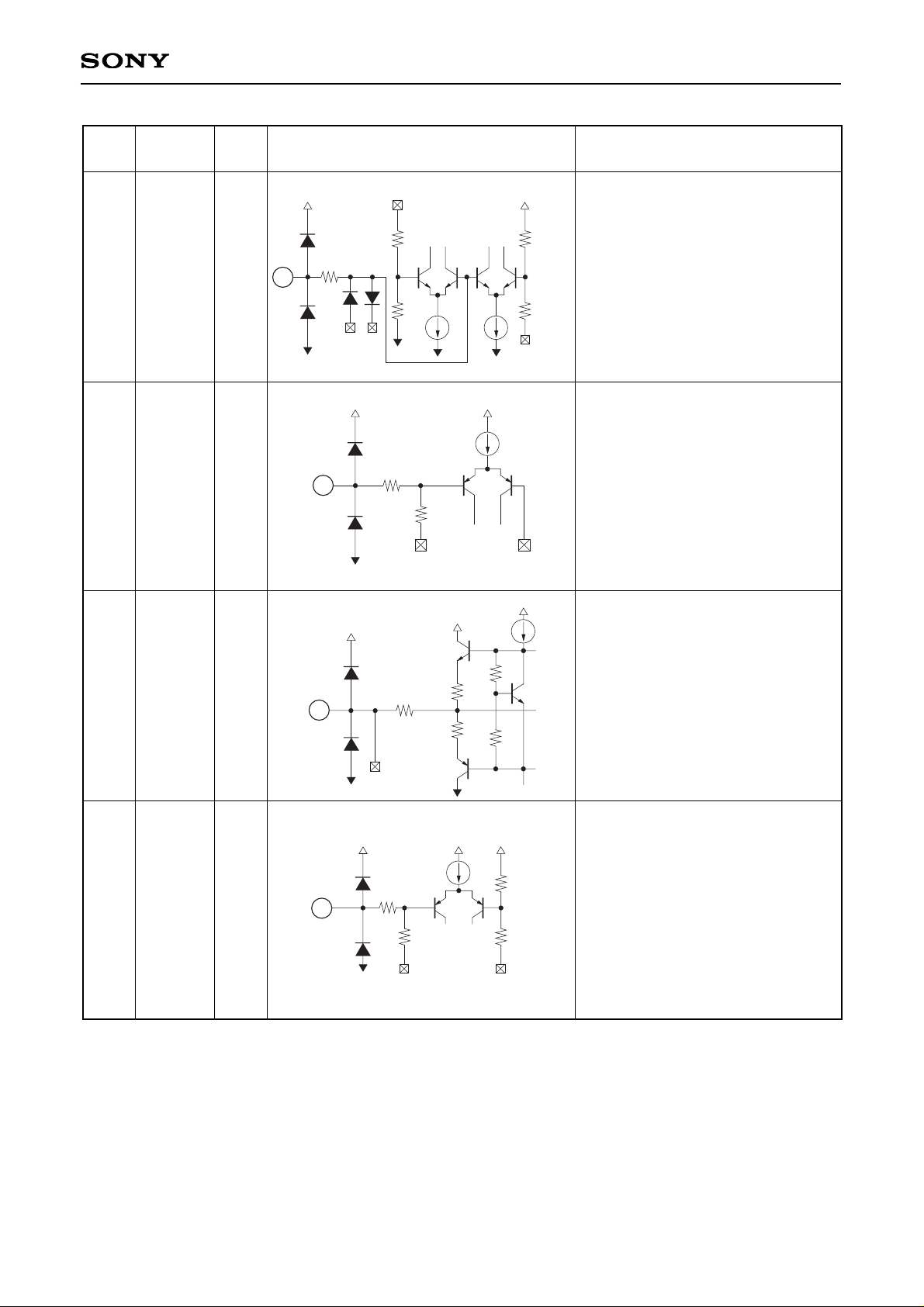

Pin

No.

Symbol

I/O

Equivalent circuit

Description

– 5 –

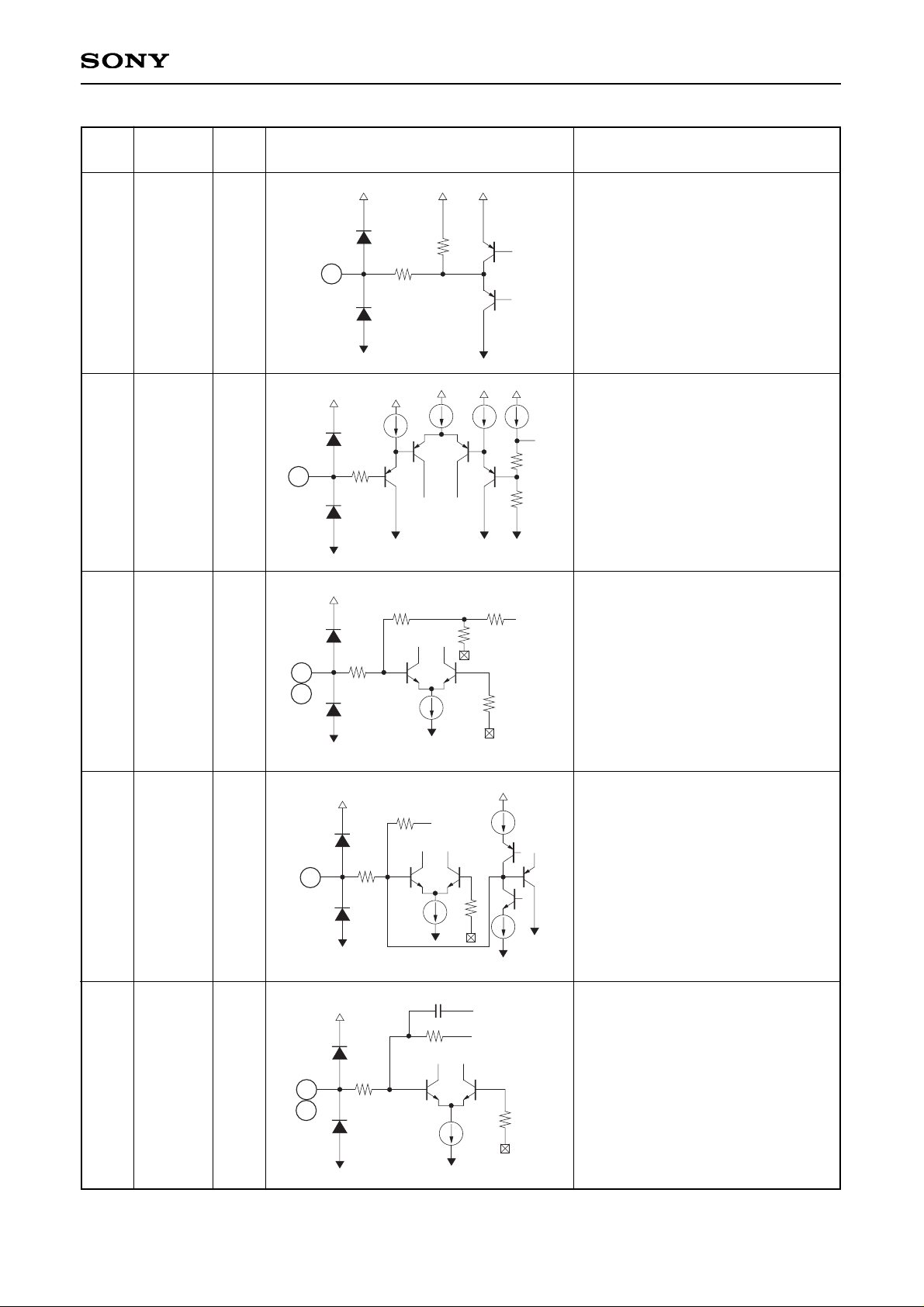

CXA1992BR

17

ISET

I

Connect an external capacitance to

set the current which determines

the Focus search, Track jump, and

Sled kick heights.

19 LOCK

I

20

CLK

I

22

DATA

I

The sled overrun prevention circuit

operates when this pin is Low.

(no pull-up resistance)

18 VCC

I

Positive power supply.

Serial data input from CPU.

(no pull-up resistance)

Serial data transfer clock input from

CPU. (no pull-up resistance)

21

XLT

I

23

XRST

I

Latch input from CPU.

(no pull-up resistance)

Reset input; resets at Low.

(no pull-up resistance)

147

17

50µ

147

19

20

22

20µ

1k

23

147

20µ

21

2k

5p

24

C. OUT

O

25

SENS1

O

26

SENS2

O

Track number count signal output.

Outputs FZC, DFCT1, TZC, BALH,

TGH, FOH, ATSC, and others

according to the command from CPU.

Outputs DFCT2, MIRR, BALL, TGL,

FOL, and others according to the

command from the CPU.

100k

147

20k

24

25

26

18

V

CC

27

FOK

O

Focus OK comparator output.

147

20k

100k

40k

27

Pin

No.

Symbol

I/O

Equivalent circuit

Description

– 6 –

CXA1992BR

28

CC2

I

29

CC1

O

30

CB

I

Input for the defect bottom hold

output with capacitance coupled.

Defect bottom hold output.

Connected internally to the

interruption comparator input.

Connection pin for defect bottom

hold capacitor.

147

147

147

28

29

30

43k

11k

120k

31

CP

I

Connection pin for MIRR hold

capacitor.

MIRR comparator non-inverted

input.

32

RF_I

I

33

RF_O O

34

RF_M

I

1.5k

31

100k

147

147

147

34

32

33

10k10k

Input for the RF summing amplifier

output with capacitance coupled.

RF sunning amplifier output. Eyepattern check point.

RF summing amplifier inverted

input.

The RF amplifier gain is determined

by the resistance connected

between this pin and RFO pin.

35

RFTC

I

External time constant setting pin

during RF level control.

147

50µ

10µ

50µ

35

Pin

No.

Symbol

I/O

Equivalent circuit

Description

– 7 –

CXA1992BR

36

LD

O

APC amplifier output.

37

PD

I

APC amplifier input.

38

39

PD1

PD2

I

I

RF I-V amplifier inverted input.

Connect these pins to the photo

diode A + C and B + D pins.

147

10k

11.6k

39

38

100µ

2k

8k

147

37

8µ

20µ

55k

10k

1k

10k

36

40

FE_BIAS

I

Bias adjustment of focus error

amplifier.

Leave this pin open for automatic

adjustment.

41

42

F

E

I

I

F I-V and E I-V amplifier inverted

input.

Connect these pins to photo diodes

F and E.

147

4k

6µ

40

147

260k

12p

500

41

42

10µ

Pin

No.

Symbol

I/O

Equivalent circuit

Description

– 8 –

CXA1992BR

43

EI

—

I-V amplifier E gain adjustment.

(When not using automatic balance

adjustment)

45

TEO

O

Tracking error amplifier output.

E-F signal is output.

46

LPFI

I

Comparator input for balance

adjustment.

(Input from TEO through LPF)

147

7µ

46

147

16k 7.5k 1.5k7.5k

10k

150k

150k

3.3k

45

260k

6.8k

75k

110k 56k 13k

43

147

27k

44

VEE

44

VEE

—

Negative power supply.

47

TEI

I

50

TDFCT

I

Tracking error input.

Capacitor connection pin for defect

time constant.

147

100k

147

3µ

47

50

Pin

No.

Symbol

I/O

Equivalent circuit

Description

– 9 –

CXA1992BR

48

ATSC

I

49

TZC I

51

VC

O

Window comparator input for ATSC

detection.

Tracking zero-cross comparator

input.

(V

CC + VEE)/2 direct voltage output.

147

75k

49

10µ

147

1k

100k

100k

1k

48

10µ 10µ

VC

50

120

120

51

52

FZC

I

Focus zero-cross comparator input.

147

10µ

52

300k 6k

54k

Pin

No.

Symbol

I/O

Equivalent circuit

Description

– 10 –

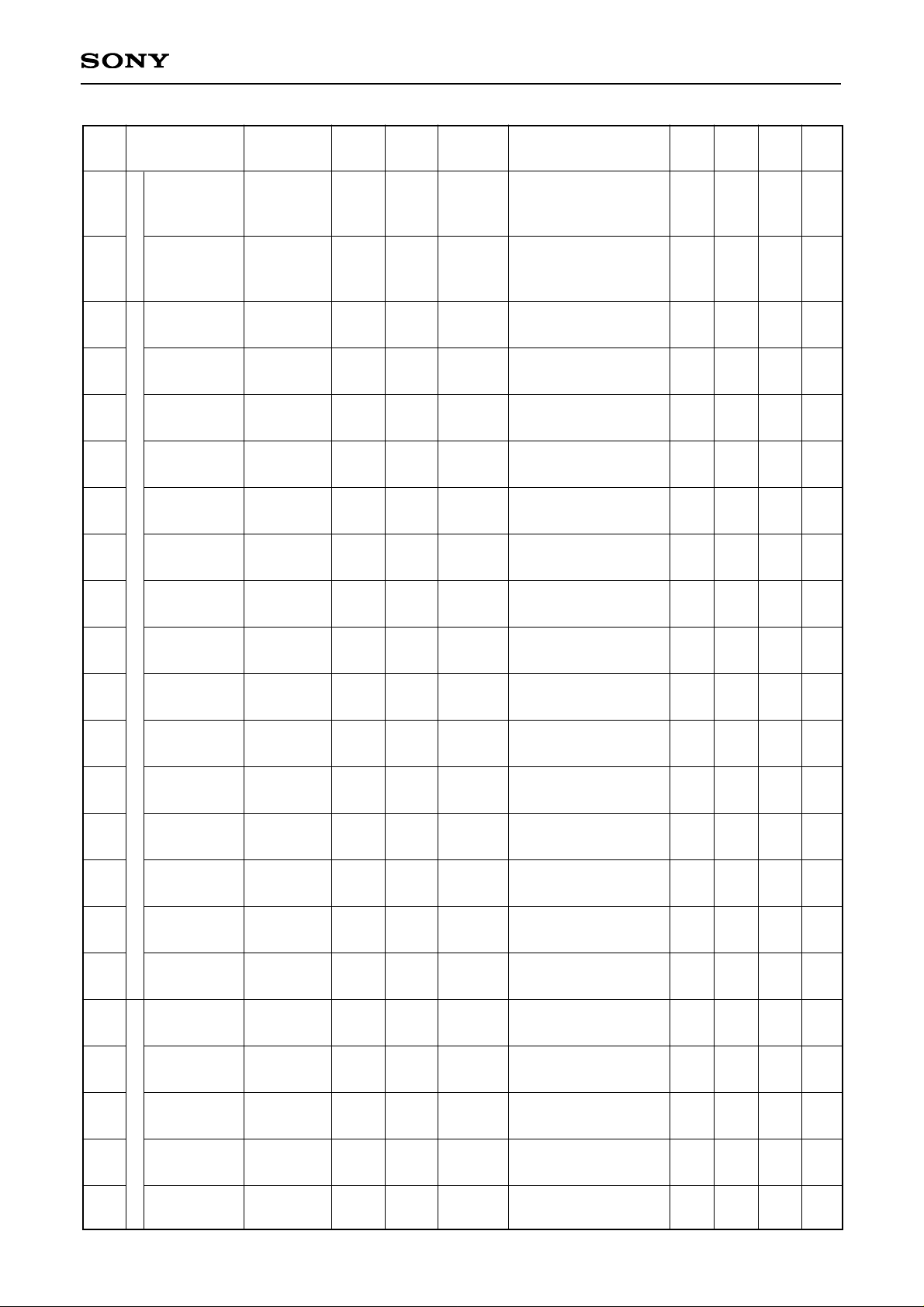

CXA1992BR

TEST

T1

T2

T3

T4

T5

T6

T7

T8

T9

T10

T11

T12

T13

T14

T15

T16

T17

T18

T19

T20

Current

consumption 1

Current

consumption 2

Center amplifier

output offset

Offset

Voltage gain

Max. output

amplitude - High

Max. output

amplitude - Low

Offset

Voltage gain 1

(PHD1)

Voltage gain 2

(PHD2)

Voltage gain

difference

Max. output

voltage – High

Max. output

voltage – Low

BIAS0

BIAS1

BIAS2

BIAS3

BIAS4

BIAS5

BIAS6

51

51

51, 51D

33S, 38, 39

33D, 38

33D, 39

1D

1S, 38

1S, 39

1S

1D, 39

1D, 38

1D

1D

1D

1D

1D

1D

1D

RST

RST

RST

RST

RST

RST

RST

39F

39F

39F

39F

39F

39F

3BF

3BE

3BD

3BB

3B7

3AF

39F

18

44

—

38

39

38

39

38

39

38

39

39

38

18

44

51

33

33

33

33

1

1

1

1

1

1

1

1

1

1

1

1

1kHz I/O ratio

V2 = 0.25VDC

V2 = –0.15VDC

1FB6: ON

1kHz I/O ratio

1kHz I/O ratio

V2 = 300mVDC

V2 = 300mVDC

IFB1, 2, 3, 4, 5, 6:

OFF

IFB1: ON, BIAS0:

reference

IFB2: ON, BIAS0: reference

Output gain difference with T15

IFB3: ON, BIAS0: reference

Output gain difference with V17

IFB4: ON, BIAS0: reference

Output gain difference with V18

IFB5: ON, BIAS0: reference

Output gain difference with V19

IFB6: ON, BIAS0: reference

Output gain difference with V20

17.2

–33.1

–100

–20

25.1

1.2

—

–120

17.4

17.4

–3

1

—

560

–31.3

5

5

5

5

5

23.3

–23.3

0

50

28.1

1.3

–1.1

0

20.4

20.4

0

1.3

–1.3

801

–25

6

6

6

6

6

33.1

–17.2

100

120

31.1

—

–1.0

120

23.4

23.4

3

—

–1

1042

–18.8

7

7

7

7

7

mA

mA

mV

mV

dB

V

V

mV

dB

dB

dB

V

V

mV

mV

dB

dB

dB

dB

dB

Item

SW conditions

(ON switches)

SD

Input

pin

Measurement

conditions

Min. Typ. Max. Unit

Electrical Characteristics (VCC = 1.5V, VEE = 1.5V, Topr = 25°C)

RF amplifierFE amplifier

Measurement pin

VC

– 11 –

CXA1992BR

FOH threshold

FOL threshold

Offset

GAIN UP (F)

GAIN UP (E)

Voltage gain

F0

Voltage gain

F1

Voltage gain

F2

Voltage gain

F3

Voltage gain

F4

Voltage gain

E0

Voltage gain

E1

Voltage gain

E2

Voltage gain

E3

Voltage gain

E4

Max. output

voltage – High

Max. output

voltage – Low

Output voltage

1

Output voltage

2

Output voltage

3

Output voltage

4

LD OFF

T21

T22

T23

T24

T25

T26

T27

T28

T29

T30

T31

T32

T33

T34

T35

T36

T37

T38

T39

T40

T41

T42

1D, 25D, 40

1D, 26D, 40

45D

41, 45S

42, 45S

41, 45S

41, 45S

41, 45S

41, 45S

41, 45S

42, 45S

42, 45S

42, 45S

42, 45S

42, 45S

41, 45D

42, 45D

36D, 37

36D, 37

36D, 37

36, 36D

36, 36D, 37

40

40

41

42

41

42

41

41

41

41

41

42

42

42

42

42

41

42

37

37

37

37

37

39F

39F

34F

308

36F

308

36F

308

34F

34E

30F

34D

34B

347

34F

30F

00

30E

30D

30B

307

34F

308

34F

308

3C4

3C4

3C4

3C4

3C0

1

1

45

45

45

45

45

45

45

45

45

45

45

45

45

45

45

36

36

36

36

36

I

FB6: ON

Pin 1 voltage when SENS1

(Pin 25) goes from High to Low

IFB6: ON

Pin 1 voltage when SENS2

(Pin 26) goes from High to Low

TOG: OFF,

BAL1, 2, 3: ON

V1 = 2 kHz, I/O ratio

TOG: OFF, BAL1, 2, 3: ON

V1 = 2 kHz, I/O ratio

TOG: OFF, BAL1, 2, 3: ON

V1 = 2kHz, TOG: OFF

I/O ratio

V1 = 2kHz, TOG1: ON

Reference to F0

V1 = 2kHz, TOG2: ON

Reference to F0

V1 = 2kHz, TOG3: ON

Reference to F0

V1 = 2kHz, TOG4: ON

Reference to F0

V1 = 2kHz, BAL: OFF

I/O ratio

V1 = 2kHz, BAL1: ON

Reference to E0

V1 = 2kHz, BAL2: ON

Reference to E0

V1 = 2kHz, BAL3: ON

Reference to E0

V1 = 2kHz, BAL4: ON

Reference to E0

V1 = 1VDC, TOG: OFF,

BAL1, 2, 3: ON

V1 = 1VDC, TOG: OFF,

BAL1, 2, 3: ON

I37 = 364µA

I37 = 439µA

I37 = 515µA

0.8mA sink

I37 = 515µA,

LD: OFF

5

–35

–25

8.6

8.6

2.5

–2.6

–4.4

–7.7

–12.2

–0.33

0.17

0.6

1.46

3.03

0.5

—

–900

–900

–100

–200

1.1

20

–20

0

11.6

11.6

5.5

–2.1

–3.9

–7.2

–11.7

2.67

0.47

0.9

1.76

3.33

0.7

–0.8

–694

–538

367

130

1.3

35

–5

25

14.6

14.6

8.5

–1.6

–3.4

–6.7

–11.2

5.67

0.77

1.2

2.06

3.63

—

–0.5

–500

–100

800

500

—

mV

mV

mV

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

V

V

mV

mV

mV

mV

V

FE amplifierTE amplifierAPC

TEST Item

SW conditions

(ON switches)

SD

Input

pin

Measurement pin

Measurement

conditions

Min. Typ. Max. Unit

– 12 –

CXA1992BR

T43

T44

T45

T46

T47

T48

T49

T50

T51

T52

T53

T54

T55

T56

T57

T58

T59

T60

T61

T62

T63

T64

50% limit

17% limit

–50% limit

–17% limit

Direct voltage

gain

FCS total gain

Feed through

1

FZC threshold

Max. output

voltage – High

Max. output

voltage – Low

Search

voltage (–)

Search

voltage (+)

Direct voltage

gain

TRK total gain

Feed through

1

Max. output

voltage – High

Max. output

voltage – Low

Jump output

voltage (–)

Jump output

voltage (+)

ATSC

threshold (–)

ATSC

threshold (+)

TZC threshold

32, 36D, 37

32, 36D, 37

36D, 37, 38,

39

36D, 37, 38,

39

2, 6D

2, 6S

26D, 52

2, 6D, 6S

2, 6D, 6S

6D

6D

13D, 47

13S, 47

13D, 47

13D, 47

13D

13D

10, 10D, 48

10, 10D, 48

25D, 49,

49B

3C7

3C5

3C7

3C5

08

—

00

08

00

08

08

02

03

25

—

20

25

20

25

20

25

2C

28

10

10

20

37

32

37

32

37

38

39

37

38

39

2

—

2

52

2

2

—

—

47

—

47

47

47

48

48

49

36

36

36

36

6

—

6

52

6

6

6

6

13

—

13

13

13

13

13

48

48

49

I37 = 273µA

Output difference with LPC ON/OFF

I37 = 394µA

Output difference with LPC ON/OFF

I37 = 742µA

Output difference with LPC ON/OFF

I37 = 621µA

Output difference with LPC ON/OFF

T9 + T47

Output gain difference between

SD = 00 and SD = 08.

Pin 52 voltage when SENS1

(Pin 25) goes from Low to High

V1 = 200mVDC

V1 = –200mVDC

T26 + T55

Output gain difference between

SD = 20 and SD = 25.

V1 = –0.5VDC

V1 = 0.5VDC

Input voltage when TG2

(Pin 10) goes from Vcc/2 to Vcc

Input voltage when TG2 (Pin 10)

goes from Vcc/2 to Vcc

Pin 49 voltage when

SENS1 (Pin 25) is 0V

300

230

–1510

–900

17.8

39.4

—

123

1

—

–640

360

12.2

18.1

—

1

—

–640

360

–25

7

–20

1020

610

–970

–580

20.8

41.6

—

150

1.3

–1.3

–540

540

14.6

20.1

—

1.3

–1.3

–540

540

–15

15

0

1510

1050

–300

–80

23.8

43.4

–30

177

—

–1

–360

640

17.6

22.1

–39

—

–1

–360

640

–7

25

20

mV

mV

mV

mV

dB

dB

dB

mV

V

V

mV

mV

dB

dB

dB

V

V

mV

mV

mV

mV

mV

RF level controllFocus servoTracking servo

TEST Item

SW conditions

(ON switches)

SD

Input

pin

Measurement

conditions

Min. Typ. Max. Unit

Measurement pin

– 13 –

CXA1992BR

T65

T66

T67

T68

T69

T70

T71

T72

T73

T74

T75

T76

T77

T78

T79

T80

T81

T82

BAL COMP

threshold – High

BAL COMP

threshold – Low

GAIN COMP

threshold – High

GAIN COMP

threshold – Low

FOK

threshold

Voltage gain

Feed through

Max. output

voltage – High

Max. output

voltage – Low

Kick voltage 1

Kick voltage 2

Max. operating

frequency 1

Min. input

operating voltage 1

Max. input

operating voltage 1

Min. operating

frequency 1

Max. operating

frequency 1

Min. input

operating voltage 1

Max. input

operating voltage 1

25D, 46,

46B

26D, 46,

46B

25D, 41,

45D

26D, 41,

45D

27D, 32

14, 14B, 15,

16S

14, 14B,

16S

14, 14B,

16D

14, 14B,

16D

16D

16D

26S, 32

26S, 32

26S, 32

25S, 38, 39

25S, 38, 39

25S, 38, 39

25S, 38, 39

300

300

308

34F

308

34F

—

25

20

25

25

25

20

20

20

20

20

10

10

10

10

46

46

41

41

32

14

14

14

14

—

—

32

32

32

38

39

38

39

38

39

38

39

46

46

45

45

32

16

16

16

16

16

16

26

26

26

25

25

25

25

Pin 46 voltage when SENS1

(Pin 25) goes from High to Low

Pin 46 voltage when SENS2

(Pin 26) goes from High to Low

Pin 45 voltage when SENS1

(Pin 25) goes from High to Low

Pin 45 voltage when SENS2

(Pin 26) goes from Low to High

Pin 32 voltage when

Pin 27 is 0V

V1 = 100Hz, I/O ratio

Output gain difference between

SD = 20 and SD = 25.

V1 = 400mVDC

V1 = 400mVDC

REV × 1

FWD × 1

Measures at SENS2

pin.

Measures at SENS2

pin.

Measures at SENS2

pin.

Measures at SENS1

pin.

Measures at SENS1

pin.

Measures at SENS1

pin.

Measures at SENS1

pin.

5

–35

175

130

–400

50

—

1

—

–750

450

30

—

1.8

—

2.5

—

1.8

20

–20

200

150

–367

—

—

1.3

–1.3

–600

600

—

—

—

—

—

—

—

35

–5

225

170

–330

—

–34

—

–1

–450

750

—

0.3

—

1

—

0.5

—

mV

mV

mV

mV

mV

dB

dB

V

V

mV

mV

kHz

Vp-p

Vp-p

kHz

kHz

Vp-p

Vp-p

Tracking servoFOKSled servoMIRRORDEFECT

TEST Item

SW conditions

(ON switches)

SD

Input

pin

Measurement

conditions

Min. Typ. Max. Unit

Measurement pin

– 14 –

CXA1992BR

S19

S26D

R40

10k

R47

10k

S26S

R53

100

R35

10k

S37

S46B

S46

S47

FEO

FEI

FDFCT

FLB

FE_O

FE_M

TA_M

TG2

TGU

SRCH

FGD

FSET

TA_O

S13D

S13S

R30

100k

R33

200k

R34

13k

R28

510k

C8

0.01µ

S10D

S10

S9

R27

10k

R29

10k

R32

100

R26

10k

S6S

S6D

R20

100k

R23

200k

R19

100

R22

10k

S12

S7

S8D

R16

13k

C4

1000P

S5

S4

R13

47k

C3

1000P

A3

S3

S2

R8

10k

S1D

S1S

R7

10k

R10

100

S52

S51D

S51I

I51

0mA

C1

1000P

A50

S50

S51

A49

S49B

S49

S48

A46

S43

R4

13k

S42

R5

390k

S41

R6

390k

S40

I40

0mA

S39

R9

30k

S38

R11

30k

V2

AC

DC

R12

330

I37

0mA

S36

S36D

I36

0mA

R14

10k

R15

1M

C5

0.1µ

R17

66k

R18

10k

S33D

R21

100

S33S

R24

10k

S32

C6

3300p

C7

0.01µ

C9

0.033µ

R31

100k

S28

S25D

R39

10k

R46

10k

S25S

R52

100

S24D

R38

10k

R45

10k

S24S

R51

100

S27D

R48

10k

S27S

R54

100

S16

S15

R44

5.1k

A14

S14B

S14

C11 47µ

R36

60k

R41

10k

S16S

S16D

R42

13k

R49

100

R2

100

R1

10k

R3

10k

S45D

S45S

S45

V1

AC

DC

GND

R50

10k

S17

R43 120k

C10 33µ

A18

A44

C2 33µ

XRST

DATA

XLT

CLK

D_GND

STORAGE1

GND

GND

DC OUTPUT

GND

GNDGND

GND

GND

STORAGE2

VCC

GND

V

EE

FZC

VC

TDFCT

TZC

V

EE

ATSC

LPFI

TEO

TEI

FE_BIAS

E

F

EI

49

50

51

52

40

41

42

43

44

45

46

47

48

2

3

4

5

6

7

8

9

10

11

121

13

2728

29

30

39

38

37

36

35

34

31

32

33

LD

RFTC

RF_M

RF_O

RF_I

CB

CC1

FOK

CC2

CP

PD2

PD1

PD

14

15

16

17

18

19

20

21

22

23

24

25

26

SL_P

SL_O

ISET

V

CC

CLK

DATA

XRST

SL_M

LOCK

C. OUT

XLT

SENS1

SENS2

R25

10k

R37

120k

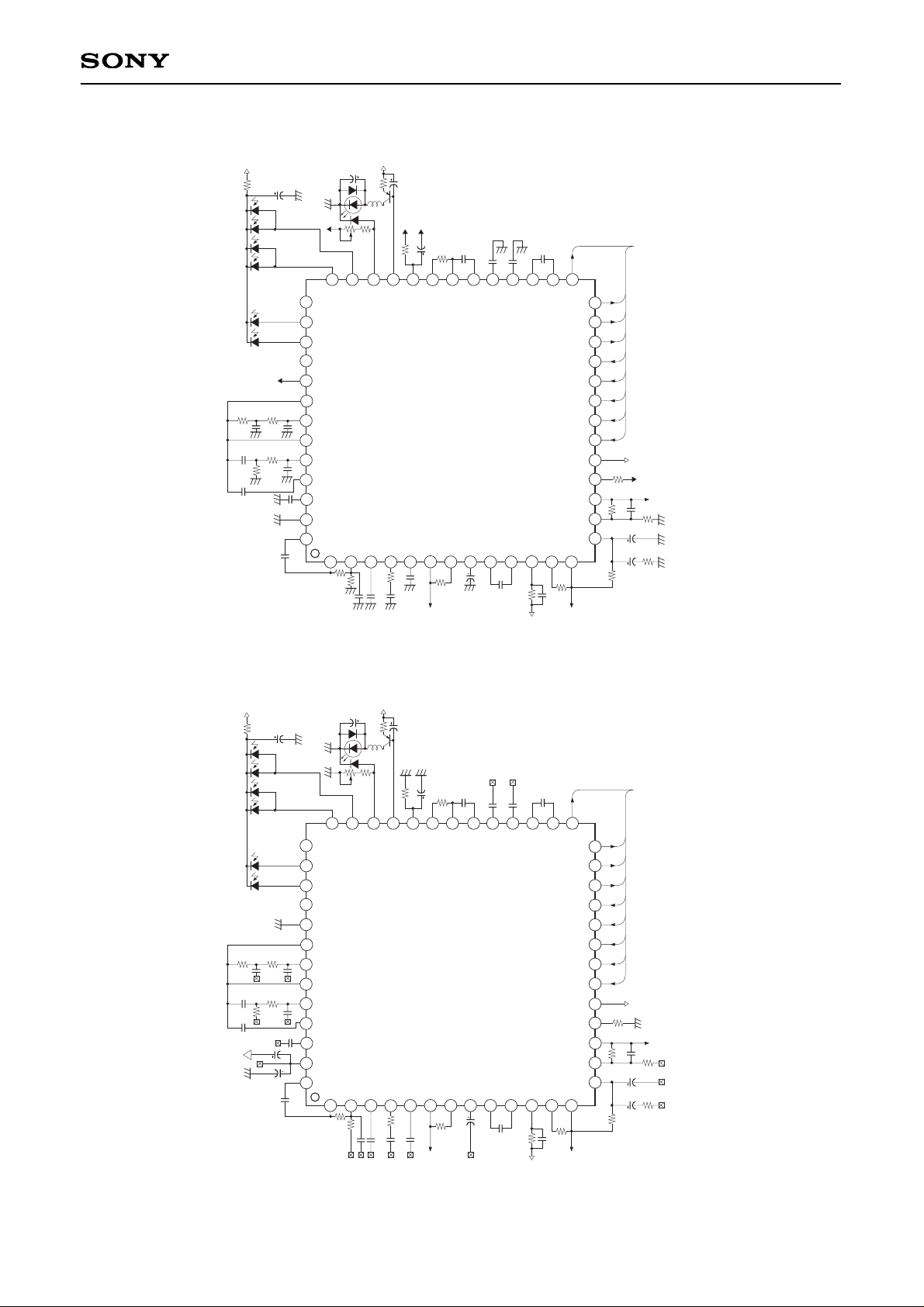

Electrical Characteristics Measurement Circuit

– 15 –

CXA1992BR

Application Circuit 1 (±2.5V power supply)

0.1µ

680k

510k

0.015µ

Vcc

MICRO

COMPUTER

DSP

0.033µ

2200p

0.1µ

0.1µ

100k

4.7µ

DRIVER

0.033µ

Vcc

100k

15k

22µ

3.3µ

DRIVER

100k

0.015µ

60k

V

EE

0.01µ

0.033µ

0.01µ

22k

Vcc

22

100µ

1µ

10µH

100

500

V

EE

VEE

100k

150k

0.047µ

0.1µ

F

E

EI

V

EE

TEO

LPFI

TEI

ATSC

TZC

TDFCT

VC

FEO

FEI

FDFCT

FGD

FLB

FE_O

FE_M

SRCH

TGU

TG2

FSET

TA_M

SENS1

C. OUT

XRST

DATA

XLT

CLK

Vcc

ISET

SL_O

SL_M

SL_P

PD2

PD1

PD

LD

RF_M

RF_O

RF_I

CP

CB

CC1

CC2

FOK

82k

Vcc

1k

3.3µ

A

C

B

D

F

E

TA_O

DRIVER

8.2k

LOCK

SENS2

RFTC

PD

LD

1M

1µ

VEE VEE

FE_BIAS

47k

330k

470p

10k

10k

0.022µ

0.022µ

FZC

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

39

38

37

36

35

34

31

32

33

41

42

45

46

47

48

49

50

51

52

1

40

44

43

0.01µ

0.01µ

Application Circuit 2 (Single +5V power supply)

0.1µ

680k

510k

0.015µ

Vcc

MICRO

COMPUTER

DSP

0.033µ

2200p

0.1µ

0.1µ

100k

4.7µ

DRIVER

0.033µ

Vcc

100k

15k

22µ

3.3µ

DRIVER

100k

0.015µ

60k

0.01µ

0.033µ

0.01µ

22k

Vcc

22

100µ

1µ

10µH

100

500

100k

150k

0.047µ

0.1µ

F

E

EI

V

EE

TEO

LPFI

TEI

ATSC

TZC

TDFCT

VC

FEO

FEI

FDFCT

FGD

FLB

FE_O

FE_M

SRCH

TGU

TG2

FSET

TA_M

SENS1

C. OUT

XRST

DATA

XLT

CLK

Vcc

ISET

SL_O

SL_M

SL_P

PD2

PD1

PD

LD

RF_M

RF_O

RF_I

CP

CB

CC1

CC2

FOK

82k

Vcc

1k

3.3µ

A

C

B

D

F

E

TA_O

DRIVER

8.2k

LOCK

SENS2

RFTC

PD

LD

1M

1µ

FE_BIAS

47k

330k

470p

10k

10k

0.022µ

0.022µ

FZC

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

39

38

37

36

35

34

31

32

33

41

42

45

46

47

48

49

50

51

52

1

40

44

43

0.01µ

0.01µ

10µ

10µ

V

CC

Application circuits shown are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for

any problems arising out of the use of these circuits or for any infringement of third party patent and other right due to same.

Loading...

Loading...