Sony CXA1871S Datasheet

—1—

E95432-TE

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

Absolute Maximum Ratings (Ta=25 °C)

• Supply voltage VCC 12 V

• Operating temperature Topr –20 to +75 °C

• Storage temperature Tstg –65 to +150 °C

• Allowable power dissipation PD 1.8 W

Operating Conditions

Supply voltage VCC 9±0.5 V

Description

The CXA1871S is a bipolar IC which integrates the

NTSC and PAL color TV luminance signal

processing, chroma signal processing, sync signal

processing, and RGB signal processing onto a

single chip.

Features

• I2C bus compatible. Various types of adjustments

and user controls performed with two bus lines

SCL and SDA.

• H and V oscillation frequencies made non-

adjusting with a countdown system.

• Non-adjusting Y system filters (chroma trap, delay

line)

• Built-in V picture distortion correction circuit

• Built-in delay line aperture compensation

• Auto cut-off function for automatic CRT cut-off

adjustment and compensation for changes with

time

• Multiple inputs

Composite Video 2 systems

(Built-in 2-input, 1-output video switch)

Y/C separation input: 1 system

On screen display input: 1 system

• Multiple system configuration possible using a non-

adjusting SECAM chroma decoder.

Applications

Color TV

Structure

Bipolar silicon monolithic IC

NTSC/PAL Y/C/Jungle

48 pin SDIP (Plastic)

CXA1871S

—2—

CXA1871S

G CUTOFF

DYNAMIC

COLOR

TRAP

DELAY

SHARPNESS

CLAMP

AUTO

PEDESTAL

Y/C MIX

CLAMP

DELAY

TOT

ACC

B.G.

ACC

DET.

COLOR

KILLER

PHASE

DET.

LPF

PHASE

SHIFT

CHROMA

DET.

Y IN

V1 IN

V2 IN

C IN

V

CC

APC

X PAL2

A PED

B-Y OUT

I

2

C BUS

DECORDER

SCL

SDA

IREF

H SYNC

REG

REGU

LATOR

H.SYNC

SEP

AFC

CERA

32f

H

VCO

1/32

2f

H

PHASE

DET

XRAY

PHASE

SHIFT

H.DRIVE

XRAY

HD

SCP

V SYNC

V.SYNC

SEP

V PLS

VOSC

V COUNT

DOWN

VOSC

V COMPENSATION

V ZOOMING

VD

ABL IN

ABL

H PHASE

AKB

TIMING

IK

CLAMP

BOUT

GOUT

ROUT

ABL LPF

V LPF

V HOLD

HP

IREF

PHASE

DET.

SW OUT

0/6DB AMP

IN SW

SW GAIN

TRAP SW

TOT SW

SUB HUE

OSD

DRIVE

G DRIVE

B DRIVE

AKB

R S/H

G S/H

B S/H

IK

B CUTOFF

DC TRAN

SHARPNESS

AFC HLOCK

NR

REF

GAMMA

GAMMA

OSD

MIX

VEX

C MODE

HV COMP

V SHIFT

V SIZE

V LIN

S CORR

V OFF

ABL

PMUTE

R OFF

G OFF

B OFF

BLK

SUB CONT

PICTURE

PICTURE

DC

SHIFT

SUB

CONT

BRIGHT

BRIGHT

SUB BRIGHT

DY COL

NR

HUE

SUB COLOR

PRE OVER

YM

RGB SW

BLUE

BLACK

OSD

BLK

OSD BLK

XRAY

41

40

38 43

39

37 36 34 33 32

42

44

8

31

29

30

27

28 26

19

21

23

18 20 222414

OSD R

OSD G

OSD B

15 16 17

5

11

6

7

10

12

25

9

AXIS

J GND

35

50/60

HUE

4.43/3.58

SW

2

CHROMA

VCO

SECAM

SECAM

REF

1

V GND

13

X' TAL PIN

DEM

AXIS

X PAL1

3

X NTSC

4

47 48

R-Y OUT

AXIS

NT/PAL

ID AXIS

PAL ID

F.F

2f

H

NT/PAL

B-Y IN

45

R-Y IN

46

COLOR

DET SW

CLAMP

COLOR

EXT

COLOR

NT/PAL

KILLER

Block Diagram

—3—

CXA1871S

Pin Configuration

R-Y IN

R-Y OUT

B-Y OUT

B-Y IN

V2 IN

SDA

SCL

V SYNC

H SYNC

SCP

REG

IREF

AFC

CERA

J GND

HP

XRAY

HD

V PLS

V LPF

V OSC

ABL LPF

VD

ABL IN

X NTSC

X PAL2

X PAL1

SECAM REF

V

CC

APC

V1 IN

A PED

Y IN

C IN

V GND

OSD BLK

OSD R

OSD G

OSD B

R S/H

R OUT

G S/H

G OUT

B S/H

B OUT

IK

V HOLD

SW OUT

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24 25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

—4—

CXA1871S

Pin Description

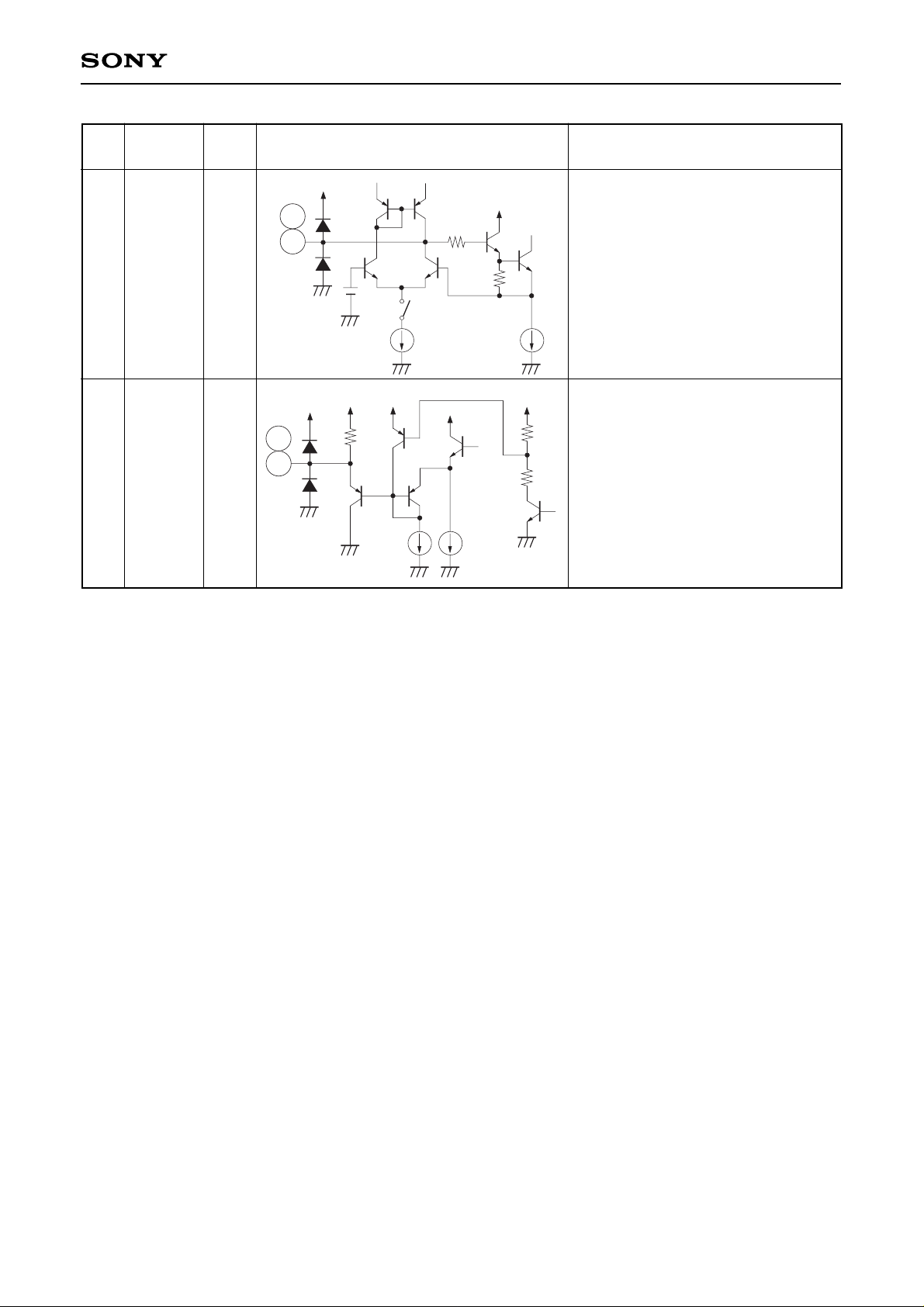

Pin

Symbol

Pin

Equivalent circuit Description

No. voltage

VCC

6 k

20 k

20 p

V

CC VCC

1

1

2

3

4

5

6

7

25

SECAM

REF

X PAL 1

X PAL 2

X NTSC

APC

V

CC

V1 IN

V2 IN

1.3 V

2.6 V

5 V

9 V

2 V

When the IC is in the SECAM

identification mode, the 4.43 MHz

VCO oscillation waveform is output

from this pin only during the VBLK

period centering on DC = 1 V. If

current of 150 µA is led from this pin

during this identification mode, the IC

switches to the SECAM mode. In the

SECAM mode, DC = 5 V.

Crystal oscillator connection pins.

Connect the PAL/N and 4.43 MHz

crystals to Pin 2, the PAL/M crystal to

Pin 3, and the NTSC crystal to Pin 4.

APC lag-lead filter CR connection pin.

Power supply pin.

Video switch input pins. Sync tip

clamping is performed, so input via

capacitors.

1.2 k

25 k

1.2 k

5

VCC

VCC

150

7

VCC

25

4 k

500

2

3

4

VCC

VCC

—5—

CXA1871S

Pin

Symbol

Pin

Equivalent circuit Description

No. voltage

2 k

30 k

12 k

25 k

500

9

VCC

VCC

VCC

8

9

10

11

V HOLD

SW OUT

Y IN

A PED

0.7 V

—

3.5 V

3.5 V

Peak hold pin for V sync separation.

Connect a capacitor.

Video switch output pin.

Y signal input pin. Input via a

capacitor.

Standard input level: 2 Vp-p

Auto pedestal (black stretch) black

peak hold pin. Connect a capacitor.

50 k

1.2 k

10

V

CC

VCC

16 k

20 k

20 k

1.2 k

11

VCC

VCC VCC VCC

55 k

VCC

8

150

1 k

50 k

—6—

CXA1871S

Pin

Symbol

Pin

Equivalent circuit Description

No. voltage

6 k 6 k

30 k

30 k

12

V

CC

12

13

14

15

16

17

18

20

22

C IN

V GND

OSD BLK

OSD R

OSD G

OSD B

R S/H

G S/H

B S/H

—

—

—

—

—

Chroma signal input pin.

Standard input level (burst level)

: 570 mVp-p

Video system (Y/C/RGB) GND pin.

Blanking signal input pin for OSD

RGB input.

0 to 1 V: Blanking not performed.

2 to 3 V: Signal from Y IN/C IN

lowered by –6 dB.

4 to 6 V: R, G and B outputs become

lower than black level.

Digital R, G and B signal input pins for

on screen display.

0 to 1 V: No OSD display.

2 to 3 V: OSD level 49 IRE (34 IRE)

4 to 6 V: OSD level 96 IRE (67 IRE)

Figures in parentheses are for when

the I2C OSD register is set to 0.

Sample-and-hold pins for R, G and B

AKB (Auto Kinetic Bias). Connect to

GND via capacitors.

40 k

15 k

2 k

60 k

30 k

2 k

60 k

30 k

2 k

60 k

14

30 k

2 k

VCC VCC

VCC

15

16

17

VCC

1.2 k

18

20

22

VCC

—7—

CXA1871S

Pin

Symbol

Pin

Equivalent circuit Description

No. voltage

19

21

23

24

26

27

28

R OUT

G OUT

B OUT

IK

ABL IN

VD

ABL LPF

—

—

—

—

—

R, G and B output pins.

Inputs the signal obtained by

converting the CRT beam current (IK)

into voltage. Connect to an emitter

follower via a capacitor.

ABL voltage input pin.

Vertical deflection sawtooth wave

output pin.

ABL signal LPF pin. Connect a

capacitor. If the AKB loop is unstable

when the power is turned on, this pin

is lowered to around 0.3 V.

150

5 k

19

21

23

VCC

VCC VCC

150

24

V

CC

VCC

150

10 k

30 k

26

V

CC

5 k

3 k

3 k

15 k

24 k

27

VCC

VCC

VCC

VCC

24 k

100 k

35 k

10 k

28

VCC VCC

VCC

—8—

CXA1871S

Pin

Symbol

Pin

Equivalent circuit Description

No. voltage

29

30

31

32

33

V OSC

V LPF

V PLS

HD

XRAY

—

5 V

—

—

—

Connect a capacitor to generate the V

sawtooth wave.

Connect a capacitor to hold the AGC

voltage which maintains the V

sawtooth wave at a constant

amplitude.

V pulse output pin. A negative

polarity pulse 3 to 3.5 H width is

output from this pin.

High level: 4.5 V

Low level: 0 V

H drive output pin. This pin is output

at the open collector.

X-ray protection circuit input pin.

When a pulse with a width of 7 V or

more is input, HD output becomes low

and R, G and B outputs are blanked.

This status is maintained until the

power supply is turned off.

Vilmax = 2.4 V

Vihmin = 3.0 V

100

100

29

VCC

VCC

VCC

VCC

20 k

20 k

32

19 k

30 k

40 k

30 k

63 k

27 k

33

VCC

VCC VCC

VCC

VCC

30

VCC

74 k

18 k

31

VCC

VCC

—9—

CXA1871S

Pin

Symbol

Pin

Equivalent circuit Description

No. voltage

34

35

36

37

38

HP

J GND

CERA

AFC

IREF

3.3 V

(at no

signal)

—

2.3 V

3.2 V

2.6 V

H pulse input pin. Inputs a 3 to 5 Vp-p

signal via a capacitor.

Jungle system (H/V) GND pin.

Connect a 32 fh (503.5 kHz) ceramic

oscillator.

AFC lag-lead filter CR connection pin.

Connect a 15 kΩ resistor between this

pin and GND.

VCC

10 k

28 k

V

CC

VCC

330

36

VCC

46 k

1.2 k

V

CC

VCC

37

150

20 k

38

VCC

VCC

10 k

60 k

VCC

VCC

34

—10—

CXA1871S

Pin

Symbol

Pin

Equivalent circuit Description

No. voltage

39

40

41

42

43

44

REG

SCL

SDA

SCP

H SYNC

V SYNC

7 V

—

—

2.6 V

3.8 V

Regulator pin for voltage generated

internally from VCC. Connect a

capacitor for stabilization.

I2C bus SCL (Serial Clock) and SDA

(Serial Data) pins.

Vilmax = 1.5 V

Vihmin = 3 V

Volmax = 0.4 V

Outputs BGP, HBLK and VBLK as

SCP (Sand Cathle Pulse).

The Typ. waveform is as follows.

H sync separation input pin. Inputs a

2 Vp-p video signal via a capacitor

and resistor.

V sync separation input pin. Inputs a

2 Vp-p video signal via a capacitor

and resistor.

150

14 k

24 k

20 k

43

10 µA

V

CC

VCC

150

10 k

26 k

31 k

10 k

20 k

44

20 µA

1.2 k

40 k

4 p

39

50 µA

VCC

VCC VCC

VCC

VCC

4 k

4 k

VCC

40

41

VCC

1.2 k

VCC

500 µA

VCC

VCC

BGP

H,VBLK

0.3 V

2.5 V

5.0 V

—11—

CXA1871S

Pin

Symbol

Pin

Equivalent circuit Description

No. voltage

1.2 k

100 µA

VCC

45

46

BGP

VCC

50 k

45

46

47

48

R-Y IN

B-Y IN

B-Y OUT

R-Y OUT

5.2 V

5 V

Color difference signal input pins.

Input via capacitors.

Standard input level

B-Y: 1.33 Vp-p

R-Y: 1.05 Vp-p

Color difference signal output pins.

Standard input level

B-Y: 0.665 Vp-p

R-Y: 0.525 Vp-p

20 k

80 k

10 k

47

48

VCC

VCC VCC VCC

—12—

CXA1871S

Video In: Sig-H2,H3

AFC: 0

Video In: Sig-H6

AFC: 0

Video In: Sig-H7

AFC: 0

Video In: Sig-H6

AFC: 1

Video In: Sig-H7

AFC: 1

Video In: Sig-H6

AFC: 2

Video In: Sig-H7

AFC: 2

Video In: Sig-H1

Video In: Sig-H1

Video In: Sig-H1

Video In: Sig-Y1

HPHASE: F

Video In: Sig-Y1

HPHASE: 7

Video In: Sig-Y1

HPHASE: 0

Video In: Sig-Y1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

Horizontal free running

frequency

Horizontal sync pull-in

range

AFC gain 1

AFC gain 2

AFC gain 3

HD output pulse width

HD output high level

HD output low level

Horizontal phase

operating range 1

Horizontal phase

operating range 2

Horizontal phase

operating range 3

HP blanking delay

time 1

HP blanking delay

time 2

SCP BGP output level

SCP BLK output level

SCP low level

Overvoltage protection

circuit VTH

H system items

Electrical Characteristics

Setting conditions

• Ta = 25 °C, VCC = 9 V

• I2C bus register should be set to “I2C Bus Register Initial Settings”.

No.

Item Symbol

Measurement

Measurement

Measurement method

conditions pin

Min. Typ. Max. Unit

70 105 140 mA

1

Current consumption 1 ICC1 6 Measure the VCC pin inflow current.

No. Item Symbol

Measurement

Measurement

Measurement method

conditions pin

Min. Typ. Max. Unit

15.47 15.65 15.83 kHz

–400 — 400 Hz

0.12 0.30 0.48 µs

— 0.5 — µs

0.75 1.2 1.75 µs

24 26 28 µs

8.7 9 — V

0.5 0.8 1.1 V

–4.3 –3.3 –2.3 µs

–1.5 –0.5 0.5 µs

1.3 2.3 3.3 µs

— 100 — ns

— 100 — ns

4 5.0 6 V

2.5 V

0.3 V

2.4 2.6 2.8 V

Hfree

∆H

AFCmax

AFCcen

AFCmin

HD, W

HD, H

HD, L

HPHmax

HPHcen

HPHmin

HPBLK1

HPBLK2

VSB

VSBL

VSL

XVTH

Check that I

2

C register HLOCK is 1.

AFCmax=t1-t2

AFCcen=t1-t2

AFCmin=t1-t2

t1: Video In: Time from fall

of Sig-H6 to rise of Pin 34.

t2: Video In: Time from fall

of Sig-H7 to rise of Pin 34.

32

34

34

34

32

23

34

23

34

42

32

VSL

VSBL

VSB

Pin 23

Pin 34

HPBLK1

HPBLK2

Pin 23

HPH

HD,H

HD,L

HD,W

Check that HD appears at 2.4 V and disappears

at 2.8 V.

—13—

CXA1871S

Video In:Sig-V1

V SHIFT:F

V SHIFT:0

V SHIFT:1F

V SIZE:0

V SIZE:3F

S CORR:0

S CORR:F

V LIN:0

V LIN:F

HV COMP: 0,

Pin 26: 6 V

HV COMP: 7,

Pin 26: 6 V

HV COMP: 0,

Pin 26: 0 V

HV COMP:7,

Pin 26: 0 V

19

20

21

22

23

24

25

26

27

28

29

30

31

V PLS high level

V PLS low level

VD output

center voltage

V SHIFT

variable range 1

V SHIFT

variable range 2

V SIZE

variable range 1

V SIZE

variable range 2

S CORR

variable range 1

S CORR

variable range 2

V LIN

variable range 1

V LIN

variable range 2

V zooming 1

V zooming 2

V system items

No. Item Symbol

Measurement

Measurement

Measurement method

conditions pin

Min. Typ. Max. Unit

4 4.5 5 V

0 0.1 0.5 V

2.75 2.9 3.05 V

–140 –125 –115 mV

110 120 140 mV

0.9 1.1 1.2 V

1.5 1.65 1.8 V

45 65 85 mV

–55 –35 –15 mV

90 120 140 mV

60 90 110 mV

0 3 15 mV

60 80 100 mV

VPLS, H

VPLS, L

VDcen

VSHIFT–

VSHIFT+

VSIZE–

VSIZE+

∆Sa

∆Sc

∆La

∆Lc

∆VZ1

∆VZ2

Vb

Vb-VDcen

Vb-VDcen

Vc-Va

Vc-Va

Vsa=Va

Vsc=Vc

Va-Vsa

Vc-Vsc

Vla=Va

Vlc=Vc

Va-Vla

Vc-Vlc

Vsmin=

Vc-Va

Vsmax=

Vc-Va

Vsmin(Vc-Va)

Vsmax(Vc-Va)

31

27

Video

In:

Sig-V1

Vc

Vb

Va

GND

Pin 27

VTRIG

0.1 ms

8.75

ms

16.57

ms

VPLS, L

VPLS, H

—14—

CXA1871S

Video In:Sig-Y1

SUBCONT: F

SUBCONT: 0

TRAP SW: 0

TRAP SW: 1

TRAP SW: 0

TRAP SW: 1

SHARP

NESS: F

SHARP

NESS: 7

SHARP

NESS: 0

DELAY=0

DELAY=2

DC TRAN: 0

DC TRAN: 7

Pin 11: 3 V

Pin 11: 5 V

Pin 11: 3 V

Pin 11: OPEN

32

33

34

35

36

37

38

39

40

41

42

43

44

45

R output level

Sub-contrast

variable range 1

Sub-contrast

variable range 2

Trap attenuation 1

Trap attenuation 2

Sharpness

characteristics 1

Sharpness

characteristics 2

Sharpness

characteristics 3

RGB output

frequency response 1

RGB output

frequency response 2

DC transmission

rate 1

DC transmission

rate 2

Auto pedestal

operation 1

Auto pedestal

operation 2

Y system items

No. Item Symbol

Measurement

Measurement

Measurement method

conditions pin

Min. Typ. Max. Unit

— 2.5 — V

2.2 2.7 3.2 dB

–3.8 –3.3 –2.8 dB

— –30 –20 dB

— –30 –20 dB

5.5 7.0 8.5 dB

1.5 2.5 4.5 dB

–7.5 –5.5 –3.0 dB

–6 –3.0 0 dB

–7 –4.2 –1 dB

96 99 100 %

73 78 85 %

280 340 400 mV

80 130 170 mV

VR

Gsc, max

Gsc, min

ATT

trap1

ATT

trap2

Gsh, max

Gsh, cen

Gsh, min

Gfreq1

Gfreq2

Gdt1

Gdt2

Vdp1

Vdp2

20log

Vsc1

VR

20log

Vsc2

VR

20log

Vtr2

Vtr1

20log

Vtr2

Vtr1

20log

Vs2

Vs1

20log

Vf2

Vf1

20log

Vf2

Vf1

Vdw-Vdb

Vdpp

Vdw-Vdb

Vdpp

Voff-Von

Voff-Von

19

19

19

19

19

21

23

19

21

23

19

19

19

Video In:

Sig-Y1

Video In:

Sig-Y2

fsc=

3.58 MHz

Video In:

Sig-Y2

fsc=

4.43 MHz

Video In:

Sig-Y4

Video In:

Sig-Y5

Video In:

Sig-Y4, Y6

Video In:

Sig-Y4, Y6

Video In:

Sig-Y3

Video In:

Sig-Y1

Video In:

Sig-H1

Video In:

Sig-Y3

Video In:

Sig-Y1

Video In:

Sig-H1

Video In:

Sig-H1

Video In:

Sig-Y10

VR

Vsc1

Vsc2

Vtr1

Vtr2

Vs1

(Sig-Y4)

Vs2

(Sig-Y5)

Vf1

(Sig-Y4)

Vf2

(Sig-Y6)

Vdpp

Vdw

Vdb

Vdpp

Vdw

Vdb

Voff

Von

Voff

Von

Vtr1

Vtr2

Vf1

(Sig-Y4)

Vf2

(Sig-Y6)

Loading...

Loading...