Page 1

SN8P2714X_2715

USER’S MANUAL

V1.4

SN8P2714X_2715

8-bit micro-controller build-in 12-bit ADC

SN8P2714

SN8P27142

SN8P27143

SN8P2715

S

O

Nii

S

O

SONIX reserves the right to make change without further notice to any products herein to improve reliability, function or design. SONIX does not

assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent

rights nor the rights of others. SONIX products are not designed, intended, or authorized for us as components in systems intended, for surgical

implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SONIX product

could create a situation where personal injury or death may occur. Should Buyer purchase or use SONIX products for any such unintended or

unauthorized application. Buyer shall indemnify and hold SONIX and its officers, employees, subsidiaries, affiliates and distributors harmless against

all claims, cost, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death

associated with such unintended or unauthorized use even if such claim alleges that SONIX was negligent regarding the design or manufacture of

the part.

N

X 88--

X

Biitt

B

Miiccrroo--

M

Coonnttrroolllleerr

C

SONiX TECHNOLOGY CO., LTD Page 1 V1.4

Page 2

AMENDMENT HISTORY

Version Date Description

VER 0.1 Aug. 2004 Preliminary Version first issue

VER 0.2 Jan. 2005 1. Add SN8P27142/ SN8P27143 relative data.

2. Fix ADC clock and Timer clock description.

3. Add LVD36 relative information.

4. Correct the LVD24 bit location from bit 3 to bit 4 in PFLAG register description.

5. Modify LVD code option related description

6. Modify TC0RATE and TC1RATE table.

7. Add TC0X8 and TC1X8 notice.

8. Release the ROM address 0x04 ~ 0x07 as general-purpose area.

9. Remove the instruction limitation at interrupt vector address (0x08)

10. Change IDE support version to M2IDE V1.04

11. Modify pin circuit diagram.

12. There is no Schmitt trigger input in port 4.

13. Add description of P0.3 without wakeup function

VER 0.3 Mar. 2005 1. Modify Zero flag description.

2. In instruction set table, change “S = 0”, otherwise “S = 1” to “S = 1”, otherwise “S =

0”

3. Fix ADC conversion time formula.

4. Remove “Note:For 12-bit resolution the conversion time is 16 steps”.

5. Remove “Note: Please use "@RST_WDT" macro to clear the watchdog timer

successfully both in S8KD-2 ICE emulation and real chip.”

6. Modify watchdog reset section

7. Fixed the slow mode current of electrical characteristic table.

VER 1.0

VER 1.1 Nov.2005

VER 1.2 Dec.2005

VER 1.3 Sep.2006

VER 1.4 Feb 2007

Sept 2005 1. Modify Programming Pin Mapping.

2. Modify PROGRAM CHECK LIST.

3. Modify P13 AVREF pin description

4. Modify 27142/143 pin assignment.

5. Modify P57,P66 TC0RATE、TC1RATE.

6. Modify P57,P66:TC0X8=1 Fosc/2~Fosc/256 to Fosc/1~Fosc/128

7. Modify P107 SLOW Mode Current.

8. ADD P97 “Note”.

Nov.2005 1. ADD Brown-Out reset circuit.

2. Working Voltage vs. Frequency graphs.

1. ADD ADC current.

2. Modify Topr value.

1. Remove 32k mode.

2. Modify P108 SN8P271XAXD to SN8P271XXD.

3. Modify P52 wakeup trigger signal.

4. Remove CHARACTERISTIC GRAPHS.

5. Modify reset section.

6. Limit Fcpu=Fosc/4~./8 when Noise Filter enable

7. Remove Pc

1. Modify 15.2 STANDARD ELECTRICAL CHARACTERISTIC.

2. Add 15.3 CHARACTERISTIC GRAPHS.

3. Add chapter17 Marking Definition.

1. Modify ELECTRICAL CHARACTERISTIC.

2. Modify RST/P0.3/VPP PIN DISCRIPTION.

SN8P2714X_2715

8-bit micro-controller build-in 12-bit ADC

SONiX TECHNOLOGY CO., LTD Page 2 V1.4

Page 3

SN8P2714X_2715

8-bit micro-controller build-in 12-bit ADC

Table of Contents

AMENDMENT HISTORY .............................................................................................................. 2

1 PRODUCT OVERVIEW................................................................................................................. 8

1.1 FEATURES OF SN8P2710 SERIES........................................................................................... 8

1.2 SYSTEM BLOCK DIAGRAM ................................................................................................. 10

1.3 PIN ASSIGNMENT................................................................................................................ 11

1.3.1 SN8P27142 Pin Assignment .......................................................................................... 11

1.3.2 SN8P27143 Pin Assignment .......................................................................................... 11

1.3.3 SN8P2714K Pin Assignment.......................................................................................... 12

1.3.4 SN8P2715P Pin Assignment.......................................................................................... 12

1.4 PIN DESCRIPTIONS............................................................................................................. 13

1.5 PIN CIRCUIT DIAGRAMS ..................................................................................................... 14

2 CODE OPTION TABLE............................................................................................................... 15

3 ADDRESS SPACES ................................................................................................................... 16

3.1 PROGRAM MEMORY (ROM) ............................................................................................... 16

3.1.1 OVERVIEW.................................................................................................................... 16

3.1.2 USER RESET VECTOR ADDRESS (0000H)................................................................. 17

3.1.3 INTERRUPT VECTOR ADDRESS (0008H)................................................................... 17

3.1.4 GENERAL PURPOSE PROGRAM MEMORY AREA..................................................... 19

3.1.5 LOOKUP TABLE DESCRIPTION................................................................................... 19

3.1.6 JUMP TABLE DESCRIPTION........................................................................................ 21

3.2 DATA MEMORY (RAM)......................................................................................................... 23

3.2.1 OVERVIEW.................................................................................................................... 23

3.3 WORKING REGISTERS ....................................................................................................... 24

3.3.1 Y, Z REGISTERS........................................................................................................... 24

3.3.2 R REGISTERS...............................................................................................................25

3.4 PROGRAM FLAG.................................................................................................................. 25

3.4.1 RESET FLAG................................................................................................................. 25

3.4.2 LVD 2.4V FLAG .............................................................................................................. 25

3.4.3 LVD 3.6V FLAG .............................................................................................................. 25

3.4.4 CARRY FLAG................................................................................................................. 26

3.4.5 DECIMAL CARRY FLAG................................................................................................ 26

3.4.6 ZERO FLAG................................................................................................................... 26

3.5 ACCUMULATOR................................................................................................................... 27

3.6 STACK OPERATIONS .......................................................................................................... 28

3.6.1 OVERVIEW.................................................................................................................... 28

SONiX TECHNOLOGY CO., LTD Page 3 V1.4

Page 4

SN8P2714X_2715

8-bit micro-controller build-in 12-bit ADC

3.6.2 STACK REGISTERS...................................................................................................... 29

3.6.3 STACK OPERATION EXAMPLE.................................................................................... 30

3.7 PROGRAM COUNTER ......................................................................................................... 31

3.7.1 ONE ADDRESS SKIPPING ........................................................................................... 32

3.7.2 MULTI-ADDRESS JUMPING......................................................................................... 33

4 ADDRESSING MODE................................................................................................................. 34

4.1 OVERVIEW........................................................................................................................... 34

4.1.1 IMMEDIATE ADDRESSING MODE............................................................................... 34

4.1.2 DIRECTLY ADDRESSING MODE ................................................................................. 34

4.1.3 INDIRECTLY ADDRESSING MODE.............................................................................. 34

4.1.4 TO ACCESS DATA in RAM BANK 0.............................................................................. 35

5 SYSTEM REGISTER................................................................................................................... 36

5.1 OVERVIEW........................................................................................................................... 36

5.2 SYSTEM REGISTER ARRANGEMENT (BANK 0) ................................................................ 36

5.2.1 BYTES of SYSTEM REGISTER..................................................................................... 36

5.2.2 BITS of SYSTEM REGISTER ........................................................................................ 37

6 RESET......................................................................................................................................... 39

6.1 OVERVIEW........................................................................................................................... 39

6.2 POWER ON RESET.............................................................................................................. 40

6.3 WATCHDOG RESET ............................................................................................................ 40

6.4 BROWN OUT RESET ........................................................................................................... 41

6.4.1 BROWN OUT DESCRIPTION........................................................................................ 41

6.4.2 THE SYSTEM OPERATING VOLTAGE DECSRIPTION............................................... 42

6.4.3 BROWN OUT RESET IMPROVEMENT......................................................................... 42

6.5 EXTERNAL RESET............................................................................................................... 44

6.6 EXTERNAL RESET CIRCUIT ............................................................................................... 44

6.6.1 Simply RC Reset Circuit................................................................................................. 44

6.6.2 Diode & RC Reset Circuit............................................................................................... 45

6.6.3 Zener Diode Reset Circuit.............................................................................................. 45

6.6.4 Voltage Bias Reset Circuit.............................................................................................. 46

6.6.5 External Reset IC ........................................................................................................... 47

7 OSCILLATORS........................................................................................................................... 48

7.1 OVERVIEW........................................................................................................................... 48

7.1.1 OSCM REGISTER DESCRIPTION................................................................................ 49

7.1.2 EXTERNAL HIGH-SPEED OSCILLATOR...................................................................... 49

7.1.3 HIGH CLOCK OSCILLATOR CODE OPTION ............................................................... 49

7.1.4 SYSTEM OSCILLATOR CIRCUITS............................................................................... 50

SONiX TECHNOLOGY CO., LTD Page 4 V1.4

Page 5

SN8P2714X_2715

8-bit micro-controller build-in 12-bit ADC

7.1.5 External RC Oscillator Frequency Measurement............................................................ 51

7.2 INTERNAL LOW-SPEED OSCILLATOR............................................................................... 52

7.3 SYSTEM MODE DESCRIPTION........................................................................................... 53

7.3.1 OVERVIEW.................................................................................................................... 53

7.3.2 NORMAL MODE ............................................................................................................ 53

7.3.3 SLOW MODE.................................................................................................................53

7.3.4 POWER DOWN (SLEEP) MODE................................................................................... 53

7.4 SYSTEM MODE CONTROL.................................................................................................. 54

7.4.1 SN8P2710 SYSTEM MODE BLOCK DIAGRAM............................................................ 54

7.4.2 SYSTEM MODE SWITCHING ....................................................................................... 55

7.5 WAKEUP TIME ..................................................................................................................... 56

7.5.1 OVERVIEW.................................................................................................................... 56

7.5.2 HARDWARE WAKEUP.................................................................................................. 56

8 TIMERS COUNTERS.................................................................................................................. 57

8.1 WATCHDOG TIMER (WDT).................................................................................................. 57

8.2 TIMER COUNTER 0 (TC0).................................................................................................... 58

8.2.1 OVERVIEW.................................................................................................................... 58

8.2.2 TC0M MODE REGISTER............................................................................................... 59

8.2.3 TC0C COUNTING REGISTER....................................................................................... 61

8.2.4 TC0R AUTO-LOAD REGISTER..................................................................................... 63

8.2.5 TC0 TIMER COUNTER OPERATION SEQUENCE....................................................... 64

8.2.6 TC0 CLOCK FREQUENCY OUTPUT (BUZZER)........................................................... 66

8.3 TIMER COUNTER 1 (TC1).................................................................................................... 67

8.3.1 OVERVIEW.................................................................................................................... 67

8.3.2 TC1M MODE REGISTER............................................................................................... 68

8.3.3 TC1C COUNTING REGISTER....................................................................................... 70

8.3.4 TC1R AUTO-LOAD REGISTER..................................................................................... 72

8.3.5 TC1 TIMER COUNTER OPERATION SEQUENCE....................................................... 73

8.3.6 TC1 CLOCK FREQUENCY OUTPUT (BUZZER)........................................................... 75

8.4 PWM FUNCTION DESCRIPTION......................................................................................... 76

8.4.1 OVERVIEW.................................................................................................................... 76

8.4.2 PWM PROGRAM DESCRIPTION.................................................................................. 77

8.4.3 PWM Duty with TCxR changing ..................................................................................... 78

8.4.4 TCxIRQ and PWM Duty ................................................................................................. 79

9 INTERRUPT ................................................................................................................................ 80

9.1 OVERVIEW........................................................................................................................... 80

9.2 INTEN INTERRUPT ENABLE REGISTER ............................................................................ 80

9.3 INTRQ INTERRUPT REQUEST REGISTER......................................................................... 81

SONiX TECHNOLOGY CO., LTD Page 5 V1.4

Page 6

SN8P2714X_2715

8-bit micro-controller build-in 12-bit ADC

9.4 P0.0 INTERRUPT TRIGGER EDGE CONTROL REGISTER ................................................ 81

9.5 INTERRUPT OPERATION DESCRIPTION........................................................................... 82

9.5.1 GIE GLOBAL INTERRUPT OPERATION ...................................................................... 82

9.5.2 INT0 (P0.0) INTERRUPT OPERATION ......................................................................... 83

9.5.3 INT1 (P0.1) INTERRUPT OPERATION ......................................................................... 83

9.5.4 TC0 INTERRUPT OPERATION..................................................................................... 85

9.5.5 TC1 INTERRUPT OPERATION..................................................................................... 86

9.5.6 MULTI-INTERRUPT OPERATION................................................................................. 87

10 I/O PORT................................................................................................................................... 89

10.1 OVERVIEW......................................................................................................................... 89

10.2 I/O PORT FUNCTION TABLE ............................................................................................. 90

10.3 PULL-UP RESISTERS ........................................................................................................ 91

10.4 I/O PORT DATA REGISTER ............................................................................................... 94

11 8-CHANNEL ANALOG TO DIGITAL CONVERTER................................................................. 96

11.1 OVERVIEW......................................................................................................................... 96

11.2 ADM REGISTER ................................................................................................................. 97

11.3 ADR REGISTERS ............................................................................................................... 97

11.4 ADB REGISTERS ............................................................................................................... 97

11.5 P4CON REGISTERS .......................................................................................................... 98

11.6 ADC CONVERTING TIME................................................................................................... 99

11.7 ADC CIRCUIT ................................................................................................................... 100

12 7-BIT DIGITAL TO ANALOG CONVERTER .......................................................................... 101

12.1 OVERVIEW....................................................................................................................... 101

12.2 DAM REGISTER ............................................................................................................... 102

12.3 D/A CONVERTER OPERATION ....................................................................................... 102

13 CODING ISSUE ...................................................................................................................... 103

13.1 TEMPLATE CODE ............................................................................................................ 103

13.2 PROGRAM CHECK LIST .................................................................................................. 107

14 INSTRUCTION SET TABLE ................................................................................................... 108

15 ELECTRICAL CHARACTERISTIC ......................................................................................... 109

15.1 ABSOLUTE MAXIMUM RATING....................................................................................... 109

15.2 STANDARD ELECTRICAL CHARACTERISTIC................................................................ 109

15.3 CHARACTERISTIC GRAPHS........................................................................................... 110

16 DEVELOPMENT TOOLS ........................................................................................................ 114

16.1 DEVELOPMENT TOOL VERSION ............................................................................................. 114

SONiX TECHNOLOGY CO., LTD Page 6 V1.4

Page 7

SN8P2714X_2715

8-bit micro-controller build-in 12-bit ADC

16.1.1 ICE (In circuit emulation)............................................................................................ 114

16.1.2 OTP Writer ................................................................................................................. 114

16.1.3 IDE (Integrated Development Environment)............................................................... 114

16.2 SN8P2715/SN8P2714 EV-KIT .......................................................................................... 115

16.2.1 PCB DESCRIPTION................................................................................................... 115

16.3 SN8P2715/14 EV-KIT CONNNECT TO SN8ICE 2K .......................................................... 116

16.4 TRANSITION BOARD FOR OTP PROGTRAMMING........................................................ 117

16.4.1 SN8P2715/2715 Rev. B TRANSITION BOARD......................................................... 117

16.4.2 CONNNECT Rev. B TRANSITION BOARD TO EASY WRITER................................ 117

16.5 OTP PROGRAMMING PIN TO TRANSITION BOARD MAPPING..................................................... 118

16.5.1 The pin assignment of Easy and MP EZ Writer transition board socket:.................... 118

16.5.2 The pin assignment of Writer V3.0 transition board socket: ....................................... 118

16.5.3 SN8P2710 Series Programming Pin Mapping:........................................................... 119

17 MARKING DEFINITION .......................................................................................................... 120

17.1 INTRODUCTION............................................................................................................... 120

17.2 MARKING INDETIFICATION SYSTEM............................................................................. 120

17.3 MARKING EXAMPLE........................................................................................................ 121

17.4 DATECODE SYSTEM....................................................................................................... 121

18 PACKAGE INFORMATION .................................................................................................... 122

18.1 P-DIP18 PIN...................................................................................................................... 122

18.2 SOP18 PIN........................................................................................................................ 123

18.3 P-DIP 20 PIN ..................................................................................................................... 124

18.4 SOP 20 PIN ....................................................................................................................... 125

18.5 SSOP20 PIN ..................................................................................................................... 126

18.6 SK-DIP28 PIN ................................................................................................................... 127

18.7 SOP28 PIN........................................................................................................................ 128

18.8 P-DIP 32 PIN ..................................................................................................................... 129

18.9 SOP 32 PIN ....................................................................................................................... 129

SONiX TECHNOLOGY CO., LTD Page 7 V1.4

Page 8

SN8P2714X_2715

8-bit micro-controller build-in 12-bit ADC

1 PRODUCT OVERVIEW

1.1 FEATURES of SN8P2710 Series

Memory configuration

♦

OTP ROM size: 2K * 16 bits. Two internal interrupts: TC0, TC1

RAM size: 128 * 8 bits Two external interrupts: INT0, INT1

Eight levels stack buffer

I/O pin configuration

♦

Input only pin: P0

Bi-directional: P2, P4, P5

Wakeup: P0.0, P0.1, P0.2

External interrupt: P0.0, P0.1

Pull-up resisters: P0, P2, P4, P5 External high clock: RC type up to 10 MHz

P4 pins shared with ADC inputs. External high clock: Crystal type up to 16 MHz

Max 8-channel 12-bit ADC.

♦

One channel 7-bit DAC.

♦

Powerful instructions

♦

One clocks per instruction cycle (1T)

Most of instructions are one cycle only

All ROM area lookup table function (MOVC) SN8P27142: P-DIP 18 pins, SOP 18pins

SN8P27143:P-DIP 20 pins, SOP 20 pins, SSOP 20 pins

SN8P2714: SK-DIP 28 pins, SOP 28pins

SN8P2715: P-DIP 32 pins, SOP 32 pins

Four interrupt sources

♦

Two 8-bit Timer/Counter

♦

TC0: Auto-reload timer/Counter/PWM0/Buzzer output

TC1: Auto-reload timer/Counter/PWM1/Buzzer output

On chip watchdog timer.

♦

System clocks and Operating modes

♦

Internal low clock: RC type 16KHz(3V), 32KHz(5V)

Normal mode: Both high and low clock active

Slow mode: Low clock only

Sleep mode: Both high and low clock stop

Package (Chip form support)

♦

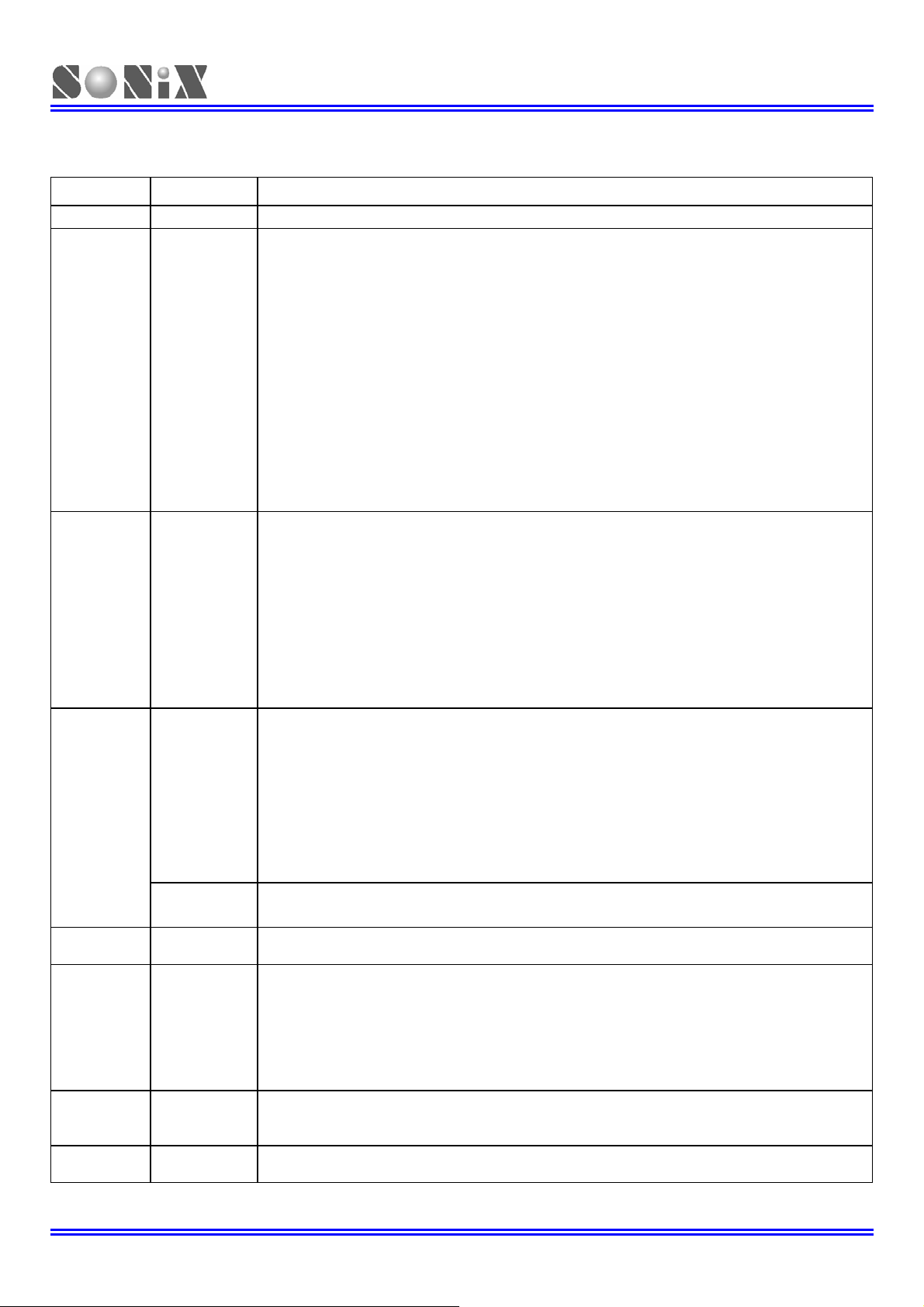

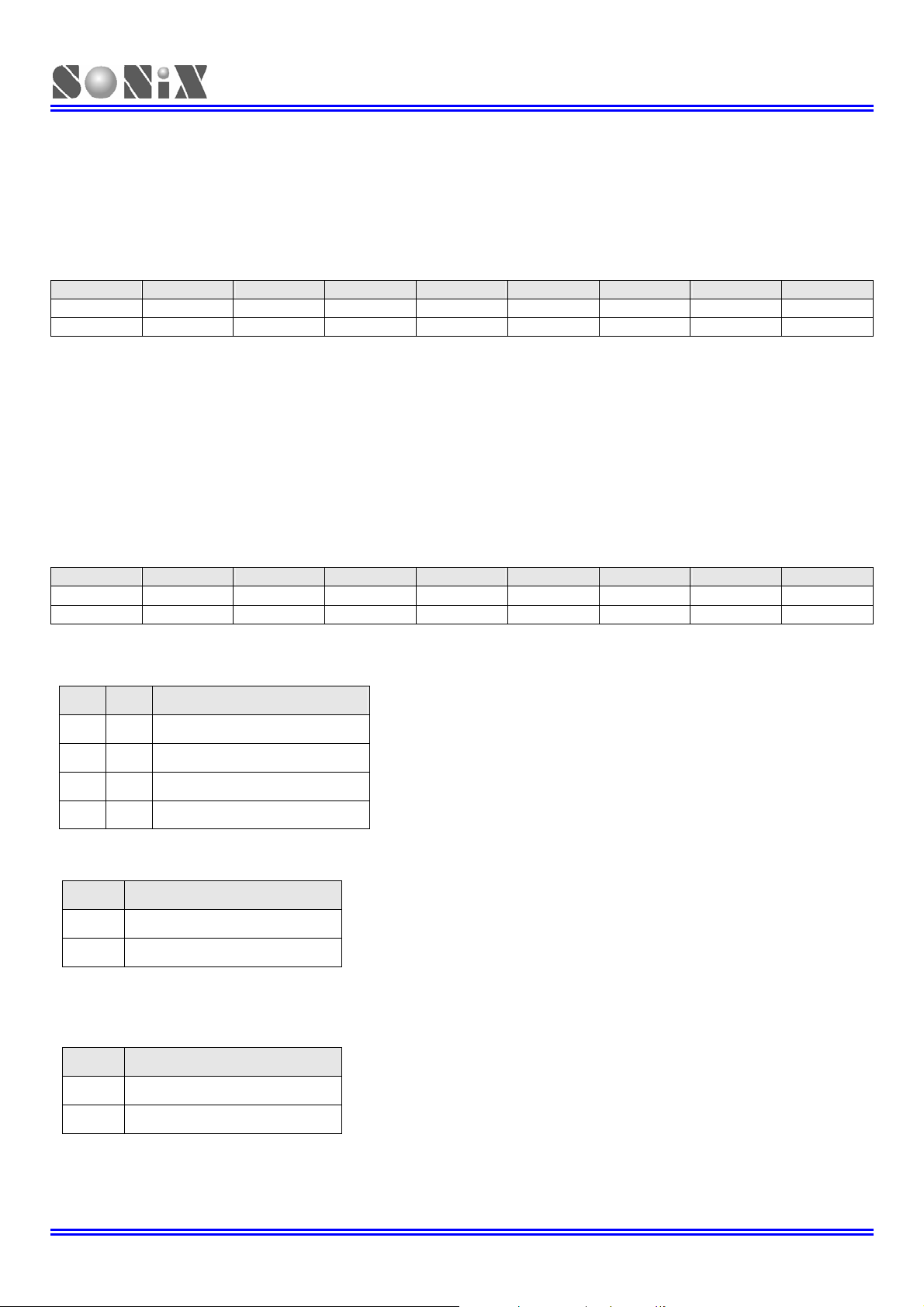

FEATURES SELECTION TABLE

CHIP ROM RAM Stack

SN8P27142 2K*16 128 8 - V V 15 5ch - 2 - 2 DIP18/SOP18

SN8P27143 2K*16 128 8 - V V 16 6ch - 2 - 2 DIP20/SOP20/SSOP20

SN8P2714 2K*16 128 8 - V V 23 8ch 1ch 2 - 3 SKDIP28/SOP28

SN8P2715 2K*16 128 8 - V V 27 8ch 1ch 2 - 3 DIP32/SOP32

SN8P2704A 4K*16 256 8 V V V 18 5ch 1ch 2 1 8 SKDIP28/SOP28

SN8P2705A 4K*16 256 8 V V V 23 8ch 1ch 2 1 9 DIP32/SOP32

Note: For SN8P27143 and SN8P27142 must configure P02R (bit 2 of P0UR) as “1” to avoid sleep mode fail.

Timer PWM

I/O ADC DAC

T0 TC0 TC1

Buzzer

SIO

Wakeup

Pin no.

Package

SONiX TECHNOLOGY CO., LTD Page 8 V1.4

Page 9

SN8P2714X_2715

8-bit micro-controller build-in 12-bit ADC

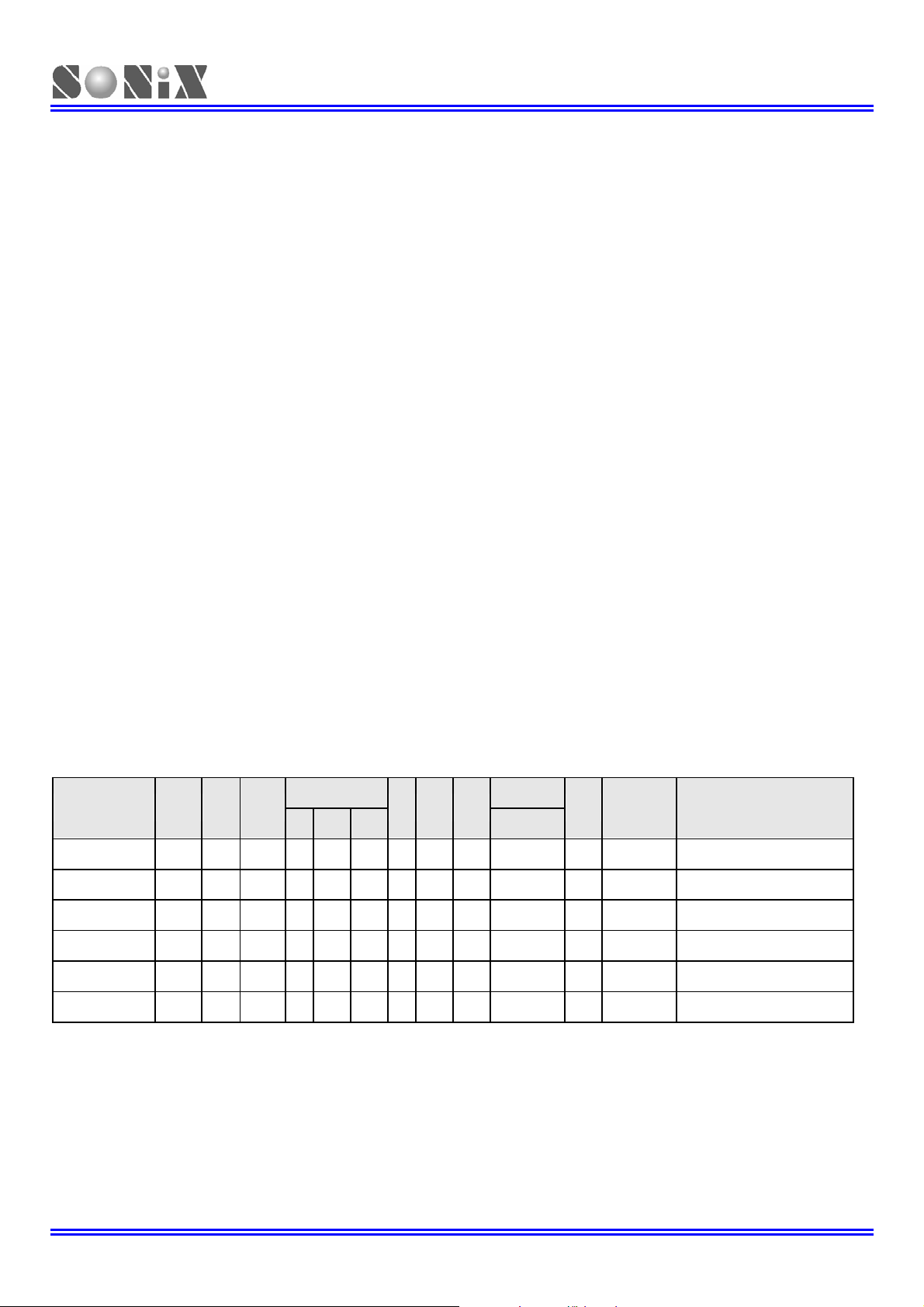

Compare SN8P2714/15 to SN8P2704A/05A

Item SN8P2714/15 SN8P2704A/05A

Excellent

AC Noise Immunity Capability

Memory

Maximum I/O pins

High Speed PWM

Programmable Open-Drain Output N/A P1.0 / P1.1 / P5.2 (SO)

B0MOV M, I No Limitation “I” can’t be 0E6h or 0E7h

B0XCH A, M No Limitation

Valid instruction in ROM address 8 No Limitation JMP or NOP

ADC Interrupt No Yes

ADC Clock Frequency

Valid Range of

TC0C/TC1C/TC0R/TC1R

Green mode No Yes

SIO Function No Yes

LVD Level: 2.0V always ON 1.8V always ON

Port 0 Input only port Bi-direction port

Interrupt Vector Instruction No Limitation NOP/JMP only

PUSH/POP Instruction No Yes

(Add an 47uF bypass Capacitor

between VDD and GND)

ROM: 2K x 16

RAM: 128 x 8

23 I/O in 28 pins package

27 I/O in 32 pins package

PWM Resolution: 8bit/6bit/5bit/4bit

8bit PWM up to 62.5K at 16Mhz

4bit PWM up to 1000K at 16Mhz

Four kinds of setting

(Configuration by ADCKS [1:0])

0x00 ~ 0xFF 0x00 ~ 0xFE

(Add an 47uF bypass Capacitor

between VDD and GND)

18 I/O in 28 pins package

23 I/O in 32 pins package

PWM Resolution: 8bit/6bit/5bit/4bit

8bit PWM up to 7.8125K at 16Mhz

4bit PWM up to 125K at 16Mhz

(Configuration by ADCKS [2:0])

Excellent

ROM: 4K x 16

RAM: 256 x 8

The address of M

can’t be 80h ~ FFh

Seven kinds of setting

SONiX TECHNOLOGY CO., LTD Page 9 V1.4

Page 10

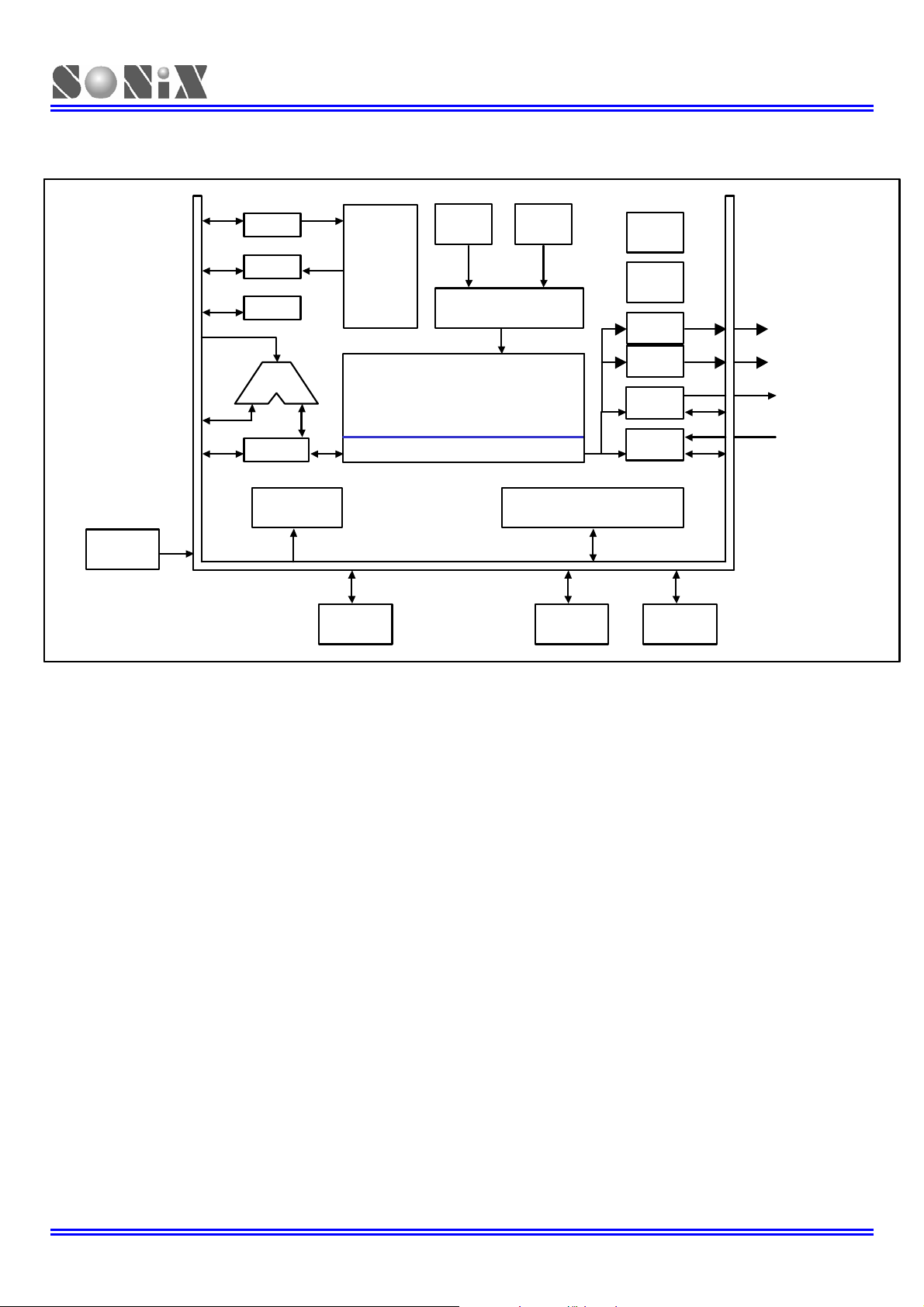

1.2 SYSTEM BLOCK DIAGRAM

H-OSC

PC

PC

IR

IR

FLAGS

FLAGS

ALU

ALU

ACC

ACC

INT ERRUPT

INT ERRUPT

CONTROL

CONTROL

OTP

OTP

ROM

ROM

SYSTEM REGISTER

SYSTEM REGISTER

H-OSC

TIMING GENERATOR

TIMING GENERATOR

RAM

RAM

8-bit micro-controller build-in 12-bit ADC

Internal

Internal

CLK

CLK

TIMER & COUNTER

TIMER & COUNTER

Lo w Vo l t

Lo w Vo l t

Detector

Detector

Watch-Dog

Watch-Dog

Timer

Timer

PWM0

PWM0

PWM1

PWM1

DAC

DAC

ADC

ADC

SN8P2714X_2715

PWM0/Buzz er0

PWM0/Buzz er0

PWM1/Buzz er1

PWM1/Buzz er1

DAO

DAO

AIN0~AIN7

AIN0~AIN7

PORT 0

PORT 0

PORT 2 PORT 4 PORT 5

PORT 2 PORT 4 PORT 5

Figure 1-1.Simplified System Block Diagram

SONiX TECHNOLOGY CO., LTD Page 10 V1.4

Page 11

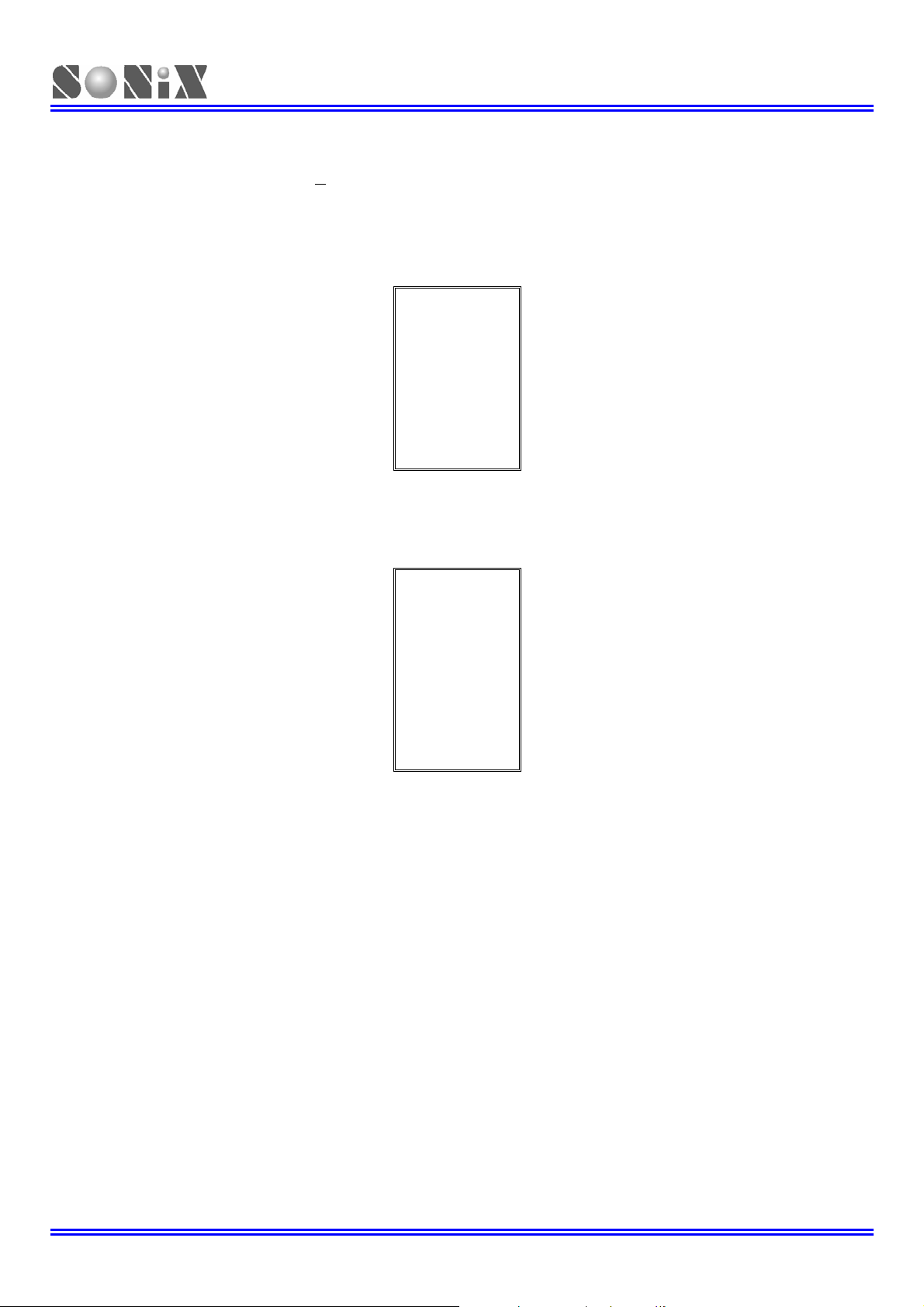

1.3 PIN ASSIGNMENT

Format Description:SN8P271xY Y = K > SK-DIP,P > P-DIP, S> SOP

1.3.1 SN8P27142 Pin Assignment

P0.1 1 U 18 P0.0

P5.6/XOUT

SN8P27142P

SN8P27142S

P2.0

P2.1

XIN

VSS

P4.4/AIN4

P4.3/AIN3

P4.2/AIN2

1.3.2 SN8P27143 Pin Assignment

P2.0 1 U 20 P0.1

P5.6/XOUT

SN8P27143P

SN8P27143S

SN8P27143X

P2.1

XIN

VSS

P4.5/AIN5

P4.4/AIN4

P4.3/AIN3

P4.2/AIN2

P4.1/AIN1

2 17

3 16

4 15

5 14

6 13

7 12

8 11

9 10

2 19

3 18

4 17

5 16

6 15

7 14

8 13

9 12

10 11

P5.0

P5.1

P5.3/BZ1/PWM1

P5.4/BZ0/PWM0

P0.3/RST/VPP

VDD

P4.0/AIN0

P4.1/AIN1

P0.0

P5.0

P5.1

P5.3/BZ1/PWM1

P5.4/BZ0/PWM0

P0.3/RST/VPP

VDD

AVREFH

P4.0/AIN0

SN8P2714X_2715

8-bit micro-controller build-in 12-bit ADC

¾ Note: For SN8P27143 and SN8P27142 must configure P02R (bit 2 of P0UR) as “1” to avoid sleep mode

fail.

¾ Note: The ADC reference voltage (AVREFH) of SN8P27142/SN8P27143 is VDD.

SONiX TECHNOLOGY CO., LTD Page 11 V1.4

Page 12

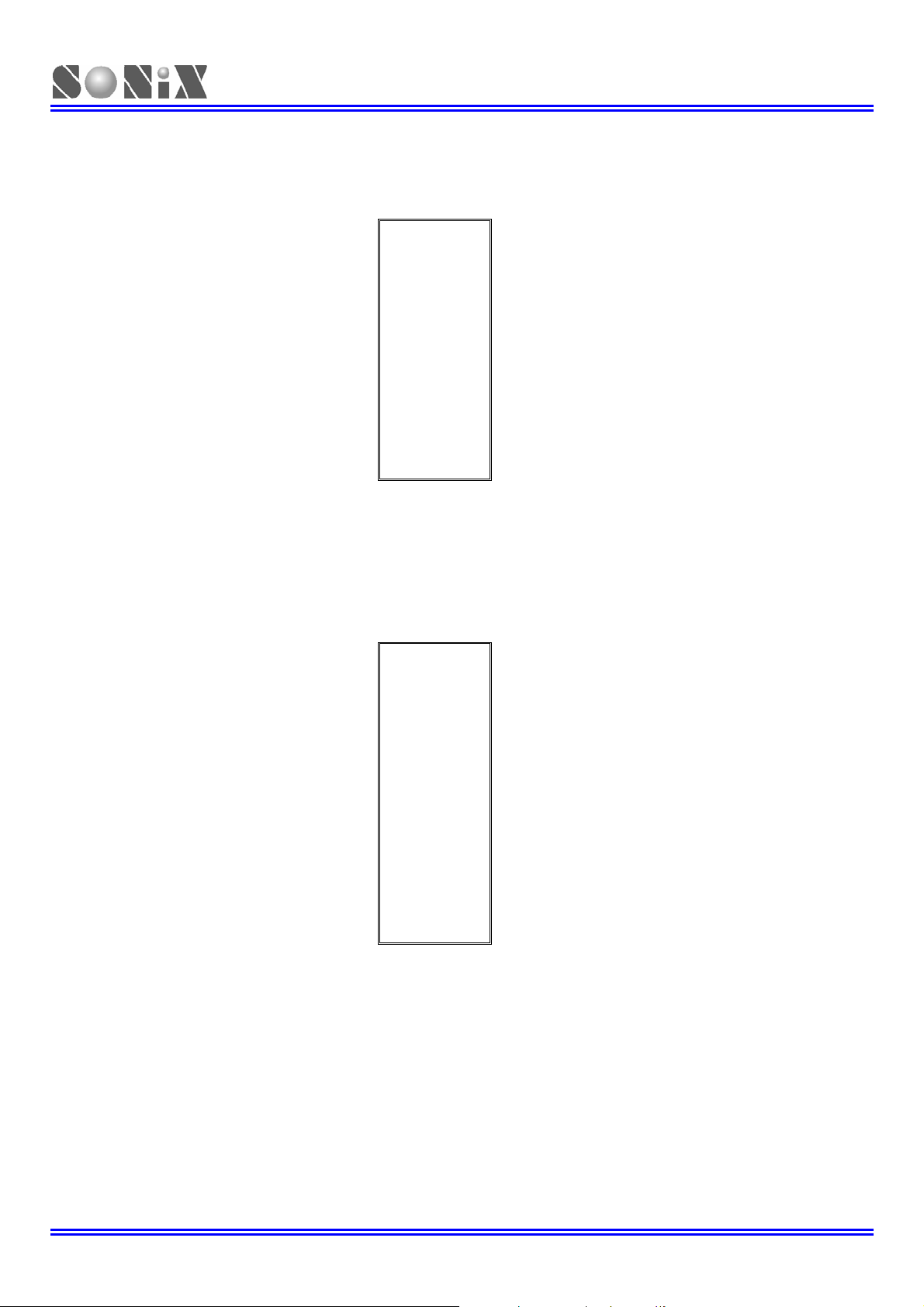

1.3.3 SN8P2714K Pin Assignment

P5.3/BZ1/PWM1 1 U 28

P5.2 2 27 DAC

P5.1 3 26 P0.3/RST/VPP

P5.0 4 25 VDD

P0.0/INT0 5 24 AVREFH

P0.1/INT1 6 23

P0.2 7 22

P2.0 8 21

P2.1 9 20

P2.2 10 19

P2.3 11 18

P2.4 12 17

P5.6/XOUT 13 16

XIN 14 15

SN8P2714K

SN8P2714S

1.3.4 SN8P2715P Pin Assignment

SN8P2714X_2715

8-bit micro-controller build-in 12-bit ADC

P5.4/BZ0/PWM0

P4.0/AIN0

P4.1/AIN1

P4.2/AIN2

P4.3/AIN3

P4.4/AIN4

P4.5/AIN5

P4.6/AIN6

P4.7/AIN7

VSS

P5.5 1 U 32 DAO

P5.4/BZ0/PWM0 2 31 P0.3/RST/VPP

P5.3/BZ1/PWM1

P0.0/INT0

P0.1/INT1

3 30 VDD

P5.2

4 29 AVREFH

P5.1

5 28 P4.0/AIN0

P5.0

6 27 P4.1/AIN1

7 26 P4.2/AIN2

8 25 P4.3/AIN3

P0.2 9 24 P4.4/AIN4

P2.0

10 23 P4.5/AIN5

P2.1

11 22 P4.6/AIN6

P2.2

12 21 P4.7/AIN7

P2.3

13 20 VSS

P2.4

14 19 XIN

P2.5

15 18 P5.6/XOUT

P2.6 16 17 P2.7

SN8P2715P

SN8P2715S

SONiX TECHNOLOGY CO., LTD Page 12 V1.4

Page 13

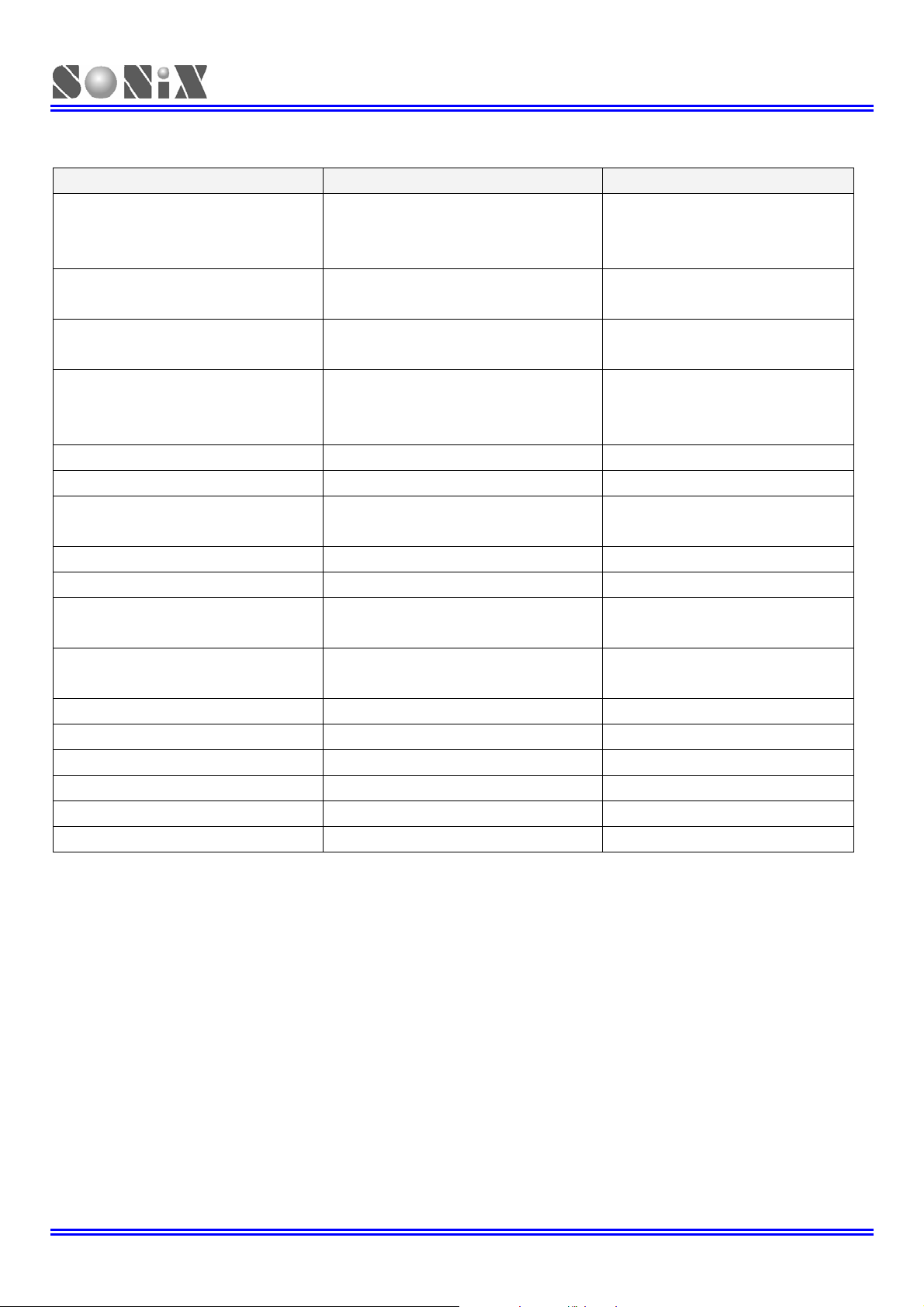

8-bit micro-controller build-in 12-bit ADC

1.4 PIN DESCRIPTIONS

PIN NAME TYPE DESCRIPTION

P0 [1:0] / INT [1:0] I P0 [1:0]: Input only pin/ wakeup/pull-up/Schmitt trigger input

INT [1:0]: External interrupt

P0 .2 I P0.2: Input only pin/wake up/pull-up/Schmitt trigger input

P2 [7:0] I/O P2 [7:0] bi-direction pins/pull-up/Schmitt trigger input

P4 [7:0] / AIN [7:0] I/O Bi-direction pins/pull-up /ADC input/ without Schmitt trigger input

P5 [5:0] I/O Bi-direction pins/pull-up/Schmitt trigger input

P5.4: PWM0/BZ0, P5.3: PWM1/BZ1

AVREFH I ADC highest reference voltage input

(NOTE :The ADC reference voltage (AVREFH) of SN8P27142 and SN8P27143 are

VDD.)

DAO O Current type DAC output

SN8P2714X_2715

P0.3/RST/VPP I/P P0.3: Schmitt trigger input pin / NO pull-up, NO wakeup/ in RC mode

P0.3 is input only pin without pull-up resistor under P0.3 mode. Add the 100 ohm

external resistor on P0.3, when it is set to be input pin.

RST: External reset, active “low”

VPP: OTP programming pin

XIN I External oscillator input pin. / External RC oscillator input

XOUT/P5.6 I/O XOUT: External oscillator output pin.

P5.6: Bi-direction pin/pull-up/Schmitt trigger input in RC mode

VDD, VSS P Power supply pins.

Table 1-1. SN8P2714/15 Pin Description

SONiX TECHNOLOGY CO., LTD Page 13 V1.4

Page 14

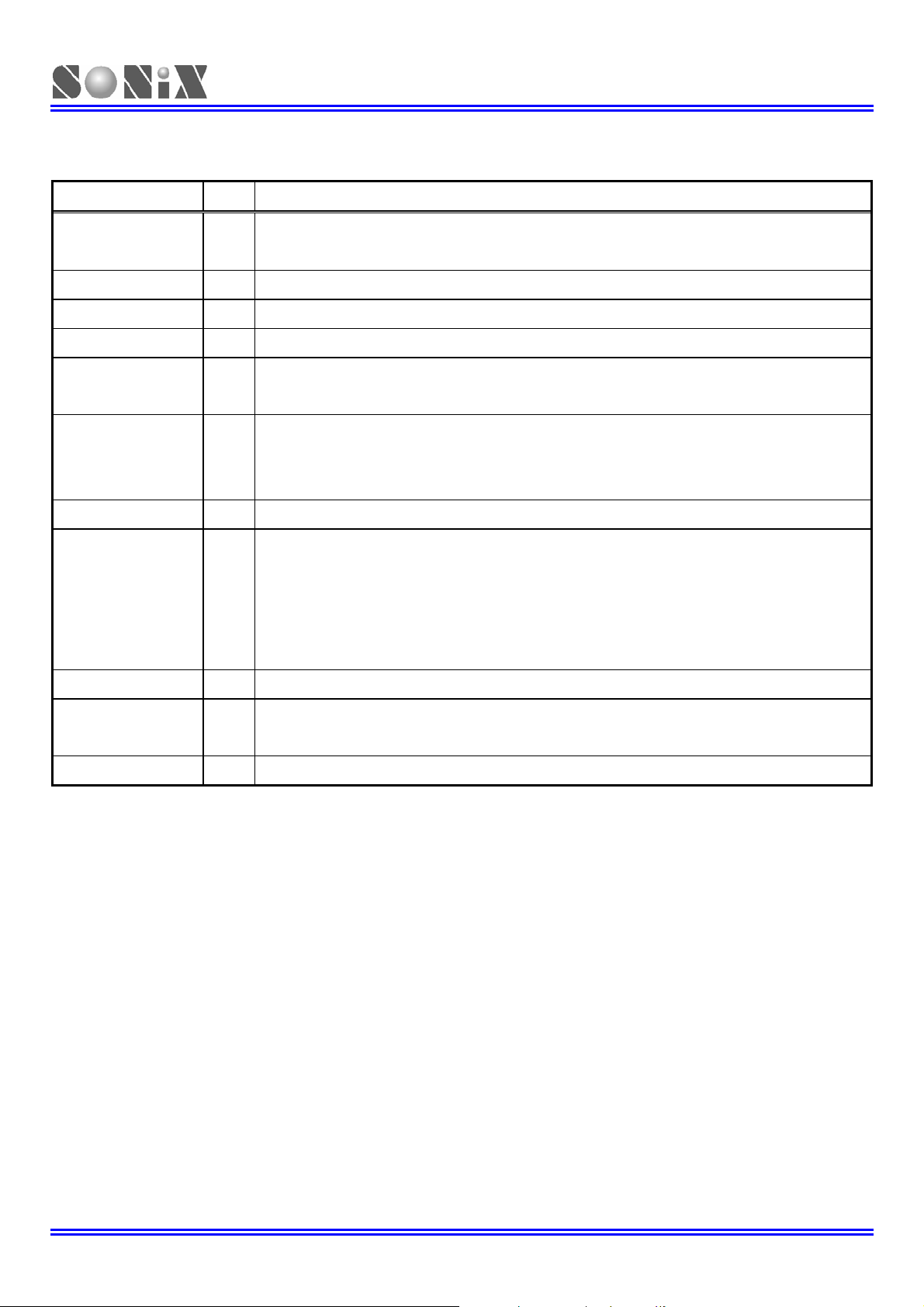

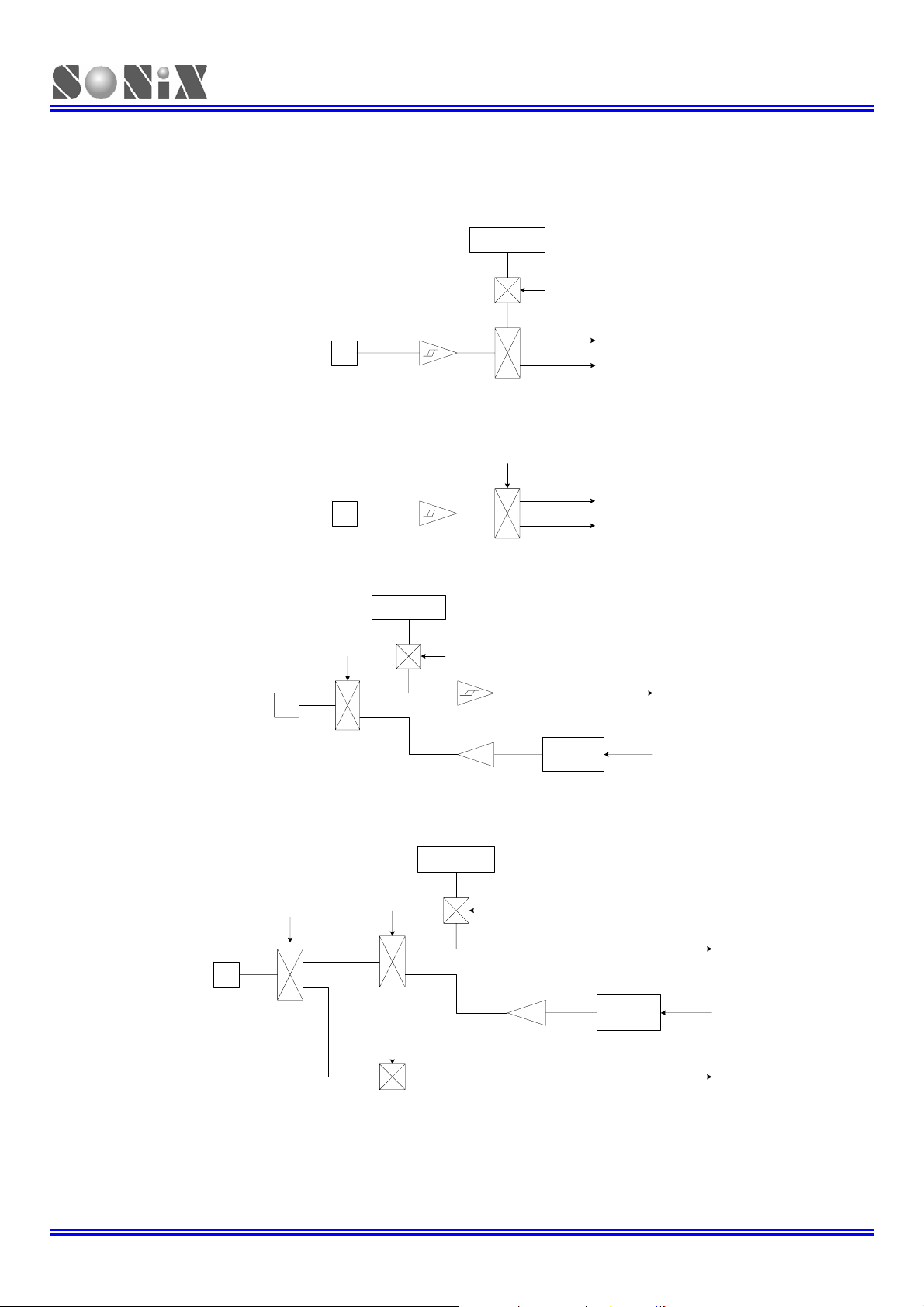

1.5 PIN CIRCUIT DIAGRAMS

Port 0.1 and P0.2 structure:

SN8P2714X_2715

8-bit micro-controller build-in 12-bit ADC

Pull-Up

PnUR

Port 0.3 structure:

Port 2, 5 structure:

Port 4 structure:

Pin

Pin

Pin

PnM

Pull-Up

Code Option

PnM, PnUR

Pull-Up

Ext. Reset

Output

Latch

Int. Bus

Int. Rst

Int. Bus

Int. Rst

Input Bus

Output Bus

P4CON

Pin

PnM

GCHS

PnM, PnUR

Output

Latch

Input Bus

Output Bus

Int. ADC

Figure 1-2. Pin Circuit Diagram

SONiX TECHNOLOGY CO., LTD Page 14 V1.4

Page 15

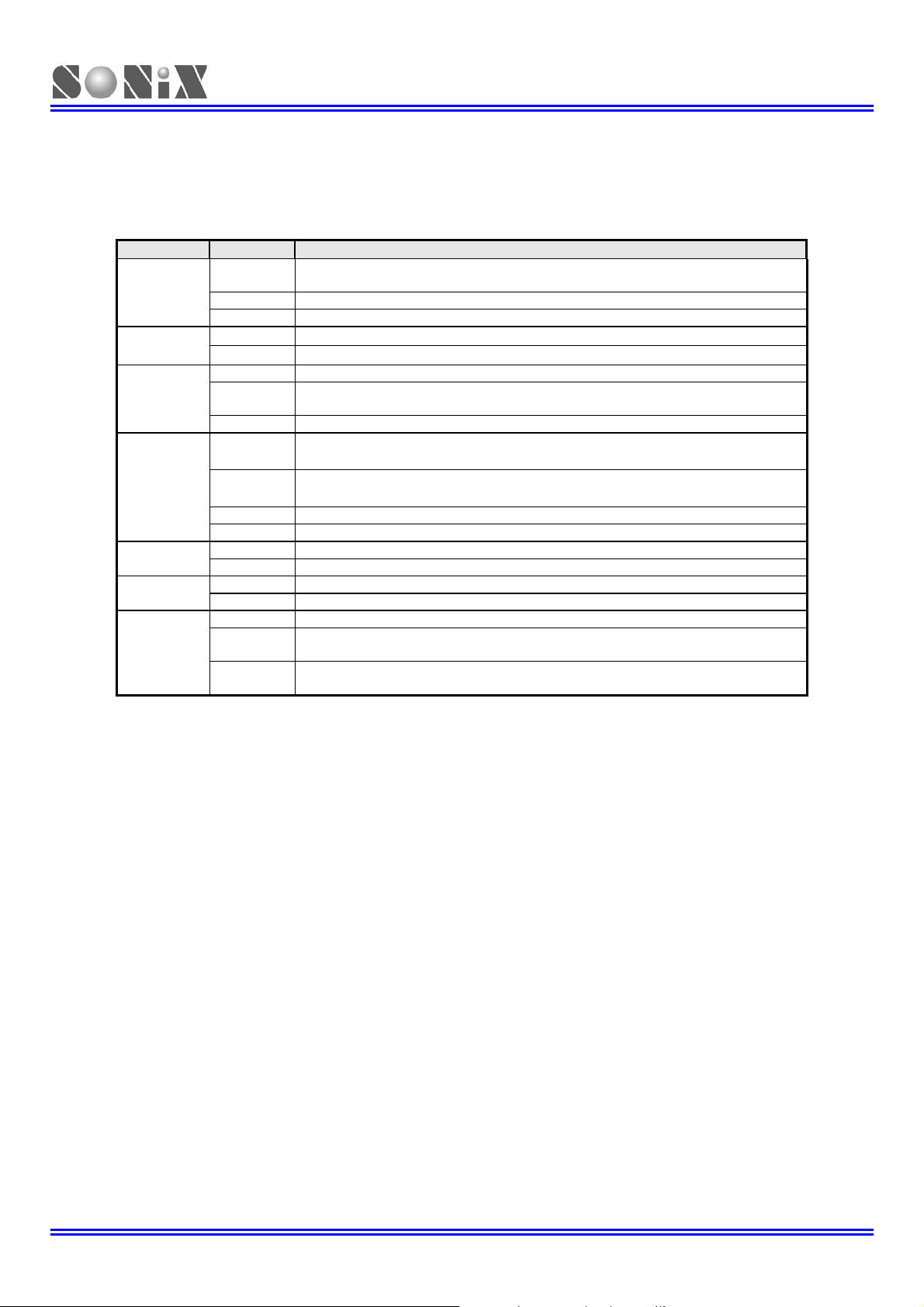

2 CODE OPTION TABLE

Code Option Content Function Description

Low cost external RC oscillator for high clock oscillator.

Output the Fcpu clock from Xout pin.

Enable Noise Filter and the Fcpu is Fosc/4~Fosc/8.

Disable Noise Filter and the Fcpu is Fosc/1~Fosc/8.

Normal mode: Enable Watchdog timer

Sleep mode: Stop Watchdog timer Stop

Instruction cycle is oscillator clock.

Notice: In Fosc/1, Noise Filter must be disabled.

Instruction cycle is 2 oscillator clocks.

Notice: In Fosc/2, Noise Filter must be disabled.

LVD will reset chip if VDD is below 2.0V

Enable LVD24 bit of PFLAG register for 2.4V low voltage indicator.

LVD will reset chip if VDD is below 2.4V

Enable LVD36 bit of PFLAG register for 3.6V low voltage indicator.

High_Clk

Noise_Filter

Watch_Dog

Fcpu

Security

RST_P0.3

LVD

Ext_RC

12M_X’tal High speed crystal /resonator (e.g. 12MHz ~ 16MHz) for high clock oscillator.

4M_X’tal Middle speed crystal /resonator (e.g. 4MHz ~ 10Mhz) for high clock oscillator.

Enable

Disable

Always_On Watchdog timer always on even in sleep (power down) mode.

Enable

Disable Disable Watchdog function.

Fosc/1

Fosc/2

Fosc/4 Instruction cycle is 4 oscillator clocks.

Fosc/8 Instruction cycle is 8 oscillator clocks.

Enable Enable ROM code Security function.

Disable Disable ROM code Security function.

Reset Enable external reset pin

P0.3 Enable P0.3 input only pin without pull-up register

LVD_L LVD will reset chip if VDD is below 2.0V

LVD_M

LVD_H

SN8P2714X_2715

8-bit micro-controller build-in 12-bit ADC

Table 2-1. Code Option Table of SN8P2714x/2715

Notice:

¾ In high noisy environment, enable “Noise Filter” and set Watch_Dog as “Always_On” is

strongly recommended.

¾ Enable “Noise Filter” will limit the Fcpu = Fosc/4 or Fosc/8

¾ Fcpu code option is only available for High Clock

¾ Fosc = Fhosc (External high clock) in normal mode.

¾ Fosc = Flosc (Internal low RC clock) in slow mode.

¾ In slow mode, Fcpu = Fosc / 4.

SONiX TECHNOLOGY CO., LTD Page 15 V1.4

Page 16

SN8P2714X_2715

8-bit micro-controller build-in 12-bit ADC

3 ADDRESS SPACES

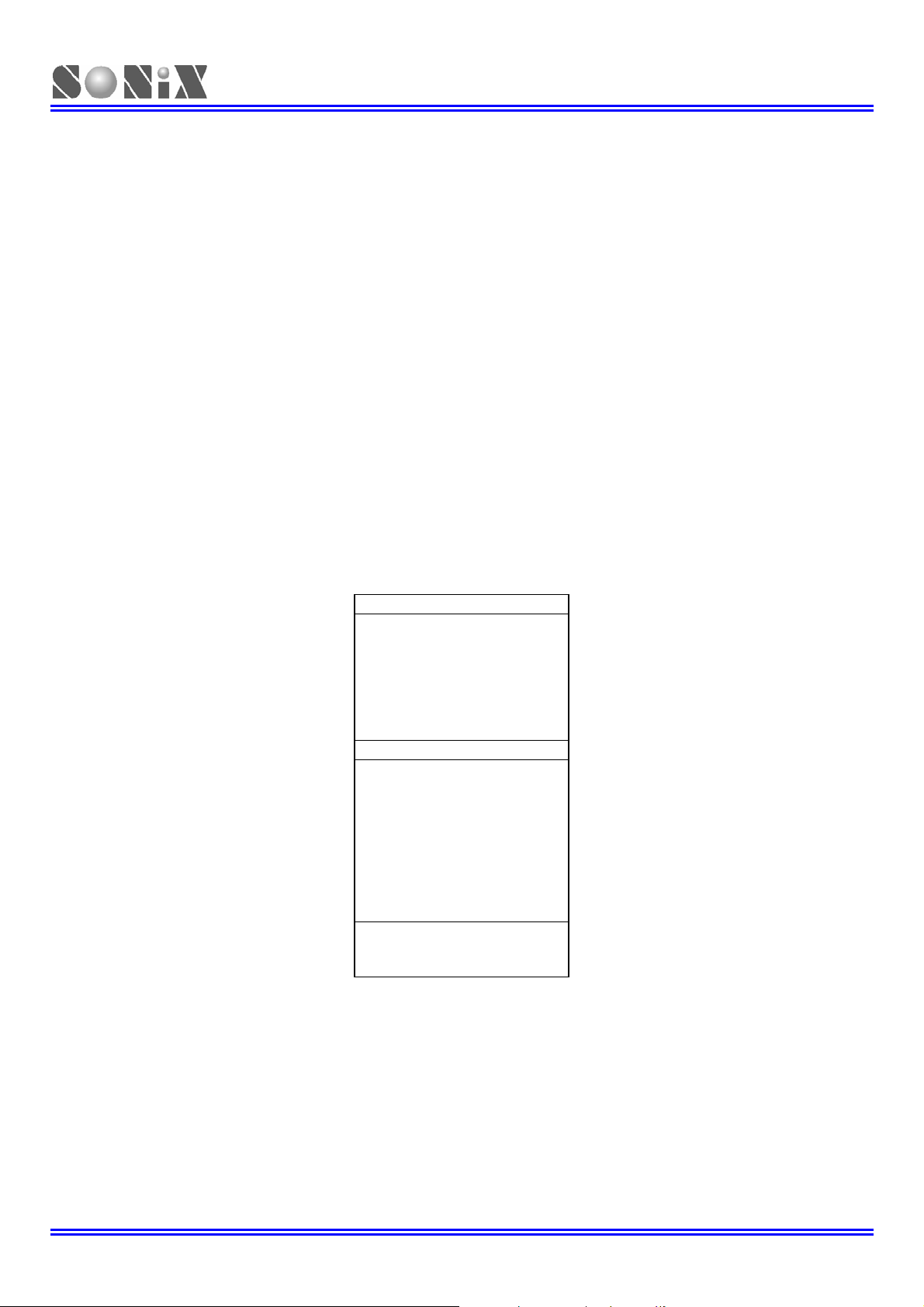

3.1 PROGRAM MEMORY (ROM)

3.1.1 OVERVIEW

ROM Maps for SN8P2710 devices provide 2K X 16-bit OTP programmable memory. The SN8P2710 program memory

is able to fetch instructions through 12-bit wide PC (Program Counter) and can look up ROM data by using ROM code

registers (R, X, Y, Z). In standard configuration, the device’s 2,048 x 16-bit program memory has four areas:

¾ 1-word reset vector addresses

¾ 1-word Interrupt vector addresses

¾ 4-words reserved area

¾ 2K words

All of the program memory is partitioned into three coding areas. The 1

vector area), the 2

nd

area is for the interrupt vector (0008H) and the 3ed area is user code area from 0009H to 07FBH.

st

area is located from 00H to 07H(The Reset

0000H

0001H Jump to user start address

0002H Jump to user start address

0003H Jump to user start address

0004H Jump to user start address

0005H Jump to user start address

0006H Jump to user start address

0007H

0008H

0009H User program

000FH

0010H

0011H

07FBH

07FCH

07FFH

Figure 3-1 ROM Address Structure

General purpose area

.

.

General purpose area

.

.

.

ROM

Reset vector

Interrupt vector

Code Option

User reset vector

Jump to user start address

User interrupt vector

End of user program

SONiX TECHNOLOGY CO., LTD Page 16 V1.4

Page 17

SN8P2714X_2715

8-bit micro-controller build-in 12-bit ADC

3.1.2 USER RESET VECTOR ADDRESS (0000H)

A 1-word vector address area is used to execute system reset. After power on reset or watchdog timer overflow reset,

then the chip will restart the program from address 0000h and all system registers will be set as default values. The

following example shows the way to define the reset vector in the program memory.

Example: After power on reset, external reset active or reset by watchdog timer overflow.

ORG 0 ; 0000H

JMP START ; Jump to user program address.

. ;

ORG 10H

START: ; 0010H, The head of user program.

. ; User program

.

.

.

ENDP

; End of program

3.1.3 INTERRUPT VECTOR ADDRESS (0008H)

A 1-word vector address area is used to execute interrupt request. If any interrupt service is executed, the program

counter (PC) value is stored in stack buffer and points to 0008h of program memory to execute the vectored interrupt.

Users have to define the interrupt vector and the following example shows the way to define the interrupt vector in the

program memory.

Example 1: This demo program includes interrupt service routine and the user program is behind the

interrupt service routine.

ORG 0 ; 0000H

JMP START ; Jump to user program address.

.

START: ; The head of user program.

ORG 8

B0XCH A, ACCBUF

B0MOV A, PFLAG

B0MOV PFLAGBUF, A

.

.

B0MOV A, PFLAGBUF

B0MOV PFLAG, A

B0XCH A, ACCBUF

RETI

.

.

.

JMP START

ENDP

; Interrupt service routine

; B0XCH doesn’t change C, Z flag

; Save PFLAG register in a buffer

; User code

; User code

; Restore PFLAG register from buffer

; End of interrupt service routine

; User program

; End of user program

; End of program

SONiX TECHNOLOGY CO., LTD Page 17 V1.4

Page 18

SN8P2714X_2715

8-bit micro-controller build-in 12-bit ADC

Example 2: The demo program includes interrupt service routine and the address of interrupt service

routine is in a special address of general-purpose area.

ORG 0 ; 0000H

JMP START ; Jump to user program address.

. ; 0001H ~ 0007H are reserved

ORG 08

JMP MY_IRQ ; 0008H, Jump to interrupt service routine address

ORG 10H

START: ; 0010H, The head of user program.

. ; User program

.

.

.

MY_IRQ: ;The head of interrupt service routine

¾ Note: It is easy to get the rules of SONIX program from demo programs given above. These points are as

following.

1.The address 0000H is a “JMP” instruction to make the program go to general-purpose ROM area.

2. The interrupt service starts from 0008H. Users can put the whole interrupt service routine from 0008H

(Example1) or to put a “JMP” instruction in 0008H then place the interrupt service routine in other

general-purpose ROM area (Example2) to get more modularized coding style.

JMP START

B0XCH A, ACCBUF

B0MOV A, PFLAG

B0MOV PFLAGBUF, A

.

.

B0MOV A, PFLAGBUF

B0MOV PFLAG, A

RETI

ENDP

; End of user program

; B0XCH doesn’t change C, Z flag

; Save PFLAG register in a buffer

; User code

; User code

; Restore PFLAG register from buffer

; End of interrupt service routine

; End of program

SONiX TECHNOLOGY CO., LTD Page 18 V1.4

Page 19

SN8P2714X_2715

8-bit micro-controller build-in 12-bit ADC

3.1.4 GENERAL PURPOSE PROGRAM MEMORY AREA

The ROM locations 0001H~0007H and 0009H~07FBH are used as general-purpose memory. The area is stored

instruction’s op-code and look-up table data. The SN8P2710 includes jump table function by using program counter

(PC) and look-up table function by using ROM code registers (R, Y, Z).

The boundary of program memory is separated by the high-byte program counter (PCH) every 100H. In jump table

function and look-up table function, the program counter can’t leap over the boundary by program counter

automatically. Users need to modify the PCH value to “PCH+1” as the PCL overflow (from 0FFH to 000H).

3.1.5 LOOKUP TABLE DESCRIPTION

In the ROM’s data lookup function, Y register to the highest 8-bit and Z register to the lowest 8-bit data of ROM

address. After MOVC instruction is executed, the low-byte data of ROM then will be stored in ACC and high-byte data

stored in R register.

Example: To look up the ROM data located “TABLE1”.

B0MOV Y, #TABLE1$M ; To set lookup table1’s middle address

B0MOV Z, #TABLE1$L ; To set lookup table1’s low address.

MOVC ; To lookup data, R = 00H, ACC = 35H

;

;

@@:

. . ;

TABLE1: DW 0035H ; To define a word (16 bits) data.

DW 5105H ; “

DW 2012H ; “

¾ CAUSION: The Y register can’t increase automatically if Z register cross boundary from 0xFF to 0x00.

Therefore, user must take care such situation to avoid loop-up table errors. If Z register overflow, Y

register must be added one. The following INC_YZ macro shows a simple method to process Y and Z

registers automatically.

¾ Note: Because the program counter (PC) is only 12-bit, the X register is useless in the application. Users

can omit “B0MOV X, #TABLE1$H”. SONiX ICE support more larger program memory addressing

capability. So make sure X register is “0” to avoid unpredicted error in loop-up table operation.

INCMS Z ; Z+1

JMP @F ; Not overflow

INCMS Y ; Z overflow (FFH Æ 00), Æ Y=Y+1

NOP ; Not overflow

MOVC ; To lookup data, R = 51H, ACC = 05H.

; Increment the index address for next address

Example: INC_YZ Macro

INC_YZ MACRO

INCMS Z ; Z+1

JMP @F ; Not overflow

INCMS Y ; Y+1

NOP ; Not overflow

@@:

ENDM

SONiX TECHNOLOGY CO., LTD Page 19 V1.4

Page 20

SN8P2714X_2715

8-bit micro-controller build-in 12-bit ADC

The other coding style of loop-up table is to add Y or Z index register by accumulator. Be careful if carry happen. Refer

following example for detailed information:

Example: Increase Y and Z register by B0ADD/ADD instruction

B0MOV Y, #TABLE1$M ; To set lookup table’s middle address.

B0MOV Z, #TABLE1$L ; To set lookup table’s low address.

GETDATA: ;

MOVC ; To lookup data. If BUF = 0, data is 0x0035

; If BUF = 1, data is 0x5105

; If BUF = 2, data is 0x2012

.

.

. . ;

TABLE1: DW 0035H ; To define a word (16 bits) data.

DW 5105H ; “

DW 2012H ; “

B0MOV A, BUF ; Z = Z + BUF.

B0ADD Z, A

B0BTS1 FC ; Check the carry flag.

JMP GETDATA ; FC = 0

INCMS Y ; FC = 1. Y+1.

NOP

SONiX TECHNOLOGY CO., LTD Page 20 V1.4

Page 21

SN8P2714X_2715

8-bit micro-controller build-in 12-bit ADC

3.1.6 JUMP TABLE DESCRIPTION

The jump table operation is one of multi-address jumping function. Add low-byte program counter (PCL) and ACC

value to get one new PCL. The new program counter (PC) points to a series jump instructions as a listing table. The

way is easy to make a multi-stage program.

When carry flag occurs after executing of “ADD PCL, A”, it will not affect PCH register. Users have to check if the jump

table leaps over the ROM page boundary or the listing file generated by SONIX assembly software. If the jump table

leaps over the ROM page boundary (e.g. from xxFFH to xx00H), move the jump table to the top of next program

memory page (xx00H). Here one page mean 256 words.

Example : If PC = 0323H (PCH = 03H、PCL = 23H)

ORG 0X0100 ; The jump table is from the head of the ROM boundary

B0ADD PCL, A ; PCL = PCL + ACC, the PCH can’t be changed.

JMP A0POINT ; ACC = 0, jump to A0POINT

JMP A1POINT ; ACC = 1, jump to A1POINT

JMP A2POINT ; ACC = 2, jump to A2POINT

JMP A3POINT ; ACC = 3, jump to A3POINT

In following example, the jump table starts at 0x00FD. When execute B0ADD PCL, A. If ACC = 0 or 1, the jump

table points to the right address. If the ACC is larger then 1 will cause error because PCH doesn’t increase one

automatically. We can see the PCL = 0 when ACC = 2 but the PCH still keep in 0. The program counter (PC) will

point to a wrong address 0x0000 and crash system operation. It is important to check whether the jump table

crosses over the boundary (xxFFH to xx00H). A good coding style is to put the jump table at the start of ROM

boundary (e.g. 0100H).

Example: If “jump table” crosses over ROM boundary will cause errors.

ROM Address

. .

. .

. .

0X00FD

0X00FE

0X00FF

0X0100

0X0101

. .

. .

SONIX provides a macro for safe jump table function. This macro will check the ROM boundary and move the jump

table to the right position automatically. The side effect of this macro is maybe wasting some ROM size. Notice the

maximum jmp table number for this macro is limited under 254.

@JMP_A MACRO VAL

IF (($+1) !& 0XFF00) !!= (($+(VAL)) !& 0XFF00)

JMP ($ | 0XFF)

ORG ($ | 0XFF)

ENDIF

ADD PCL, A

ENDM

¾ Note: “VAL” is the number of the jump table listing number.

B0ADD PCL, A ; PCL = PCL + ACC, the PCH can’t be changed.

JMP A0POINT ; ACC = 0

JMP A1POINT ; ACC = 1

JMP A2POINT

JMP A3POINT ; ACC = 3

; ACC = 2 Å jump table cross boundary here

SONiX TECHNOLOGY CO., LTD Page 21 V1.4

Page 22

SN8P2714X_2715

8-bit micro-controller build-in 12-bit ADC

Example: “@JMP_A” application in SONIX macro file called “MACRO3.H”.

B0MOV A, BUF0 ; “BUF0” is from 0 to 4.

@JMP_A 5 ; The number of the jump table listing is five.

JMP A0POINT ; If ACC = 0, jump to A0POINT

JMP A1POINT ; ACC = 1, jump to A1POINT

JMP A2POINT ; ACC = 2, jump to A2POINT

JMP A3POINT ; ACC = 3, jump to A3POINT

JMP A4POINT ; ACC = 4, jump to A4POINT

If the jump table position is from 00FDH to 0101H, the “@JMP_A” macro will make the jump table to start from 0100h.

SONiX TECHNOLOGY CO., LTD Page 22 V1.4

Page 23

SN8P2714X_2715

8-bit micro-controller build-in 12-bit ADC

3.2 DATA MEMORY (RAM)

3.2.1 OVERVIEW

The SN8P2710 has internally built-in the data memory up to 128 bytes for storing the general-purpose data.

For SN8P2710

¾ 128 * 8-bit general purpose area in bank 0

¾ 128 * 8-bit system special register area

The memory is located in bank 0. The bank 0, using the first 128-byte location assigned as general-purpose area, and

the remaining 128-byte in bank 0 as system register.

BANK 0

000h 000h~07Fh of Bank 0 = To store general-

“ purpose data (128 bytes).

“

“

“

“

07Fh

080h 080h~0FFh of Bank 0 = To store system

“ registers (128 bytes).

“

“

“

“

0FFh

RAM location

General purpose area

System register

End of bank 0 area

Figure 3-2 RAM Location of SN8P2710

¾ Note: The undefined locations of system register area are logic “high” after executing read instruction

“MOV A, M”.

SONiX TECHNOLOGY CO., LTD Page 23 V1.4

Page 24

SN8P2714X_2715

8-bit micro-controller build-in 12-bit ADC

3.3 WORKING REGISTERS

The locations 82H to 84H of RAM bank 0 in data memory stores the specially defined registers such as register R, Y, Z,

respectively shown in the following table. These registers can use as the general purpose of working buffer and be

used to access ROM’s and RAM’s data. For instance, all of the ROM’s table can be looked-up with R, Y and Z

registers. The data of RAM memory can be indirectly accessed with Y and Z registers.

80H 81H 82H 83H 84H 85H

RAM

- - R/W R/W R/W -

3.3.1 Y, Z REGISTERS

The Y and Z registers are the 8-bit buffers. There are three major functions of these registers. First, Y and Z registers

can be used as working registers. Second, these two registers can be used as data pointers for @YZ register. Third,

the registers can be address ROM location in order to look-up ROM data.

Y initial value = XXXX XXXX

084H Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Y

R/W R/W R/W R/W R/W R/W R/W R/W

Z initial value = XXXX XXXX

083H Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Z

R/W R/W R/W R/W R/W R/W R/W R/W

The @YZ that is data point_1 index buffer located at address E7H in RAM bank 0. It employs Y and Z registers to

addressing RAM location in order to read/write data through ACC. The Lower 4-bit of Y register is pointed to RAM

bank number and Z register is pointed to RAM address number, respectively. The higher 4-bit data of Y register is

truncated in RAM indirectly access mode.

Example: If want to read a data from RAM address 25H of bank 0, it can use indirectly addressing mode to

B0MOV Y, #00H ; To set RAM bank 0 for Y register

B0MOV Z, #25H ; To set location 25H for Z register

B0MOV A, @YZ ; To read a data into ACC

Example: Clear general-purpose data memory area of bank 0 using @YZ register.

MOV A, #0

B0MOV Y, A ; Y = 0, bank 0

MOV A, #07FH

B0MOV Z, A ; Z = 7FH, the last address of the data memory area

CLR_YZ_BUF:

CLR @YZ ; Clear @YZ to be zero

DECMS Z ; Z – 1, if Z= 0, finish the routine

JMP CLR_YZ_BUF ; Not zero

CLR @YZ

END_CLR: ; End of clear general purpose data memory area of bank 0

.

Note: Please consult the “LOOK-UP TABLE DESCRIPTION” about Y, Z register look-up table application.

YBIT7 YBIT6 YBIT5 YBIT4 YBIT3 YBIT2 YBIT1 YBIT0

ZBIT7 ZBIT6 ZBIT5 ZBIT4 ZBIT3 ZBIT2 ZBIT1 ZBIT0

access data as following.

- - R Z Y -

SONiX TECHNOLOGY CO., LTD Page 24 V1.4

Page 25

SN8P2714X_2715

8-bit micro-controller build-in 12-bit ADC

3.3.2 R REGISTERS

There are two major functions of the R register. First, R register can be used as working registers. Second, the R

registers can be store high-byte data of look-up ROM data. After MOVC instruction executed, the high-byte data of a

ROM address will be stored in R register and the low-byte data stored in ACC.

R initial value = XXXX XXXX

082H Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

R

R/W R/W R/W R/W R/W R/W R/W R/W

¾ Note: Please consult the “LOOK-UP TABLE DESCRIPTION” about R register look-up table application.

RBIT7 RBIT6 RBIT5 RBIT4 RBIT3 RBIT2 RBIT1 RBIT0

3.4 PROGRAM FLAG

The PFLAG includes reset flag, low voltage detect flag, carry flag, decimal carry flag (DC) and zero flag (Z). If the result

of operating is zero or there is carry, borrow occurrence, then these flags will be set to PFLAG register.

PFLAG initial value = 00xx,x000

086H Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

PFLAG

R/W R/W R/W R/W - R/W R/W R/W

NT0 NPD LVD36 LVD24 - C DC Z

3.4.1 RESET FLAG

NT0 NPD Reset Status

0 0 Watch-dog time out

0 1 Reserved

1 0 Reset by LVD

1 1 Reset by external Reset Pin

3.4.2 LVD 2.4V FLAG

LVD24 VDD Status

1 VDD <= 2.4V

0 VDD > 2.4V

Note: This bit is only valid when code option LVD=LVD_M

3.4.3 LVD 3.6V FLAG

LVD36 VDD Status

1 VDD <= 3.6V

0 VDD > 3.6V

Note: This bit is only valid when code option LVD=LVD_H

SONiX TECHNOLOGY CO., LTD Page 25 V1.4

Page 26

SN8P2714X_2715

8-bit micro-controller build-in 12-bit ADC

3.4.4 CARRY FLAG

C = 1: If executed arithmetic addition with occurring carry signal or executed arithmetic subtraction without borrowing

signal or executed rotation instruction with shifting out logic “1”.

C = 0: If executed arithmetic addition without occurring carry signal or executed arithmetic subtraction with borrowing

signal or executed rotation instruction with shifting out logic “0”.

3.4.5 DECIMAL CARRY FLAG

DC = 1: If executed arithmetic addition with occurring carry signal from low nibble or executed arithmetic subtraction

without borrow signal from high nibble.

DC = 0: If executed arithmetic addition without occurring carry signal from low nibble or executed arithmetic subtraction

with borrow signal from high nibble.

3.4.6 ZERO FLAG

Z = 1: ACC or arithmetic operation result is zero after executing a instruction. Refer instruction set table for

detailed information.

Z = 0: ACC or arithmetic operation result is not zero after executing a instruction. Refer instruction set table

for detailed information.

SONiX TECHNOLOGY CO., LTD Page 26 V1.4

Page 27

SN8P2714X_2715

8-bit micro-controller build-in 12-bit ADC

3.5 ACCUMULATOR

The ACC is an 8-bits data register responsible for transferring or manipulating data between ALU and data memory. If

the result of operating is zero (Z) or there is carry (C or DC) occurrence, then these flags will be set to PFLAG register.

ACC is not in data memory (RAM), so ACC can’t be access by “B0MOV” instruction during the instant addressing

mode.

Example: Read and write ACC value.

; Read ACC data and store in BUF data memory

MOV BUF, A

. .

; Write a immediate data into ACC

MOV A, #0FH

. .

; Write ACC data from BUF data memory

MOV A, BUF

. .

The ACC value don’t store in any interrupt service executed. ACC must be exchanged to another data memory defined

by users. Thus, once interrupt occurs, these data must be stored in the data memory based on the user’s program as

follows.

Example: ACC and working registers protection.

ACCBUF EQU 00H ; ACCBUF is ACC data buffer in bank 0.

INT_SERVICE:

B0XCH A, ACCBUF

B0XCH A, ACCBUF ; Re-load ACC

RETI ; Exit interrupt service vector

¾ Notice: To save and re-load ACC data must be used “B0XCH” instruction, or the PLAGE value maybe

modified by ACC.

B0MOV A, PFLAG

B0MOV PFLAGBUF, A

.

.

B0MOV A, PFLAGBUF

B0MOV PFLAG, A

; B0XCH doesn’t change C, Z flag

; Save PFLAG register in a buffer

; Restore PFLAG register from buffer

SONiX TECHNOLOGY CO., LTD Page 27 V1.4

Page 28

SN8P2714X_2715

8-bit micro-controller build-in 12-bit ADC

3.6 STACK OPERATIONS

3.6.1 OVERVIEW

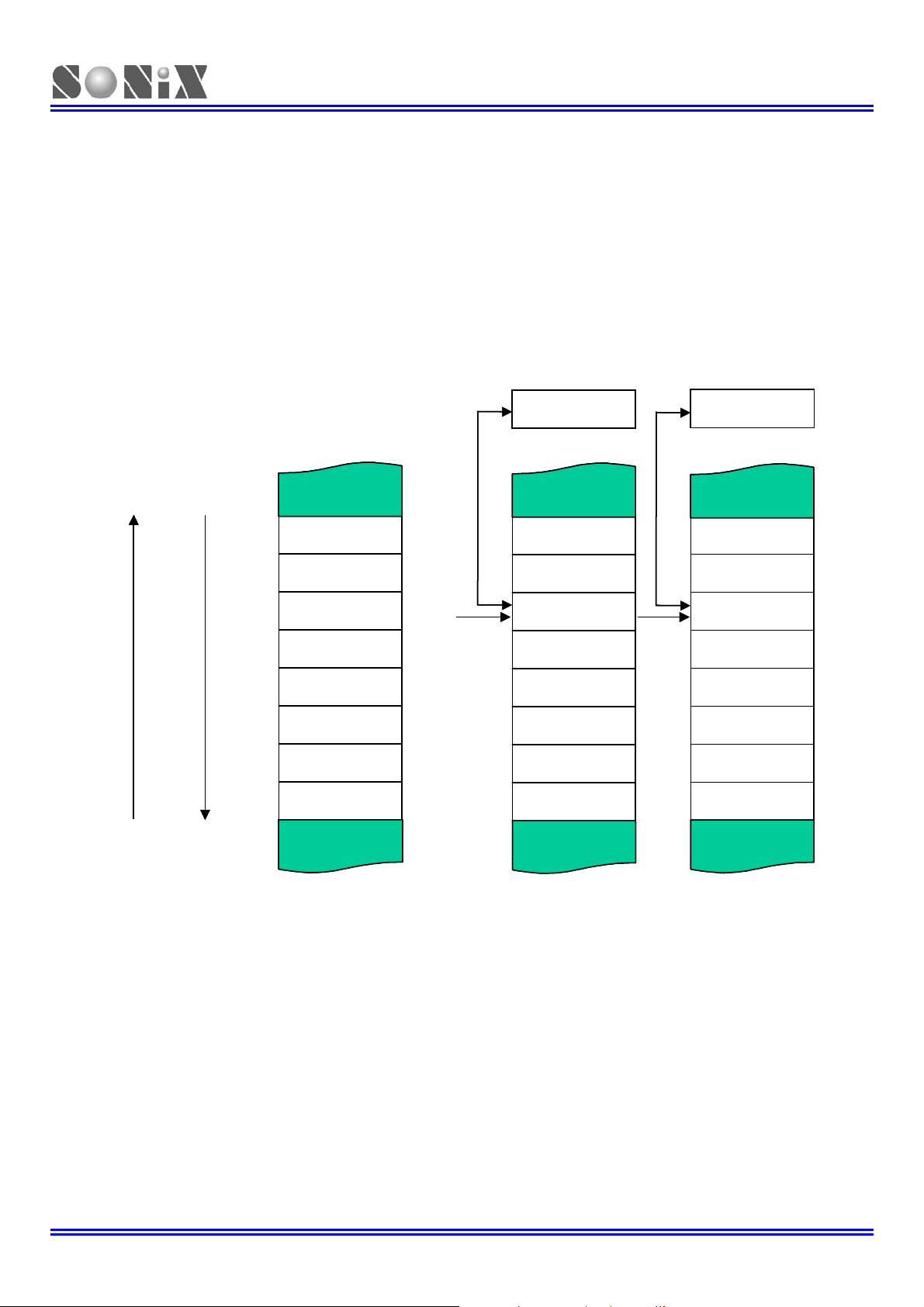

The stack buffer of SN8P2710 has 8-level high area and each level is 11-bits length. This buffer is designed to save

and restore program counter’s (PC) data when interrupt service is executed. The STKP register is a pointer designed

to point active level in order to save or restore data from stack buffer for kernel circuit. The STKnH and STKnL are the

12-bit stack buffers to store program counter (PC) data.

STACK BUFFER

STACK BUFFER

PCL

PCL

PCLPCL

STK0L

STK0L

STK0L

RET /

RET /

RETI

RETI

CALL /

CALL /

interrupt

interrupt

STKP = 7

STKP = 7

STKP = 7

PCH

PCH

PCHPCH

STK0H

STK0H

STK0H

STKP + 1

STKP + 1

STKP + 1

STKP - 1

STKP - 1

STKP - 1STKP - 1

STKP = 6

STKP = 6

STKP = 6

STKP = 5

STKP = 5

STKP = 5

STKP = 4

STKP = 4

STKP = 4

STKP = 3

STKP = 3

STKP = 3

STKP = 2

STKP = 2

STKP = 2

STKP = 1

STKP = 1

STKP = 1

STKP = 0

STKP = 0

STKP = 0

STKP

STKPSTKP

Figure 3-3 Stack Operation

STK1H

STK1H

STK1H

STK2H

STK2H

STK2H

STK3H

STK3H

STK3H

STK4H

STK4H

STK4H

STK5H

STK5H

STK5H

STK6H

STK6H

STK6H

STK7H

STK7H

STK7H

STKP

STKPSTKP

STK1L

STK1L

STK1L

STK2L

STK2L

STK2L

STK3L

STK3L

STK3L

STK4L

STK4L

STK4L

STK5L

STK5L

STK5L

STK6L

STK6L

STK6L

STK7L

STK7L

STK7L

SONiX TECHNOLOGY CO., LTD Page 28 V1.4

Page 29

SN8P2714X_2715

8-bit micro-controller build-in 12-bit ADC

3.6.2 STACK REGISTERS

The stack pointer (STKP) is a 4-bit register to store the address used to access the stack buffer, 11-bits data memory

(STKnH and STKnL) set aside for temporary storage of stack addresses.

The two stack operations are writing to the top of the stack (Stack-Save) and reading (Stack-Restore) from the top of

stack. Stack-Save operation decrements the STKP and the Stack-Resotre operation increments one time. That makes

the STKP always points to the top address of stack buffer and writes the last program counter value (PC) into the stack

buffer.

The program counter (PC) value is stored in the stack buffer before a CALL instruction executed or during interrupt

service routine. Stack operation is a LIFO type (Last in and first out). The stack pointer (STKP) and stack buffer

(STKnH and STKnL) are located in the system register area bank 0.

STKP (stack pointer) initial value = 0xxx x111

0DFH Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

STKP

R/W - - - - R/W R/W R/W

STKPBn: Stack pointer. (n = 0 ~ 3)

GIE: Global interrupt control bit. 0 = disable, 1 = enable. More detail information is in interrupt chapter.

Example: Stack pointer (STKP) reset routine.

MOV A, #00000111B

B0MOV STKP, A

STKn (stack buffer) initial value = xxxx xxxx xxxx xxxx, STKn = STKnH + STKnL (n = 7 ~ 0)

0F0H~0FFH Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

STKnH

- - - - - R/W R/W R/W

0F0H~0FFH Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

STKnL

R/W R/W R/W R/W R/W R/W R/W R/W

STKnH: Store PCH data as interrupt or call executing. The n expressed 0 ~7.

STKnL: Store PCL data as interrupt or call executing. The n expressed 0 ~7.

GIE - - - - STKPB2 STKPB1 STKPB0

- - - - - SnPC10 SnPC9 SnPC8

SnPC7 SnPC6 SnPC5 SnPC4 SnPC3 SnPC2 SnPC1 SnPC0

SONiX TECHNOLOGY CO., LTD Page 29 V1.4

Page 30

SN8P2714X_2715

8-bit micro-controller build-in 12-bit ADC

3.6.3 STACK OPERATION EXAMPLE

The two kinds of Stack-Save operations to reference the stack pointer (STKP) and write the program counter contents

(PC) into the stack buffer are CALL instruction and interrupt service. Under each condition, the STKP is decremented

and points to the next available stack location. The stack buffer stores the program counter about the op-code address.

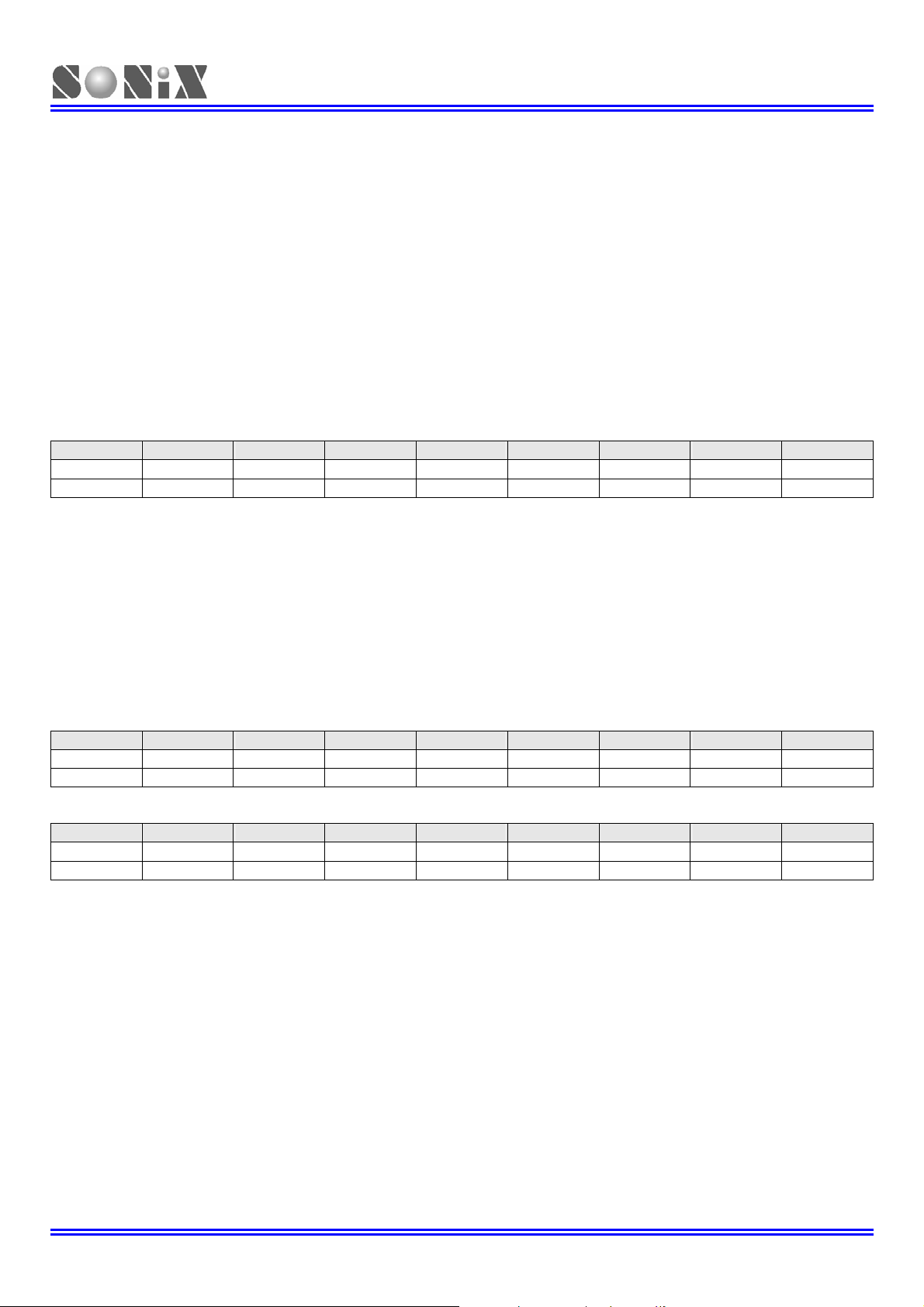

The Stack-Save operation is as following table.

Stack Level

STKPB2 STKPB1 STKPB0 High Byte Low Byte

0

1

2

3

4

5

6

7

>8

Table 3-1. STKP, STKnH and STKnL relative of Stack-Save Operation

STKP Register Stack Buffer Description

1 1 1 STK0H STK0L

1 1 0 STK1H STK1L

1 0 1 STK2H STK2L

1 0 0 STK3H STK3L

0 1 1 STK4H STK4L

0 1 0 STK5H STK5L

0 0 1 STK6H STK6L

0 0 0 STK7H STK7L

- - - - -

Stack Overflow

-

-

-

-

-

-

-

-

The RETI instruction is for interrupt service routine. The RET instruction is for CALL instruction. When a Stack-Restore

operation occurs, the STKP is incremented and points to the next free stack location. The stack buffer restores the last

program counter (PC) to the program counter registers. The Stack-Restore operation is as following table.

Stack Level

STKPB2 STKPB1 STKPB0 High Byte Low Byte

7

6

5

4

3

2

1

0

Table 3-2. STKP, STKnH and STKnL relative of Stack-Restore Operation

STKP Register Stack Buffer Description

0 0 0 STK7H STK7L

0 0 1 STK6H STK6L

0 1 0 STK5H STK5L

0 1 1 STK4H STK4L

1 0 0 STK3H STK3L

1 0 1 STK2H STK2L

1 1 0 STK1H STK1L

1 1 1 STK0H STK0L

-

-

-

-

-

-

-

-

SONiX TECHNOLOGY CO., LTD Page 30 V1.4

Page 31

SN8P2714X_2715

8-bit micro-controller build-in 12-bit ADC

3.7 PROGRAM COUNTER

The program counter (PC) is a 11-bit binary counter separated into the high-byte 3 bits and the low-byte 8 bits. This

counter is responsible for pointing a location in order to fetch an instruction for kernel circuit. Normally, the program

counter is automatically incremented with each instruction during program execution.

Besides, it can be replaced with specific address by executing CALL or JMP instruction. When JMP or CALL

instruction is executed, the destination address will be inserted to bit 0 ~ bit 10.

PC Initial value = xxxx 0000 0000 0000

Bit 15 Bit 14 Bit 13 Bit 12 Bit 11 Bit 10 Bit 9 Bit 8 Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

PC

PCH Initial value = xxxx x000

PCL Initial value = 0000 0000

- - - - - 0 0 0 0 0 0 0 0 0 0 0

0CFH Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

PCH

- - - - - R/W R/W R/W

0CEH Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

PCL

R/W R/W R/W R/W R/W R/W R/W R/W

- - - - - PC10 PC9 PC8

PC7 PC6 PC5 PC4 PC3 PC2 PC1 PC0

PCH PCL

SONiX TECHNOLOGY CO., LTD Page 31 V1.4

Page 32

SN8P2714X_2715

8-bit micro-controller build-in 12-bit ADC

3.7.1 ONE ADDRESS SKIPPING

There are 7 instructions (CMPRS, INCS, INCMS, DECS, DECMS, B0BTS0, B0BTS1) with one address skipping

function. If the result of these instructions is matched, the PC will add 2 steps to skip next instruction.

If the condition of bit test instruction is matched, the PC will add 2 steps to skip next instruction.

JMP C0STEP ; Else jump to C0STEP.

.

C0STEP: NOP

B0MOV A, BUF0 ; Move BUF0 value to ACC.

JMP C1STEP ; Else jump to C1STEP.

.

C1STEP: NOP

If the ACC is equal to the immediate data or memory, the PC will add 2 steps to skip next instruction.

JMP C0STEP ; Else jump to C0STEP.

.

C0STEP: NOP

If the result after increasing 1 or decreasing 1 is 0xffh (for DECS and DECMS) or 0x00h (for INCS and INCMS) ,

the PC will add 2 steps to skip next instruction.

INCS instruction:

JMP C0STEP ; Else jump to C0STEP.

.

C0STEP: NOP

INCMS instruction:

JMP C0STEP ; Else jump to C0STEP.

.

C0STEP: NOP

DECS instruction:

JMP C0STEP ; Else jump to C0STEP.

.

C0STEP: NOP

DECMS instruction:

JMP C0STEP ; Else jump to C0STEP.

.

C0STEP: NOP

B0BTS1

B0BTS0

CMPRS

INCS

INCMS

DECS

DECMS

FC ; Skip next instruction, if Carry_flag = 1

FZ ; Skip next instruction, if Zero flag = 0.

A, #12H ; Skip next instruction, if ACC = 12H.

BUF0 ; Skip next instruction, if BUF0 = 0X00H.

BUF0 ; Skip next instruction, if BUF0 = 0X00H.

BUF0 ; Skip next instruction, if BUF0 = 0XFFH.

BUF0 ; Skip next instruction, if BUF0 = 0XFFH.

SONiX TECHNOLOGY CO., LTD Page 32 V1.4

Page 33

SN8P2714X_2715

8-bit micro-controller build-in 12-bit ADC

3.7.2 MULTI-ADDRESS JUMPING

Users can jump round multi-address by either JMP instruction or ADD M, A instruction (M = PCL) to activate

multi-address jumping function. If carry signal occurs after execution of ADD PCL, A, the carry signal will not affect

PCH register.

Example: If PC = 0323H (PCH = 03H、PCL = 23H)

; PC = 0323H

MOV A, #28H

B0MOV PCL, A ; Jump to address 0328H

. .

. .

; PC = 0328H . .

MOV A, #00H

B0MOV PCL, A ; Jump to address 0300H

Example: If PC = 0323H (PCH = 03H、PCL = 23H)

; PC = 0323H

B0ADD PCL, A ; PCL = PCL + ACC, the PCH cannot be changed.

JMP A0POINT ; If ACC = 0, jump to A0POINT

JMP A1POINT ; ACC = 1, jump to A1POINT

JMP A2POINT ; ACC = 2, jump to A2POINT

JMP A3POINT ; ACC = 3, jump to A3POINT

. . ;

SONiX TECHNOLOGY CO., LTD Page 33 V1.4

Page 34

SN8P2714X_2715

8-bit micro-controller build-in 12-bit ADC

4 ADDRESSING MODE

4.1 OVERVIEW

The SN8P2710 provides three addressing modes to access RAM data, including immediate addressing mode, directly

addressing mode and indirectly address mode. The main purpose of the three different modes is described in the

following:

4.1.1 IMMEDIATE ADDRESSING MODE

The immediate addressing mode uses an immediate data to set up the location (MOV A, #I, B0MOV M,#I) in ACC or

specific RAM.

Immediate addressing mode

MOV A, #12H ; To set an immediate data 12H into ACC

4.1.2 DIRECTLY ADDRESSING MODE

The directly addressing mode uses address number to access memory location (MOV A,12H, MOV 12H,A).

Directly addressing mode

B0MOV A, 12H ; To get a content of location 12H of bank 0 and save in ACC

4.1.3 INDIRECTLY ADDRESSING MODE

The indirectly addressing mode is to set up an address in data pointer registers (Y/Z) and uses MOV instruction to

read/write data between ACC and @YZ register (MOV A,@YZ, MOV @YZ,A).

Example: Indirectly addressing mode with @YZ register

CLR Y ; To clear Y register to access RAM bank 0.

B0MOV Z, #12H ; To set an immediate data 12H into Z register.

B0MOV A, @YZ ; Use data pointer @YZ reads a data from RAM location

; 012H into ACC.

SONiX TECHNOLOGY CO., LTD Page 34 V1.4

Page 35

SN8P2714X_2715

8-bit micro-controller build-in 12-bit ADC

4.1.4 TO ACCESS DATA in RAM BANK 0

In the RAM bank 0, this area memory can be read/written by these twoaccess methods.

Example 1: To use RAM bank0 dedicate instruction (Such as B0xxx instruction).

B0MOV A, 12H ; To move content from location 12H of RAM bank 0 to ACC

Example 2: To use indirectly addressing mode with @YZ register.

CLR Y ; To clear Y register for accessing RAM bank 0.

B0MOV Z, #12H ; To set an immediate data 12H into Z register.

B0MOV A, @YZ ; Use data pointer @YZ reads a data from RAM location

; 012H into ACC.

SONiX TECHNOLOGY CO., LTD Page 35 V1.4

Page 36

SN8P2714X_2715

8-bit micro-controller build-in 12-bit ADC

5 SYSTEM REGISTER

5.1 OVERVIEW

The system special register is located at 80h~FFh. The main purpose of system registers is to control the peripheral

hardware of the chip. Using system registers can control I/O ports, ADC, PWM, timers and counters by programming.

The Memory map provides an easy and quick reference source for writing application program.

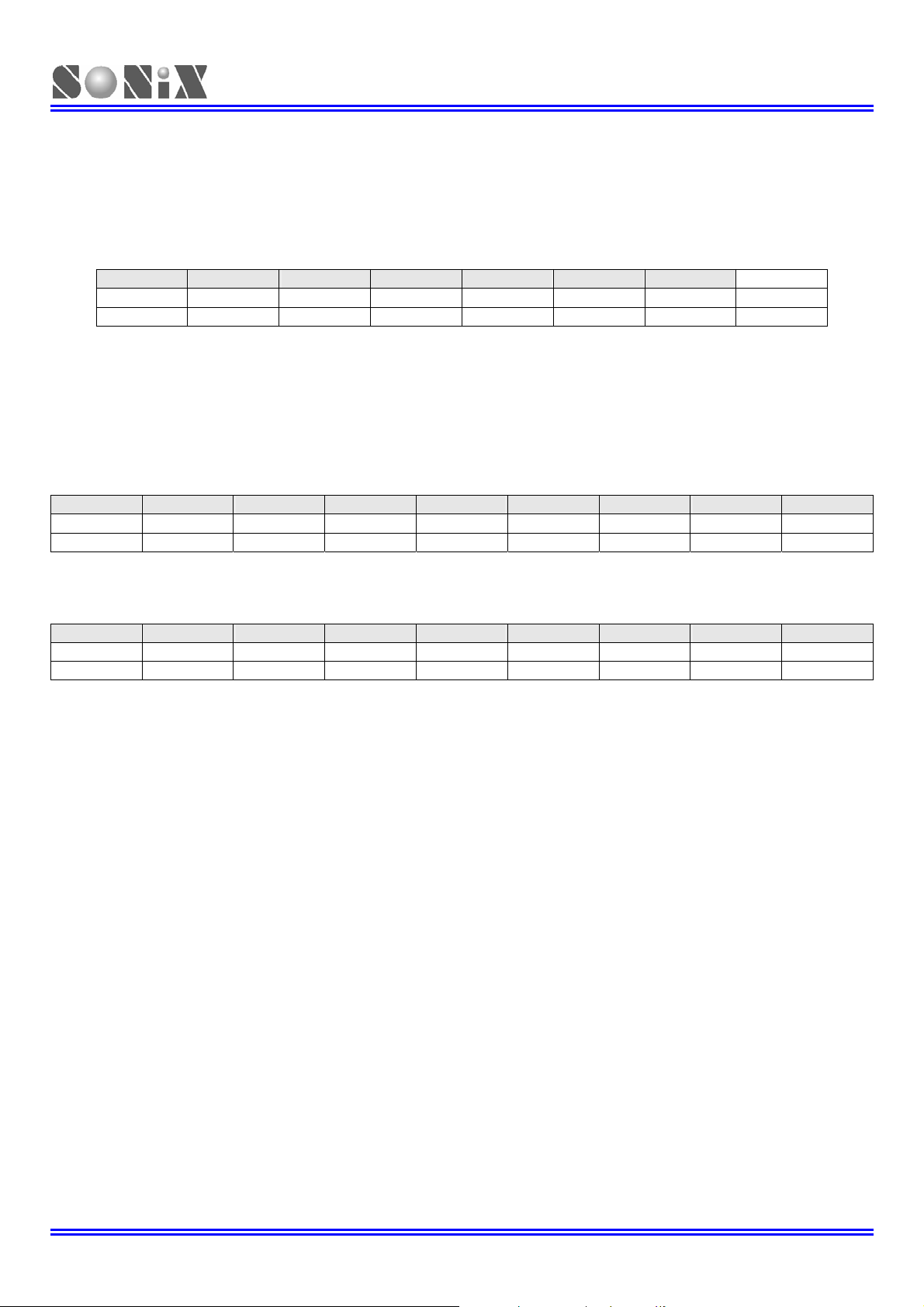

5.2 SYSTEM REGISTER ARRANGEMENT (BANK 0)

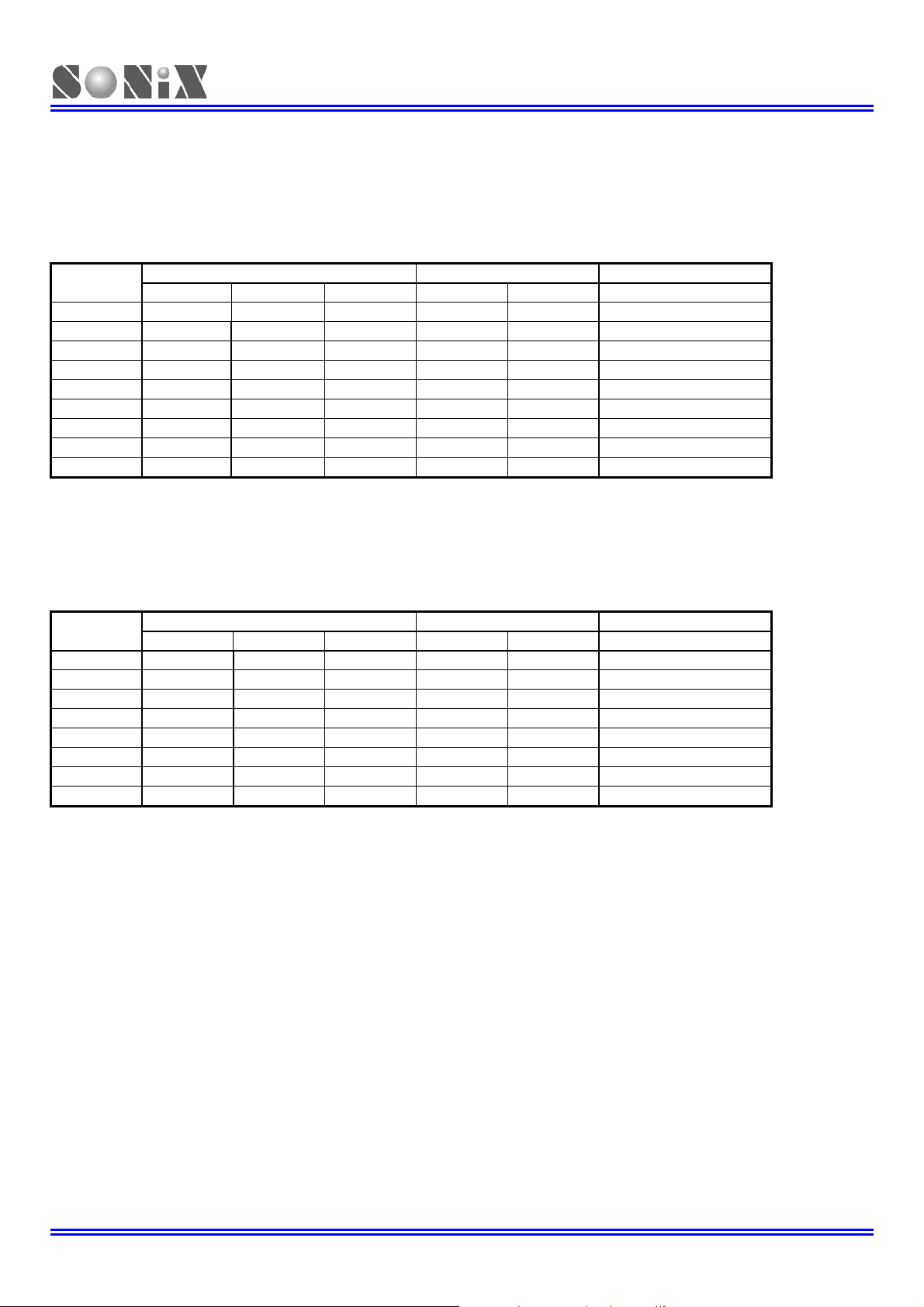

5.2.1 BYTES of SYSTEM REGISTER

SN8P2710

0 1 2 3 4 5 6 7 8 9 A B C D E F

- - R Z Y - PFLAG - - - - - - - - -

8

- - - - - - - - - - - - - - - -

9

- - - - - - - - - - - - - - P4CON -

A

DAM ADM ADB ADR - - - - - - - - - - - PEDGE

B

- - P2M - P4M P5M - - INTRQ INTEN OSCM -

C

P0 - P2 - P4 P5 - - T0M - TC0M TC0C TC1M TC1C TC1R STKP

D

P0UR - P2UR - P4UR P5UR - @YZ - - - - - - - -

E

STK7L STK7H STK6L STK6H STK5L STK5H STK4L STK4H STK3L STK3H STK2L STK2H STK1L STK1H STK0L STK0H

F

WDTR

TC0R PCL PCH

Table 5-1. System Register Arrangement of SN8P2710

Description

PFLAG = ROM page and special flag register. R = Working register and ROM lookup data buffer.

DAM = DAC’s mode register. Y, Z = Working, @YZ and ROM addressing register.

ADB = ADC’s data buffer. ADM = ADC’s mode register.

PnM = Port n input/output mode register. ADR = ADC’s resolution selects register.

INTRQ = Interrupts’ request register. Pn = Port n data buffer.

OSCM = Oscillator mode register. INTEN = Interrupts’ enable register.

T0M = Timer/ Counter 0, Timer/ Counter 1 speed selection . PCH, PCL = Program counter.

TC1M = Timer/Counter 1 mode register. TC0M = Timer/Counter 0 mode register.

TC1C = Timer/Counter 1 counting register. TC0C = Timer/Counter 0 counting register.

STKP = Stack pointer buffer. TC0R = Timer/Counter 0 auto-reload data buffer.

@HL = RAM HL indirect addressing index pointer. TC1R = Timer/Counter 1 auto-reload data buffer.

P4CON= Port 4 configuration setting STK0~STK7 = Stack 0 ~ stack 7 buffer.

¾ Note:

@YZ = RAM YZ indirect addressing index pointer.

a). All of register names had been declared in SONiX 8-bit MCU assembler.

b). One-bit name had been declared in SONiX 8-bit MCU assembler with “F” prefix code.

c). It will get logic “H” data, when use instruction to check empty location.

d). The low nibble of ADR register is read only.

e). “b0bset”, “b0bclr”, ”bset”, ”bclr” instructions only support “R/W” registers.

SONiX TECHNOLOGY CO., LTD Page 36 V1.4

Page 37

SN8P2714X_2715

8-bit micro-controller build-in 12-bit ADC

5.2.2 BITS of SYSTEM REGISTER

SN8P2710 System register table

Address Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 R/W Remarks

080H

081H

082H RBIT7 RBIT6 RBIT5 RBIT4 RBIT3 RBIT2 RBIT1 RBIT0 R/W R

083H ZBIT7 ZBIT6 ZBIT5 ZBIT4 ZBIT3 ZBIT2 ZBIT1 ZBIT0 R/W Z

084H YBIT7 YBIT6 YBIT5 YBIT4 YBIT3 YBIT2 YBIT1 YBIT0 R/W Y

085H

086H NT0 NPD LVD36 LVD24 - C DC Z R/W PFLAG

087H - - - - - - - - - -

0AEH P4CON7 P4CON6 P4CON 5 P4CON4 P4CON3 P4CON2 P4CON1 P4CON0 W P4CON

0B0H DAENB DAB6 DAB5 DAB4 DAB3 DAB2 DAB1 DAB0 R/W DAM data register

0B1H ADENB ADS EOC GCHS - CHS2 CHS1 CHS0 R/W ADM mode register

0B2H ADB11 ADB10 ADB9 ADB8 ADB7 ADB6 ADB5 ADB4 R ADB data buffer

0B3H - ADCKS1 - ADCKS0 ADB3 ADB2 ADB1 ADB0 R/W ADR register

0B4H - - - - - - - - -

0B5H - - - - - - - - -

0B6H - - - - - - - - -

0B8H - - - - - - - - -

0BFH - - - P00G1 P00G0 - - - R/W PEDGE

0C0H - - - - - - - - -

0C1H - - - - - - - - -

0C2H P27M P26M P25M P24M P23M P22M P21M P20M R/W P2M I/O direction

0C3H - - - - - - - - -

0C4H P47M P46M P45M P44M P43M P42M P41M P40M R/W P4M I/O direction

0C5H - P56M P55M P54M P53M P52M P51M P50M R/W P5M I/O direction

0C8H - TC1IRQ TC0IRQ - - - P01IRQ P00IRQ R/W INTRQ

0C9H - TC1IEN TC0IEN - - - P01IEN P00IEN R/W INTEN

0CAH - - - - CPUM0 CLKMD STPHX - R/W OSCM

0CCH WDTR7 WDTR6 WDTR5 WDTR4 WDTR3 WDTR2 WDTR1 WDTR0 W WDTR

0CDH TC0R7 TC0R6 TC0R5 TC0R4 TC0R3 TC0R2 TC0R1 TC0R0 W TC0R

0CEH PC7 PC6 PC5 PC4 PC3 PC2 PC1 PC0 R/W PCL

0CFH - - - - - PC10 PC9 PC8 R/W PCH

0D0H - - - - P03 P02 P01 P00 R P0 data buffer

0D1H - - - - - - - - -

0D2H P27 P26 P25 P24 P23 P22 P21 P20 R/W P2 data buffer

0D3H - - - - - - - - -

0D4H P47 P46 P45 P44 P43 P42 P41 P40 R/W P4 data buffer

0D5H - P56 P55 P54 P53 P52 P51 P50 R/W P5 data buffer

0D8H - - - - TC1X8 TC0X8 - - R/W T0M

0D9H - - - - - - - - -

0DAH TC0ENB TC0rate2 TC0rate1 TC0rate0 TC0CKS ALOAD0 TC0OUT

0DBH TC0C7 TC0C6 TC0C5 TC0C4 TC0C3 TC0C2 TC0C1 TC0C0 R/W TC0C

0DCH TC1ENB TC1rate2 TC1rate1 TC1rate0 TC1CKS ALOAD1 TC1OUT

0DDH TC1C7 TC1C6 TC1C5 TC1C4 TC1C3 TC1C2 TC1C1 TC1C0 R/W TC1C

0DEH TC1R7 TC1R6 TC1R5 TC1R4 TC1R3 TC1R2 TC1R1 TC1R0 W TC1R

0DFH GIE - - - - STKPB2 STKPB1 STKPB0 R/W STKP stack pointer

0E0H - - - - - P02R P01R P00R W P0UR

0E1H - - - - - - - - -

0E2H P27R P26R P25R P24R P23R P22R P21R P20R W P2UR

0E3H - - - - - - - - -

0E4H P47R P46R P45R P44R P43R P42R P41R P40R W P4UR

0E5H - P56R P54R P54R P53R P52R P51R P50R W P5UR

0E6H - - - - - - - - -

0E7H @YZ7 @YZ6 @YZ5 @YZ4 @YZ3 @YZ2 @YZ1 @YZ0 R/W @YZ index pointer

0E9H - - - - - - - - -

0F0H S7PC7 S7PC6 S7PC5 S7PC4 S7PC3 S7PC2 S7PC1 S7PC0 R/W STK7L

0F1H - - - - - S7PC10 S7PC9 S7PC8 R/W STK7H

0F2H S6PC7 S6PC6 S6PC5 S6PC4 S6PC3 S6PC2 S6PC1 S6PC0 R/W STK6L

0F3H - - - - - S6PC10 S6PC9 S6PC8 R/W STK6H

PWM0OUT

PWM1OUT

R/W TC0M

R/W TC1M

SONiX TECHNOLOGY CO., LTD Page 37 V1.4

Page 38

SN8P2714X_2715

8-bit micro-controller build-in 12-bit ADC

Address Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 R/W Remarks

0F4H S5PC7 S5PC6 S5PC5 S5PC4 S5PC3 S5PC2 S5PC1 S5PC0 R/W STK5L

0F5H - - - - - S5PC10 S5PC9 S5PC8 R/W STK5H

0F6H S4PC7 S4PC6 S4PC5 S4PC4 S4PC3 S4PC2 S4PC1 S4PC0 R/W STK4L

0F7H - - - - - S4PC10 S4PC9 S4PC8 R/W STK4H

0F8H S3PC7 S3PC6 S3PC5 S3PC4 S3PC3 S3PC2 S3PC1 S3PC0 R/W STK3L

0F9H - - - - - S3PC10 S3PC9 S3PC8 R/W STK3H

0FAH S2PC7 S2PC6 S2PC5 S2PC4 S2PC3 S2PC2 S2PC1 S2PC0 R/W STK2L

0FBH - - - - - S2PC10 S2PC9 S2PC8 R/W STK2H

0FCH S1PC7 S1PC6 S1PC5 S1PC4 S1PC3 S1PC2 S1PC1 S1PC0 R/W STK1L

0FDH - - - - - S1PC10 S1PC9 S1PC8 R/W STK1H

0FEH S0PC7 S0PC6 S0PC5 S0PC4 S0PC3 S0PC2 S0PC1 S0PC0 R/W STK0L

0FFH - - - - - S0PC10 S0PC9 S0PC8 R/W STK0H

Table. Bit System Register Table of SN8P2710

Note:

a). To avoid system error, please be sure to put all the “0” as it indicates in the above table

b). All of register name had been declared in SONiX 8-bit MCU assembler.