Page 1

Preliminary SN8P1702A/SN8P1703A

SN8P1700A 系列

用户手册

8-bit micro-controller build-in 12-bit ADC

SN8P1702A

SN8P1703A

SONiX 8 位单片机

SONIX 公司保留对以下所有产品在可靠性、功能和设计方面的改进做进一步说明的权利。SONIX 不承担由本手

册所涉及的产品或电路的运用和使用所引起的任何责任。SONIX 的产品不是专门设计应用于外科植入、生命维持和

任何 SONIX 产品的故障会对个体造成伤害甚至死亡的领域。如果将 SONIX 的产品应用于上述领域,即使这些是由

SONIX 在产品设计和制造上的疏忽引起的,用户也应赔偿所有费用、损失、合理的人身伤害或死亡所直接或间接产

生的律师费用,并且用户保证 SONIX 及其雇员、子公司、分支机构和销售商与上述事宜无关。

SONiX TECHNOLOGY CO., LTD Page 1 Revision 0.8

Page 2

版本号 日期 说明

VER0.1

VER0.2

VER0.3

VER0.4

VER0.5

VER0.6

VER0.7

VER0.8

2003 年 7 月 V1.0 第一版

2003 年 7 月 更改了看门狗的溢出列表

2003 年 7 月

2003 年 8 月

2003 年 9 月 1. 增加了 SN8P1702A SSOP20 到 Mask Mass 产品中

2003 年 9 月 1. 调整了 ADC 的转换时间表

2003 年 12 月 1. 把最低工作电压从“2.2V”改为“2.4V”

2003 年 12 月 1.把 SN8A1702B(MASK)的“P5.3”改为“P5.3/BZ1/PWM1”

2004 年 7 月 1.把 AVRE FH 和 AVREFL 之间的最小电压由 1.2V 改为 2.0V。

1. 修改了产品列表

2. 修改了 DC 电流特性

3. 更改特性

4. 将 SN8P1703 部分的数据改成 SN8P1706A

5. 在引脚说明的后面重新将编译选项表定位

6. 修正了 QTP 的校准表

7. 更改了寄存器的说明

8. 在电气特性里增加了 LVD 的标准值 1.8V

9. 在编译选项里增加了噪声滤波器

2. 增加定时器 TC1 到升级表中

3. 调整了第八章的表格/图的顺序

4. 调整了定时器 TC1/TC0 说明和列表

5. 调整了 PWM 的说明和列表

6. 调整了电气特性列表

2. 调整了 PEDGE 寄存器的说明

3. 调整了 INTRQ 寄存器的说明

4. 删除了校准表

5. 将 SN8P1702A 和 SN8P1703A 的引脚分开说明

6. 删除了 PCB 布线

7. 增加了 P-DIP 20 和 SOP 20 的封装

8. 增加了 SN8A1702B 和 SN8A1703A 的说明

2. 删除了“SN8P1702AOTP”芯片宣告

3. 删除了 SN8P1702A 和 SN8A1702A 所有的 SSOP20 的封装说明。

4. 在第一章节里修改了“OTP/MASK 的关系表”和“SN8P1702 的升级表”,将

5. 在第一章节里删除了 ADC 的等级表

6. 在“系统寄存器的字节”里将寄存器“TC0C”的名称改为“TC1C”

7. 删除了“OSG”的编译选项和所有的有关说明

8. 删除了“32K_X’tal”的编译选项和所有的有关说明

9. 更正了 P00G[1:0](PEDGE 寄存器)的定义

10.把 SN8P1702(老版 OTP)的 P5.3 引脚由“P5.3/BZ1/PWM1”改为“P5.3”

11.把 SN8P1702A/SN8P1703A 的 RST 由“RST”改为“RST/VPP”

12.在编译选项章节中增加了“典型工作电压和系统时钟频率表的关系”

2.调整 ADC 的烧录注意事项。

3.在 EOC 的说明中,把“ADENB 位复位”改为“ADS 位复位”。

4.调整了部分电气特性:AVref ,Vani,增加 Tast 。

Preliminary SN8P1702A/SN8P1703A

8-bit micro-controller build-in 12-bit ADC

修 正 记 录

“SN8A1703A”重命名为“SN8A1703B”

将“01=上升沿”改为“01=下降沿”

将“10=下降沿”改为“10=上升沿”

SONiX TECHNOLOGY CO., LTD Page 2 Revision 0.8

Page 3

Preliminary SN8P1702A/SN8P1703A

8-bit micro-controller build-in 12-bit ADC

目 录

1 产品简介 ................................................................................................................................................... 6

1.1 概述 .......................................................................................................................................................6

1.1.1 产品性能表 ...................................................................................................................................6

1.1.2 MASK / OTP 关系表.....................................................................................................................6

1.1.3 SN8P1702 的升级(老版 OTP) .................................................................................................6

1.2 SN8P1702A / SN8P1703A 特性 ...........................................................................................................7

1.3 系统框图................................................................................................................................................8

1.4 引脚配置................................................................................................................................................9

1.4.1 SN8P1702A 引脚配置 ..................................................................................................................9

1.4.2 SN8P1703A 引脚配置 ................................................................................................................10

1.5 引脚说明.............................................................................................................................................. 11

1.6 引脚电路图 .......................................................................................................................................... 11

2 编译选项表(CODE OPTION) ............................................................................................................. 12

3 存储器..................................................................................................................................................... 13

3.1 程序存储器(ROM) ..........................................................................................................................13

3.1.1 概述 ............................................................................................................................................13

3.1.2 复位向量地址(0000H)............................................................................................................13

3.1.3 中断向量地址(0008H)............................................................................................................14

3.1.4 CHECKSUM 计算.......................................................................................................................15

3.1.5 通用程序存储区 ..........................................................................................................................15

3.1.6 查表功能 .....................................................................................................................................16

3.1.7 跳转表.........................................................................................................................................17

3.2 数据存储器(RAM)...........................................................................................................................18

3.2.1 概述 ............................................................................................................................................18

3.2.2 工作寄存器 .................................................................................................................................19

3.2.2.1 Y, Z 寄存器 ...........................................................................................................................19

3.2.2.2 R 寄存器..............................................................................................................................19

3.2.3 程序状态字 .................................................................................................................................20

3.2.3.1 进位标志.............................................................................................................................20

3.2.3.2 辅助进位标志......................................................................................................................20

3.2.3.3 零标志 ................................................................................................................................20

3.3 累加器(ACC) ..................................................................................................................................21

3.4 堆栈 .....................................................................................................................................................22

3.4.1 概述 ............................................................................................................................................22

3.4.2 堆栈寄存器 .................................................................................................................................23

3.4.3 堆栈操作举例..............................................................................................................................24

3.5 程序计数器(PC)..............................................................................................................................25

3.5.1 单地址跳转 .................................................................................................................................25

3.5.2 多地址跳转 .................................................................................................................................26

4 寻址模式 ................................................................................................................................................. 27

4.1 概述 .....................................................................................................................................................27

4.2 立即寻址..............................................................................................................................................27

4.3 直接寻址..............................................................................................................................................27

4.4 间接寻址..............................................................................................................................................27

4.5 寻址 RAM BANK0 ...............................................................................................................................27

5 系统寄存器.............................................................................................................................................. 28

5.1 概述 .....................................................................................................................................................28

5.2 系统寄存器配置(BANK 0)...............................................................................................................28

5.2.1 系统寄存器的字节.......................................................................................................................28

5.2.2 系统寄存器的位地址配置表 ........................................................................................................29

6 上电复位 ................................................................................................................................................. 30

6.1 概述 .....................................................................................................................................................30

6.2 外部复位..............................................................................................................................................31

7 振荡器..................................................................................................................................................... 32

7.1 概述 .....................................................................................................................................................32

7.1.1 时钟框图 .....................................................................................................................................32

7.1.2 OSCM 寄存器.............................................................................................................................33

7.1.3 外部高速振荡器 ..........................................................................................................................34

7.1.4 振荡器模式编译选项...................................................................................................................34

SONiX TECHNOLOGY CO., LTD Page 3 Revision 0.8

Page 4

Preliminary SN8P1702A/SN8P1703A

8-bit micro-controller build-in 12-bit ADC

7.1.5 振荡器二分频编译选项 ...............................................................................................................34

7.2 系统振荡器电路图 ...............................................................................................................................35

7.3 外部 RC 振荡器频率测试.....................................................................................................................35

7.4 内部低速振荡器...................................................................................................................................36

7.5 系统模式..............................................................................................................................................37

7.5.1 概述 ............................................................................................................................................37

7.5.2 普通模式 .....................................................................................................................................37

7.5.3 低速模式 .....................................................................................................................................37

7.5.4 绿色模式 .....................................................................................................................................37

7.5.5 省电模式 .....................................................................................................................................37

7.5.6 系统模式控制..............................................................................................................................38

7.5.6.1 系统模式转换......................................................................................................................39

7.6 唤醒时间..............................................................................................................................................40

7.6.1 概述 ............................................................................................................................................40

7.6.2 硬件唤醒 .....................................................................................................................................40

7.6.3 外部唤醒触发控制.......................................................................................................................40

8 定时/计数器............................................................................................................................................. 41

8.1 看门狗定时器(WDT) .......................................................................................................................41

8.2 T0M 寄存器 .........................................................................................................................................42

8.3 定时计数器 TC0 ..................................................................................................................................43

8.3.1 概述 ............................................................................................................................................43

8.3.2 TC0M 模式寄存器.......................................................................................................................44

8.3.3 TC0C 计数寄存器 .......................................................................................................................44

8.3.4 TC0 溢出时间 .............................................................................................................................45

8.3.5 TC0R 自动装载寄存器................................................................................................................48

8.3.6 TC0 操作流程 .............................................................................................................................49

8.3.7 TC0 时钟频率输出(BUZZER 输出) ........................................................................................51

8.3.8 TC0OUT 频率表 .........................................................................................................................52

8.4 定时/计数器 TC1 .................................................................................................................................54

8.4.1 概述 ............................................................................................................................................54

8.4.2 TC1M 模式寄存器.......................................................................................................................55

8.4.3 TC1C 计数寄存器 .......................................................................................................................55

8.4.4 TC1 溢出时间 .............................................................................................................................56

8.4.5 TC1R 自动装载寄存器................................................................................................................59

8.4.6 TC1 操作流程 .............................................................................................................................60

8.4.7 TC1 时钟频率输出(BUZZER 输出) ........................................................................................62

8.5 PWM ...................................................................................................................................................63

8.5.1 概述 ............................................................................................................................................63

8.5.2 PWM 操作举例 ...........................................................................................................................65

9 中断 ........................................................................................................................................................ 66

9.1 概述 .....................................................................................................................................................66

9.2 INTEN 中断使能寄存器.......................................................................................................................66

9.3 INTRQ 中断请求寄存器.......................................................................................................................67

9.4 中断操作举例 ......................................................................................................................................68

9.4.1 GIE 总中断操作 ..........................................................................................................................68

9.4.2 INT0 (P0.0)中断操作 ..................................................................................................................69

9.4.3 TC0 中断操作 .............................................................................................................................70

9.4.4 TC1 中断操作 .............................................................................................................................71

9.4.5 多中断操作 .................................................................................................................................72

10 输入/输出............................................................................................................................................. 73

10.1 概述.....................................................................................................................................................73

10.2 输入/输出功能表..................................................................................................................................73

10.3 上拉电阻..............................................................................................................................................74

10.4 I/O 端口模式........................................................................................................................................75

10.5 I/O 数据寄存器 ....................................................................................................................................76

11 4 通道 A/D 转换................................................................................................................................... 77

11.1 概述 .....................................................................................................................................................77

11.2 ADM 寄存器 ........................................................................................................................................78

11.3 ADR 寄存器.........................................................................................................................................78

11.4 ADB 寄存器 .........................................................................................................................................79

11.5 P4C0N 寄存器.....................................................................................................................................79

11.6 ADC 转换时间 .....................................................................................................................................80

SONiX TECHNOLOGY CO., LTD Page 4 Revision 0.8

Page 5

Preliminary SN8P1702A/SN8P1703A

8-bit micro-controller build-in 12-bit ADC

11.7 ADC 电路 ............................................................................................................................................81

12 编程..................................................................................................................................................... 82

12.1 编程模板..............................................................................................................................................82

12.2 程序检查对照表...................................................................................................................................85

13 指令表 ................................................................................................................................................. 86

14 电气特性.............................................................................................................................................. 87

14.1 极限参数..............................................................................................................................................87

14.2 标准电气特性 ......................................................................................................................................87

15 封装..................................................................................................................................................... 88

15.1 P-DIP18 PIN .......................................................................................................................................88

15.2 SOP18 PIN..........................................................................................................................................89

15.3 P-DIP 20 PIN.......................................................................................................................................90

15.4 SOP 20 PIN.........................................................................................................................................91

15.5 SSOP 20 PIN ......................................................................................................................................92

SONiX TECHNOLOGY CO., LTD Page 5 Revision 0.8

Page 6

Preliminary SN8P1702A/SN8P1703A

r

V

V

V

V13V

8-bit micro-controller build-in 12-bit ADC

1 产品简介

1.1 概述

SN8P1702A/SN8P1703A 8 位微控制器采用 CMOS 技术,结构独特,具有低功耗、高性能的特点。

SN8P1700A 系列内部包括一个大容量的程序存储器 OTP ROM,一个数据存储器 RAM,两个 8 位定时/计数器

(TC0,TC1),一个看门狗定时器 WDT,三个中断源(TC0, TC1, INT0),4 通道的 8 位/12 位分辨率的 AD 转换器,

两通道的高速 PWM 输出(PWM0, PWM1),两通道峰鸣器输出(BZ0, BZ1)和 8 层堆栈缓冲器。

此外,芯片有四种可选择的外部振荡源,用户可自行选择振荡方式:高/低速晶体振荡器、陶瓷谐振器和廉价的

RC 振荡器等。SN8P1700A 系列还可以通过程序设定内部 RC 振荡器作为低速模式时钟源。

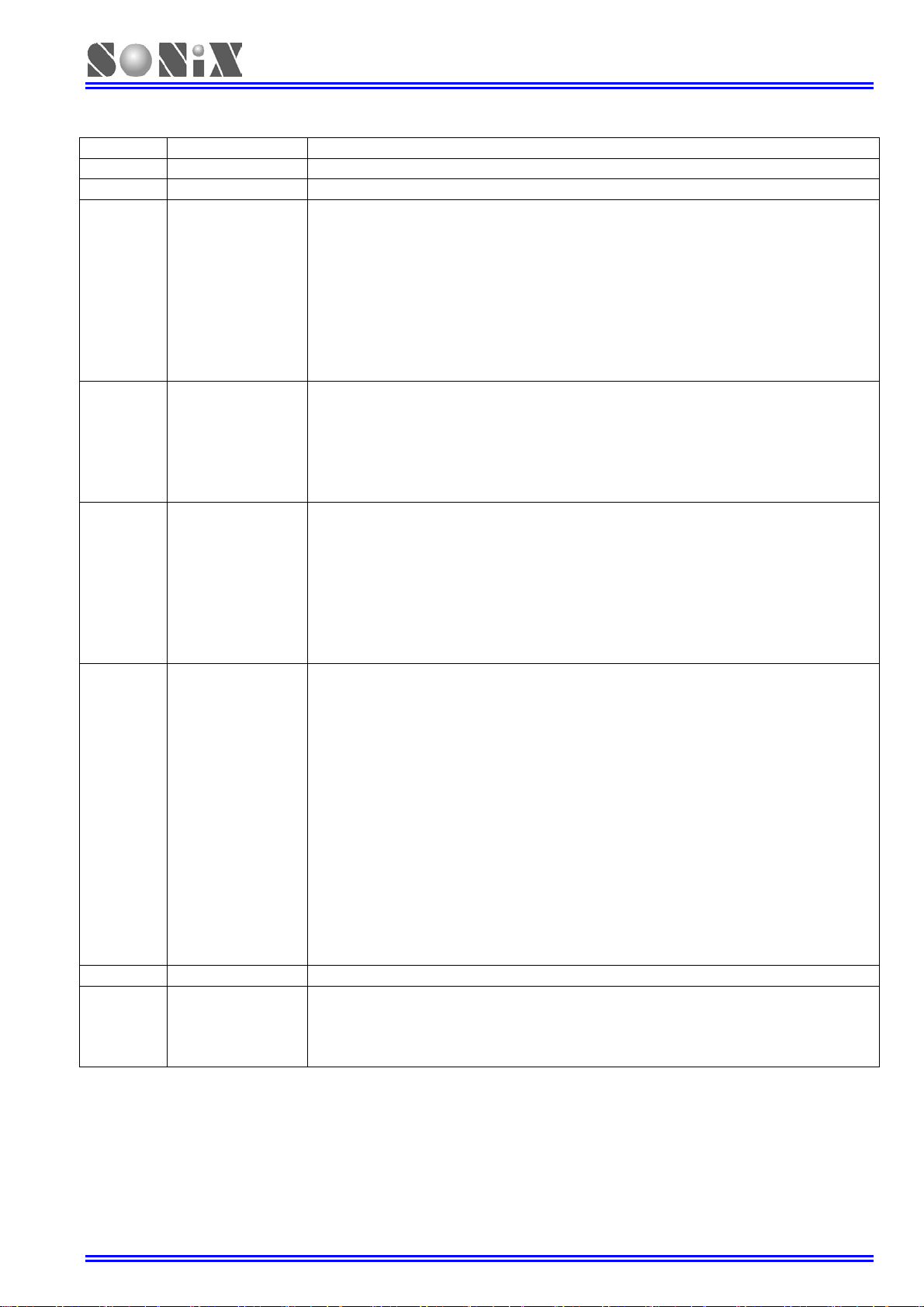

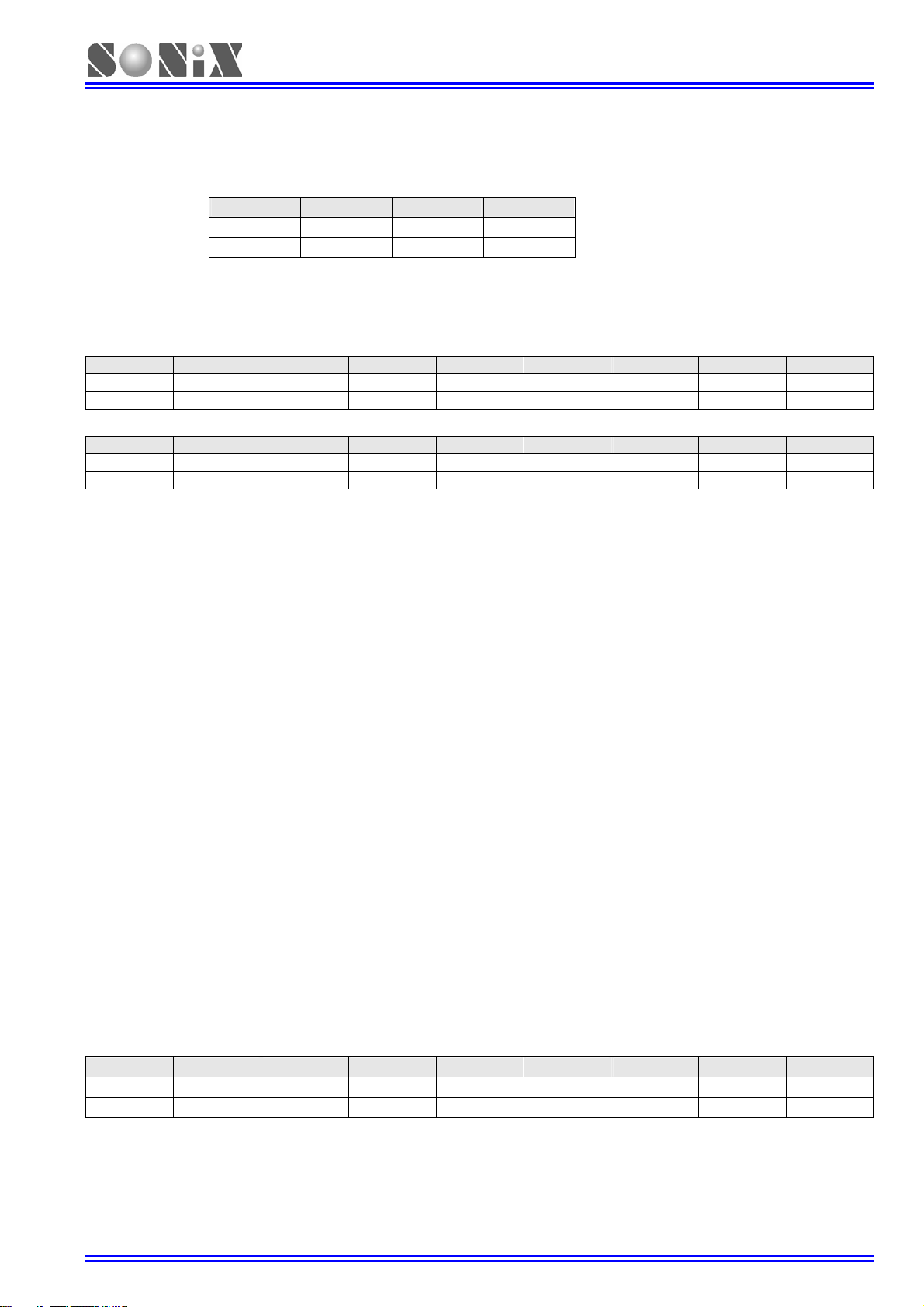

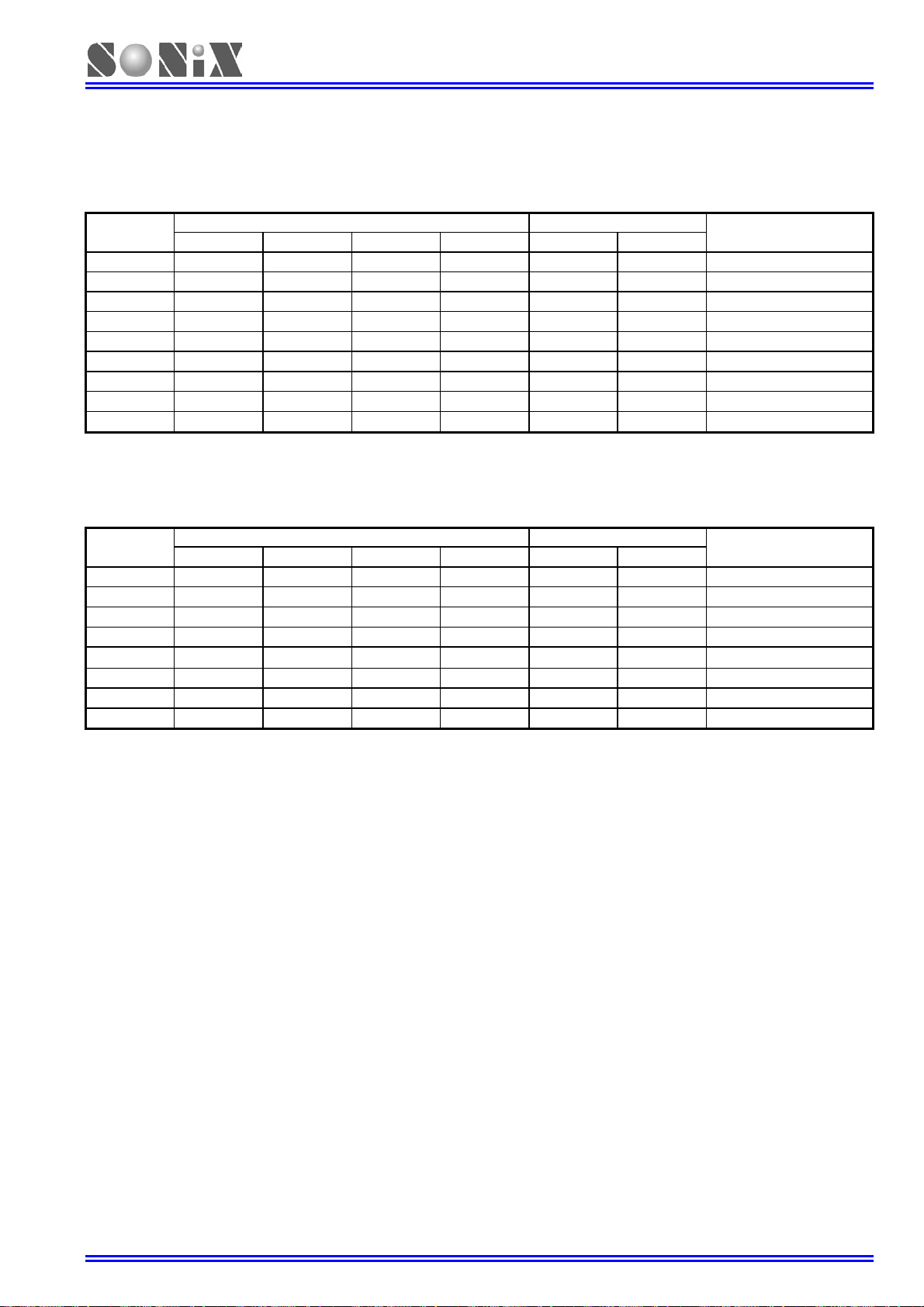

1.1.1 产品性能表

CHIP ROM RAM 堆栈

SN8P1702A 1K*16 128 SN8P1703A 1K*16 128

8

表 1-1 SN8P1702A / SN8P1703A 的产品列表

定时器 PWM

T0 TC0 TC1

-

I/O AVref ADC

12 - 4ch 2 3 DIP18/SOP18

4ch 2 3 DIP20/SOP20/SSOP20

Buzze

唤醒功能

引脚数目

封装

1.1.2 MASK / OTP 关系表

MASK 封装形式 OTP 汇编宣告

SN8A1702B DIP18/SOP18 SN8P1702A CHIP SN8P1702A

SN8A1703B DIP20/SOP20 /SSOP20 SN8P1703A CHIP SN8P1703A

1.1.3 SN8P1702 的升级(老版 OTP)

Chip SN8P1702 SN8P1702A SN8P1703A

汇编宣告 SN8P1702 SN8P1702A SN8P1703A

标准电流(3V) 3uA < 1uA < 1uA

4MHz 工作电流(3V) 1.5mA < 1mA < 1mA

4MHz 工作电流(5V) 7mA < 3mA < 3mA

绿色模式 - 是 是

P0.0 中断边沿 下降沿 下降/上升/双边沿 下降/上升/双边沿

P1 唤醒 低电平 改变电平 改变电平

AVREFH 无 无 是

ADC 通道 4 4 4

P4CON 寄存器 - 是 是

RAM 64 128 128

GPIO 12 12 13

TC1 - 是 是

PWM - 是 是

上拉电阻寄存器 通过端口 通过引脚 通过引脚

上拉电阻寄存器 @SET_PUR PnUR PnUR

SN8P1702 引脚兼容性 是 是 否

WDT 时钟源 高速时钟 高速时钟(内部 RC) 高速时钟(内部 RC)

内部 RC 总处于开发状态 WDT 的时钟源固定为内

部 RC

上电延迟(4MHz/3V) ~70ms ~200ms ~200ms

MASK SN8A1702A SN8A1702B SN8A1703B

封装 PDIP18/SOP18 PDIP18/SOP18 PDIP20/SOP20/SSOP20

¾ 注:在以后的新项目中,我们不建议使用 SN8P1702。

- 是 是

SONiX TECHNOLOGY CO., LTD Page 6 Revision 0.8

Page 7

Preliminary SN8P1702A/SN8P1703A

8-bit micro-controller build-in 12-bit ADC

1.2 SN8P1702A / SN8P1703A 特性

♦ 存储器配置 ♦ 三个中断源

OTP ROM:1K * 16 bits. 两个内部中断:TC0, TC1

RAM:128 * 8 bits. 一个外部中断:INT0.

♦ I/O 配置 ♦ 一个 4 通道 12 位 ADC

单向输入:P0

输入/输出:P1,P4,P5 ♦ 两个高速 PWM 输出.

具有唤醒功能的引脚:P0,P1 ♦ 两个 Buzzer 输出(BZ0/BZ1)

上拉电阻寄存器:P0,P1,P4,P5

外部中断:P0 ♦ 双重时钟系统提供 4 种操作模式

引脚 P4 和 ADC 输入共享. 外部高速时钟:RC 最大 10MHz

外部高速时钟:晶体 最大 16 MHz

♦ 两个 8 位定时/计数器. (TC0, TC1). 内部低速时钟:RC 16KHz(3V),32KHz(5V)

♦ 内置看门狗定时器 普通模式:高速时钟和内部低速时钟同时运行

♦ 8 层堆栈缓冲器 低速模式:仅内部低速时钟运行

绿色模式:由定时器周期性唤醒

睡眠模式:高速时钟和内部低速时钟都停止

♦ 59 条功能强大的质量

一个指令周期为四个时钟

所有指令长度均为 1 个字长 ♦ 封装 (支持的芯片格式)

绝大部分指令的周期为 1 个周期. SN8P1702A:PDIP 18 / SOP 18

查表指令(MOVC)寻址整个 ROM SN8P1703A:PDIP 20 / SOP 20 / SSOP20

SONiX TECHNOLOGY CO., LTD Page 7 Revision 0.8

Page 8

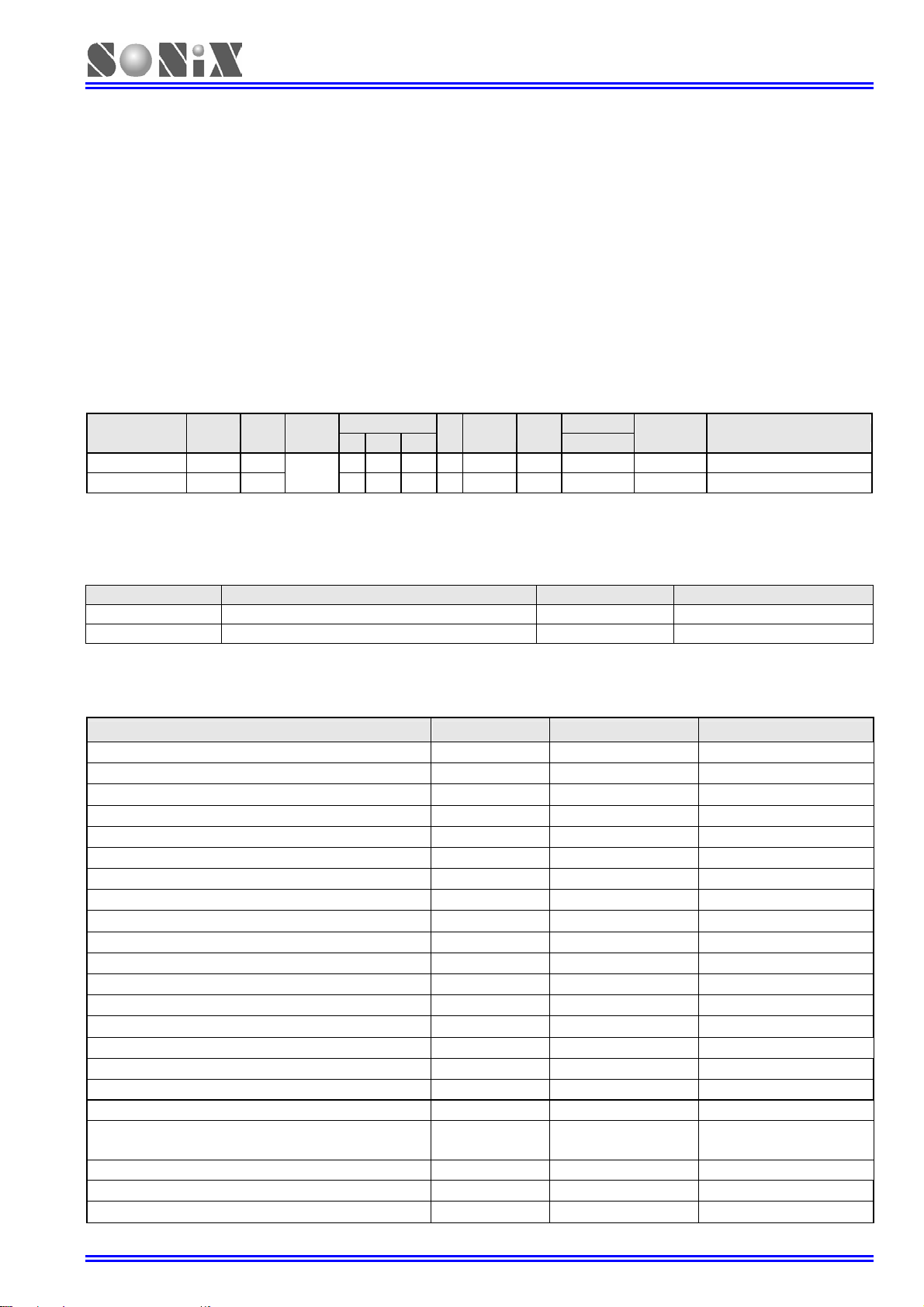

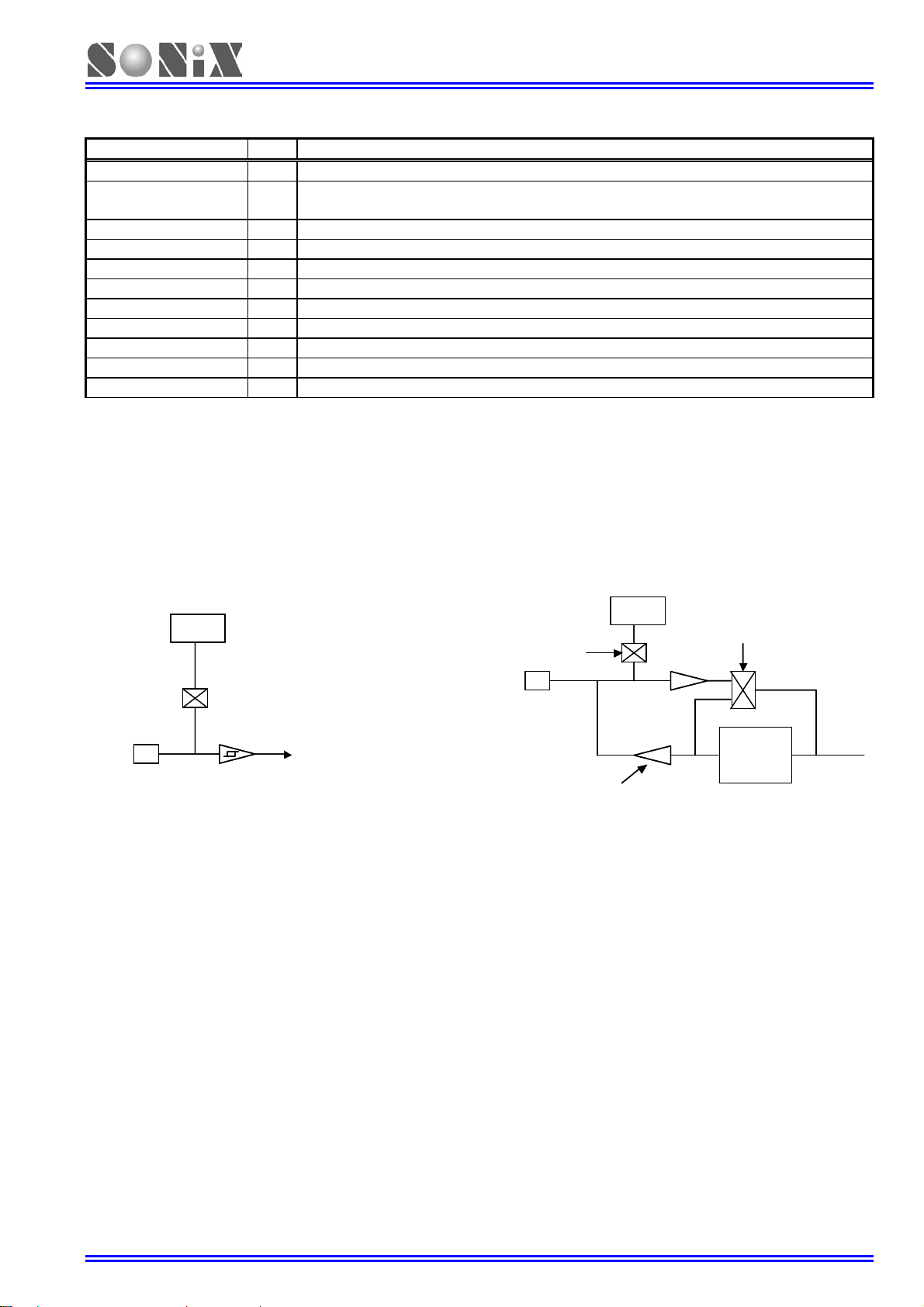

1.3 系统框图

Preliminary SN8P1702A/SN8P1703A

8-bit micro-controller build-in 12-bit ADC

PORT 0

PC

OTP

IR

FLAGS

ALU

ACC

INTERRUPT

CONT RO L

PORT 1 PORT 4 PORT 5

ROM

SYST EM REGIST ER

H-OSC

TIMING GENERATOR

RAM

Internal

CLK

TIMER & COUNTER

Low Volt

Detector

Watch-Dog

Timer

PWM0

PWM1

ADC

PWM0/Buzzer0

PWM1/Buzzer1

AIN0~AIN3

图 1-1 系统的简单框图

SONiX TECHNOLOGY CO., LTD Page 8 Revision 0.8

Page 9

Preliminary SN8P1702A/SN8P1703A

1.4 引脚配置

格式说明:SN8P170XAY

= P> PDIP, S > SOP,X> SSOP

Y

1.4.1 SN8P1702A 引脚配置

OTP:

SN8P1702AS (SOP 18PIN) / SN8P1702AP (PDIP 18PIN)

P0.0/INT0 1 U 18 VDD

RST 2 17 XIN

P1.1 3 16 XOUT

P1.0 4 15 P5.0

VSS 5 14 P5.1

P4.3/AIN3 6 13 P5.2

P4.2/AIN2 7 12 P5.3/BZ1/PWM1

P4.1/AIN1 8 11 P5.4/BZ0/PWM0

P4.0/AIN0 9 10 VDD

SN8P1702AP

SN8P1702AS

MASK:

SN8A1702BS(SOP 18PIN) / SN8A1702BP(PDIP 18PIN)

P0.0/INT0 1 U 18 VDD

RST 2 17 XIN

P1.1 3 16 XOUT

P1.0 4 15 P5.0

VSS 5 14 P5.1

P4.3/AIN3 6 13 P5.2

P4.2/AIN2 7 12 P5.3/BZ1/PWM1

P4.1/AIN1 8 11 P5.4/BZ0/PWM0

P4.0/AIN0 9 10 VDD

SN8A1702BP

SN8A1702BS

老版 OTP:

SN8P1702S(SOP 18PIN) / SN8P1702P(PDIP 18PIN)

P0.0/INT0 1 U 18 VDD

RST 2 17 XIN

P1.1 3 16 XOUT

P1.0 4 15 P5.0

VSS 5 14 P5.1

P4.3/AIN3 6 13 P5.2

P4.2/AIN2 7 12 P5.3

P4.1/AIN1 8 11 P5.4/BZ0/PWM0

P4.0/AIN0 9 10 VDD

SN8P1702P

SN8P1702S

8-bit micro-controller build-in 12-bit ADC

SONiX TECHNOLOGY CO., LTD Page 9 Revision 0.8

Page 10

Preliminary SN8P1702A/SN8P1703A

8-bit micro-controller build-in 12-bit ADC

1.4.2 SN8P1703A 引脚配置

OTP:

SN8P1703AS (SOP 20PIN) / SN8P1703AP (PDIP 20PIN) / SN8P1703AX (SSOP 20PIN)

P0.0/INT0 1 U 20 VDD

RST/VPP 2 19 XIN

P1.1 3 18 XOUT

P1.0 4 17 P5.0

VSS 5 16 P5.1

P4.3/AIN3 6 15 P5.2

P4.2/AIN2 7 14 P5.3/BZ1/PWM1

P4.1/AIN1 8 13 P5.4/BZ0/PWM0

P4.0/AIN0 9 12 P5.5

AVREFH 10 11 VDD

SN8P1703AP

SN8P1703AS

SN8P1703AX

MASK:

SN8A1703BS (SOP 20PIN) / SN8A1703BP (PDIP 20PIN) / SN8A1703BX (SSOP 20PIN)

P0.0/INT0 1 U 20 VDD

RST 2 19 XIN

P1.1 3 18 XOUT

P1.0 4 17 P5.0

VSS 5 16 P5.1

P4.3/AIN3 6 15 P5.2

P4.2/AIN2 7 14 P5.3/BZ1/PWM1

P4.1/AIN1 8 13 P5.4/BZ0/PWM0

P4.0/AIN0 9 12 P5.5

AVREFH 10 11 VDD

SN8A1703BP

SN8A1703BS

SN8A1703BX

SONiX TECHNOLOGY CO., LTD Page 10 Revision 0.8

Page 11

Preliminary SN8P1702A/SN8P1703A

8-bit micro-controller build-in 12-bit ADC

1.5 引脚说明

PIN 类型 说 明

VDD, VSS P 数字电路电源输入端

RST/VPP I

XIN, XOUT I, O 外部振荡器引脚(RC 模式中为 XIN.)

P0.0 / INT0 I P 0.0 / INT0 触发引脚 (施密特结构) ,内置上拉电阻

P1.0 ~ P1.1 I/O P1.0~P1.1 输入/输出引脚,内置上拉电阻

P4.0 ~ P4.3 I/O P4.0~P4.3 输入/输出引脚,内置上拉电阻

P5.0~P5.2, P5.5 I/O P5.0~P5.2, P5.5 输入/输出引脚,内置上拉电阻

P5.3 / BZ1 / PWM1 I/O P5.3 输入/输出引脚,Buzzer 或 PWM1 输出端,内置上拉电阻

P5.4 / BZ0 / PWM0 I/O P5.4 输入/输出引脚,Buzzer 或 PWM0 输出端,内置上拉电阻

AVREFH I A/D 转换模拟参考电压高电平输入端

AIN0 ~ AIN3 I A/D 转换输入通道

RST:系统复位输入端,施密特结构,低电平触发,通常保持高电平.

VPP:OTP ROM 编程引脚

表 1-3 引脚说明

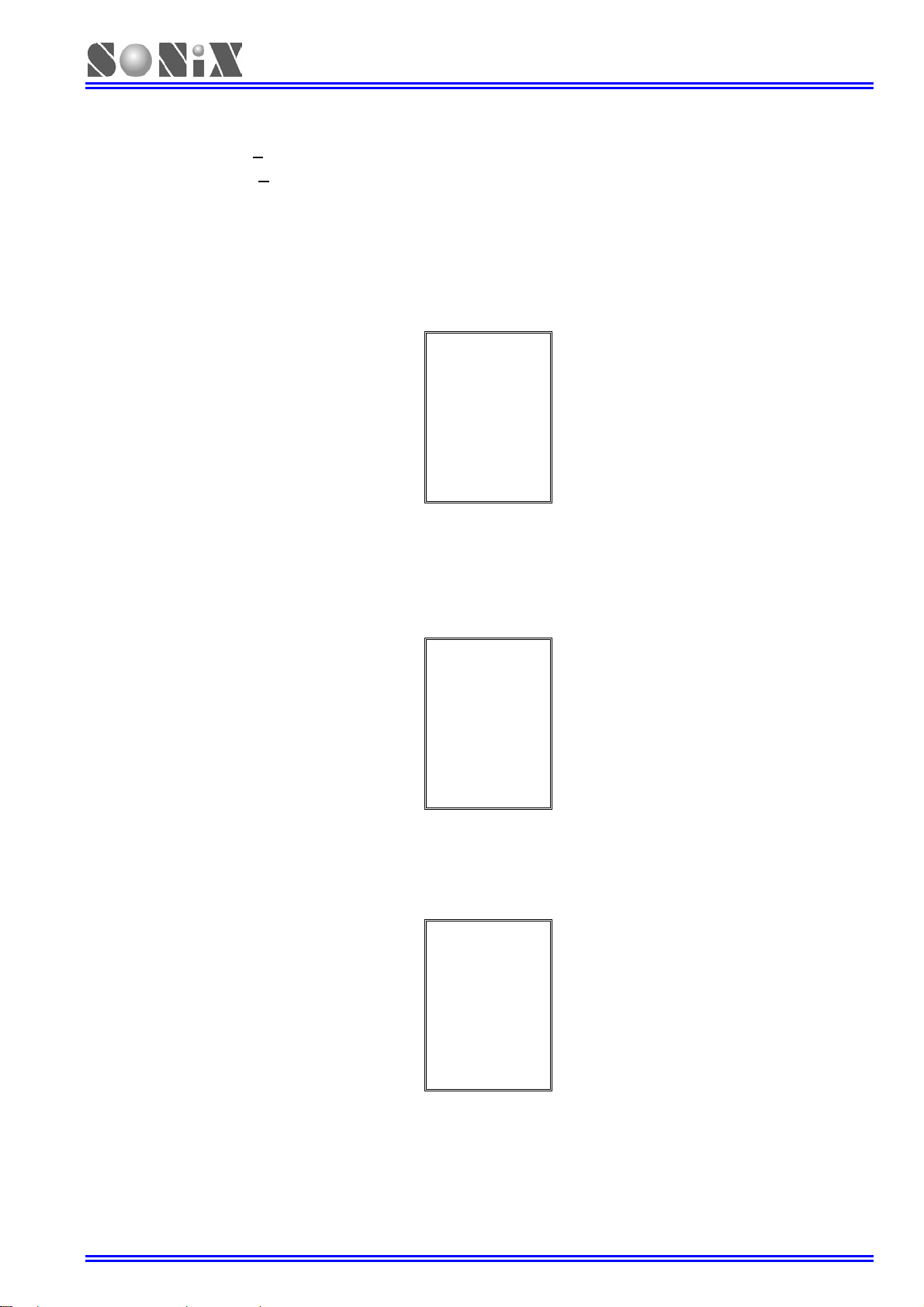

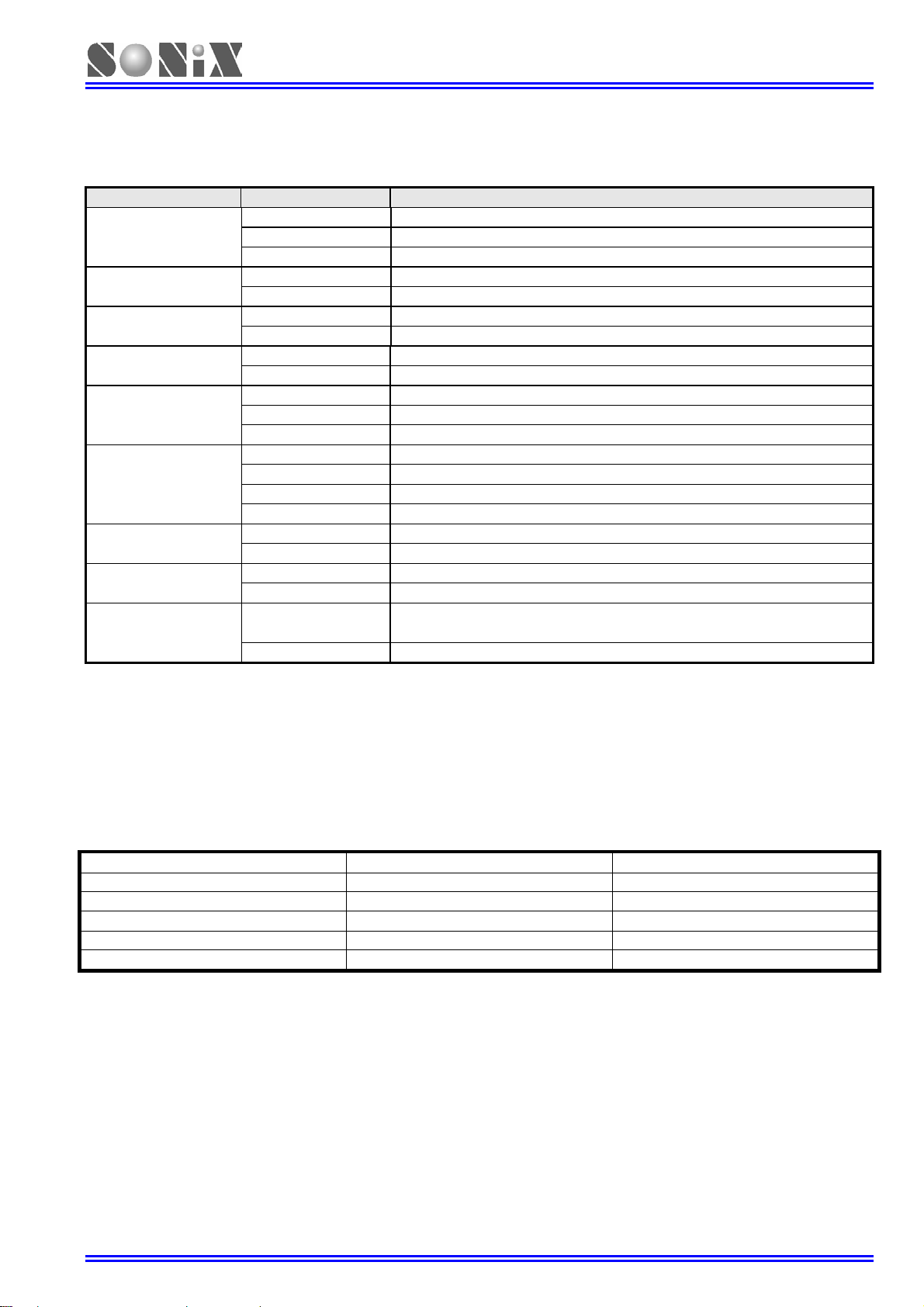

1.6 引脚电路图

Port0 structure

Port0 structure

PUR

PUR

Int. bus

Pin

Pin

¾ 注:所有锁存输出电路均为图腾柱结构

Int. bus

Port1, 4, 5 stru cture

Port1, 4, 5 stru cture

PnM

PnM

Pin

Pin

图 1-2 引脚电路图

PnM

PnM

PUR

PUR

PnM

PnM

Latch

Latch

Int. bus

Int. bus

SONiX TECHNOLOGY CO., LTD Page 11 Revision 0.8

Page 12

Preliminary SN8P1702A/SN8P1703A

8-bit micro-controller build-in 12-bit ADC

2 编译选项表(Code Option)

编译选项 内容 功 能 说 明

RC 外部高速时钟振荡器采用 RC 振荡电路

High_Clk

High_Clk / 2

Watch_dog

Security

TC0_Counter

TC1_Counter

Noise Filter

Low Power

INT_16K_RC

注:

¾ 在高干扰环境下,强烈建议使能“Noise Filter”选项;

¾ 如果使能“Noise Filter”选项,则编译器自动禁止“Low Power”选项;但若禁止“Noise Filter”选项,编译器则自动

使能“Low Power”选项;

¾ 除了低速模式的其它模式下,使能“Low Power”选项会减小工作电流;

¾ 如果在“High_Clk”选项中选择“RC”,编译器将强迫使能“High_Clk/2”选项。

典型工作电压和系统时钟频率(Fosc)的关系表:

系统时钟(Fosc) 使能 Noise/禁止 Low Power 禁止 Noise/使能 Low Power

2 MHz 2.2 2.2

4 MHz 2.3 2.5

8 MHz 2.4 3.0

12 MHz 2.9 3.7

16 MHz 3.4 4.5

上表仅作为设计参考,而不作任何保证。

12M X’tal 外部高速时钟振荡器采用高频晶体振荡器/陶瓷谐振器(如 12MHz)

4M X’tal 外部高速时钟振荡器采用标准晶体振荡器/陶瓷谐振器(如 3.58MHz)

Enable 外部高速时钟 2 分频, Fosc = 高速时钟 / 2

Disable Fosc = 高速时钟

Enable 使能看门狗定时器功能

Disable 禁止看门狗定时器功能

Enable 允许 ROM 程序代码加密

Disable 禁止 ROM 程序代码加密

8-bit TC0 作为 8 位计数器

6-bit TC0 作为 6 位计数器

4-bi TC0 作为 4 位计数器

8-bit TC1 作为 8 位计数器

6-bit TC1 作为 6 位计数器

5-bit TC1 作为 5 位计数器

4-bit TC1 作为 4 位计数器

Enable 使能噪音滤除功能以提高抗干扰性能

Disable 禁止噪音滤除功能

Enable 使能低功耗功能以节电

Disable 禁止低功耗功能

Always ON

By_CPUM 由 CPUM 寄存器控制内部 16K (3V) RC 时钟是否使能

表 2-1 SN8P1702A / SN8P1703A 的编译选项表

迫使看门狗定时器的时钟源来自 INT_16K_RC,则使看门狗定时器一直

处于使能状态(即使在省电模式和绿色模式下)。

SONiX TECHNOLOGY CO., LTD Page 12 Revision 0.8

Page 13

Preliminary SN8P1702A/SN8P1703A

8-bit micro-controller build-in 12-bit ADC

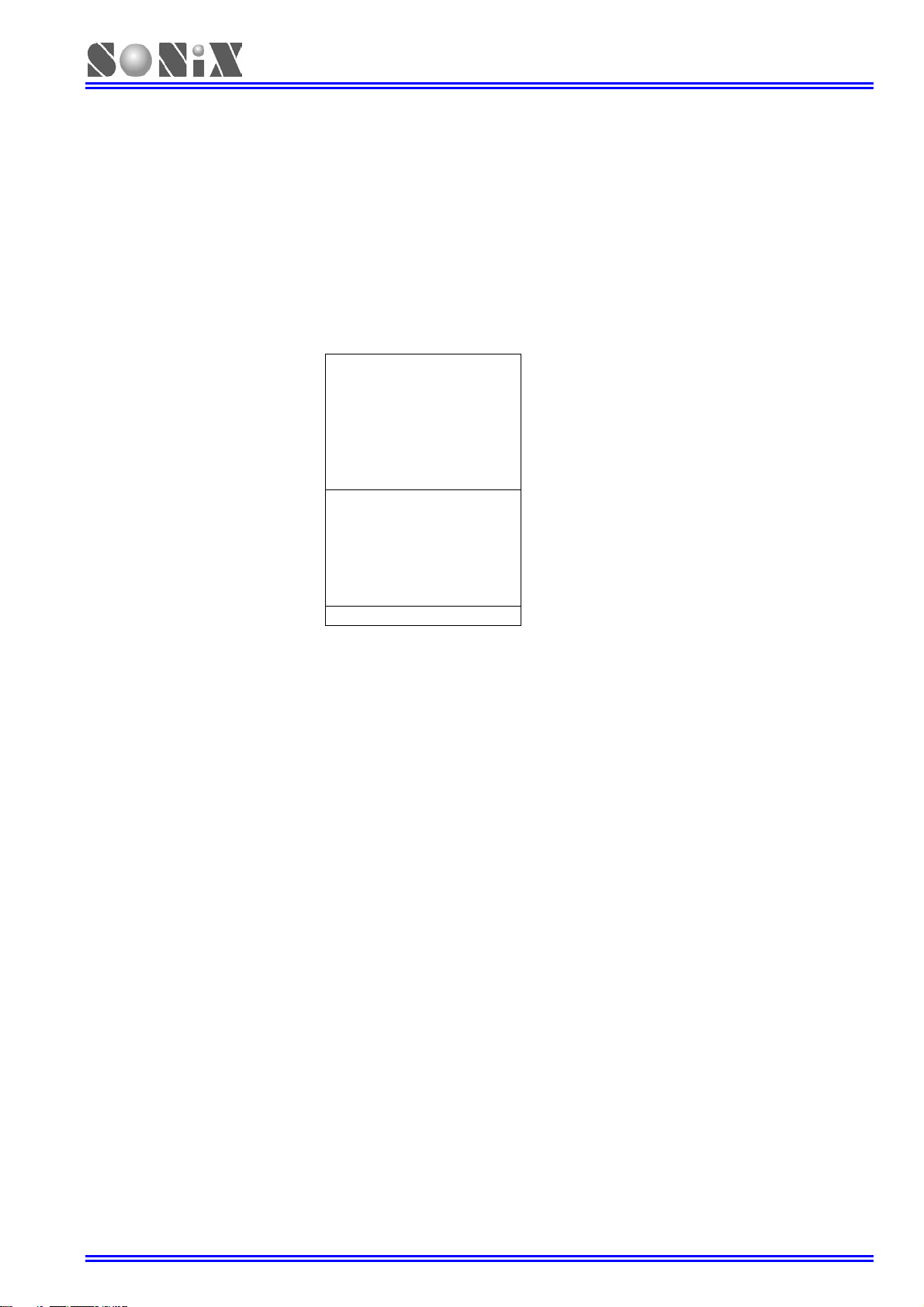

3 存储器

3.1 程序存储器(ROM)

3.1.1 概述

SN8P1702A / SN8P1703A 的程序存储器为 OTP ROM,其容量为 1K*16 位,可以由 12 位的程序计数器 PC 对

程序存储器进行寻址,或由专用寄存器(R、X、Y、Z)对 ROM 进行查表访问。在标准配置中,1024*16 位的程序

存储器分为 4 个区域:

¾ 1-word 的复位向量区

¾ 1-word 的中断向量区

¾ 5-word 的保留区

¾ 1K words (SN8P1702)

所有的程序存储器被分为 3 个代码区:0000H~0003H( 复位向量区) ,0004H~0007H( 系统保留区) ,

0008H~03FEH(中断向量区和通用存储区)。0008H 是中断向量的入口地址。

ROM

0000H 复位向量 程序开始

0001H 跳转到用户程序

0002H 跳转到用户程序

0003H

0004H

0005H

0006H

0007H

0008H 中断向量 中断入口地址

0009H 用户程序区

.

.

000FH

0010H

0011H

.

.

03FEH

03FFH 保留区

图 3-1 ROM 地址分配图

通用存储区

跳转到用户程序

保留区

通用存储区

程序结束

3.1.2 复位向量地址(0000H)

上电复位或看门狗溢出复位后,系统从地址 0000H 开始重新执行程序,所有的系统寄存器恢复为默认值。下面

的例子给出了如何在程序存储器里定义复位向量。

例: 上电复位,外部复位或看门狗定时器溢出复位:

CHIP SN8P1702A

ORG 0 ; 0000H

JMP START ;

. ; 0001H ~ 0007H 保留

ORG 10H

START: ; 0010H,

. ; 用户程序

.

ENDP ; 程序结束

SONiX TECHNOLOGY CO., LTD Page 13 Revision 0.8

跳转到用户程序区

用户程序的起始位置

Page 14

Preliminary SN8P1702A/SN8P1703A

8-bit micro-controller build-in 12-bit ADC

3.1.3 中断向量地址(0008H)

一旦有中断响应,程序计数器(PC)的值就会存入堆栈缓存器中并跳转至 0008H 处执行中断服务程序。用户使

用时必须自行定义中断向量。下面的例子给出了如何在程序中定义中断向量。

例 1: 下面的程序包括中断程序,主程序位于中断服务程序后。

CHIP SN8P1702A

ORG 0 ; 0000H

JMP START ; 跳转到用户程序

. ; 0004H ~ 0007H 保留

ORG 8 ;中断服务程序

B0XCH A, ACCBUF ;B0XCH 不会影响到 C, Z

B0MOV A, PFLAG

B0MOV PFLAGBUF, A ; 保存 PFLAG 寄存器

.

B0MOV A, PFLAGBUF

B0MOV PFLAG, A ; 恢复 PFLAG 寄存器

B0XCH A, ACCBUF ; B0XCH 不影响 C,Z

RETI ; 中断返回

START: ; 用户程序起始地址

. ; 用户程序

.

JMP START ; 用户程序结束

ENDP ; 程序结束

例 2:下面的程序包括中断服务程序,中断服务程序的入口在通用程序存储区的指定地址

CHIP SN8P1702A

ORG 0 ; 0000H

JMP START ; 跳转到用户程序.

. ; 0004H ~ 0007H 保留

ORG 08

JMP MY_IRQ ; 0008H, 跳转到中断服务程序

ORG 10H

START: ; 0010H, 用户程序起始地址

. ; 用户程序

.

JMP START ; 用户程序结束

MY_IRQ: ; 中断服务程序的起始地址

B0XCH A, ACCBUF ; B0XCH 不会影响到 C, Z

B0MOV A, PFLAG

B0MOV PFLAGBUF, A ; 保存 PFLAG 寄存器

.

B0MOV A, PFLAGBUF

B0MOV PFLAG, A ; 恢复 PFLAG 寄存器

B0XCH A, ACCBUF ; B0XCH 不会影响到 C, Z

RETI ; 中断返回

ENDP ; 程序结束

¾ 注:从上面的程序中很容易的可以得出 SONIX 的主要编程规则,有以下几点:

1. 地址 0000H 处的“JMP”指令使程序跳转至通用 ROM 区,0004H~0007H 由系统保留,用户必须跳过

0004H~0007H;

2. 中断服务从 0008H 开始,用户可以将中断子程序的入口地址放在 0008H(例 1)或者在 0008H 写入一个

跳转指令(例 2),而将整个中断子程序位于通用 ROM 区,从而形成模块化编程风格

SONiX TECHNOLOGY CO., LTD Page 14 Revision 0.8

Page 15

Preliminary SN8P1702A/SN8P1703A

V

V

V

M

Y

Z

@@

_

C

T

D

V

C

_

S

Z

@

_

Y

V

S

V

2

S

Y

_END

_

V

S

T

V

S

T

S

Z

S

Z

S

Z

S

Z

T

_

S

@

_

_

8-bit micro-controller build-in 12-bit ADC

3.1.4 CHECKSUM 计算

ROM 中的 0004H~0007H 和最后的一个地址是系统保留区,用户应该在计算 Checksum 时跳过这一区域。

例:下面的程序给出了在计算 Checksum 时如何跳过保留区。

MO

B0MO

MO

B0MOV END_ADDR2,A ; 保存结束地址的高字节

CLR Y ; 清

CLR

:

CALL YZ

MOV

B0BSE

AD

MO

AD

JMP END

AAA:

INCM

JMP

JMP Y

END_CHECK:

MO

CMPR

JMP AAA ; 不是则继续计算

MO

CMPR

JMP AAA ; 检查

JMP CHECKSUM

YZ

CHECK: ; 是则结束计算

MO

CMPR

RE

MO

CMPR

RE

INCM

INCM

INCM

INCM

RE

Y

ADD_1:

INCM

NOP

JMP

CHECKSUM

……….

……….

END

USER_CODE: ; 程序结束

END:

; 不是 0004H 则返回继续计算

; 不是 0004H 则返回继续计算

;

A,#END_USER_CODE$L

END_ADDR1,A ; 保存结束地址的低字节

A,#END_USER_CODE$

寄存器

; 清 Z 寄存器

CHECK ; 调用函数,判断YZ 的值

;

FC ; 清进位标志 C

DATA1,A ;

A,R

DATA2,A ;

CHECK ; 检查YZ 的值是否指向结束地址

; 递增 Z

B ;Z不为 0,继续计算

ADD_1 ;Z=0,调整

A,END_ADDR1

A,Z ; 检查Y是否等于结束地址的高字节

A,END_ADDR

A,Y ; 检查是否到 0004H 位置

A,#04H

A,Z ;

A,#00H

A,Y ;

; 是到 0004H 位置则 Z 加 4,跳过 0004H-0007H

Y ; 递增Y,继续计算

B ; 跳转到 CHECKSUM 计算

; 是则结束计算

是否等于结束地址的高字节

; 不是则继续计算

3.1.5 通用程序存储区

位于 ROM 中 0010H~0FEFH 的 992 字作为通用程序存储区,这一区域主要用来存储指令的操作代码和查表数

据。SN8P1702A/SN8P1703A 中包括用程序计数器 PC 实现的跳转表程序和通过寄存器(R、X、Y、Z)实现的查

表程序。

在对程序计数器进行操作导致 PCL 溢出时,PCH 不会自动加 1,因此在跳转表程序和查表程序中,计数器不会

自动跳过边界,当 PCL 发生溢位(从 0FFH 增至 000H)时,用户必须自行将 PCH 调整为 PCH+1。

SONiX TECHNOLOGY CO., LTD Page 15 Revision 0.8

Page 16

Preliminary SN8P1702A/SN8P1703A

@

Y

@@

_

@

@@

Y

8-bit micro-controller build-in 12-bit ADC

3.1.6 查表功能

在 ROM 的查表功能程序中,X 寄存器指向数据 ROM 地址的高 8 位,Y 寄存器指向地址的中间 8 位,Z 寄存器

指向低 8 位地址,执行 MOVC 指令后,数据的低字节存入累加器 ACC 中,而数据的高字节存入 R 寄存器中。

例:查找位于 “table_1”的 ROM 数据.

B0MOV Y, #TABLE1$M ; 取得表格地址高字节

B0MOV Z, #TABLE1$L ; 取得表格地址低字节

MOVC ; 查表, R = 00H, ACC = 35H

;

; 索引地址加 1

INCMS Z ; Z+1

JMP

INCMS

NOP ;

;

: MOVC ; 查表, R = 51H, ACC = 05H.

. . ;

TABLE1: DW 0035H ; 定义表格数据

DW 5105H ; “

DW 2012H ; “

¾ 注:当 Z 寄存器从 0XFFH 增至 0X00H 跨越页边界时,Y 寄存器不会自动增加。所以用户必须注意处理这种情

况,避免查表错误。如果 Z 寄存器发生溢出,Y 寄存器必须增 1。下面给出的宏指令 INC_YZ 提供了解决此问

题的方法 。

¾ 注:因为程序计数器 PC 只有 12 位,X 寄存器在查表的时候实际是没有用处的,用户可以省略“B0MOV X,

#TABLE1$H”。SONiX ICE 能够支持更大的程序寻址能力,所以必须保证 X 寄存器为 0,以避免查表中出现不

可预知的错误。

例: 宏指令 INC_YZ

INC

YZ MACRO

INCMS Z ; Z+1

JMP

INCMS Y ; Y+1

NOP ; Y 无溢出

:

ENDM

另一种编译风格的查表是通过累加器增加间接寄存器 Y 和 Z,但要注意是否有进位发生。下面的例子给出了详

细操作步骤:

例: 执行指令 B0ADD/ADD 增加 Y、Z

B0MOV Y, #TABLE1$M ; 取得表格地址高字节

B0MOV Z, #TABLE1$L ; 取得表格地址低字节

B0MOV A, BUF ; Z = Z + BUF

B0ADD Z, A

B0BTS1 FC ; 检查进位标志 C

JMP GETDATA ; FC = 0

INCMS

NOP

GETDATA:

MOVC ; 查表,若 BUF = 0,结果是 0x0035

; 若 BUF = 1,结果是 0x5105

; 若 BUF = 2, 结果是 0x2012

. .

TABLE1: DW 0035H ; 定义一个 WORD 的表格数据

DW 5105H

DW 2012H

F ; 无进位

; Z 溢出(FFH Æ 00)则, Æ Y=Y+1

F ; Z 无溢出

; FC = 1. Y+1.

SONiX TECHNOLOGY CO., LTD Page 16 Revision 0.8

Page 17

Preliminary SN8P1702A/SN8P1703A

A

A

A

A

A

A

A

A

A

A

@

((

)

($ |

)

($ |

)

A

A

A

@

A

A

A

A

A

8-bit micro-controller build-in 12-bit ADC

3.1.7 跳转表

跳转表操作可以完成多个地址跳转功能,将程序计数器的低字节 PCL 与累加器 ACC 相加从而得到一个指向新

的跳转地址的程序计数器值,这种方法可以方便多个任务的处理。

执行“ADD PCL, A”如果有进位发生,结果并不会影响 PCH 寄存器。用户必须检查跳转表是否跨越了 ROM 的

页边界。如果跳转表跨越了 ROM 页边界(例如从 XXFFH 到 XX00H),将跳转表移动到下一页程序存储区的顶部

(XX00H)。注:一页包含 256words。

例:设 PC = 0323H (PCH = 03H、PCL = 23H)

ORG 0X0100 ; 跳转表最好放在 ROM 的边界位置

B0ADD PCL,

JMP

JMP

JMP

JMP

在下面的例子中,跳转表格从 0x00FD 开始,执行“B0ADD PCL A”时,如果 ACC = 0 或 1,跳转表格指

向正确的地址,但如果 ACC 大于 1,因为 PCH 不能自动加 1,程序就会出错:可以看到当 ACC=2 时,PCL=0,

而 PCH 仍然保持为 0,则新的程序计数器 PC 将指向错误的地址 0x0000,程序失效。因此,检查跳转表格是否跨

越边界(xxFFH 到 xx00H)非常重要。良好的编译风格是将跳转表格放在 ROM 的开始边界(如 0100H)。

例:如果跳转表格跨越 ROM 边界,将引起程序错误:

ROM Address

. .

0X00FD B0ADD PCL,

0X00FE JMP

0X00FF JMP

0X0100 JMP

0X0101 JMP

. .

. .

SONIX 提供了一条宏指令以保证安全的跳转表操作,这条宏指令会检查 ROM 的边界,并自动将跳转表移动到

正确的位置。但宏指令会占用 ROM 的存储空间。

JMP_A MACRO VAL

IF

JMP

ORG

ENDIF

ENDM

¾ “VAL”为跳转列表的个数

例: “@JMP_A” 在 SONIX 的宏文件中称为“MACRO3.H”.

B0MOV

JMP

JMP

JMP

JMP

JMP

. .

如果跳转表格的位置是从 00FDH 到 0101H, 那么宏指令“@JMP_A” 将使跳转表格从 0100h 开始。

DD PCL,

JMP_A 5 ; 要跳转的总的地址数是 5.

0POINT ; ACC = 0

1POINT ; ACC = 1

2POINT ; ACC = 2 Å跳转表跨越边界

3POINT ; ACC = 3

, BUF0 ; “BUF0” 的值为 0-4

0POINT ; ACC = 0,跳转到A0POINT

1POINT ; ACC = 1,跳转到A1POINT

2POINT ; ACC = 2,跳转到A2POINT

3POINT ; ACC = 3,跳转到A3POINT

4POINT ; ACC = 4,跳转到A4POINT

0POINT ; ACC = 0,跳转到A0POINT

1POINT ; ACC = 1,跳转到A1POINT

2POINT ; ACC = 2,跳转到A2POINT

3POINT ; ACC = 3,跳转到A3POINT

; PCL = PCL + ACC,PCH 的值不能改变

$+1) !& 0XFF00) !!= (($+(VAL)) !& 0XFF00

0XFF

0XFF

; PCL = PCL + ACC,但 PCH 不会改变

SONiX TECHNOLOGY CO., LTD Page 17 Revision 0.8

Page 18

Preliminary SN8P1702A/SN8P1703A

8-bit micro-controller build-in 12-bit ADC

3.2 数据存储器(RAM)

3.2.1 概述

SN8P1702A / SN8P1703A 有 256 字节内置数据存储器用来存储用户数据。

¾ 128 * 8 位数据存储器(bank 0)

¾ 128 * 8 位系统专用寄存器

该存储器分为 bank0 和 bank1 两页,用户可通过 RBANK 寄存器的页选择位访问两个 RAM 页中的所有数据单元。

在 bank 0 中,前面的 128 字节作为用户通用区,剩下的 128 字节就作为系统寄存器。

RAM

000h Bank0 的 000h~07Fh 是数据存储区(128 bytes)

“

“

“

“

“

BANK 0

¾ 注:执行读指令“MOV A, M”后,系统寄存器中未定义的区域置为逻辑“high”。

07Fh

080h Bank0 的 80h~FFh 是系统寄存器区共 128 bytes.

“

“

“

“

“

0FFh 系统保留

用户存储区

系统寄存器

图 3-2 RAM 分配图

SONiX TECHNOLOGY CO., LTD Page 18 Revision 0.8

Page 19

Preliminary SN8P1702A/SN8P1703A

Y

A, @

A

A

A

A

_YZ_

@

–

_YZ_

@

_

8-bit micro-controller build-in 12-bit ADC

3.2.2 工作寄存器

RAM bank0 中 82H~84H 是系统专用寄存器,如 R、Y 和 Z 寄存器,如下表所示。这些寄存器可用作一般的工

作缓冲器或用来访问 ROM 和 RAM 中的数据。例如,所有的 ROM 列表可以通过 R、Y、Z 查找,RAM 可由 Y 和 Z

寄存器间接寻址。

3.2.2.1 Y,Z 寄存器

8 位寄存器 Y 和 Z 主要用作系统专用寄存器 Y 和 Z,@YZ 间接寻址和查表寻址寄存器。

Y 初始值=0000 0000

084H Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

YBIT7 YBIT6 YBIT5 YBIT4 YBIT3 YBIT2 YBIT1 YBIT0

R/W R/W R/W R/W R/W R/W R/W R/W

Z 初始值=0000 0000

083H Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Z ZBIT7 ZBIT6 ZBIT5 ZBIT4 ZBIT3 ZBIT2 ZBIT1 ZBIT0

R/W R/W R/W R/W R/W R/W R/W R/W

间接寻址寄存器@YZ 位于 RAM bank0 中 E7H 单元,通过 Y 和 Z 寄存器的内容访问 RAM 数据,并可通过 ACC

对该数据进行读/写。Y 寄存器的低 4 位决定了数据的 RAM 页数,Z 寄存器给出其具体地址。 Y 的高 4 位在 RAM

间接寻址模式中是无效的。

例: 间接寻址访问 RAM bank 1 的 25H 单元

B0MOV Y, #01H ; 把 BANK0 的 RAM 高 8Bit 地址送到 Y 寄存器

B0MOV Z, #25H ; 把 BANK0 的 RAM 底 8Bit 地址送到 Z 寄存器

B0MOV

例: 用@YZ 对 RAM bank 1 清零

MOV

B0MOV Y,

MOV

B0MOV Z,

CLR

CLR

DECMS Z ; Y

JMP CLR

CLR

END

¾ 注:关于 Y, Z 寄存器的查表应用请参考“查表程序说明”

BUF:

CLR: ; 结束通用区所有存储器的清零程序

3.2.2.2 R 寄存器

寄存器 R 是一个 8 位缓存器,可作为工作寄存器或在查找 ROM 数据时存放数据的高字节。执行 MOVC 指令后,

ROM 数据的高字节存入 R 寄存器中,低字节存入累加器 ACC 中。

R 初始值=0000 0000

082H Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

R RBIT7 RBIT6 RBIT5 RBIT4 RBIT3 RBIT2 RBIT1 RBIT0

R/W R/W R/W R/W R/W R/W R/W R/W

¾ 注:关于 R 寄存器的查表应用请参考“查表程序说明”

82H 83H 84H

RAM R Z Y

R/W R/W R/W

YZ ; 读上面地址对应储存器的值到ACC

, #1

; Y = 1, bank 1

, #07FH

; Y = 7FH,数据存储器的低地址

YZ ; 清零

1,Y= 0 结束子程序

BUF ; 不为零继续计算

YZ

SONiX TECHNOLOGY CO., LTD Page 19 Revision 0.8

Page 20

Preliminary SN8P1702A/SN8P1703A

8-bit micro-controller build-in 12-bit ADC

3.2.3 程序状态字

程序状态字 PFLAG 包括进位标志(C),辅助进位标志(DC)和零标志(Z),如果运算结果为零或者有进位、借位发

生,将影响 PFLAG 寄存器。

PFLAG 初始值=xxxx x000

086H Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

PFLAG - - - - - C DC Z

- - - - - R/W R/W R/W

3.2.3.1 进位标志

C = 1:执行算术加法后有进位发生,执行算术减法后没有借位或移位指令后移出逻辑“1”

C = 0:执行算术加法后没有进位发生,执行算术减法后有借位或移位指令后移出逻辑“0”

3.2.3.2 辅助进位标志

DC = 1:执行算术加法操作产生由低字节向高字节的进位或执行算术减法操作没有从高字节借位

DC = 0:执行算术加法操作没有产生由低字节向高字节的进位或执行算术减法操作从高字节借位

3.2.3.3 零标志

Z = 1: 指令执行后,ACC 的结果为零

Z = 0: 指令执行后,ACC 的结果非零

SONiX TECHNOLOGY CO., LTD Page 20 Revision 0.8

Page 21

Preliminary SN8P1702A/SN8P1703A

8-bit micro-controller build-in 12-bit ADC

3.3 累加器(ACC)

累加器 ACC 是一个 8 位专用数据寄存器,用来进行算术逻辑运算或数据存储器之间数据的传送和处理。如果对

ACC 的操作结果为零(Z)或者有进位产生(C 或 DC),那么这些标志将会影响 PFLAG 寄存器。

由于 ACC 不在数据存储器(RAM)中,所以执行“B0MOV”指令不能够访问 ACC,必须通过“MOV”指令

对 ACC 进行读/写。

例: 读/写 ACC 中数据

; 读取 ACC 中的数据并存在 BUF 中

MOV BUF, A

. .

; 写入一个立即数到 ACC 中

MOV A, #0FH

. .

; 读取 BUF 中的数据存在 ACC 中

MOV A, BUF

. .

中断发生时,系统不会自动保存 ACC 和 PFLAG 的值。一旦中断发生,必须把 ACC 存储在用户自定义的存储

器中,如下所示:

例:保护 ACC 和工作寄存器

ACCBUF EQU 00H ; ACCBUF 用来保存 ACC 的数据

INT_SERVICE:

B0XCH A, ACCBUF ; B0XCH 不影响标志位 C,Z

B0XCH A, ACCBUF ; 保存 ACC 的值

B0MOV A, PFLAG ; 保存 PFLAG 的值

B0MOV PFLAGBUF,A

.

B0MOV A, PFLAGBUF ; 恢复 PFLAG 的值

B0MOV PFLAG,A

B0XCH A, ACCBUF ; 恢复 ACC 的值

B0XCH A, ACCBUF ; 恢复 ACC 的值

RETI ; 退出中断服务程序

¾ 注:为了保护和恢复 ACC,必须使用指令“B0XCH”,否则 ACC 会影响 PLAGE。

SONiX TECHNOLOGY CO., LTD Page 21 Revision 0.8

Page 22

Preliminary SN8P1702A/SN8P1703A

8-bit micro-controller build-in 12-bit ADC

3.4 堆栈

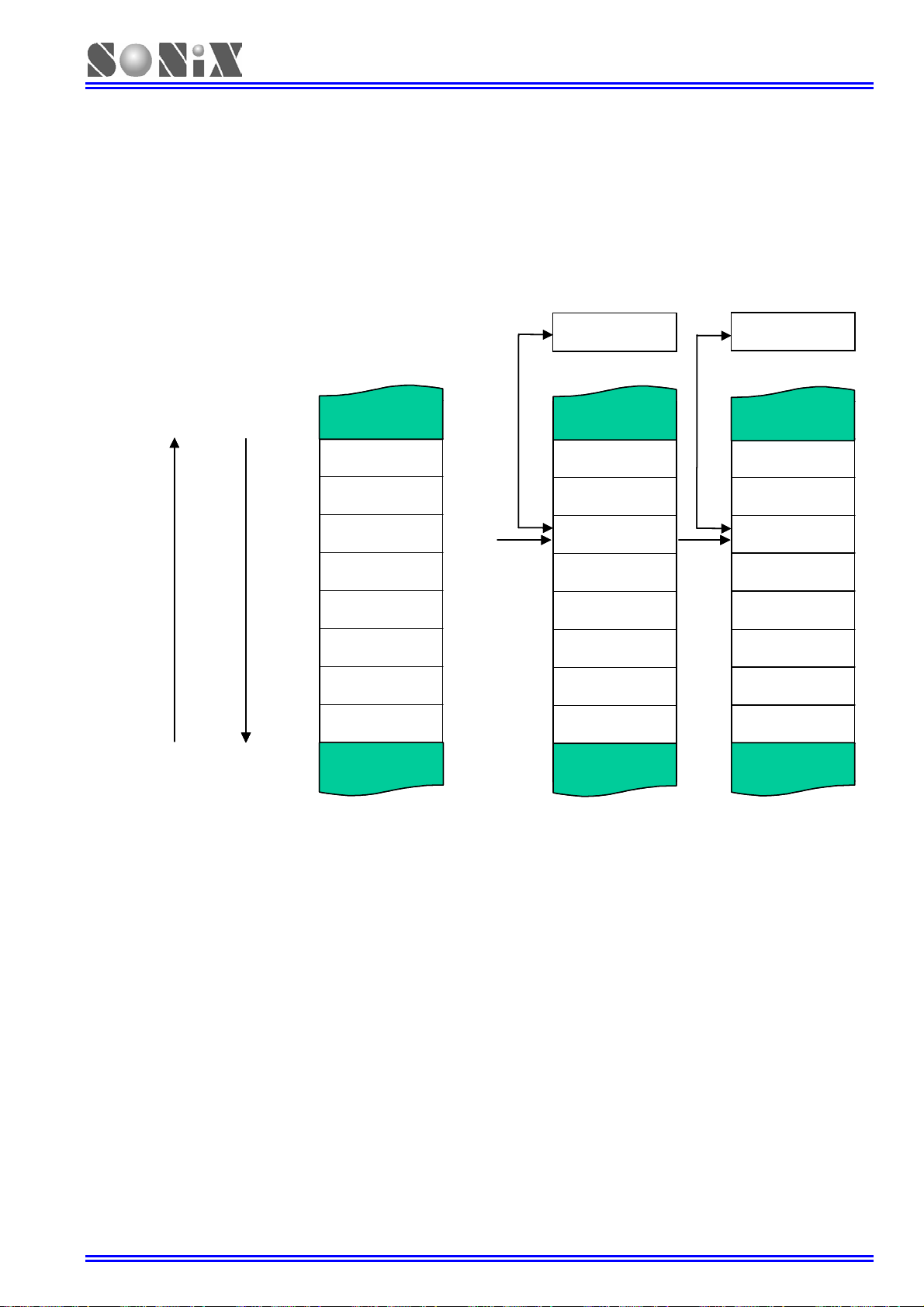

3.4.1 概述

SN8P1702A /SN8P1703A 共有 8 层堆栈,每层 12 位。堆栈缓冲器在中断现场保护和恢复时存放程序计数器 PC。

堆栈指针 STKP 指示当前栈顶位置以便保护和恢复数据,12 位的寄存器 STKnH 和 STKnL 存放程序计数器 PC 的数

据。

STACK BUFFER

STACK BUFFER

PCL

PCL

PCLPCL

STK0L

STK0L

STK0L

STK1L

STK1L

STK1L

RET /

RET /

RETI

RETI

CALL /

CALL /

interrupt

interrupt

STKP = 7

STKP = 7

STKP = 7

STKP = 6

STKP = 6

STKP = 6

PCH

PCH

PCHPCH

STK0H

STK0H

STK0H

STK1H

STK1H

STK1H

STKP + 1

STKP + 1

STKP + 1

STKP - 1

STKP - 1

STKP - 1STKP - 1

STKP = 5

STKP = 5

STKP = 5

STKP = 4

STKP = 4

STKP = 4

STKP = 3

STKP = 3

STKP = 3

STKP = 2

STKP = 2

STKP = 2

STKP = 1

STKP = 1

STKP = 1

STKP = 0

STKP = 0

STKP = 0

STKP

STKPSTKP

STK2H

STK2H

STK2H

STK3H

STK3H

STK3H

STK4H

STK4H

STK4H

STK5H

STK5H

STK5H

STK6H

STK6H

STK6H

STK7H

STK7H

STK7H

图 3-3 堆栈保护和堆栈恢复示意图

STKP

STKPSTKP

STK2L

STK2L

STK2L

STK3L

STK3L

STK3L

STK4L

STK4L

STK4L

STK5L

STK5L

STK5L

STK6L

STK6L

STK6L

STK7L

STK7L

STK7L

SONiX TECHNOLOGY CO., LTD Page 22 Revision 0.8

Page 23

Preliminary SN8P1702A/SN8P1703A

8-bit micro-controller build-in 12-bit ADC

3.4.2 堆栈寄存器

堆栈指针(STKP)是一个 4 位的专用寄存器,用来指示堆栈栈顶位置,12 位的数据存储器(STKnH 和 STKnL)

用来存储程序计数器(PC)的值。

堆栈操作有两种:入栈(Stack-Save)和出栈(Stack-Restore)。执行 Stack-Save 操作,STKP 自动减量;执

行 Stack-Restore 操作,STKP 自动增量。这样,STKP 总是指向栈顶位置。

执行 CALL 指令和响应中断时,程序计数器(PC)的值会被保存在堆栈中,堆栈操作遵循先进后出的原则。堆

栈指针寄存器(STKP)和缓冲器 STKnH、STKnL 位于 BANK0。

STKP(堆栈指针)初始值=0xxx 1111

0DFH Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

STKP GIE - - - STKPB3 STKPB2 STKPB1 STKPB0

R/W - - - R/W R/W R/W R/W

STKBn:堆栈指针。(n = 0~3)

GIE:全局中断控制位。0 = 禁止,1 = 使能。详见中断章节。

例:堆栈指针(STKP)复位。

MOV A, #00001111B

B0MOV STKP, A

STKn(堆栈缓冲器)初始值=xxxx xxxx xxxx xxxx, STKn = STKnH + STKnL (n = 7~0)

0F0H~0FFH Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

STKnH - - - - SnPC11 SnPC10 SnPC9 SnPC8

- - - - R/W R/W R/W R/W

0F0H~0FFH Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

STKnL SnPC7 SnPC6 SnPC5 SnPC4 SnPC3 SnPC2 SnPC1 SnPC0

R/W R/W R/W R/W R/W R/W R/W R/W

STKnH:在执行中断或 CALL 指令时存储 PCH 的数据。n:8 ~11.

STKnL:在执行中断或 CALL 指令时存储 PCH 的数据。n:0 ~7.

SONiX TECHNOLOGY CO., LTD Page 23 Revision 0.8

Page 24

Preliminary SN8P1702A/SN8P1703A

8-bit micro-controller build-in 12-bit ADC

3.4.3 堆栈操作举例

程序调用指令(CALL)和中断都涉及到对堆栈指针 STKP 的操作和将程序计数器 PC 保存在堆栈缓冲区。在两

种操作中,堆栈指针 STKP 都会减 1 并指向下一个可用的堆栈区域,堆栈缓存器中则保存了程序指针。入栈保护操

作如下表所示:

堆栈层数

0 1 1 1 1 STK0H STK0L -

1 1 1 1 0 STK1H STK1L -

2 1 1 0 1 STK2H STK2L -

3 1 1 0 0 STK3H STK3L -

4 1 0 1 1 STK4H STK4L -

5 1 0 1 0 STK5H STK5L -

6 1 0 0 1 STK6H STK6L -

7 1 0 0 0 STK7H STK7L -

>8 - - - - - - 堆栈溢出

对应每个入栈操作,都有一个出栈操作来恢复程序计数器 PC 的值。RETI 指令用于中断服务程序中,RET 用于

子程序调用。出栈时,STKP 加 1 并指向下一个空闲堆栈缓存器。堆栈恢复操作如下表所示:

堆栈层数

7 1 0 0 0 STK7H STK7L -

6 1 0 0 1 STK6H STK6L -

5 1 0 1 0 STK5H STK5L -

4 1 0 1 1 STK4H STK4L -

3 1 1 0 0 STK3H STK3L -

2 1 1 0 1 STK2H STK2L -

1 1 1 1 0 STK1H STK1L -

0 1 1 1 1 STK0H STK0L -

STKPB3 STKPB2 STKPB1 STKPB0 高字节 低字节

STKPB3 STKPB2 STKPB1 STKPB0 高字节 低字节

STKP 堆栈缓冲器

表 3-1 STKP, STKnH 和 STKnL 在堆栈保护中的关系

STKP

表 3-2 STKP, STKnH 和 STKnL 在堆栈恢复中的关系

堆栈缓冲器

说 明

说明

SONiX TECHNOLOGY CO., LTD Page 24 Revision 0.8

Page 25

Preliminary SN8P1702A/SN8P1703A

8-bit micro-controller build-in 12-bit ADC

3.5 程序计数器(PC)

程序计数器 PC 是一个 12 位专用二进制计数器,由 4 位高字节和 8 位低字节组成,PC 总是指向下一条将要访

问指令的地址,一般在程序执行过程中,PC 会随着指令的执行自动增量。

PC 初始值=xxxx 0000 0000 0000

Bit 15 Bit 14 Bit 13 Bit 12 Bit 11 Bit 10 Bit 9 Bit 8 Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

PC - - - - 0 0 0 0 0 0 0 0 0 0 0 0

PCH PCL

PCH 初始值=xxxx 0000

0CFH Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

PCH - - - - PC11 PC10 PC9 PC8

- - - - R/W R/W R/W R/W

PCL 初始值=0000 0000

0CEH Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

PCL PC7 PC6 PC5 PC4 PC3 PC2 PC1 PC0

R/W R/W R/W R/W R/W R/W R/W R/W

3.5.1 单地址跳转

单地址跳转指令共有 9 条:CMPRS、INCS、INCMS、DECS、DECMS、BTS0、BTS1、B0BTS0、B0BTS1。

如果指令的结果相匹配,PC 加 2,跳过当前指令的下一条指令。

如果位测试结果匹配,那么 PC 加 2,跳过当前指令的下一条指令

B0BTS1 FC ; 如果 C=1 则跳过下一条指令

JMP C0STEP ; 否则跳转到 C0STEP.

.

C0STEP: NOP

B0MOV A, BUF0 ; 把 BUF0 的值赋给 ACC.

B0BTS0 FZ ; 如果 Z=0,则跳过下一条指令

JMP C1STEP ; 否则跳到 C1STEP.

.

C1STEP: NOP

如果 ACC 与立即数或内存中的内容相等,那么 PC 加 2,跳过当前指令的下一条指令

CMPRS A, #12H ; 如果 ACC = 12H. 则跳过下一条指令

JMP C0STEP ; 否则跳到 C0STEP.

.

C0STEP: NOP

如果加 1(INCS、INCMS)/减 1(DECS、DECMS)后的结果为 0x00H/0xffH,那么 PC 加 2 跳过当前指令的

下一条指令。

INCS:

INCS BUF0 ; 如果 BUF0 = 0X00H,则跳过下一条指令

JMP C0STEP ; 否则跳到 C0STEP.

.

C0STEP: NOP

INCMS:

INCMS BUF0 ; 如果 BUF0 = 0X00H,则跳过下一条指令

JMP C0STEP ; 否则跳到 C0STEP.

…

C0STEP: NOP

DECS:

DECS BUF0 ; 如果 BUF0 = 0XFFH,则跳过下一条指令

JMP C0STEP ; 否则跳到 C0STEP.

.

C0STEP: NOP

DECMS:

DECMS BUF0 ; 如果 BUF0 = 0XFFH,则跳过下一条指令

JMP C0STEP ; 否则跳到 C0STEP.

…

C0STEP: NOP

:

SONiX TECHNOLOGY CO., LTD Page 25 Revision 0.8

Page 26

Preliminary SN8P1702A/SN8P1703A

8-bit micro-controller build-in 12-bit ADC

3.5.2 多地址跳转

用户可以通过 JMP 和“ ADD PCL,A ”指令实现多地址跳转。 “ADD PCL, A”执行后若有进位发生,进位标志

并不会影响 PCH 寄存器。

例: 设 PC = 0323H (PCH = 03H、PCL = 23H)

; PC = 0323H

MOV A, #28H

B0MOV PCL, A ; 跳到地址 0328H

. .

. .

; PC = 0328H . .

MOV A, #00H

B0MOV PCL, A ; 跳到地址 0300H

例:设 PC = 0323H (PCH = 03H、PCL = 23H)

; PC = 0323H

B0ADD PCL, A ; PCL = PCL + ACC,PCH 的值不变

JMP A0POINT ; ACC = 0,跳到 A0POINT

JMP A1POINT ; ACC = 1,跳到 A1POINT

JMP A2POINT ; ACC = 2,跳到 A2POINT

JMP A3POINT ; ACC = 3,跳到 A3POINT

. . ;

SONiX TECHNOLOGY CO., LTD Page 26 Revision 0.8

Page 27

Preliminary SN8P1702A/SN8P1703A

A

A

8-bit micro-controller build-in 12-bit ADC

4 寻址模式

4.1 概述

SN8P1702A / SN8P1703A 提供了三种 RAM 寻址方式:立即寻址、直接寻址和间接寻址。这 3 种不同寻址模式

的用途将在下面一一描述。

4.2 立即寻址

将一个立即数送入累加器或指定的 RAM 单元:MOV A, # I ; B0MOV M, # I

立即寻址模式

MOV A, #12H ; 立即数 12H 存入 ACC

4.3 直接寻址

通过单元地址访问存储区:MOV A, 12H ; MOV 12H, A

直接寻址模式

B0MOV A, 12H ; bank 0 中 12H 的数据送入 ACC

4.4 间接寻址

目的单元地址存放在指针寄存器(Y/Z)中,利用 MOV/B0MOV 指令在 ACC 和寄存器@YZ 之间读/写数据:

MOV A, @YZ ; MOV @YZ, A

例: 对@YZ 间接寻址:

CLR Y ; 清 Y,指向 RAM bank 0.

B0MOV Z, #12H ; 送一个立即数 12H 到 Z

B0MOV A, @YZ ; 用数据指针 @YZ 取得相应存储器的地址 012H 的数据送给

4.5 寻址 RAM BANK0

RAM bank 0 的数据都可以通过这三种寻址方式进行读/写。

例 1: 立即数寻址(例如 B0xxx 指令)

B0MOV A, 12H ; 赋一个立即数 12H(bank 0)到 ACC

例 2: @YZ 间接寻址

CLR Y ; 清 Y,指向 RAM bank 0.

B0MOV Z, #12H ; 送一个立即数 12H 到 Z

B0MOV A, @YZ ; 用数据指针 @YZ 取得相应存储器的地址 012H 的数据送给

CC

CC

SONiX TECHNOLOGY CO., LTD Page 27 Revision 0.8

Page 28

Preliminary SN8P1702A/SN8P1703A

@

8-bit micro-controller build-in 12-bit ADC

5 系统寄存器

5.1 概述

RAM 中 bank0 的 80H~FFH 被留做系统专用寄存器,用来控制芯片的外部硬件资源,如输入/输出口状态、SIO、

ADC、PWM、定时器和计数器等。下面的系统专用寄存器地址分配表为编写应用程序提供了方便快捷的参考基准源。

通过 bank0 的读/写指令(B0MOV, B0BSET, B0BCLR…)或选定的 RAM 页(RBANK = 0)访问系统寄存器。

5.2 系统寄存器配置(BANK 0)

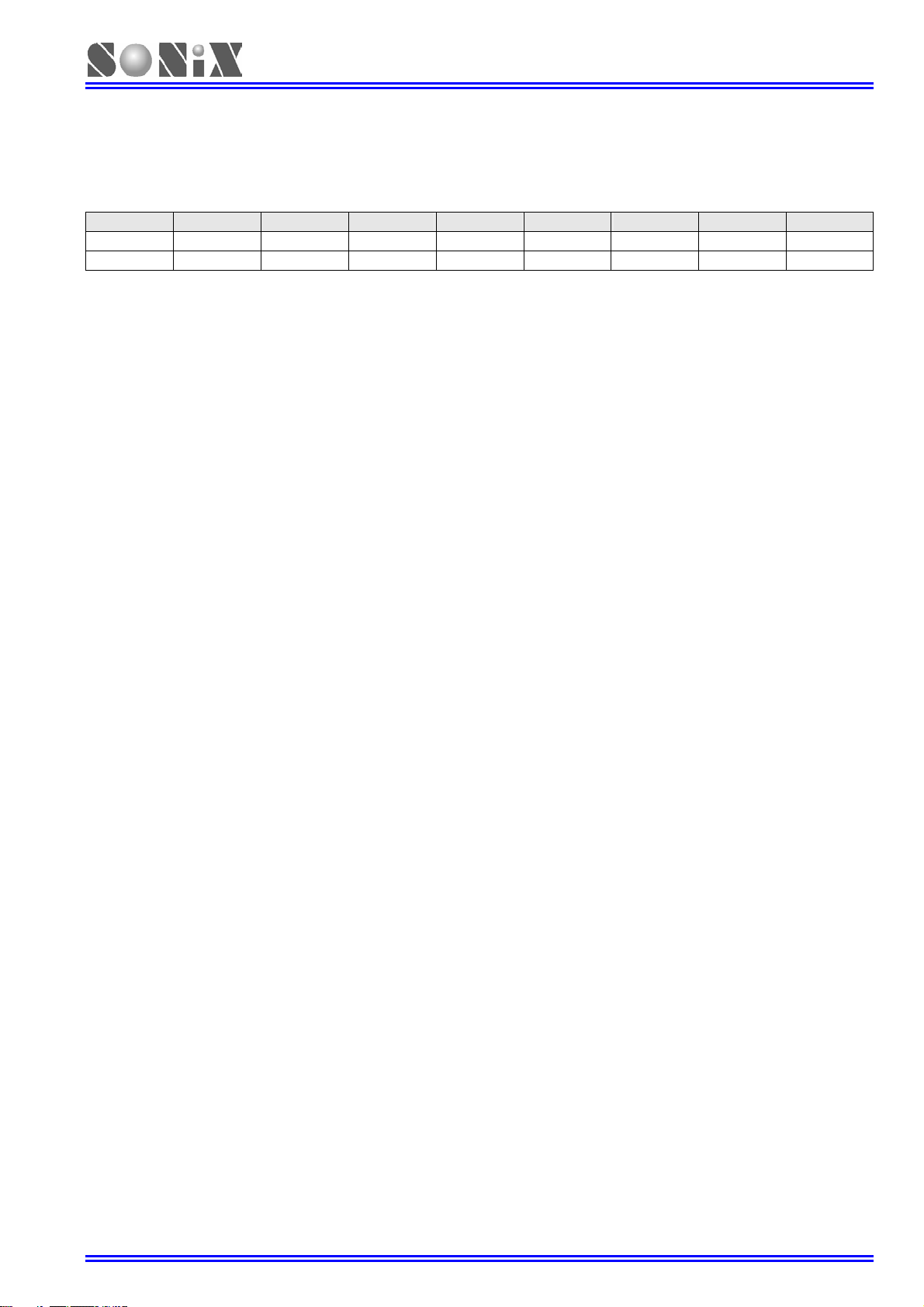

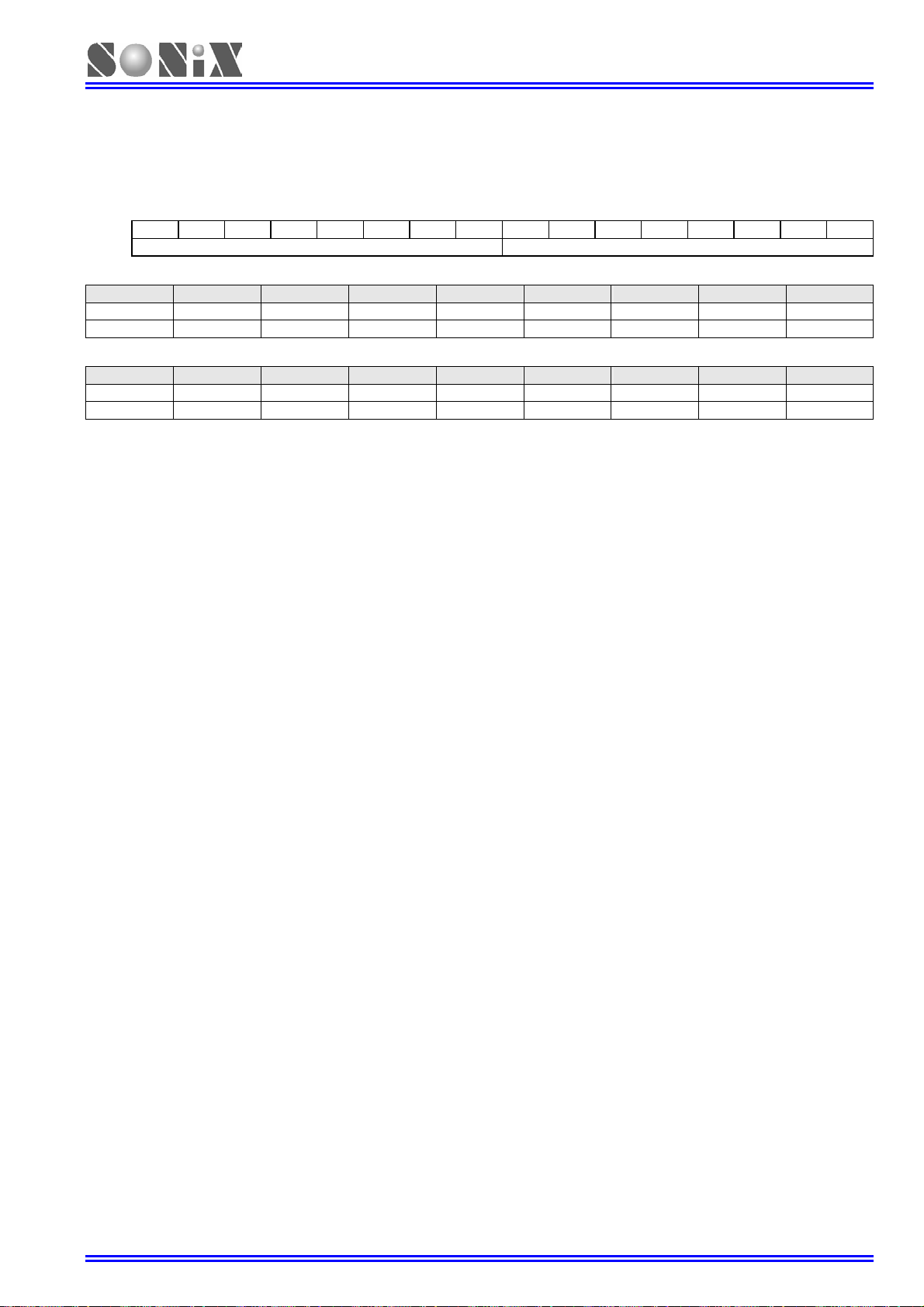

5.2.1 系统寄存器的字节

0 1 2 3 4 5 6 7 8 9 A B C D E F

8 - - R Z Y - PFLAG - - - - - - - - -

9 - - - - - - - - - - - - - - - -

A - - - - - - - - - - - - - - P4CON -

B - ADM ADB ADR - - - - - - - - - - - PEDGE

C P1W P1M - - P4M P5M - - INTRQ INTEN OSCM - - TC0R PCL PCH

D P0 P1 - - P4 P5 - - T0M - TC0M TC0C TC1M TC0C TC1R STKP

E P0UR P1UR - - P4UR P5UR - @YZ - - - - - - - -

F STK7 STK7 STK6 STK6 STK5 STK5 STK4 STK4 STK3 STK3 STK2 STK2 STK1 STK1 STK0 STK0

表 5-1 系统专用寄存器地址分配

说明:

PFLAG = ROM 页和特殊标志寄存器 R = 工作寄存器和 ROM 查表数据缓存器

ADB = ADC 数据缓冲器 Y, Z = 工作寄存器,

输入输出模式寄存器

PnM =

INTRQ =

OSCM =

TC0/1M =

TC0/1C =

TC0/1R =

STKP = 堆栈指针 INTEN = 中断使能寄存器

@HL = 间接寻址寄存器 PCH, PCL = 程序计数器

@YZ =

¾ 注:

a) 所有的寄存器名称已经在 SN8ASM 汇编语言是默认的;

b) 寄存器中各位的名称已在 SN8ASM 汇编语言中以“F”为前缀定义过;

c) 在用指令检查空位时,都置为逻辑“H”;

d) ADR 寄存器中的低字节是只读寄存器;

e) 指令“b0bset”, “b0bclr”, ”bset”, ”bclr” 仅对 “R/W” 寄存器有效。

中断请求寄存器

振荡器寄存器

TC0/1 模式寄存器

TC0/1 计数寄存器

TC0/1 自动装载数据寄存器

间接寻址寄存器

RBANK =

ADM =

P1W =

PnUR=

STK0~STK7 =

RAM Bank 选择寄存器

ADC 模式寄存器

ADC 精度寄存器

ADR =

P1 口唤醒功能寄存器

Port n 数据缓冲器

Pn =

上拉寄存器

Stack 0 ~ stack 7 缓冲器

YZ 和 ROM 寻址寄存器

SONiX TECHNOLOGY CO., LTD Page 28 Revision 0.8

Page 29

Preliminary SN8P1702A/SN8P1703A

8-bit micro-controller build-in 12-bit ADC

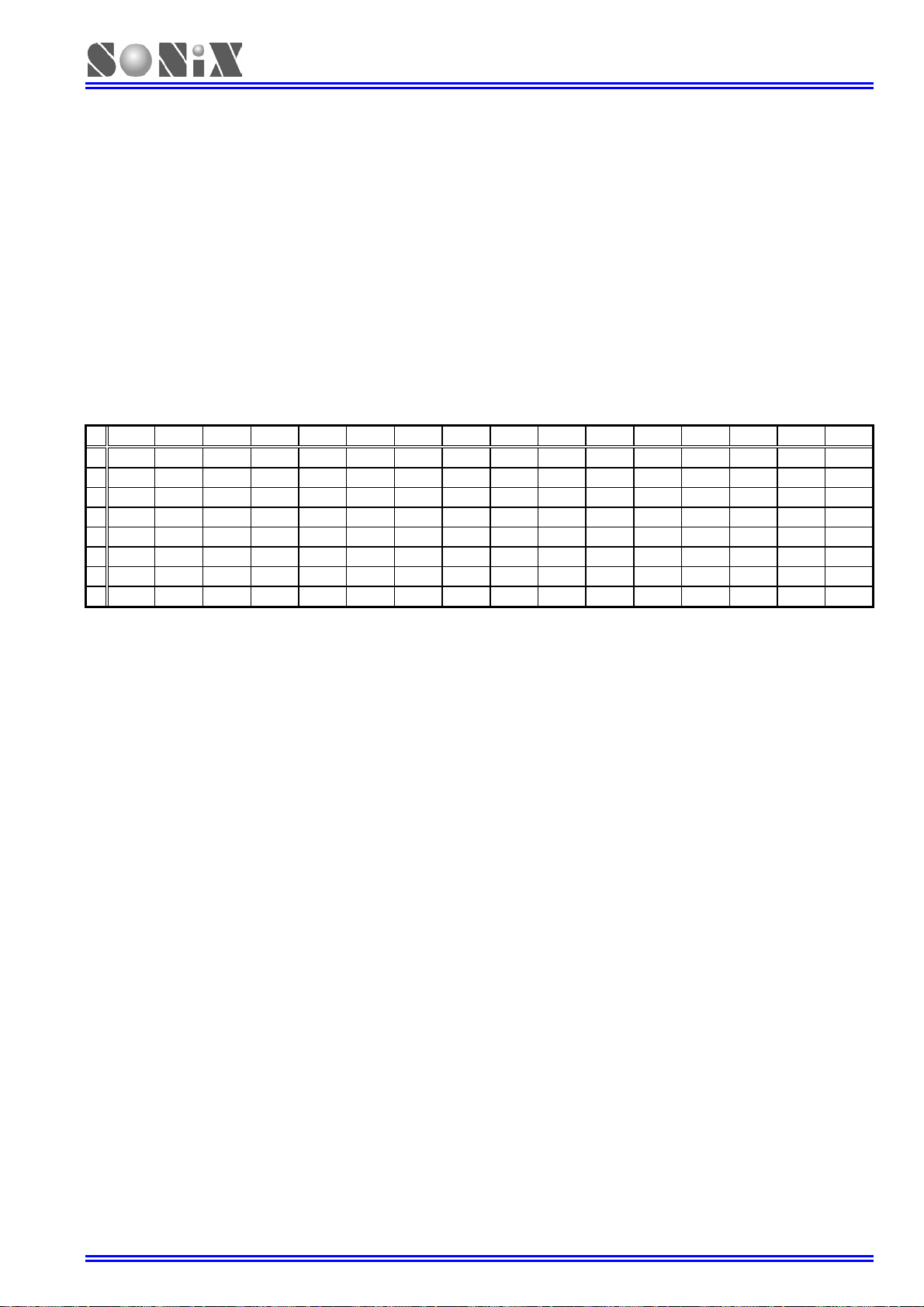

5.2.2 系统寄存器的位地址配置表

地址 Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 读/写 注

082H RBIT7 RBIT6 RBIT5 RBIT4 RBIT3 RBIT2 RBIT1 RBIT0 R/W R

083H ZBIT7 ZBIT6 ZBIT5 ZBIT4 ZBIT3 ZBIT2 ZBIT1 ZBIT0 R/W Z

084H YBIT7 YBIT6 YBIT5 YBIT4 YBIT3 YBIT2 YBIT1 YBIT0 R/W Y

086H - - - - - C DC Z R/W PFLAG

0AEH - - - - P4CON3 P4CON2 P4CON1 P4CON0 R/W P4CON

0B1H ADENB ADS EOC GCHS - - CHS1 CHS0 R/W ADM 模式寄存器

0B2H ADB11 ADB10 ADB9 ADB8 ADB7 ADB6 ADB5 ADB4 R ADB 数据缓冲器

0B3H - ADCKS1 ADLEN - ADB3 ADB2 ADB1 ADB0 R/W ADR 寄存器

0BFH PEDGEN - - P00G1 P00G0 - - - R/W PEDGE

0C0H 0 0 0 0 0 0 P11W P10W W P1W 唤醒寄存器

0C1H 0 0 0 0 0 0 P11M P10M R/W P1M I/O 方向寄存器

0C4H 0 0 0 0 P43M P42M P41M P40M R/W P4M I/O 方向寄存器

0C5H 0 0 P55M P54M P53M P52M P51M P50M R/W P5M I/O 方向寄存器

0C8H 0 TC1IRQ TC0IRQ 0 0 0 0 P00IRQ R/W INTRQ

0C9H 0 TC1IEN TC0IEN 0 0 0 0 P00IEN R/W INTEN

0CAH WTCKS WDRST WDRATE CPUM1 CPUM0 CLKMD STPHX 0 R/W OSCM

0CDH TC0R7 TC0R6 TC0R5 TC0R4 TC0R3 TC0R2 TC0R1 TC0R0 W TC0R

0CEH PC7 PC6 PC5 PC4 PC3 PC2 PC1 PC0 R/W PCL

0CFH - - - - - - PC9 PC8 R/W PCH

0D0H - - - - - - - P00 R P0 数据缓冲器

0D1H - - - - - - P11 P10 R/W P1 数据缓冲器

0D4H - - - - P43 P42 P41 P40 R/W P4 数据缓冲器

0D5H - - P55 P54 P53 P52 P51 P50 R/W P5 数据缓冲器

0D8H - - - - TC1X8 TC0X8 TC0GN - R/W T0M

0DAH TC0ENB TC0rate2 TC0rate1 TC0rate0 TC0CKS ALOAD0 TC0OUT PWM0OUT R/W TC0M

0DBH TC0C7 TC0C6 TC0C5 TC0C4 TC0C3 TC0C2 TC0C1 TC0C0 R/W TC0C

0DCH TC1ENB TC1rate2 TC1rate1 TC1rate0 0 ALOAD1 TC1OUT PWM1OUT R/W TC1M

0DDH TC1C7 TC1C6 TC1C5 TC1C4 TC1C3 TC1C2 TC1C1 TC1C0 R/W TC1C

0DEH TC1R7 TC1R6 TC1R5 TC1R4 TC1R3 TC1R2 TC1R1 TC1R0 W TC1R

0DFH GIE - - - STKPB3 STKPB2 STKPB1 STKPB0 R/W STKP 堆栈指针

0E0H P00R R/W P0UR

0E1H P11R P10R R/W P1UR

0E4H P43R P42R P41R P40R R/W P4UR

0E5H P55R P54R P53R P52R P51R P50R R/W P5UR

0E7H @YZ7 @YZ6 @YZ5 @YZ4 @YZ3 @YZ2 @YZ1 @YZ0 R/W @YZ 间接寻址寄存器

0F0H S7PC7 S7PC6 S7PC5 S7PC4 S7PC3 S7PC2 S7PC1 S7PC0 R/W STK7L

0F1H - - - - - - S7PC9 S7PC8 R/W STK7H

0F2H S6PC7 S6PC6 S6PC5 S6PC4 S6PC3 S6PC2 S6PC1 S6PC0 R/W STK6L

0F3H - - - - - - S6PC9 S6PC8 R/W STK6H

“ “““““““ “““

“ “““““““ “““

“ “““““““ “““

0FCH S1PC7 S1PC6 S1PC5 S1PC4 S1PC3 S1PC2 S1PC1 S1PC0 R/W STK1L

0FDH - - - - - - S1PC9 S1PC8 R/W STK1H

0FEH S0PC7 S0PC6 S0PC5 S0PC4 S0PC3 S0PC2 S0PC1 S0PC0 R/W STK0L

0FFH - - - - - - S0PC9 S0PC8 R/W STK0H

表 5-2 系统寄存器的位地址配置表

¾ 注:

a)为避免系统出错,程式中使用到上表中所有标“0”的位时要设定为“0”;

b)所有的寄存器名称在 SN8ASM 编译器中是默认的;

c)寄存器中各位的名称已在 SN8ASM 汇编语言中以“F”为前缀定义过;

d)指令“b0bset”、“b0bclr”、”bset”、”bclr”仅对“R/W”寄存器有效。

SONiX TECHNOLOGY CO., LTD Page 29 Revision 0.8

Page 30

Preliminary SN8P1702A/SN8P1703A

8-bit micro-controller build-in 12-bit ADC

6 上电复位

6.1 概述

SN8P1702A / SN8P1703A 有两种系统复位方式:外部复位和内部低电压侦测(LVD)复位。外部复位电路是一

个简单的 RC 电路,低电压侦测(LV D)是芯片内置电路。当其中任何一个复位信号产生时,系统复位并初始化系统

寄存器,时序图如下

:

VDD

External Reset

LVD

Internal Reset Signal

LVD Detect Level

External Reset Detect Level

End of LVD Reset

End of External Reset

图 6-1 上电复位时序图

SONiX TECHNOLOGY CO., LTD Page 30 Revision 0.8

Page 31

Preliminary SN8P1702A/SN8P1703A

8-bit micro-controller build-in 12-bit ADC

6.2 外部复位

外部复位为低电平有效,当复位引脚侦测到低电压时,系统开始复位,直到侦测到的电压达到高电平。

VDD

External Reset

Internal Reset Signal

图 6-2 外部复位时序图

用户必须确保 VDD 先于外部复位电压达到稳定状态(图 6-2),否则复位无效。外部复位电路是一个简单的 RC

电路,如下图所示:

R

C

0.1uF

R2 110

20K ohm

External Reset Detect Level

End of External ResetSystem Reset

VDD

RST

MCU

VSS

VCC

GND

图 6-3 外部复位电路

¾ 注:使用 R2 可以避免外部干扰对 MCU 复位的影响,建议 R2 的值为 100~200Ω。

在某些情况下,通过在 VCC 和复位引脚之间放置一个二极管可以改善掉电复位。

DIODE

C

0.1uF

R

20K ohm

R2 110

VDD

RST

MCU

VSS

VCC

GND

图 6-4 加二极管后的外部复位电路

¾ 注:使用 R2 可以避免外部干扰对 MCU 复位的影响,建议 R2 的值为 100~200Ω。

SONiX TECHNOLOGY CO., LTD Page 31 Revision 0.8

Page 32

Preliminary SN8P1702A/SN8P1703A

8-bit micro-controller build-in 12-bit ADC

7 振荡器

7.1 概述

SN8P1702A / SN8P1703A 是具有高速时钟和低速时钟的双时钟微控制器。高速时钟由外部振荡电路提供,低

速时钟由芯片内部 RC 振荡电路提供

外部高速时钟和内部低速时钟都可用作系统时钟(Fosc),系统时钟再经 4 分频后作为指令执行时钟周期(Fcpu)。

Fcpu = Fosc / 4

下面是需要用到系统时钟的外围设备:

9 定时计数器(TC0 /TC1)

9 看门狗定时器

9 AD 转换

9 PWM 输出(PWM0, PWM1)

9 蜂鸣器输出(TC0OUT, TC1OUT)

7.1.1 时钟框图

HXRC(1:0) is code option

HXRC(1:0) is code option

•00= RC

•00= RC

•01 =32 Khz Oscillator

•01 =32 Khz Oscillator

•10 = High Speed Oscillator (>10Mhz)

•10 = High Speed Oscillator (>10Mhz)

•11 = Standard Oscillator (4Mhz)

•11 = Standard Oscillator (4Mhz)

STPHX HXRC

STPHX HXRC

STPHX HXRC

XIN

XIN

XIN

XOUT

XOUT

XOUT

¾ HXOSC:外部高速时钟

¾ LXOSC:内部低速时钟

HXOSC.

HXOSC.

HXOSC.

CPUM0

CPUM0

CPUM0

LXOSC.

LXOSC.

LXOSC.

CPUM0

CPUM0

CPUM0

fh

fh

fh

OSG : Oscillator Safe Guard

OSG : Oscillator Safe Guard

1 : Disable -- System Default

1 : Disable -- System Default

fl

fl

fl

0 : Enable

0 : Enable

Divided by 2

Divided by 2

1 : Disable

1 : Disable

0 : Enable

0 : Enable

Divided by 2OSG

Divided by 2Divided by 2OSGOSG

图 7-1 时钟框图

CLKMD

CLKMD

CLKMD

Divided by 4

Divided by 4

Divided by 4Divided by 4

fosc/4 CPUM0

fosc/4 CPUM0

fosc/4 CPUM0

fcpu

fcpu

fcpu

SONiX TECHNOLOGY CO., LTD Page 32 Revision 0.8

Page 33

Preliminary SN8P1702A/SN8P1703A

[

p

14

p

8-bit micro-controller build-in 12-bit ADC

7.1.2 OSCM 寄存器

振荡器控制寄存器 OSCM 决定了系统振荡源、系统模式以及看门狗定时器的时钟源等。

OSCM 初始值 = 0000 000x

0CAH Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

WDRST Wdrate CPUM1 CPUM0 CLKMD STPHX 0

- R/W R/W R/W R/W R/W R/W -

Bit1 STPHX: 外部高速时钟控制位

0 = 自由运行

1 = 停止

¾ 注:该位仅能控制外部高速振荡器。如果 STPHX=1,内部低速时钟 RC 振荡器仍然运行。

Bit2 CLKMD: 系统高/低速模式选择位

0 = 普通(双重)模式

1 = 低速模式

Bit

4:3] CPUM[1:0]: CPU 运行模式控制位

00 = 普通模式

01 = 睡眠(省电)模式

10 = 绿色模式

11 = 保留

Bit5 Wdrate: 看门狗定时器速率选择位

0 = Fc

1 = Fcpu ÷ 28

Bit6 WDRAT: 看门狗定时器复位位

0 = 看门狗正常运行

1 = 看门狗定时器清零

Bit7 WTCKS:看门狗定时器时钟源选择位

0 = Fc

1 = 内部 RC 低速时钟

u ÷ 2

u

SONiX TECHNOLOGY CO., LTD Page 33 Revision 0.8

Page 34

Preliminary SN8P1702A/SN8P1703A

8-bit micro-controller build-in 12-bit ADC

7.1.3 外部高速振荡器

SN8P1702A / SN8P1703A 可以工作于四种振荡器模式: RC 振荡器模式、外部高速振荡模式(12M 编译选项)、

标准振荡模式(4M 编译选项)和低速振荡模式(32K 编译选项)。在不同的应用场合,用户可通过编译选项,为工

作系统选择适当的高速时钟源。

例: 外部高速振荡器停止.

B0BSET FSTPHX ; 停止外部高速振荡器

B0BSET FCPUM0 ; 停止外部高速振荡器和内部低速振荡器并将系统从睡眠(省

电)模式中唤醒.

7.1.4 振荡器模式编译选项

SN8P1702A / SN8P1703A 在不同的应用下提供 4 种振荡模式,分别为:4M,12M,32K 和 RC,以支持不同

的振荡器类型和频率。MCU 运行高速时钟系统比运行低速时钟系统需要的电流要多。对于晶振,有 3 个选择项,当

振荡器的类型为 RC 型时,选择“RC”,系统将自动二分频。在编译前,用户可以从编译选项表中选择振荡器的类型。

编译选项表如下所示:

代码 振荡器模式 说 明

00 RC 模式 从 XOUT 引脚输出频率为 Fcpu 的方波

01 32K 晶振 32768Hz

10 12M 晶振 12MHz ~ 16MHz

11 4M 晶振 3.58MHz

7.1.5 振荡器二分频编译选项

SN8P1702A / SN8P1703A 有一个将外部时钟 2 分频的编译选项:“HIGH_CLK /2”,如果“HIGH_CLK /2”是使能

的,那么外部时钟频率被 8 分频后作为指令周期 Fcpu:Fcpu=Fosc/8;如果“HIGH_CLK /2”被禁止,则外部时钟频

率被 4 分频后作为指令周期:Fcpu=Fosc/4。

¾ 注:在 RC 模式中,“HIGH_CLK /2”通常处于使能状态。

SONiX TECHNOLOGY CO., LTD Page 34 Revision 0.8

Page 35

7.2 系统振荡器电路图

Preliminary SN8P1702A/SN8P1703A

8-bit micro-controller build-in 12-bit ADC

20PF

CRYSTAL

20PF

图 7-2 晶体振荡器

R

C

图 7-3 RC 振荡器

External Clock Input

VDD

XIN

XOUT

VSS

VDD

XIN

XOUT

VSS

MCU

MCU

VDD

XIN

MCU

XOUT

VSS

图 7-4 外部时钟输入

¾ 注 1:外部振荡电路的 VDD 和 VSS 必须来自微控制器,而不是相邻的其它电源端。

¾ 注 2:外部时钟输入可以选择 RC 振荡器或晶体振荡器,产生的时钟由 XIN 引脚输入。

¾ 注 3:在 RC 振荡器模式下,外部时钟频率被 2 分频。

¾ 注 4:外部振荡器的电源端和接地端必须和微控器的 VDD 和 VSS 相连,以提高整个系统的性能。

7.3 外部 RC 振荡器频率测试

测试外部 RC 振荡器的频率 Fosc 有两种方法: 一是测试 XOUT 的输出波形。在外部 RC 振荡器模式下,XOUT

的输出波形频率就是 Fcpu。二是通过程序测试指令周期 Fcpu 来测量,因为外部 RC 频率就等于 4倍的 Fcpu,通 过

Fcpu 就可以得到外部 RC 的频率 Fosc。测试外部振荡器频率 Fcpu 的程序如下:

例:外部振荡器的指令周期测试

B0BSET P1M.0 ; 设置 P1.0 为输出模式,输出频率信号.

@@:

B0BSET P1.0 ; 在 RC 模式下输出频率信号.

B0BCLR P1.0 ;

JMP @B

SONiX TECHNOLOGY CO., LTD Page 35 Revision 0.8

Page 36

Preliminary SN8P1702A/SN8P1703A

8-bit micro-controller build-in 12-bit ADC

7.4 内部低速振荡器

SN8P1700A 内置低速 RC 振荡器可提供系统时钟、定时计数器、看门狗定时器、SIO 等的时钟源。

例: 停止内部低速振荡器

B0BSET FCPUM0 ; 停止外部高速和内部低速振荡器,进入睡眠模式

¾ 注:内部低速时钟不能被单独停止,它由 OSCM 寄存器的 CPUM0 位控制。

低速振荡器采用 RC 振荡电路,频率受系统电压和温度的影响。通常情况下,RC 振荡器的频率约为 16KHZ(3V)、

32KHZ(5V)。RC 频率和电压之间的关系如下图所示:

Internal RC vs. VDD

40

35

30

25

20

15

10

Fintrc (KHz)

5

0

1.80 2.00 2.50 3.00 3.50 4.00 4.50 5.00 5.50 6.00 6.50

7.329

32.008

28.673

25.338

22.003

18.668

15.333

11.998

8.663

38.678

35.343

VDD (Volts)

图 7-5 内部 RC 与 VDD 之间的函数关系

例:由 Fcpu 测试内部 RC 频率。 内部 RC 频率等于 4 倍的 Fcpu。我们可以从 Fcpu 得到内部 RC 的频率

B0BSET P1M.0 ; 设置 P1.0 为输出模式,输出频率信号.

B0BSET FCLKMD ; 切换到内部低速

@@:

B0BSET P1.0 ; 在低速模式下输出频率信号.

B0BCLR P1.0 ;

JMP @B

SONiX TECHNOLOGY CO., LTD Page 36 Revision 0.8

Page 37

Preliminary SN8P1702A/SN8P1703A

8-bit micro-controller build-in 12-bit ADC

7.5 系统模式

7.5.1 概述

SN8P1702A / SN8P1703A 能够在 4 种不同的模式之间转换,以减小功耗。

¾ 普通(高速)模式

¾ 低速模式

¾ 省电(睡眠)模式

¾ 绿色模式

实际应用中,用户可以利用 OSCM 寄存器调整系统的工作模式。 高速模式下,指令周期(Fcpu)为 Fosc/4,

低速模式下/3V 下,Fcpu 为 16KHz/4。

7.5.2 普通模式

普通模式中,系统时钟源为内部高速时钟。系统上电时,系统默认为普通模式,指令周期为 fosc/4。当外部高速

振荡器是 3.58MHZ 时,指令周期为 3.58MHZ/4=895KHZ。所有的软件和硬件都能够在普通模式下运行和工作,系

统可转入省电模式、低速模式和绿色模式

。

7.5.3 低速模式

低速模式中,系统时钟源为内部低速时钟。设 CLKMD = 1,系统就进入内部低速模式。低速模式下的运行与普

通模式的工作状态相似,仅时钟频率降低。系统在低速模式时可以转换到高速普通模式和省电模式。设 STPHX=1,

可以停止外部高速振荡器,系统功耗也会降低。

7.5.4 绿色模式

绿色模式是一种低功耗模式,在绿色模式下,只有 TC0 仍然运行,而其他的硬件则停止工作。外部高速振荡器

和内部低速振荡器仍然运行。设 CPUM1=1,CPUM0=0,系统就进入绿色模式。设 TC0GN=1(T0M 的第 1 位),

使能 TC0 的绿色模式唤醒功能。系统可以由 TC0 和 P0 的电平变换来唤醒。

绿色模式提供定时唤醒功能。用户可通过设置 TC0 来确定系统的唤醒时间。系统可以从普通模式和低速模式进

入绿色模式,在普通模式下,TC0 的溢出时间较短,而在低速模式下,其溢出时间就较长。在实际应用中,用户可

根据情况选择合适的唤醒时间。在绿色模式下,其电源功耗为 5uA (3V)。

7.5.5 省电模式

省电模式也称睡眠模式,系统进入睡眠状态时,将停止工作,功耗低至近似于零。省电模式常用于电池供电等

节电系统。设 CPUM0=1,系统进入省电模式,外部高速和低速振荡器均停止,P0、P1 的触发信号可将系统唤醒。

SONiX TECHNOLOGY CO., LTD Page 37 Revision 0.8

Page 38

7.5.6 系统模式控制

系统模式框图

Preliminary SN8P1702A/SN8P1703A

8-bit micro-controller build-in 12-bit ADC

P0,P1 口唤醒功能激活

外部复位激活

普通模式

省电模式

(睡眠模式)

CPUM1, CPUM0 = 01

CPUM1, CPUM0 = 01

CLKMD = 1

CLKMD = 1

CLKMD = 0

CLKMD = 0

低速模式

P0,P1 口唤醒功能激活

,

TC0 溢出激活

外部复位激活

CPUM1, CPUM0 = 10

CPUM1, CPUM0 = 10

绿色模式

图 7-6 系统模式框图

P0,P1 口唤醒功能激活

TC0 溢出激活

外部复位激活

工作模式 普通模式 低速模式

HX osc.

LX osc.

运行

运行 运行 运行 停止

STPHX

绿色模式

省电(睡眠)模式 说明

STPHX 停止

CPU 指令 执行 执行 停止 停止

TC0 *有效 *有效 *有效 无效 *程序激活*

WDT 有效 有效 INT_16K_RC 无效

内部中断 全部有效 全部有效 TC0 全部无效

外部中断 全部有效 全部有效 全部有效 全部无效

系统唤醒 - - P0, P1, TC0 复位信号 P0, P1, 复位信号

表 7-1 操作模式说明

SONiX TECHNOLOGY CO., LTD Page 38 Revision 0.8

Page 39

Preliminary SN8P1702A/SN8P1703A

8-bit micro-controller build-in 12-bit ADC

7.5.6.1 系统模式转换

普通/低速模式转换为省电模式

CPUM0 = 1

B0BSET FCPUM0 ; 设置 CPUM0=1,进入睡眠模式。

系统在睡眠模式中,只有具有唤醒功能的引脚和复位引脚能够将系统唤醒。

普通模式转换为低速模式

B0BSET FCLKMD ; 设置 CLKMD = 1,进入低速模式

B0BSET FSTPHX ; 停止高速振荡器以省电

¾ 注:用户可以不用理会高速振荡器是否停止。

低速模式转换为普通模式(外部高速振荡器仍然运行)

B0BCLR FCLKMD ;

低速模式转换为普通模式(外部高速振荡器停止)

如果外部高速时钟停止时程序欲重新回到普通模式,就必须延迟 10mS 以等待外部时钟稳定下来。

B0BCLR FSTPHX ; 启动外部高速振荡器

B0MOV Z, #27 ; 若 VDD = 5V,则内部 RC 的频率为 32KHz (典型值)

@@: DECMS Z ; 高速振荡器稳定时间 0.125ms X 81 = 10.125ms

JMP @B

;

B0BCLR FCLKMD ; 进入普通模式

例:进入绿色模式,由 TC0 唤醒

; 设置定时器 TC0 的唤醒功能

B0BCLR FTC0IEN ; 禁止 TC0 中断

B0BCLR FTC0ENB ; 禁止 TC0 计数

MOV A,#20H ;

B0MOV TC0M,A ; 设置 TC0 时钟源= Fcpu / 64

MOV A,#74H

B0MOV TC0C,A ; 设置 TC0C 的初始值 = 74H (设置 TC0 定时间隔= 10 ms)

B0BCLR FTC0IEN ; 禁止 TC0 中断

B0BCLR FTC0IRQ ; 清 TC0 中断请求标志

B0BSET FTC0ENB ; 使能 TC0 定时器功能

B0BSET FTC0GN ; 使能 TC0 唤醒功能

; 进入绿色模式

B0BCLR FCPUM0 ; 设置 CPUMx = 10

B0BSET FCPUM1

¾ 注:如果 TC0ENB = 0 或者 TC0GN = 0, TC0 没有将系统从绿色模式中唤醒进入普通/低速模式的功能。

设置 CLKMD=0

SONiX TECHNOLOGY CO., LTD Page 39 Revision 0.8

Page 40

Preliminary SN8P1702A/SN8P1703A

8-bit micro-controller build-in 12-bit ADC

7.6 唤醒时间

7.6.1 概述

外部高速振荡器从停止到运行需要一段时间的延迟,这段延迟时间对振荡器的稳定工作是必需的。在有些应用

中,外部高速振荡器可能需要经常的开停。外部高速振荡器重新启动需要的这一延迟时间称为唤醒时间。

有两种情况需要唤醒时间:一是从省电模式转换到普通模式,二是从低速模式转换到普通模式。对前一种情况,

SN8P1702A / SN8P1703A 提供了 2048 个振荡时钟作为唤醒时间,后一种情况需要用户自行计算唤醒时间。

7.6.2 硬件唤醒

当系统处于省电(睡眠)模式时,外部高速振荡器停止运行。从睡眠模式唤醒时,SN8P1702A / SN8P1703A

提供 2048 个外部高速振荡时钟作为唤醒时间,以使振荡电路达到稳定状态。唤醒时间结束后,系统进入通常模式,

唤醒时间的计算如下:

唤醒时间 = 1/Fosc×2048 (sec)+X’tal 稳定时间

X’tal 稳定时间决定于 X’tal 的类型,一般为 2~4ms。

例:在省电模式,系统由 P0 或 P1 端的触发信号唤醒。唤醒时间结束后,系统进入普通模式,P0 和 P1 端唤醒

时间如下:

唤醒时间=1/Fosc× 2048 = 0.57 ms (Fosc = 3.58MHz)

总的唤醒时间=0.57ms+X’tal 固定时间

省电(睡眠)模式下,具有唤醒功能的 P0 和 P1 都能将系统唤醒,P0 永远具有唤醒功能,而 P1 的唤醒功能受

寄存器 P1W 控制。

P1W 初始值=xxxx xx00

0C0H Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

P1W 0 0 0 0 0 0 P11W P10W

- - - - - - W W

Bit[1:0] P11W, P10W:

0 = 禁止 Port1 的唤醒功能

1 = 使能 Port1 的唤醒功能

Port1 唤醒功能控制位。

7.6.3 外部唤醒触发控制

在 SN8P1702A / SN8P1703A 中由寄存器 PEDGE 控制唤醒触发的方向。

PEDGE 初始值=0xx0 0xxx

0BFH Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

PEDGE PEDGEN - - P00G1 P00G0 - - -

R/W - - R/W R/W - - -

Bit7 PEDGEN:中断和唤醒触发边沿控制位。

0=禁止边沿触发功能;

P0:低电平触发唤醒,下降沿触发中断;

P1:低电平触发唤醒。

1=使能边沿触发功能。

P0.0:由 P00G1 和 P00G0 位控制唤醒和中断的触发;

P1:改变电平(下降沿或上升沿)触发唤醒。

Bit[4: 3] P00G[1:0]:P0.0 边沿选择位。

00=保留

01=下降沿

10=上升沿

11= 上升/下降双边沿

SONiX TECHNOLOGY CO., LTD Page 40 Revision 0.8

Page 41

Preliminary SN8P1702A/SN8P1703A

X

[

p

p

p

看

8-bit micro-controller build-in 12-bit ADC

8 定时/计数器

8.1 看门狗定时器(WDT)

看门狗定时器(WDT)是一个二进制加 1 计数器,用来监控程序的运行状态,如果程序由于干扰进入未知状态,

看门狗定时器将溢出,使微控制器复位。程序中定期要将看门狗定时器清零(“B0BSET FWDRST”),否则,看门狗

定时器溢出会造成系统复位。设置 OSCM 寄存器的 WDRATE 位可以选择看门狗定时器的溢出时间。在省电模式和

绿色模式下,看门狗定时器将被禁止。

OSCM 初始值=0000 000x

0CAH Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

OSCM WTCKS WDRST Wdrate CPUM1 CPUM0 CLKMD STPHX -

R/W R/W R/W R/W R/W R/W R/W -

Bit1 STPH

0 = 自由运行

1 = 停止

¾ 注:该位仅能控制外部高速振荡器,若 STPHX=1,内部低速 RC 振荡器仍然运行。

Bit2 CLKMD:系统高/低速模式选择位。

0 = 普通(双重)模式

1 = 低速模式

Bit

4:3] CPUM[1:0]:CPU 运行模式控制位

00 = 普通模式

01 = 睡眠(省电)模式

10 = 绿色模式

11 = 保留

Bit5 Wdrate:看门狗定时器速率选择位。

0 = Fc

1 = Fc

Bit6 WDRST:看门狗定时器复位位。

0 = 看门狗正常运行

1 = 将看门狗定时计数器清零

Bit7 WTCKS:看门狗定时器时钟源选择位

0 = Fc

1 =内部 RC 低速时钟

WTCKS WTRATE CLKMD

0 0 0 1 / ( Fcpu ÷ 214 ÷ 16 ) = 293 ms, Fosc=3.58MHz

0 1 0 1 / ( Fcpu ÷ 28 ÷ 16 ) = 500 ms, Fosc=32768Hz

0 0 1 1 / ( Fcpu ÷ 214 ÷ 16 ) = 65.5s, Fosc=16KHz@3V

0 1 1 1 / ( Fcpu ÷ 28 ÷ 16 ) = 1s, Fosc=16KHz@3V

1 - - 1 / ( 16K ÷ 512 ÷ 16 ) ~ 0.5s @3V

¾ 注:编译选项可控制是否运行看门狗定时器

例:下面是看门狗定时器的操作,在程序的开始将看门狗定时计数器清零。

Main:

B0BSET FWDRST ; 清看门狗定时器

. .

CALL SUB1

CALL SUB2

. .

JMP MAIN

:外部高速振荡器控制位。

u ÷ 214

u ÷ 28

u

门狗定时器溢出时间

表 8-1 看门狗定时器溢出时间表

SONiX TECHNOLOGY CO., LTD Page 41 Revision 0.8

Page 42

Preliminary SN8P1702A/SN8P1703A

8-bit micro-controller build-in 12-bit ADC

8.2 T0M 寄存器

T0M 初始值=xxxx 000x

0D8H Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

T0M - - - - TC1X8 TC0X8 TC0GN -

- - - - R/W R/W R/W -

Bit3 TC1X8:TC1 定时器速率的 8 倍。

0 = 禁止

1 = 使能

Bit2 TC0X8:TC0 定时器速率的 8 倍。

0 = 禁止

1 = 使能

Bit0 TC0GN:开放 TC0 绿色模式的唤醒功能

0 = 禁止

1 = 使能

SONiX TECHNOLOGY CO., LTD Page 42 Revision 0.8

Page 43

Preliminary SN8P1702A/SN8P1703A

8-bit micro-controller build-in 12-bit ADC

8.3 定时计数器 TC0

8.3.1 概述

定时/计数器 TC0 用来产生定时中断请求。它是具有自动重新装载功能的定时/计数器,主要由两部分组成:8 位

自动装载寄存器 TC0R,用于保存计数参考值;8 位自动加 1 的计数器 TC0C。

TC0out

TC0out

PWM0OUT

PWM0OUT

TC0 Time out

TC0 Time out

fcpu

fcpu

÷ 2

÷ 2

(8-TC0Rate)

(8-TC0Rate)

TC0enb

TC0enb

TC0R reload

data buffer

data buffer

load

load

TC0C

TC0C

8-bit binary counter

8-bit binary counter

Aload0

Aload0

Compare

Compare

Internal P5.4 I/O circuit

Internal P5.4 I/O circuit

Auto. reload

Auto. reload

R

R

S

S

Buzzer

Buzzer

÷2

÷2

PWM

PWM

P5.4

P5.4TC0R reload

CPUM0

CPUM0

图 8-1 计数定时器 TC0 框图

TC0 的主要功能如下:

¾ 8 位可编程定时器:根据设定的时钟频率,产生定时中断。

¾ 频率输出(BUZZER 输出):通过 BZ0 引脚 (P5.4)输出一个可选择的时钟频率。

¾ PWM:PWM 输出,由 PWM1OUT 位控制,通过 PWM0OUT 引脚 (P5.4)输出。

SONiX TECHNOLOGY CO., LTD Page 43 Revision 0.8

Page 44

Preliminary SN8P1702A/SN8P1703A

A

/

/

/

8-bit micro-controller build-in 12-bit ADC

8.3.2 TC0M 模式寄存器

TC0M 为 8 位可读/写模式控制寄存器。通过载入不同值,用户可以在执行程序过程中动态的调整定时器的时钟

频率。

通过设置 TC0 的 TC0RATE0~TC0RATE2 和 T0M 寄存器的 TC0X8 位,TC0 提供了 8 种可选择的速率。若

TC0X8=1,TC0 的速率是 TC0X8=0(初始值)的 8 倍,TC0M 的第 7 位 TC0ENB 是 TC0 定时器的开始控制位。

TC0M 初始值=0000 0000

0DAH Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

TC0M TC0ENB TC0RATE2 TC0RATE1 TC0RATE0 TC0CKS

R/W R/W R/W R/W R/W R/W R/W R/W

Bit7

0 = 禁止

1 =

Bit[6:4] TC0RATE[2:0]

Bit3 TC0CKS:TC0 时钟源选择位

0 = Fcpu

1 =

Bit2

0 = 无自动装载功能

1 =

Bit1

0 = 禁止 TC0 的信号输出,开放 P5.4 的基本输入

1 = 开放 TC0 的信号输出,禁止 P5.4 的基本输入

Bit0

0 = 禁止 PWM 功能

1 =

¾

注:当 TC0CKS=1 时,TC0 就是一个外部事件计数器。

TC0ENB:TC0 计数器

使能

:TC0 时钟源选择位。TC0X8 是 T0M 寄存器的第 2 位。

TC0RATE [2:0]

000 Fcpu/256 = Fosc/1024 Fosc/128

001 Fcpu/128 = Fosc/512 Fosc/64

… … …

110 Fcpu/4 = Fosc/16 Fosc/2

111 Fcpu/2 = Fosc/8 Fosc

注:Fcpu=Fosc/4

外部时钟来自 INT0/P0.0 引脚

ALOAD0:TC0 自动装载功能控制位

自动装载

TC0OUT:TC0 超时触发信号输出控制位

PWM0OUT: TC0 的 PWM 输出控制位

开放 PWM 功能(TC0OUT 必须为 0)

BZ0/PWM0OUT 使能位

TC0 时钟源

TC0X8 = 0 TC0X8 = 1

输出功能

输出功能 (自动禁止 PWM0OUT 功能)

LOAD0 TC0OUT PWM0OUT

8.3.3 TC0C 计数寄存器

TC0C 是一个 8 位定时/计数器,只要 TC0ENB 置“1”就开启定时器。TC0C 是个加 1 计数器,时钟源频率由

TC0RATE0~TC0RATE2 决定。当 TC0C 计到“0FFH”后,若再加 1 就会回到“00H”,产生溢出,此时,TC0 中断请求

标志被置为

TC0C 初始值=xxxx xxxx

0DBH Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

TC0C TC0C7 TC0C6 TC0C5 TC0C4 TC0C3 TC0C2 TC0C1 TC0C0

SONiX TECHNOLOGY CO., LTD Page 44 Revision 0.8

“1”,如果 TC0 中断又同时被使能(TC0IEN =1),那么系统将执行 TC0 的中断服务程序。

R/W R/W R/W R/W R/W R/W R/W R/W

Page 45

Preliminary SN8P1702A/SN8P1703A

8-bit micro-controller build-in 12-bit ADC

8.3.4 TC0 溢出时间

TC0 的速率由 TC0Rate 和编译选项 TC0_Counter 共同确定,通过设置 TC0Rate 可以确定 TC0 的时钟频率,

通过设置

TC0C

N 由编译选项 TC0_Counter 确定。

TC0_Counter N TC0C 的最大值

¾

注:TC0C 的值必须小于等于 TC0 的最大值。

例:设 Fosc = 3.58MHz,时间间隔为 10ms。

例:设 Fosc=3.58MHz,时间间隔为 1.25ms。

例:设 Fosc=3.58MHz,时间间隔为 1ms。

TC0_Counter 可以使 TC0 为 8-bit、6-bit、5-bit 或 4-bit。

的计算如下:

TC0C 初始值 = N-(TC0 中断间隔时间×输入时钟)

8-bit 256 255

6-bit 64 63

5-bit 32 31

4-bit 16 15

TC0C(74H)=256-(10ms*fcpu/64)(TC0RATE=010,TC0_Counter=8-bit, TC0X8=0)

TC0C 初始值 = 256 - (TC0 中断间隔时间 × 输入时钟)

= 256 - (10ms×3.58×10

= 256 - (10

-2

×3.58×106÷4÷64)

6

÷4÷64)

= 116

= 74H

TC0C(74H)=256-(1.25ms* fcpu /64) (TC0RATE=010,TC0_Counter=8-bit, TC0X8=1)

TC0C 初始值 = 256 - (TC0 中断间隔时间×输入时钟)

= 256 - (1.25ms×3.58×10

= 256 - (0.00125×3.58×10

6

÷4÷32)

6

÷4÷32)

= 116

= 74H

TC0C(74H)=256-(1ms* fcpu /64) (TC0RATE=010,TC0_Counter=6-bit, TC0X8=1)

TC0C 初始值 = 64 - (TC0 中断间隔时间 × 输入时钟)

= 64 - (1ms×3.58×10

= 64 - (0.001×3.58×10

6

÷4÷64)

6

÷4÷64)

= 64 - 14

= 32H

SONiX TECHNOLOGY CO., LTD Page 45 Revision 0.8

Page 46

Preliminary SN8P1702A/SN8P1703A

)

(

)

)

(

)

)

(

)

)

(

)

8-bit micro-controller build-in 12-bit ADC

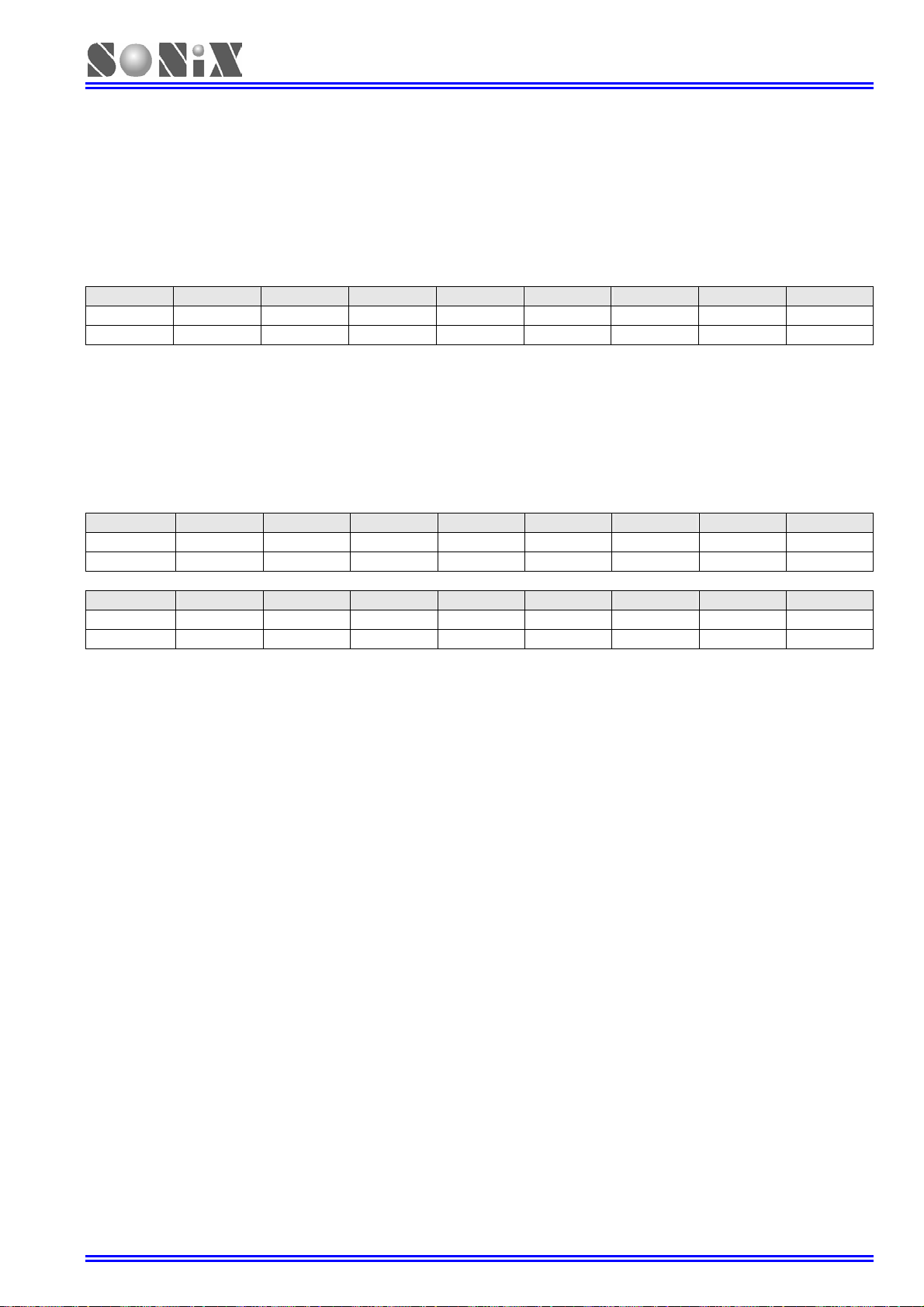

TC0_Counter=8-bit, TC0X8=0

TC0RATE TC0CLOCK

000 Fcpu/256 73.2 ms 286us 8000 ms 31.25 ms

001 Fcpu/128 36.6 ms 143us 4000 ms 15.63 ms

010 Fcpu/64 18.3 ms 71.5us 2000 ms 7.8 ms

011 Fcpu/32 9.15 ms 35.8us 1000 ms 3.9 ms

100 Fcpu/16 4.57 ms 17.9us 500 ms 1.95 ms

101 Fcpu/8 2.28 ms 8.94us 250 ms 0.98 ms

110 Fcpu/4 1.14 ms 4.47us 125 ms 0.49 ms

111 Fcpu/2 0.57 ms 2.23us 62.5 ms 0.24 ms

TC0_Counter=6-bit, TC0X8=0

TC0RATE TC0CLOCK

000 Fcpu/256 18.3 ms 286us 2000 ms 31.25 ms

001 Fcpu/128 9.15 ms 143us 1000 ms 15.63 ms

010 Fcpu/64 4.57 ms 71.5us 500 ms 7.8 ms

011 Fcpu/32 2.28 ms 35.8us 250 ms 3.9 ms

100 Fcpu/16 1.14 ms 17.9us 125 ms 1.95 ms

101 Fcpu/8 0.57 ms 8.94us 62.5 ms 0.98 ms

110 Fcpu/4 0.285 ms 4.47us 31.25 ms 0.49 ms

111 Fcpu/2 0.143 ms 2.23us 15.63 ms 0.24 ms

TC0_Counter=5-bit, TC0X8=0

TC0RATE TC0CLOCK

000 Fcpu/256 9.15 ms 286us 1000 ms 31.25 ms

001 Fcpu/128 4.57 ms 143us 500 ms 15.63 ms

010 Fcpu/64 2.28 ms 71.5us 250 ms 7.8 ms

011 Fcpu/32 1.14 ms 35.8us 125 ms 3.9 ms

100 Fcpu/16 0.57 ms 17.9us 62.5 ms 1.95 ms

101 Fcpu/8 0.285 ms 8.94us 31.25 ms 0.98 ms

110 Fcpu/4 0.143 ms 4.47us 15.63 ms 0.49 ms

111 Fcpu/2 71.25 us 2.23us 7.81 ms 0.24 ms

TC0_Counter=4-bit, TC0X8=0

TC0RATE TC0CLOCK

000 Fcpu/256 4.57 ms 286us 500 ms 31.25 ms

001 Fcpu/128 2.28 ms 143us 250 ms 15.63 ms

010 Fcpu/64 1.14 ms 71.5us 125 ms 7.8 ms

011 Fcpu/32 0.57 ms 35.8us 62.5 ms 3.9 ms

100 Fcpu/16 0.285 ms 17.9us 31.25 ms 1.95 ms

101 Fcpu/8 0.143 ms 8.94us 15.63 ms 0.98 ms

110 Fcpu/4 71.25 us 4.47us 7.81 ms 0.49 ms

111 Fcpu/2 35.63 us 2.23us 3.91 ms 0.24 ms

高速模式

最大溢出间隔时间 单步间隔时间 = max/256 最大溢出间隔时间 单步间隔时间 = max/256

高速模式

最大溢出间隔时间 单步间隔时间 = max/64 最大溢出间隔时间 单步间隔时间 = max/64

高速模式

最大溢出间隔时间 单步间隔时间 = max/32 最大溢出间隔时间 单步间隔时间 = max/32

高速模式

最大溢出间隔时间 单步间隔时间 = max/16 最大溢出间隔时间 单步间隔时间 = max/16

(Fcpu = 3.58MHz / 4

(Fcpu = 3.58MHz / 4

(Fcpu = 3.58MHz / 4

(Fcpu = 3.58MHz / 4

低速模式