Page 1

1

Eddy DK

Programmer Guide

Ver 2.1.0.3

2009. 10.22

Page 2

2

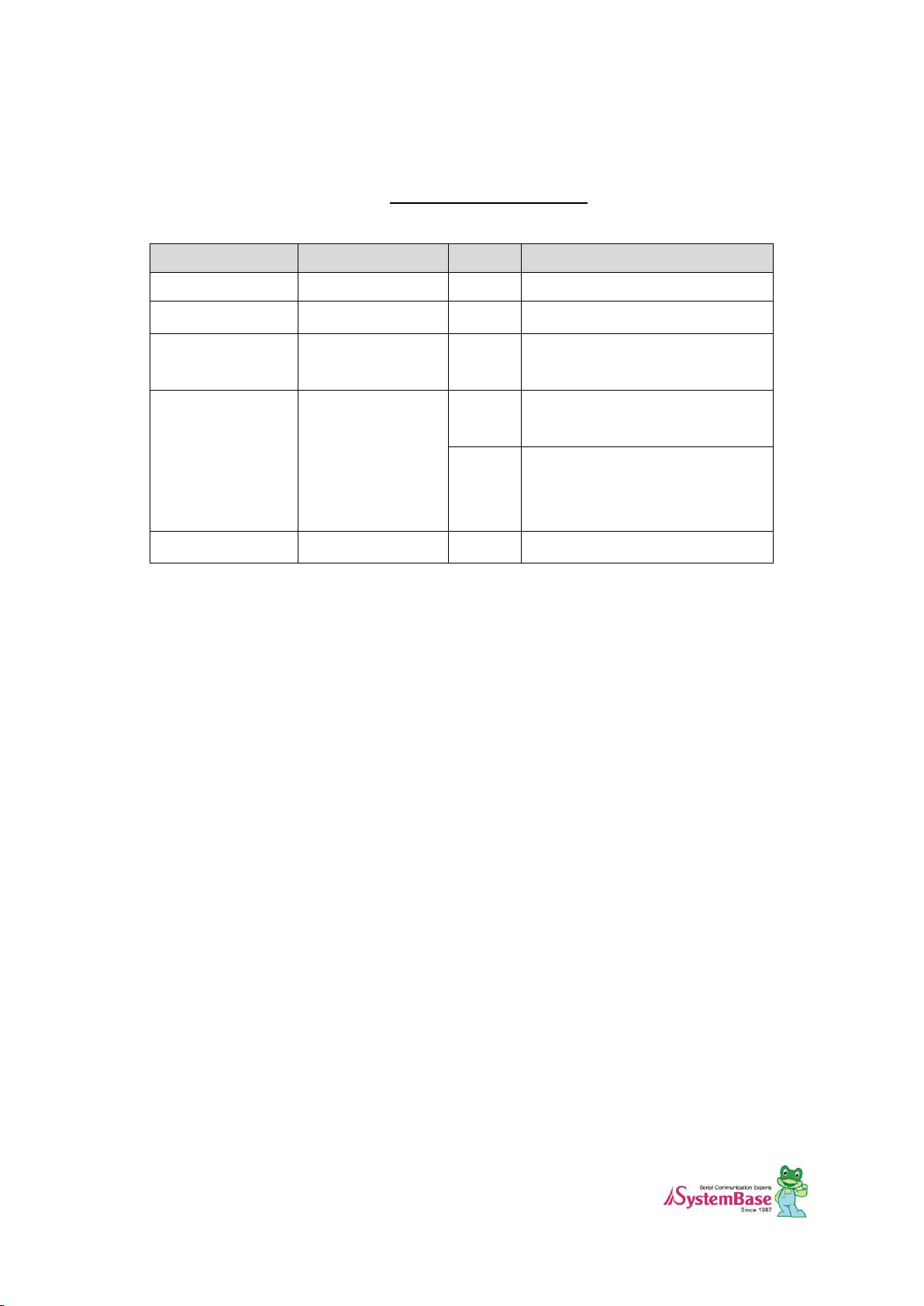

Revision Date

Document Version

Pages

Description

Feb-5-2009

2.1.0.1

All

Initial release by shlee

Sep-10-2009

2.1.0.2

All

Added WiFi

Oct-14-2009

2.1.0.3

11

J2 pin33 PC12 PC13

J2 pin35 PC13 PC12

Oct-22-2009

2.1.0.3

17,18,19

J2 pin33 PC12 PC13

J2 pin35 PC13 PC12

18,19

J2 pin33 J9_26 J9_33

J2 pin34 J9_25 J9_34

J2 pin33 J9_24 J9_35

Nov-23-2009

2.1.0.3

2,4,6

Added S4M

Revision History

Page 3

3

Table of Contents

Chapter 1. Introduction ................................................................................................................. 5

1.1 About this document ........................................................................................................................ 5

1.2 Who should read this document? .................................................................................................... 5

1.3 Document organization .................................................................................................................... 6

1.4 Eddy-DK Related Documents .......................................................................................................... 7

1.5 Technical Support ............................................................................................................................ 9

Chapter 2. Getting Started ......................................................................................................... 10

2.1 What can you do with Eddy DK ? .................................................................................................. 10

2.2 Eddy-DK Package Contents .......................................................................................................... 10

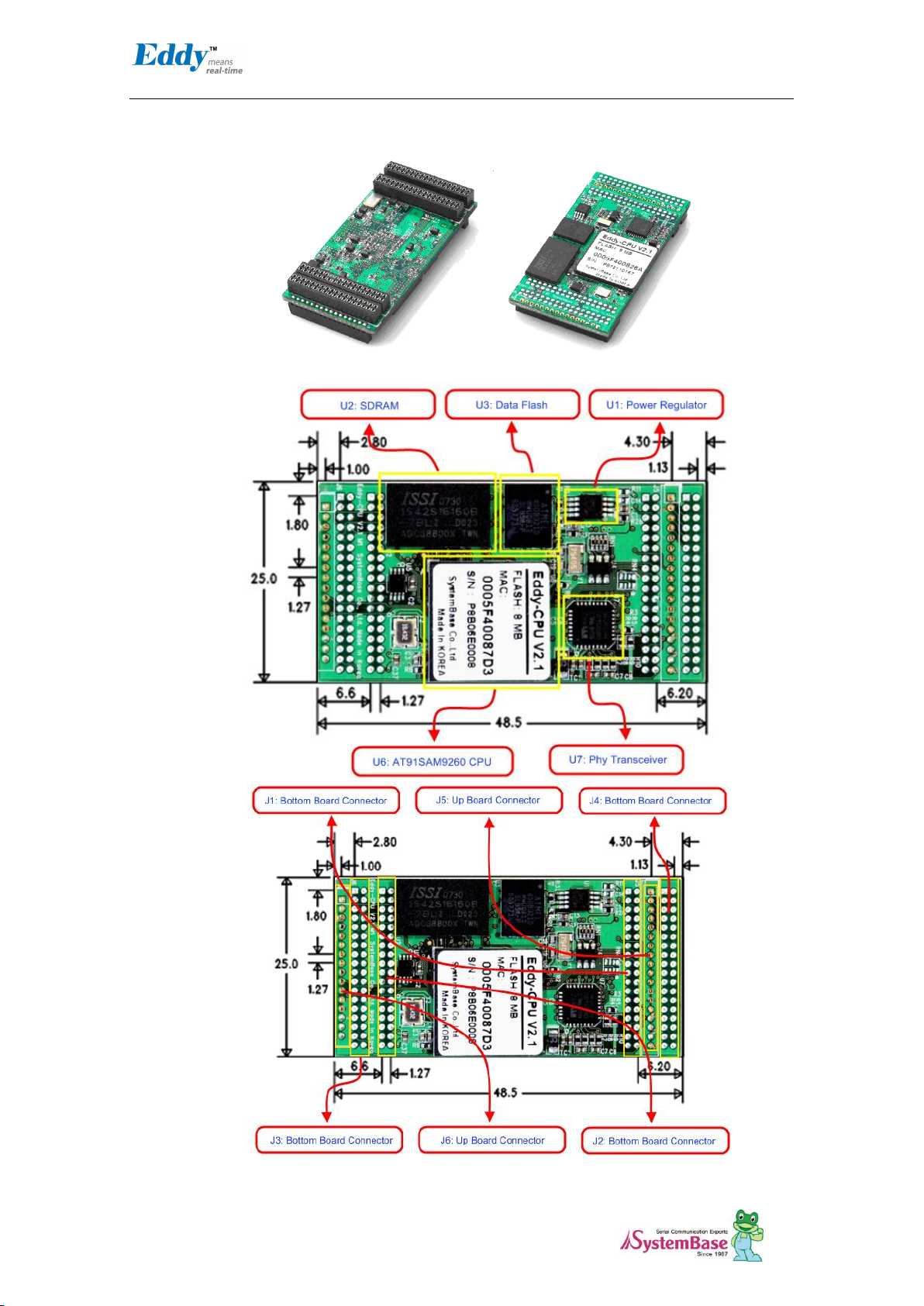

2.3 Eddy-CPU v2.1 ............................................................................................................................... 11

2.4 Eddy-DK v2.1 ................................................................................................................................. 25

2.5 Eddy-S4M v2.1 ............................................................................................................................... 40

2.6 Eddy-S4M-DK v2.1 ........................................................................................................................ 50

2.7 Eddy-S4M-JiG v2.1 ........................................................................................................................ 59

Chapter 3. Development Environment ........................................................................................ 63

3.1 Source code directory structure .................................................................................................... 63

3.2 Language ........................................................................................................................................ 64

3.3 Development Environment ............................................................................................................. 64

3.4 Installing on Windows OS .............................................................................................................. 64

3.5 Installation of Cygwin ..................................................................................................................... 64

3.6 Configuration of Windows Environment Variables ........................................................................ 67

3.7 Installation of Toolchain ................................................................................................................. 67

3.8 Installation of Eddy DK Source ...................................................................................................... 67

3.9 Installing on Linux ........................................................................................................................... 68

3.10 Installation of Toolchain ................................................................................................................. 68

3.11 Installation of Eddy DK Source ...................................................................................................... 69

3.12 Removing Development Environment ............................................................................................ 69

3.13 Removing Windows Development Environment ............................................................................ 69

3.14 Removing Linux Development Environment .................................................................................. 69

Chapter 4. Compiling of Application Program ............................................................................ 70

4.1 Program Type ................................................................................................................................. 70

4.2 Writing Application Program .......................................................................................................... 72

4.3 Writing Makefile .............................................................................................................................. 72

4.4 Application Program Compile ........................................................................................................ 73

4.5 Compiling on Windows .................................................................................................................. 73

4.6 Compiling on Linux ......................................................................................................................... 73

4.7 Compiling with LemonIDE .............................................................................................................. 74

Page 4

4

4.8 Running Application on Eddy ......................................................................................................... 74

4.9 Uploading and Executing on Eddy ................................................................................................ 74

4.10 Execute a file on Booting of Eddy ................................................................................................. 75

Chapter 5. Creating Firmware .................................................................................................... 76

5.1 How to Create a Firmware ............................................................................................................. 76

5.2 Firmware Upgrade .......................................................................................................................... 78

Chapter 6. Library Introduction ................................................................................................... 81

6.1 Introduction ..................................................................................................................................... 81

6.2 Makefile .......................................................................................................................................... 81

6.3 System functions ............................................................................................................................ 81

6.4 Eddy Environment Function ........................................................................................................... 82

6.5 Serial functions ............................................................................................................................... 84

6.6 Ethernet functions .......................................................................................................................... 87

6.7 GPIO Functions .............................................................................................................................. 92

6.8 ADC Function ................................................................................................................................. 98

6.9 RTC Function .................................................................................................................................. 99

6.10 Debugging Function ....................................................................................................................... 99

Chapter 7. Eddy Software ........................................................................................................ 101

7.1 Software Structure Diagram ......................................................................................................... 101

7.2 Main Applications ......................................................................................................................... 102

7.3 eddy.c Application ........................................................................................................................ 102

7.4 Pinetd.c Application ..................................................................................................................... 102

7.5 Other Applications ........................................................................................................................ 102

Chapter 8. Handling HTML & CGI ............................................................................................ 103

8.1 WEB Configuration ....................................................................................................................... 103

8.2 Example of HTML Code ............................................................................................................... 103

8.3 Example CGI Code ....................................................................................................................... 104

Chapter 9. Appendix ................................................................................................................ 107

9.1 System recovery via Bootloader .................................................................................................. 107

9.2 System recovery via USB............................................................................................................. 112

9.3 Product Specification ................................................................................................................... 118

9.4 Ordering Infomation ...................................................................................................................... 123

Page 5

Chapter 1. Introduction

5

Chapter 1. Introduction

This chapter explains about this manual and introduces the related documents and support.

1.1 About this document

This manual explains about how a programmer can develop a customized application for Eddy module and how this

application can be uploaded and executed on the module. To help programmers with this work, information on

Eddy's operating system and API functions for convenient source writing is supplied.

After reading this document, a programmer can write his or her own application and execute it on the module.

1.2 Who should read this document?

This document is designed for programmers who wish to develop a new application using Eddy DK. It is strongly

recommended that the programmer read this document before starting any programming work. If you are an

administrator or an end user who just needs to apply the module into practical applications, you do not need to read

this document. User's Guide will be helpful in that case. This manual deals with the complete process of writing

source codes and making a firmware that can be uploaded and executed on Eddy module.

Page 6

Chapter 1. Introduction

6

1.3 Document organization

Chapter 1. Introduction is a preface with general information and introductory notices.

Chapter 2. Getting Started gives brief information needed before starting programming work.

Chapter 3. Writing Application explains about the process of writing a customized application and related work..

Chapter 4. Compiling Application deals with the process of compiling your application with Makefile.

Chapter 5. Creating Firmware helps you converting a compiled application into a firmware that can be accepted by

Eddy module.

Chapter 6. Library explains about the library and API functions you can use while programming and application.

Chapter 7. Eddy Software shows how to implement simple TCP/IP and serial routines using example source codes

that are included in the development kit.

Chapter 8. Handling HTML & CGI provides a guide for integrating your own applications with Eddy's web interface.

Chapter 9. Appendix provides programming notes and a list of default utilities.

Page 7

Chapter 1. Introduction

7

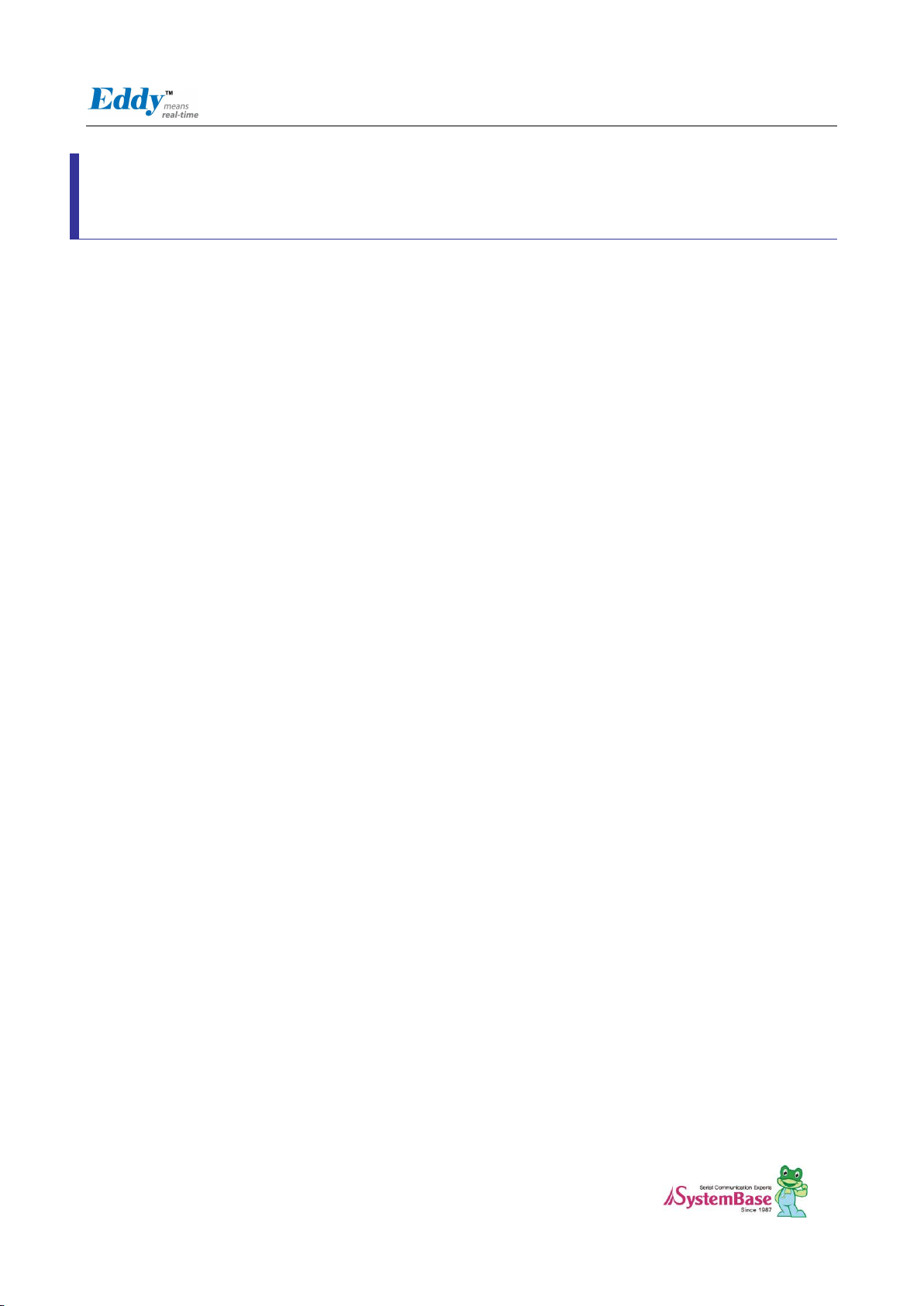

Document Name

Description

User Guide

Integration, configuration, and management of Eddy for the

administrator

Programmer’s Guide

Programmer’s application development guide, including in-depth

approach to compiling, linking, and creating firmware

API reference is also included with a list of available functions

for customized application programming

LemonIDE Manual

Guide for primary function of each tool contained in LemonIDE on

Windows and Linux.

Portview User Manual

Guide for SystemBase device server management application

Portview

COM Port Redirector User

Manual

Guide for SystemBase COM Port Redirector

TestView User Manual

Guide for TestView application for testing Eddy serial port and lan

port.

Document Name

Description

Eddy-CPU Spec Sheet

Specifications for Eddy CPU and DK board.

Eddy-S4M Spec Sheet

Eddy-S4M spec description

Eddy-WiFi Spec Sheet

Eddy-WiFi module spec description

LemonIDE Spec Sheet

integrated development environment description

1.4 Eddy-DK Related Documents

The following table summarizes documents included in the Eddy-DK document set.

If you need brief information on Eddy or embedded device servers in general, please visit our corporate website at

http://www.sysbas.com/. You can view and/or download documents related to Eddy as well as latest software and

firmware updates. Available resources are as follows:

Page 8

Chapter 1. Introduction

8

Lemonix Spec Sheet

Lemonix RTOS description

Eddy White Paper

An introductory reading for anyone new to embedded device server.

Deals with background, history, market environment, and technology

All documents are updated promptly, so check for the recent document update. The contents in these documents

are subject to change without any notice in advance.

Page 9

Chapter 1. Introduction

9

1.5 Technical Support

There are three ways you can get a technical support from SystemBase.

First, visit our website http://www.sysbas.com/ and go to ‘Technical Support’ menu. There you can read FAQ

and ask your own question as well.

Second, you can e-mail our technical support team. The mail address is tech@sysbas.com. Any kind of inquiries,

requests, and comments are welcome.

Finally, you can call us at the customer center for immediate support. Our technical support team will kindly help you

get over with the problem.

The number to call is 82-2-855-0501 (Extension number 225). Do not forget to dial the extension number after getting

a welcome message.

Copyright 2007 SystemBase Co., Ltd. All rights reserved.

Homepage: http://www.sysbas.com/

Tel: +82-2-855-0501

Fax: +82-2-855-0580

1601, DaeRyung Post Tower 1, 212-8, Guro-dong, Guro-gu, Seoul, Korea

Page 10

Chapter 2. Getting Started

10

Chapter 2. Getting Started

This chapter explains about packaging and installation, and discusses key features of Eddy-DK.

2.1 What can you do with Eddy DK ?

Eddy DK is designed to help programmers to develop a customized application that can be applied to

Eddy module easier and faster. It has been a time-consuming and burdensome work to port an

operating system and develop an application on a new hardware. Eddy module and Software

Development Kit makes this work easy.

Eddy DK is different with other device servers in which it can run customized applications. Users can

upload most existing socket/serial communication applications that are running on the Linux

environment. This openness allows users to apply wide variety of functions into the module with

relatively less restrictions.

Eddy DK supports IDE (LemonIDE) and SDK environment to help programmers to execute their own

applications on the module. Programmers can easily write applications using the Linux environment,

with the help of SDK and example source codes. Cross-compiler running on the standard Linux

environment helps your applications to run on the Eddy module. Embedded Linux on Eddy can

provide stable and rapid environment for your applications.

2.2 Eddy-DK Package Contents

Eddy-DK includes Eddy module.

Eddy-DK package contains as follows. Make sure following contents are included in the Eddy Serial

DK Package.

- Case of Eddy-DK (Eddy-CPU v2.1 1ea, Eddy-DK v2.1board 1ea)

- Case of Eddy-S4M-DK (Eddy-S4M v2.1 1ea, Eddy-S4M-DK board 1ea, (Option : Eddy-S4M-JIG))

- 1EA , Serial cable

- 1EA , LAN cable

- 1EA, USB A to B Cable

- 1EA , Power adaptor

- 1EA , CD (SystemBase SDK, LemonIDE, compile environment, utilities, manuals)

Page 11

Chapter 2. Getting Started

11

2.3 Eddy-CPU v2.1

Page 12

Chapter 2. Getting Started

12

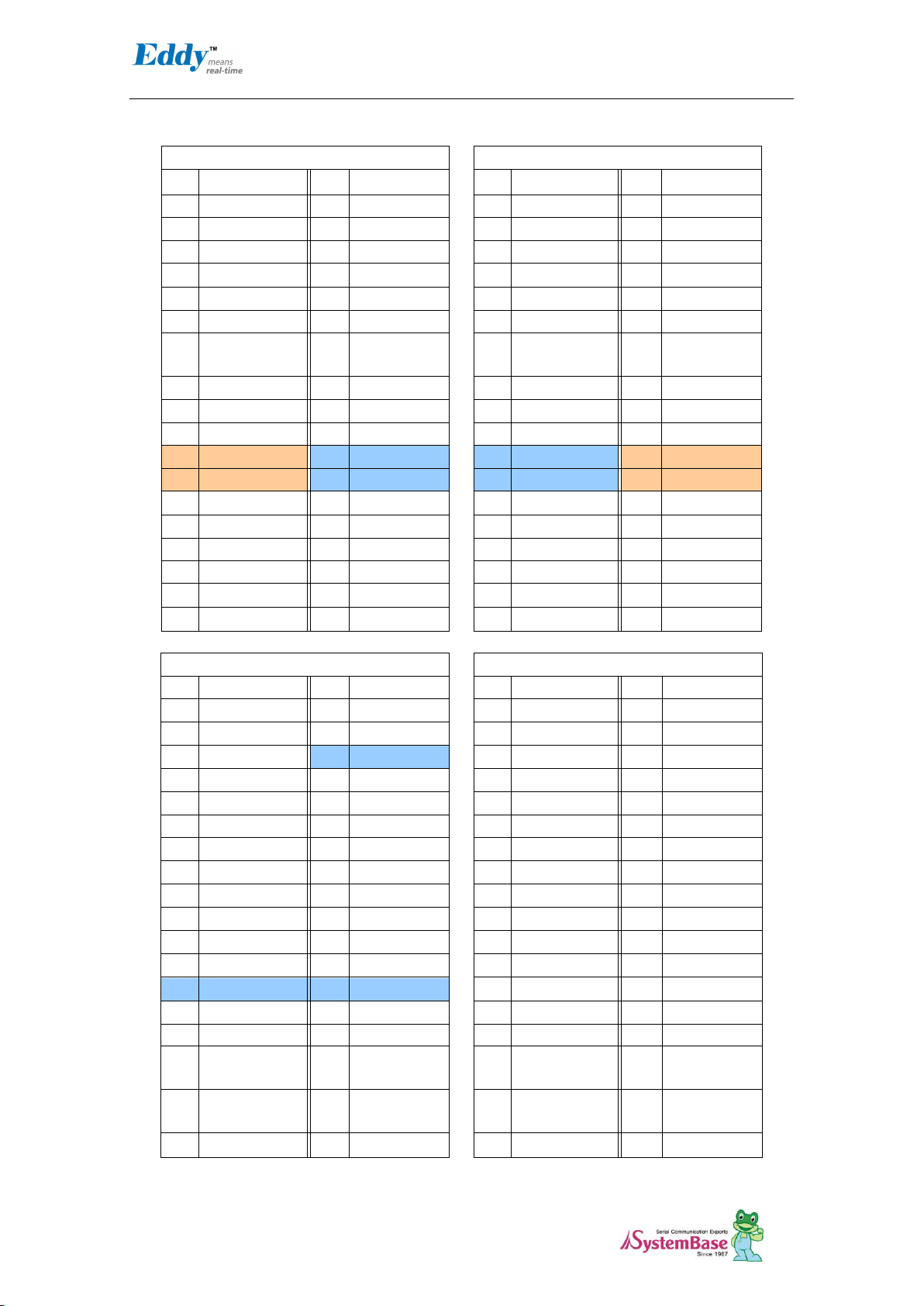

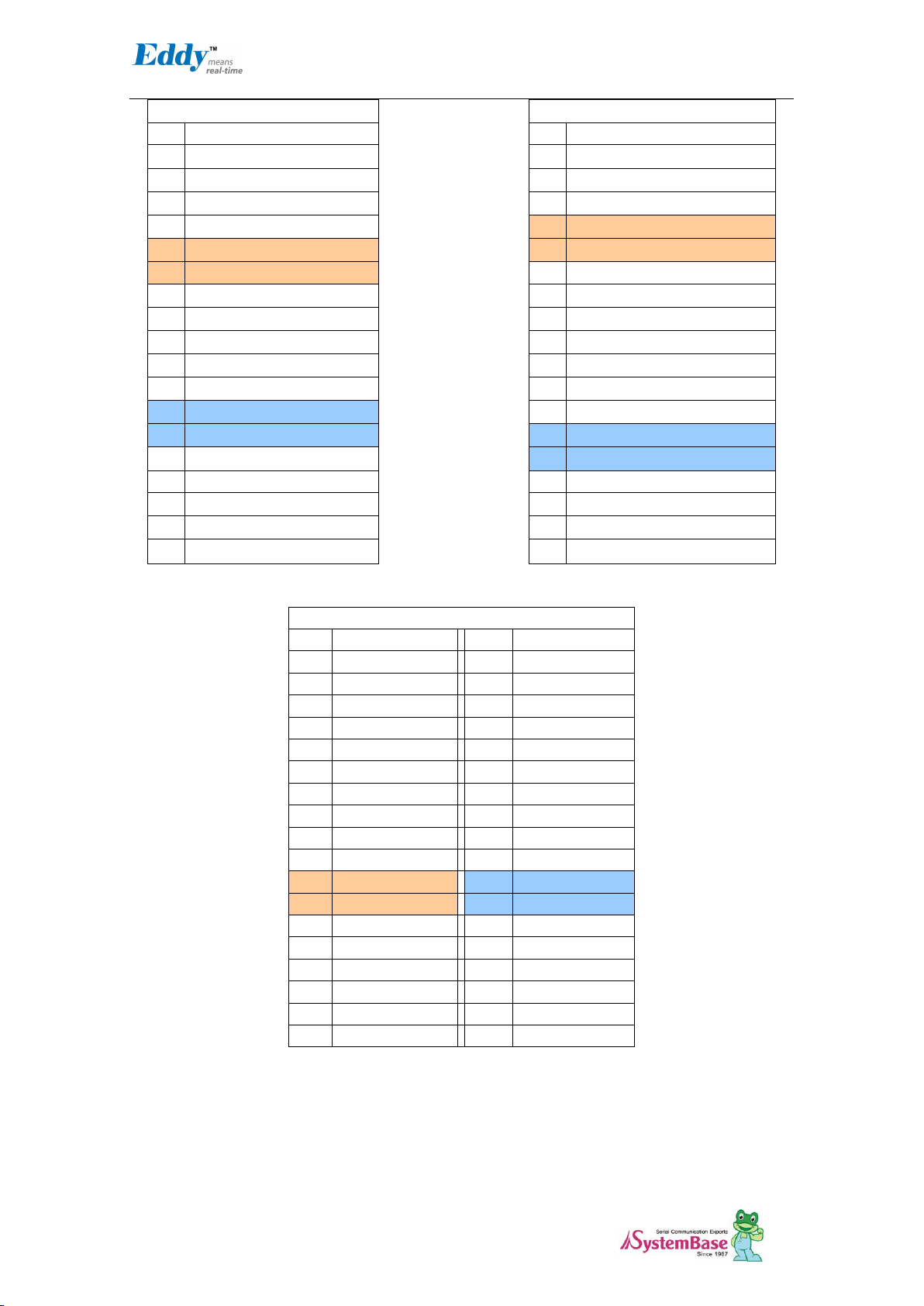

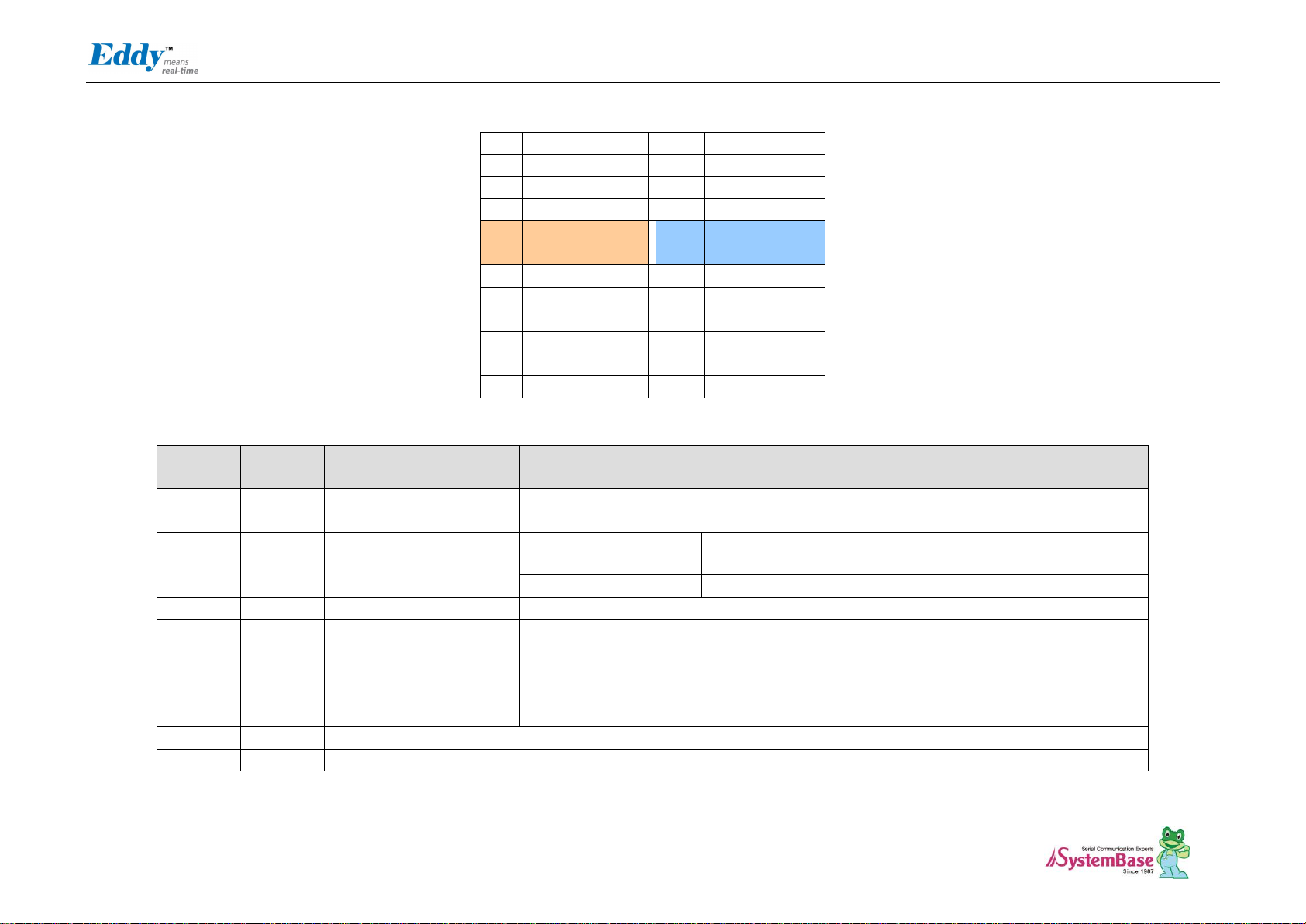

J1 J2

Pin

Signal Name

Pin

Signal Name

Pin

Signal Name

Pin

Signal Name

1

PA5

2 PA4

1 A15

2 A14

3

PC5

4 PC19

3 A13

4 A12 5 PC21

5 PC23

5 A11

5 A10

7

HDMA

8

NC

7 A9

8

A8

9

HDPA

10

DDM

9 A7

10

A6

11

PC26

12

DDP

11

A5

12

A4

13

PC4 (RDY#)

14

PC16

(nRESET)

13

A3

14

A2

15

ICE_NTRST

16

RTCK

15

A1

16

A0

17

TDO

18

TMS

17

PC9

18

NWE

19

TDI

20

TCK

19

FPG

20

NRD

21

3.3V

22

GND

21

GND

22

3.3V

23

3.3V

24

GND

23

GND

24

3.3V

25

PB29 (CTS1)

26

PB28 (RTS1)

25

D7

26

D6

27

PB6 (TXD1)

28

PB7 (RXD1)

27

D5

28

D4

29

A20

30

A19

29

D3

30

D2

31

LAN_Speed

32

LAN_lLink

31

D1

32

D0

33

LAN_RX-

34

LAN_RX+

33

PC13

34

JTAGSEL

35

LAN_TX-

36

LAN_TX+

35

PC12

36

NC

J3 J4

Pin

Signal Name

Pin

Signal Name

Pin

Signal Name

Pin

Signal Name

1

PID0

2 PID1

1 PB12

2 PB13

3

PID2

4 PID3

3 PB30

4 PB31

5

PID4

5 GND

5 PB0

5 PC22

7

PC14

8 PC17

7 PB1

8 PB16

9

PC18

10

PC8 (RTS3)

9 PB2

10

PB17

11

PC20

12

PC10 (CTS3)

11

PB3

12

PB18

13

PA22

14

PC15 (IRQ1)

13

BHDM

14

PB19

15

PB8

16

PB9 (RXD2)

15

BHDP

16

PB20

17

PB10

18

PB11(RXD3)

17

A16

18

PB21

19

PC0

20

PC1 (AD1)

19

A17

20

A18

21

PC2

22

PC3 (AD3)

21

D8

22

D9

23

PB14 (DRXD)

24

PB15 (DTXD)

23

D10

24

D11

25

GND

26

GND

25

D12

26

D13

27

BMS

28

NRST

27

D14

28

D15

29

PB23 / DCD0

30

PB5 / RXD0

29

TWD

30

TCK

31

PB4 / TXD0

32

PB24 / DTR0

31

NANDOE

32

NAND_CLE /

A22

33

PB22 / DSR0

34

PB26 / RTS0

33

NANDWE

34

NAND_ALE /

A21

35

PB27 / CTS0

36

PB25 / RI0

35

NC

36

NC

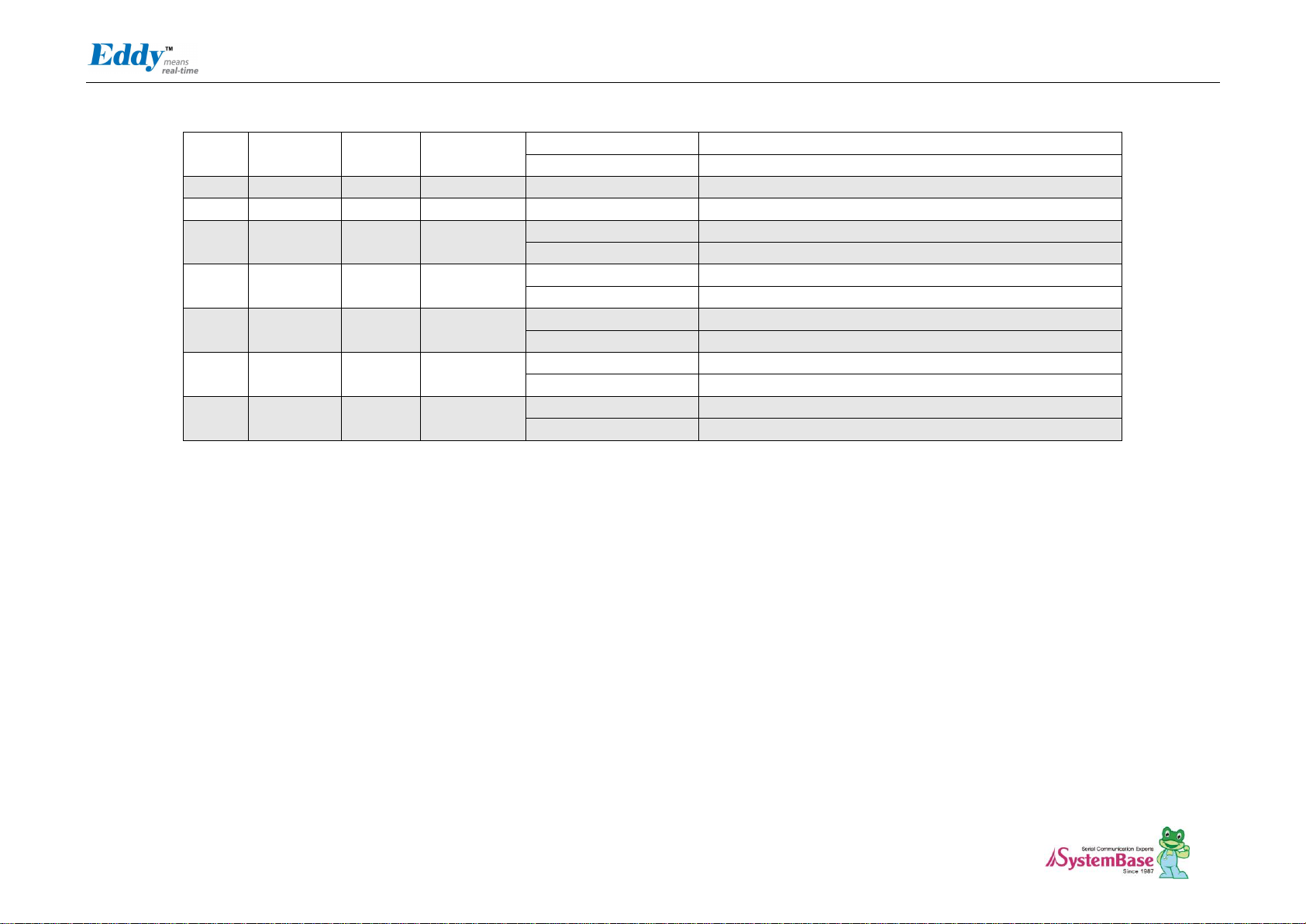

Eddy-CPU v2.1 Pin Assignment

Page 13

Chapter 2. Getting Started

13

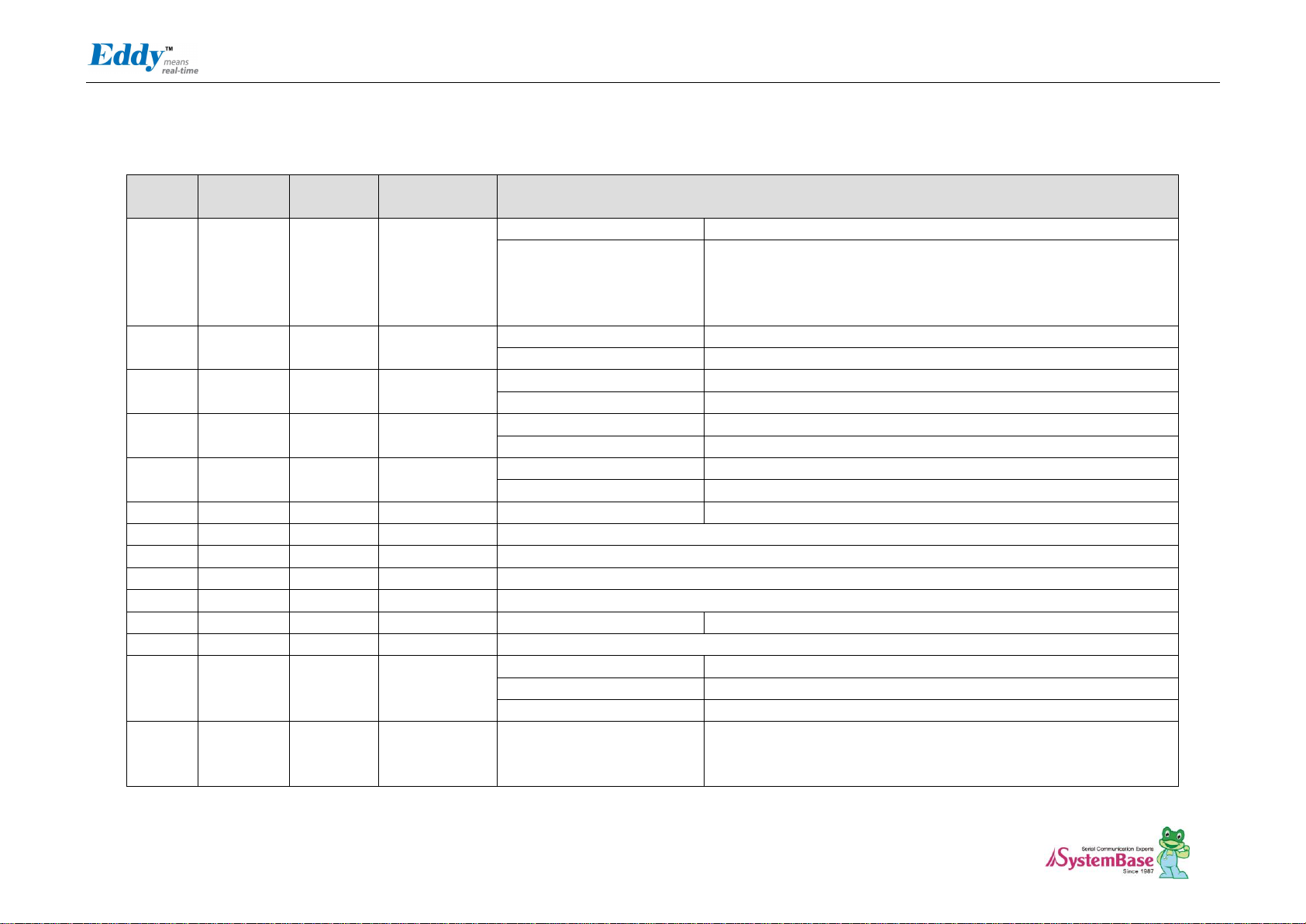

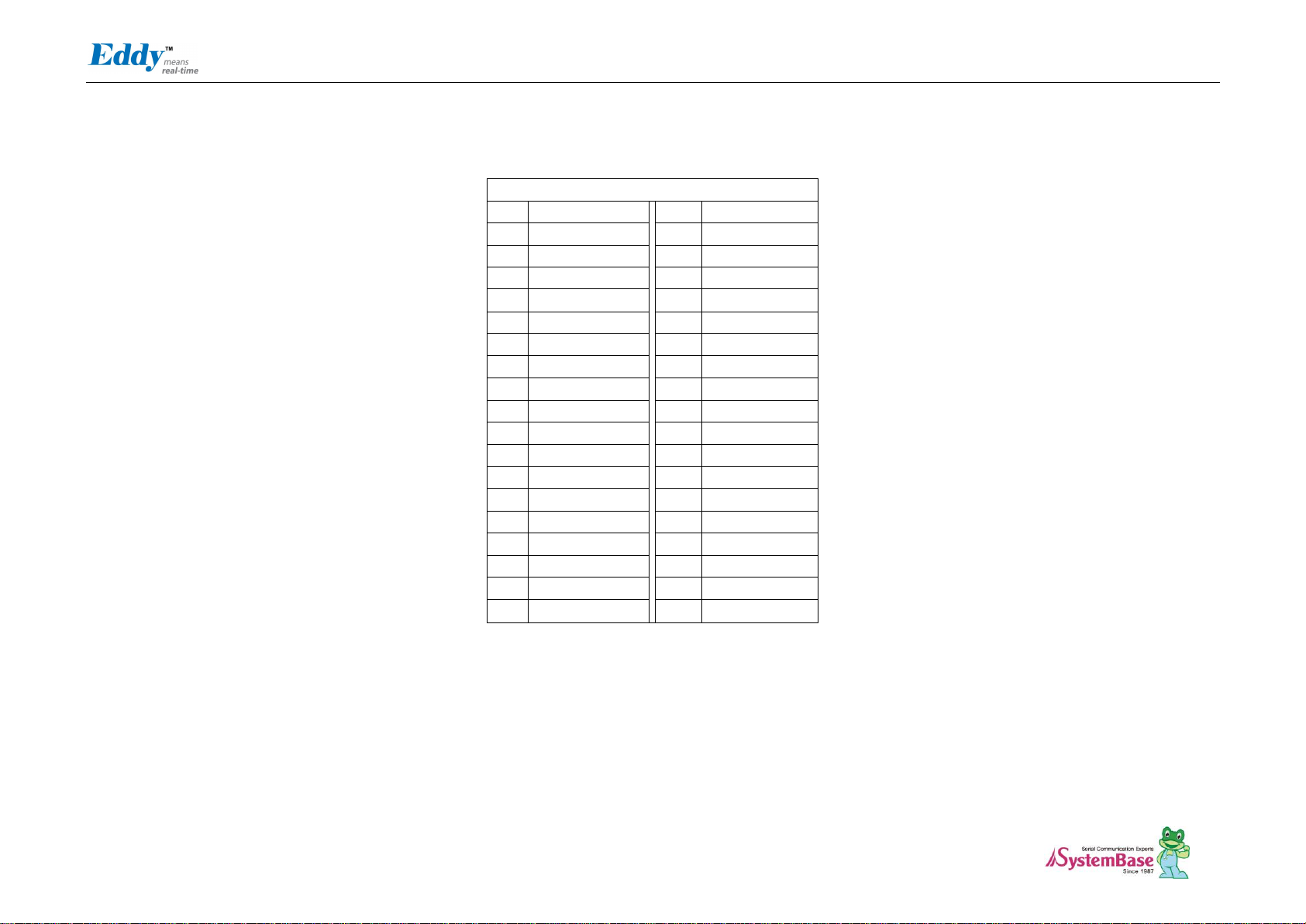

J5

J6

Pin

Signal Name

Pin

Signal Name

1

PB0

2

PB1

1

NC

3

PB2

2

NC

4

PB3

3

3.3V

5

3.3V

4

3.3V

6

3.3V

5 PC25 / BT_Factory

7

BHDM, USB Host Data(-)

6

PB10 / TXD3

8

BHDP, USB Host Data(+)

7

PB11 / RXD3

9

PA31 / TXD4

8

PC8 / RTS3

10

PA30 / RXD4

9

PC10 / CTS3

11

NRST

10

PC24 / BT_MODE

12

GND

11

NRST

13

GND

12

GND

14

PA9 / WPID0

13

GND

15

PC6 / WPID1

14

NC

16

PC7 / WPID2

15

NC

17

NC

16

NC

18

NC

J1

Pin

Signal Name

Pin

Signal Name

1

PA5

2

PA4

3

PC5

4

PC19

5

PC21

5

PC23

7

HDMA

8

NC

9

HDPA

10

DDM

11

PC26

12

DDP

13

PC4 (RDY#)

14

PC16 (nRESET)

15

ICE_NTRST

16

RTCK

17

TDO

18

TMS

19

TDI

20

TCK

21

3.3V

22

GND

23

3.3V

24

GND

25

PB29 (CTS1)

26

PB28 (RTS1)

27

PB6 (TXD1)

28

PB7 (RXD1)

29

A20

30

A19

31

LAN_Speed

32

LAN_lLink

33

LAN_RX-

34

LAN_RX+

35

LAN_TX-

36

LAN_TX+

J1 Specifications

Page 14

Chapter 2. Getting Started

14

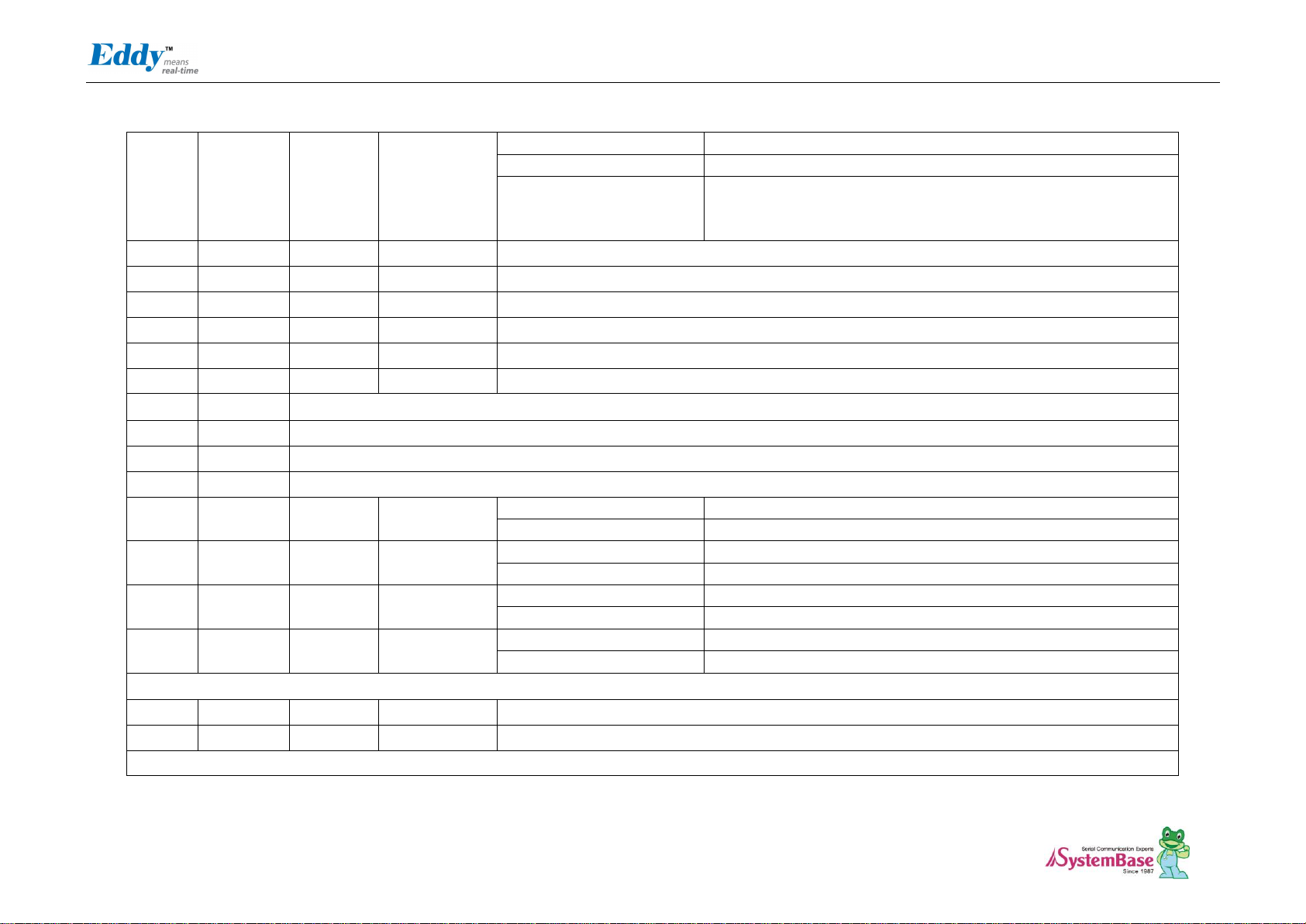

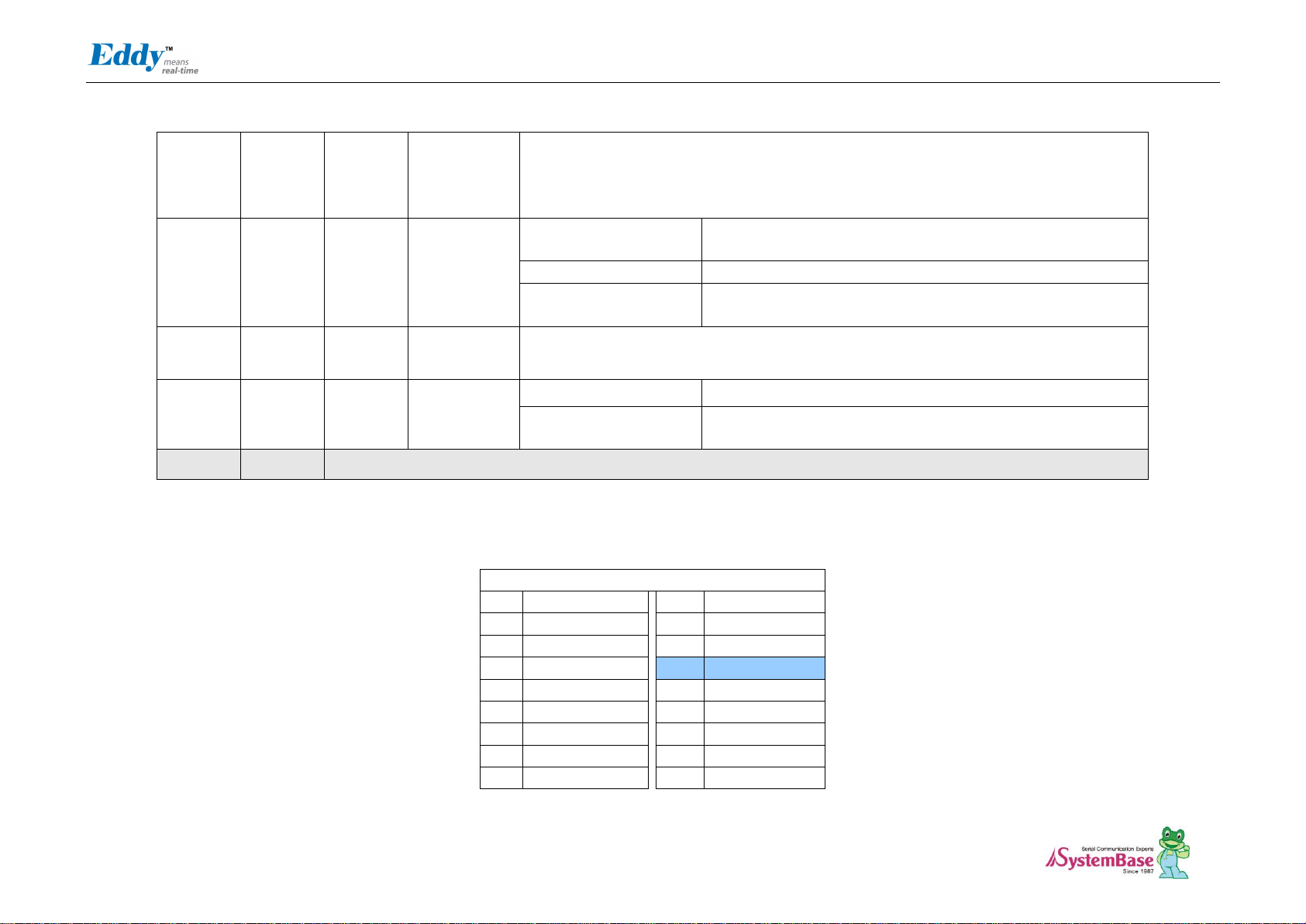

Pin No

Name

DK v2.1

Pin No

Expansion

Header Pin No

Description

1

PA5

J10_1

J4_2

Peripheral A : CTS2

UART #2 Clear to Send Signal

Peripheral B : MCBD1

Disabled.

Data Flash connected with SPI0 is used for Eddy-CPU v2.1. For this

reason SPI0 and MCDB0, MCDB3, and MCCDB signals, multiplexing,

cannot be used, thus Multimedia Card Slot B is disabled.

2

PA4

J10_2

J4_1

Peripheral A : RTS2

UART #2 Request to Send Signal

Peripheral B : MCDB2

Disabled.

3

PC5

J10_3

J4_12

Peripheral A : A24

External Address Bus

Peripheral B : SPI1_NPCS1

SPI1(Serial Peripheral Interface) Peripheral Chip Select 1

4

PC19

J10_4

J4_24

Peripheral A : A24

Multimedia Card Slot B Data

Peripheral B : SPI1_NPCS2

SPI1(Serial Peripheral Interface) Peripheral Chip Select 2

5

PC21

J10_5

J4_26

Peripheral A : D21

External Data bus

Peripheral B : EF100

Ethernet(WAN) Force 100Mbit/sec.

6

PC23

J10_6

J4_28

Peripheral A : D23

External Data Bus

7

HDMA

J10_7

J1_27

USB Host Port A Data -

8

NC

J10_8

--

Not Connect

9

HDPA

J10_9

J1_29

USB Host Port A Data +

10

DDM

J10_10

-

USB Device Port Data -

11

PC26

J10_11 - D26

External Data Bus

12

DDP

J10_12

-

USB Device Port Data +

13

PC4

(RDY#)

J10_13

J4_11

Eddy-DK v2,1 : RDY#(OUT)

Ready signal. Output signal for CPU operation status

Peripheral A : A23

External Address Bus

Peripheral B : SPI1_NPCS2

SPI1(Serial Peripheral Interface) Peripheral Chip Select 2

14

PC16

(nRESET)

J10_14

J4_21

Eddy-DK v2,1 : nRESET#(IN)

Polling Input signal continually from External Reset key, implement as

below with checking the constant time of "Low."

Less than 5 seconds: General reset function.

J1 Pin Description

Page 15

Chapter 2. Getting Started

15

More than 5 seconds: Factory Default function.

Peripheral A : D16

External Data Bus

Peripheral B : SPI0_NPCS2

Disabled

SPI0_SPCK, SPI0_MISO, and SPI0_MOSI signals for SPI0 are disabled

as they are not connected externally.

15

ICE_NTRST

J10_15

J7_3

ICE Test Reset Signal

16

RTCK

J10_16

J7_11

Return Test Clock

17

TDO

J10_17

J7_13

Test Data Out

18

TMS

J10_18

J7_7

Test Mode Select

19

TDI

J10_19

J7_5

Test Data In

20

TCK

J10_20

J7_9

Test Clock

21

3.3V

3.0V to 3.6V power input

22

GND

Ground

23

3.3V

3.0V to 3.6V power input

24

GND

Ground

25

PB29

J10_25

J2_30

Peripheral A : CTS1

USART1 Clear To Send

Peripheral B : ISI_VSYNC

Image Sensor Vertical Synchronization

26

PB28

J10_26

J2_29

Peripheral A : RTS1

USART1 Request To Send

Peripheral B : ISI_PCK (IN)

Image Sensor Pixel Clock Provided by the Image Sensor

27

PB6

J10_27

J2_7

Peripheral A : TXD1

USART1 Transmit Data

Peripheral B : TCLK1

Timer Counter ch1 External CLK IN

28

PB7

J10_28

J2_8

Peripheral A : RXD11

USART1 Receive Data

Peripheral B : TCLK2

Timer Counter ch2 External CLK IN

Address Bus

29

A20

J10-29

J1_31

Address Bus

30

A19

J10_30

J1_32

Address Bus

Ethernet 10/100 (Auto MDI/MDIX)

Page 16

Chapter 2. Getting Started

16

31

LED_Speed

J10_31

-

LAN connection speed

Speed

Pin State

LED Definition

10Base-T

H

OFF

100Base-TX

L

ON

32

LED_Link

J10_32

-

LAN connection status

Link/Activity

Pin State

LED Definition

No Link

H

OFF

Link L ON

Activity

Toggle

Blinking

33

LAN_RX-

J10_33 - CPU 내부 Ethernet PHY(WAN)의 Physical receive or transmit signal (- differential)

34

LAN_RX+

J10_34 - CPU 내부 Ethernet PHY(WAN)의 Physical receive or transmit signal (+ differential)

35

LAN_TX-

J10_35 - Physical transmit of CPU Internal Ethernet PHY(WAN) or receive signal (- differential)

36

LAN_TX+

J10_36 - Physical transmit of CPU Internal Ethernet PHY(WAN) or receive signal (+ differential)

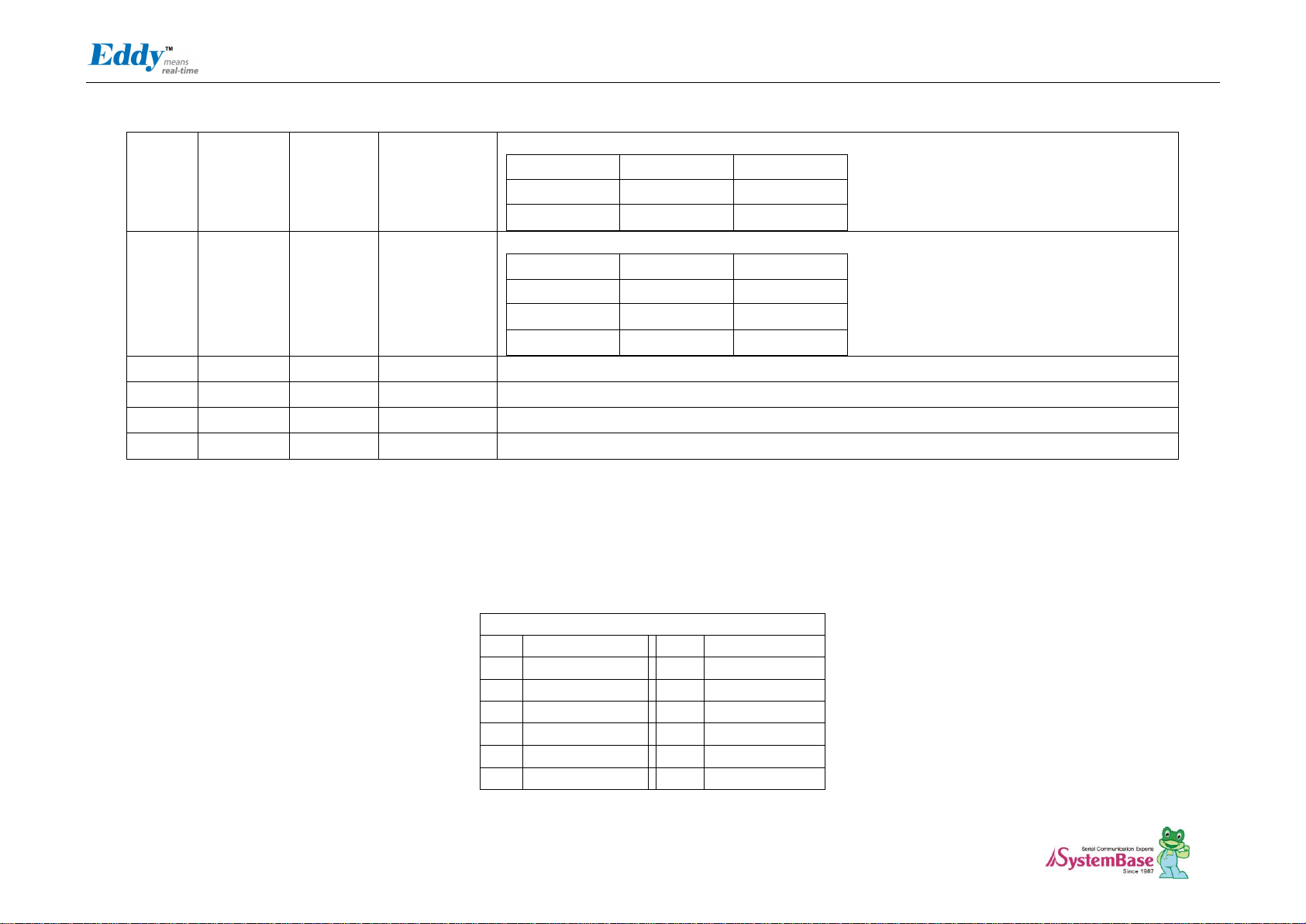

J2

Pin

Signal Name

Pin

Signal Name

1

A15

2

A14

3

A13

4

A12

5

A11

5

A10

7

A9

8

A8

9

A7

10

A6

11

A5

12

A4

J2 Specifications

Connect USB cable to J1 while the jumper is connected to J2, so that applications can be compiled, linked, created, and uploaded to the Eddy-CPU module. (Please refer to

Programmer Guide for more information.)

Page 17

Chapter 2. Getting Started

17

13

A3

14

A2

15

A1

16

A0

17

PC9

18

NWE

19

FPG

20

NRD

21

GND

22

3.3V

23

GND

24

3.3V

25

D7

26

D6

27

D5

28

D4

29

D3

30

D2

31

D1

32

D0

33

PC13

34

JTAGSEL

35

PC12

36

NC

Pin No

Name

DK v2.1

Pin No

Expansion

Header Pin No

Description

1~16

A[15:0]

J9_1

-J9_16

J3_4-J3_20

External Address Bus 0-15 (0 at reset)

DK is directly connected with CPU and external connecter (J3) is connected by buffer.

17

PC9

J9_17

J4_14

Peripheral A : NCS5

External device Chip Select 5.

256MB memory area addressable, active low

Peripheral B : TIOB0

Timer Counter ch0 I/O Line B

18

NEW

J9_18

J1_21

External device Write Enable signal, active low

19

FPG

J9_19

-

For Flash Programming

You can program Data Flash in Eddy CPU v2.1 via USB. Refer to 2.4.2.3 S6:NAND Flash & Data

Flash Chip Select for further information.

20

NRD

J9_20

J1_23

External device Read Enable signal, active low

21, 23

GND

Ground

22, 24

3.3V

3.0V to 3.6V power input

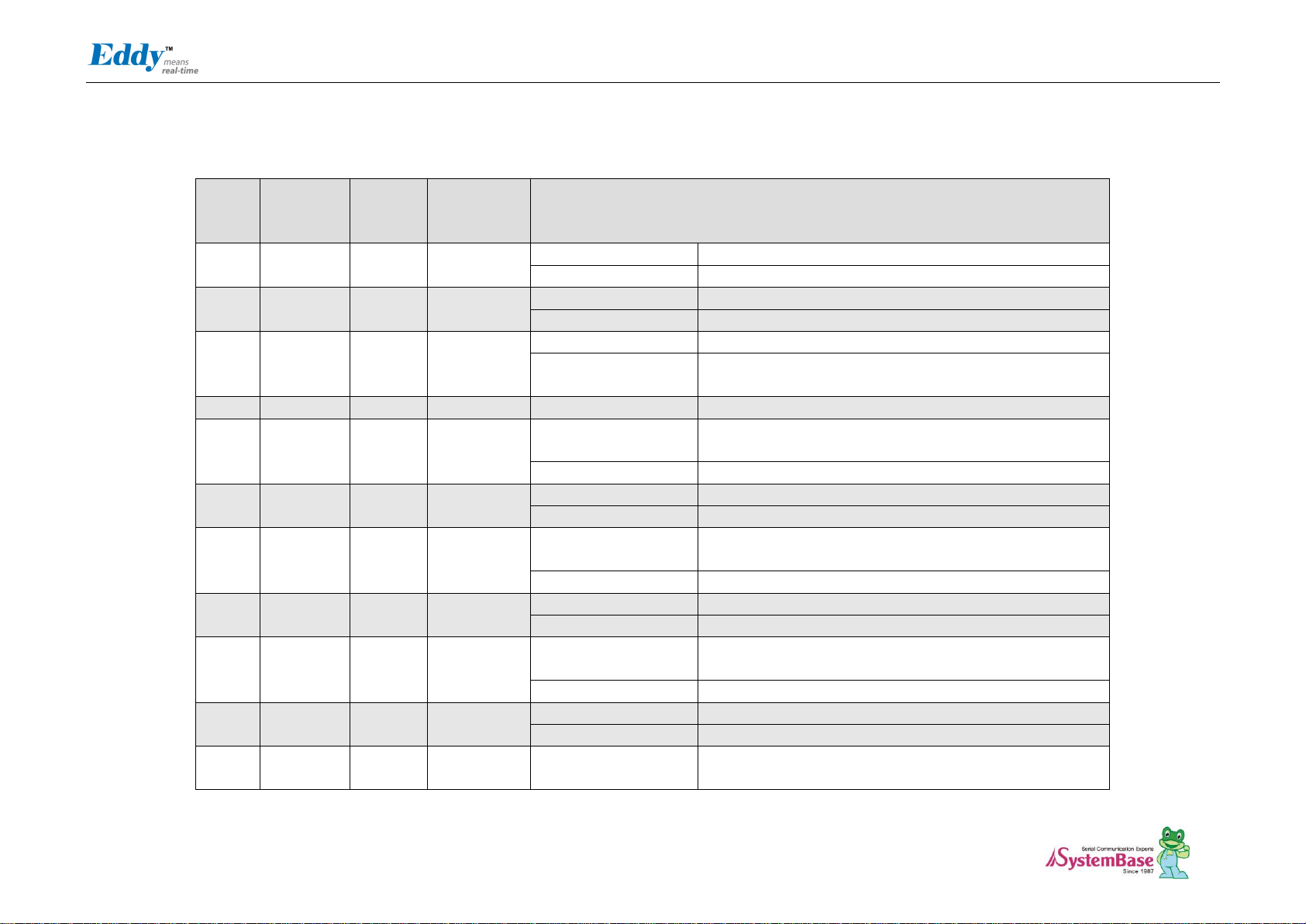

J2 Pin Description

Page 18

Chapter 2. Getting Started

18

25~32

D[7:0]

J9_25

- J3_32

J3_29 - J3_36

External Data Bus 0-7

DK is directly connected with CPU and external connecter (J3) is connected by buffer. You

should enable PC13(NCS6 : Chip Select 6) for working buffer, if you reset, it becomes Pulled-up

input.

33

PC13

J9_33

J4_18

Edd-DK v2.1 : NCS6

Data Bus connected with external header can be used when NCS6

is enabled.

Peripheral A : FIQ

Fast Interrupt Input

Peripheral B : NCS6

External device Chip Select 6

256MB memory area addressable, active low

34

JTAGSEL

J9_34

-

JTAG boundary scan can be used by connecting pin34 and 36(J14 connection). This pin should

not be connected when using ICE (In-Circuit Emulator) or in normal operation status.

35

PC12

J9_35

J4_17

Peripheral A : IRQ0

External Interrupt Input 0

Peripheral B : NCS7

External device Chip Select 7.

256MB memory area addressable, active low

36

NC

Not Connect

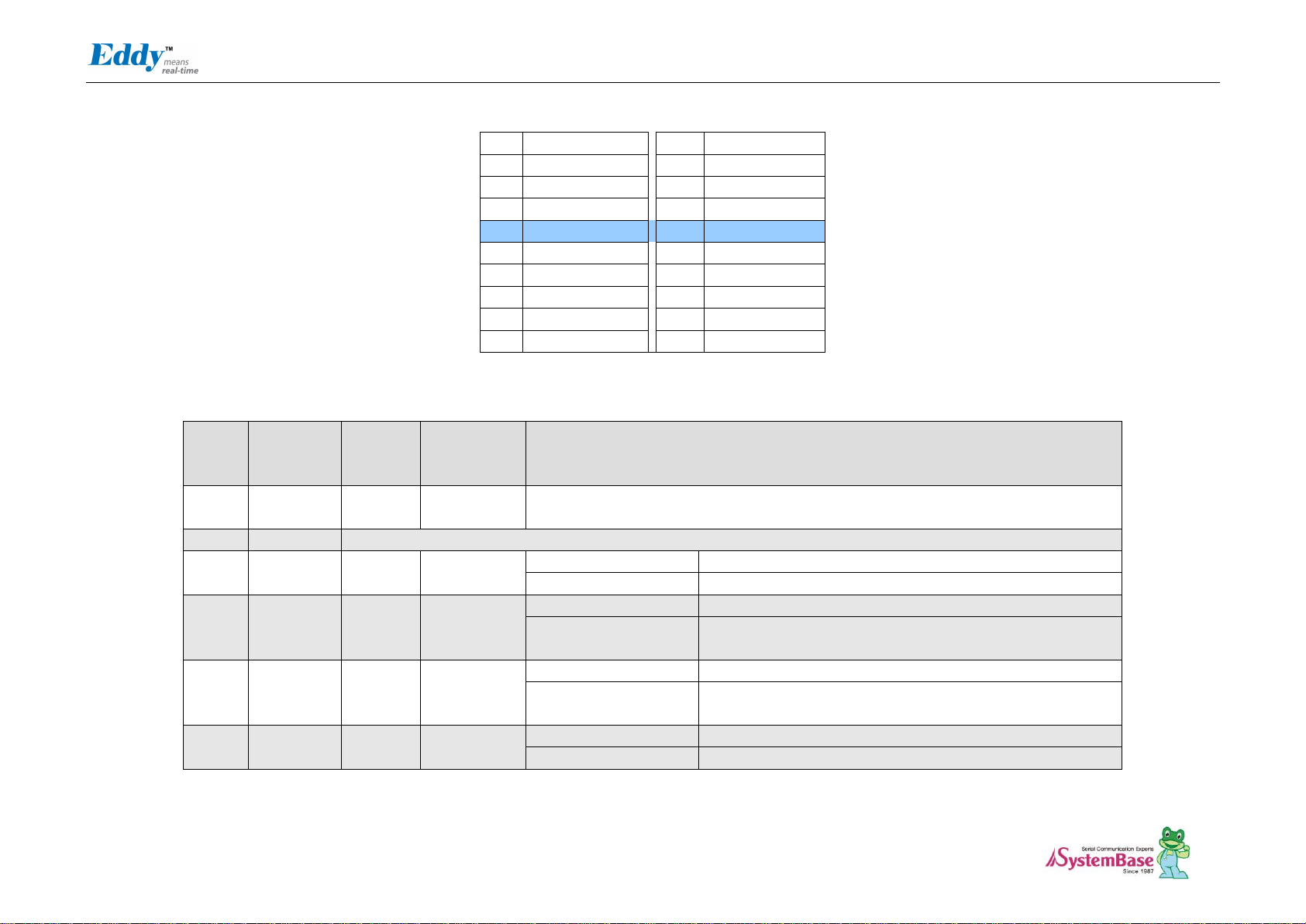

J3

Pin

Signal Name

Pin

Signal Name

1

PID0

2

PID1

3

PID2

4

PID3

5

PID4

5

GND

7

PC14

8

PC17

9

PC18

10

PC8 (RTS3)

11

PC20

12

PC10 (CTS3)

13

PA22

14

PC15 (IRQ1)

15

PB8

16

PB9 (RXD2)

J3 Specifications

Page 19

Chapter 2. Getting Started

19

17

PB10

18

PB11(RXD3)

19

PC0

20

PC1 (AD1)

21

PC2

22

PC3 (AD3)

23

PB14 (DRXD)

24

PB15 (DTXD)

25

GND

26

GND

27

BMS

28

NRST

29

PB23 / DCD0

30

PB5 / RXD0

31

PB4 / TXD0

32

PB24 / DTR0

33

PB22 / DSR0

34

PB26 / RTS0

35

PB27 / CTS0

36

PB25 / RI0

Pin No

Name

DK v2.1

Pin No

Expansion

Header Pin

No

Description

1-5

PID[4:0]

J8_1

~J8_5

-

Product ID only used by the manufacturer.

Please do not work on these pins.

6,25,26

GND

Ground

7

PC14

J8_7

J4_19

Peripheral A : NCS3

External Device Chip Select 3

Peripheral B : IRQ2

External Interrupt Input 2

8

PC17

J8_8

J4_22

Peripheral A : D17

External Data Bus

Peripheral B :

SPI0_NPCS3

Disabled

9

PC18

J8_9

J4_23

Peripheral A : D18

External Data Bus

Peripheral B :

SPI1_NPCS1

SPI1(Serial Peripheral Interface) Peripheral Chip Select 1

10

PC8

J8_10

J4_13

Peripheral A : NCS4

External Device Chip Select 4

Peripheral B : RTS3

USART3 Request to Send

J3 Pin Description

Page 20

Chapter 2. Getting Started

20

11

PC20

J8_11

J4_25

Peripheral A : D20

External Data Bus

Peripheral B :

SPI1_NPCS3

SPI1(Serial Peripheral Interface) Peripheral Chip Select 3

12

PC10

J8_12

J4_15

Peripheral A : A25

External Address Bus

Peripheral B : CTS3

USART3 Clear to Send

13

PA22

J8_13

-

Digital I/O Input 4

14

PC15

J8_14

J4_20

Peripheral A : NWAIT

External Wait Signal Input

Peripheral B : IRQ1

External Interrupt Input 2

15

PB8

J8_15

J2_9

Peripheral A : TXD2

UART2 Transmit Data

16

PB9

J8_16

J2_10

Peripheral A : RXD2

UART2 Receive Data

17

PB10

J8_17

J2_11

Peripheral A : TXD3

UART3 Transmit Data

Peripheral B : ISI_D8

Image Sensor Data 8

18

PB11

J8_18

J2_12

Peripheral A : RXD3

UART3 Receive Data

Peripheral B : ISI_D9

Image Sensor Data 9

19

PC0

J8_19

J4_7

Peripheral A : AD0

Analog to Digital Converter Input Ch0

Peripheral B : SCK3

USART3 Serial Clock

20

PC1

J8_20

J4_8

Peripheral A : AD1

Analog to Digital Converter Input Ch1

Peripheral B : PCK0

Programmable Clock Output 0

21

PC2

J8_21

J4_9

Peripheral A : AD2

Analog to Digital Converter Input Ch2

Peripheral B : PCK1

Programmable Clock Output 1

22

PC3

J8_22

J4_10

Peripheral A : AD3

Analog to Digital Converter Input Ch3

Peripheral B :

SPI1_NPCS3

SPI1(Serial Peripheral Interface) Peripheral Chip Select 3

23

PB14

J8_23

J2_15

Peripheral A : DRXD

Debug Receive Data

24

PB15

J8_24

J2_16

Peripheral A : DTXD

Debug Transmit Data

27

BMS

J8_27

-

Boot Mode Select signal

BMS = 1, Boot on Embedded ROM

BMS = 0, Boot on External Memory

28

NRST

J8_28

J1_20

External device Reset signal, active low signal

Page 21

Chapter 2. Getting Started

21

29

PB23

J8_29

J4_28

Peripheral A : DCD0

USART0 Data Carrier Detection

Peripheral B : ISI_D3

Image Sensor Data 3

30

PB5

J8_30

J2_6

Peripheral A : RXD0

USART0 Receive Data

31

PB4

J8_31

J2_5

Peripheral A : TXD0

USART0 Transmit Data

32

PB24

J8_32

J2_25

Peripheral A : DTR0

USART0 Data Terminal Ready

Peripheral B : ISI_D4

Image Sensor Data 4

33

PB22

J8_33

J2_23

Peripheral A : DSR0

USART0 Data Set Ready

Peripheral B : ISI_D2

Image Sensor Data 2

34

PB26

J8_34

J2_27

Peripheral A : RTS0

USART0 Request To Send

Peripheral B : ISI_D6

Image Sensor Data 6

35

PB27

J8_35

J2_28

Peripheral A : CTS0

USART0 Clear To Send

Peripheral B : ISI_D7

Image Sensor Data 7

36

PB25

J8_36

J2_26

Peripheral A : RI0

USART0 Ring Indicator

Peripheral B : ISI_D5

Image Sensor Data 5

Page 22

Chapter 2. Getting Started

22

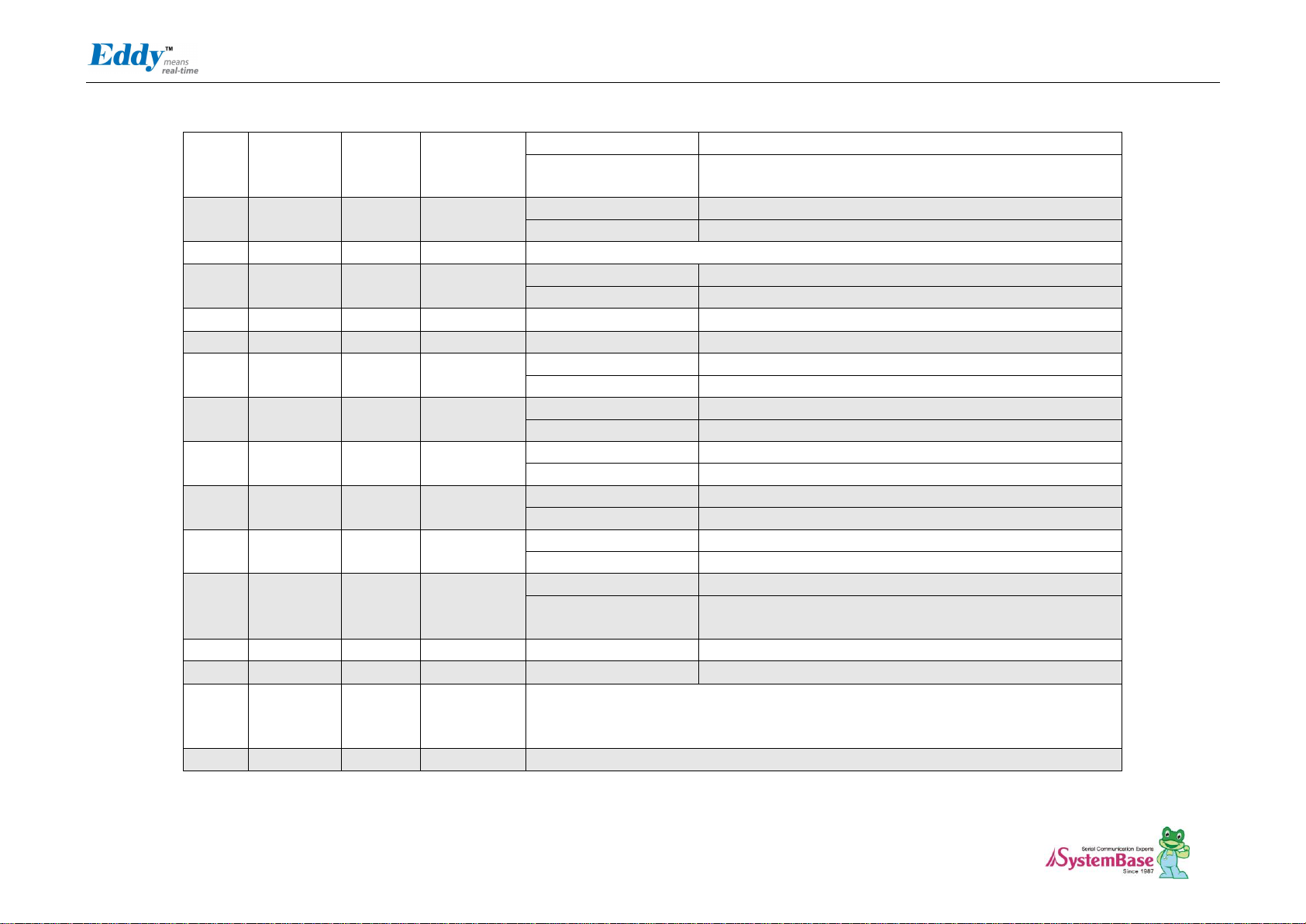

J4

Pin

Signal Name

Pin

Signal Name

1

PB12

2

PB13

3

PB30

4

PB31

5

PB0

5

PC22

7

PB1

8

PB16

9

PB2

10

PB17

11

PB3

12

PB18

13

BHDM

14

PB19

15

BHDP

16

PB20

17

A16

18

PB21

19

A17

20

A18

21

D8

22

D9

23

D10

24

D11

25

D12

26

D13

27

D14

28

D15

29

TWD

30

TCK

31

NANDOE

32

NAND_CLE / A22

33

NANDWE

34

NAND_ALE / A21

35

NC

36

NC

J4 Specifications

Page 23

Chapter 2. Getting Started

23

Pin No

Name

DK v2.1

Pin No

Expansion

Header Pin

No

Description

1

PB12

J11_1

J2_17

Peripheral A : TXD5

USART5 Transmit Data

Peripheral B : ISI_D10

Image Sensor Data 10

2

PB13

J11_2

J2_18

Peripheral A : RXD5

USART5 Receive Data

Peripheral B : ISI_D11

Image Sensor Data 11

3

PB30

J11_3

J2_31

Peripheral A : PCK0

Programmable Clock Output 0

Peripheral B :

ISI_HSYNC

Image Sensor Horizontal Synchronization

4

PB31

J11_4

J2_32

Peripheral A : PCK1

Programmable Clock Output 1

5

PB0

J11_5

J2_2

Peripheral A :

SPI1_MISO

SPI1(Serial Peripheral Interface) Master In Slave Out

Peripheral B : TIOA3

Timer Counter ch3 I/O Line A

6

PC22

J11_6

J4_27

Peripheral A : D22

Peripheral B : TCLK5

Timer Counter ch5 External CLK IN

7

PB1

J11_7

J2_3

Peripheral A :

SPI1_MOSI

Peripheral B : TIOB3

Timer Counter ch3 I/O Line B

8

PB16

J11_8

J2_17

Peripheral A : TK0

SSC Transmit Clock

Peripheral B : TCLK3

Timer Counter ch3 External CLK IN

9

PB2

J11_9

J2_4

Peripheral A :

SPI1_SPCK

SPI1(Serial Peripheral Interface) Serial Clock

Peripheral B : ISI_D3

Image Sensor Data 3

10

PB17

J11_10

J2_18

Peripheral A : TF0

SSC Transmit Frame Sync

Peripheral B : TCLK4

Timer Counter ch4 External CLK IN

11

PB3

J11_11

J2_5

Peripheral A :

SPI1_NPCS0

SPI1(Serial Peripheral Interface) Peripheral Chip Select 0

J4 Pin Description

Page 24

Chapter 2. Getting Started

24

Peripheral B : TIOA5

Timer Counter ch5 I/O Line A

12

PB18

J11_12

J2_19

Peripheral A : TD0

SSC Transmit Data

Peripheral B : TIOB4

Timer Counter ch4 I/O Line B

13

HDMB

J11_13

J1_28

USB Device Port Data -

14

PB19

J11_14

J2_20

Peripheral A : RD0

SSC Receive Data

Peripheral B : TIOB5

Timer Counter ch5 I/O Line B

15

HDPB

J11_15

J1_30

USB Device Port Data +

16

PB20

J11_16

J2_21

Peripheral A : RK0

SSC Receive Clock

Peripheral B : ISI_D0

Image Sensor Data 0

17

A16

J11_17

J3_3

External Address Bus

18

PB21

J11_18

J2_22

Peripheral A : RF0

SSC Receive Frame Sync

Peripheral B : ISI_D1

Image Sensor Data 1

19

A17

J11_19

J3_2

External Address Bus

20

A18

J11_20

J3_1

21-28

D[8:15]

J11_21

~J11_28

J3_28

~J3_21

External Data Bus 8-15

DK is directly connected with CPU and external connecter (J3) is connected by buffer.

PC13(NCS6 : Chip Select 6) should be enabled for working buffer, if it is reset, it work

as Pulled-up input.

29

TWD

J11_29

J4_3

Two-wire Serial Data. This pin cannot be used for GPIO.

30

TWCK

J11_30

J4_4

Two-wire Serial Data. This pin cannot be used for GPIO.

31

NANDOE

J11_31

-

NAND Flash Output Enable

32

A22

J11_32

J1_29

Address Bus

DK is directly connected with CPU and external connecter (J3) is connected by buffer.

33

NANDWE

J11_33

-

NAND Flash Write Enable

34

A21

J11_34

J1_30

Address Bus

35,36

NC

Not Connect

Page 25

Chapter 3. Development

25

NOTE:

Ensure that the input power supply for Eddy Serial DK is from 9V to 48V with 500 mA (or higher).

Environment

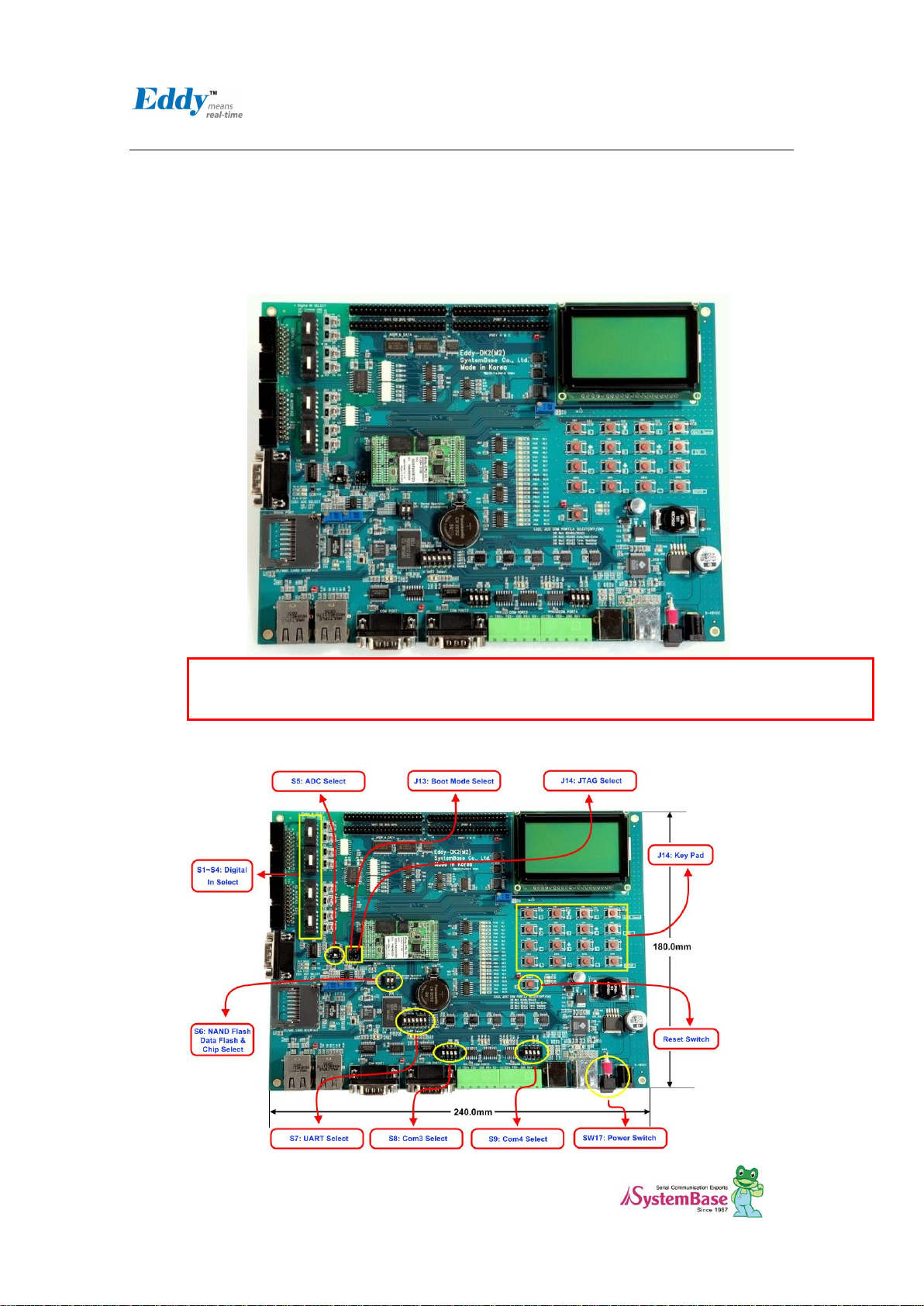

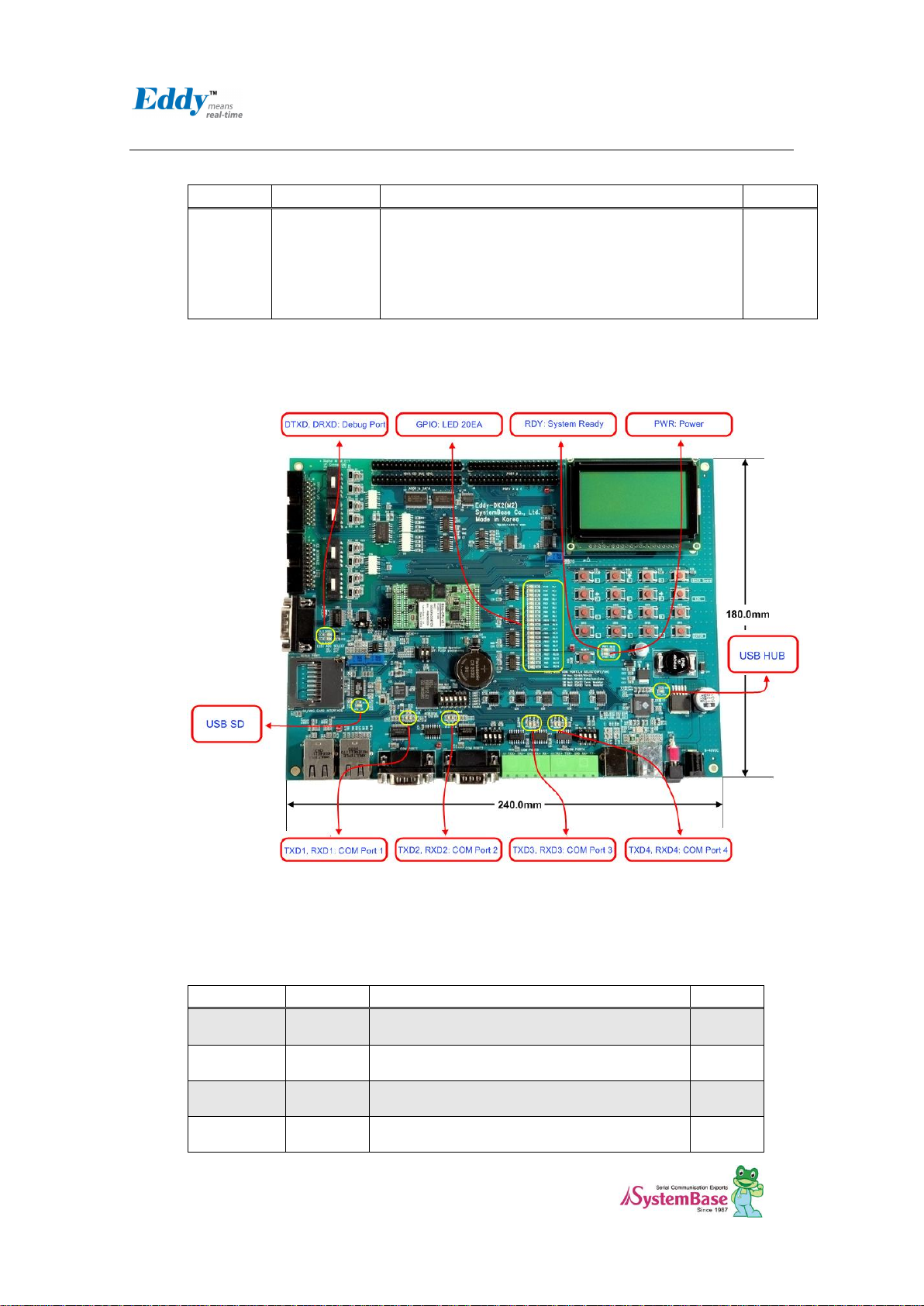

2.4 Eddy-DK v2.1

2.4.1 Modules’Locations

2.4.2 Switch Description

Page 26

Chapter 3. Development

26

MODE

Switch

설명

GND

Comm

on

UP

Common GND

COM

(GND)

Isolated Input

Signal(Source)

Eddy DK v2.1

1.1K

4.7K

VCC

Comm

on

Down

Common VCC

EXTERNAL POWER

Isolated Input

Signal(SINK)

Eddy DK v2.1

1.1K

4.7K

ON

1

ON

PIN name

Fuction

Discription

I/O

PC0

ADC0

Temp. Sensor Input(LM50), RN: U22

IN

SW Off : ADC mode

SW ON : GPIO mode

Environment

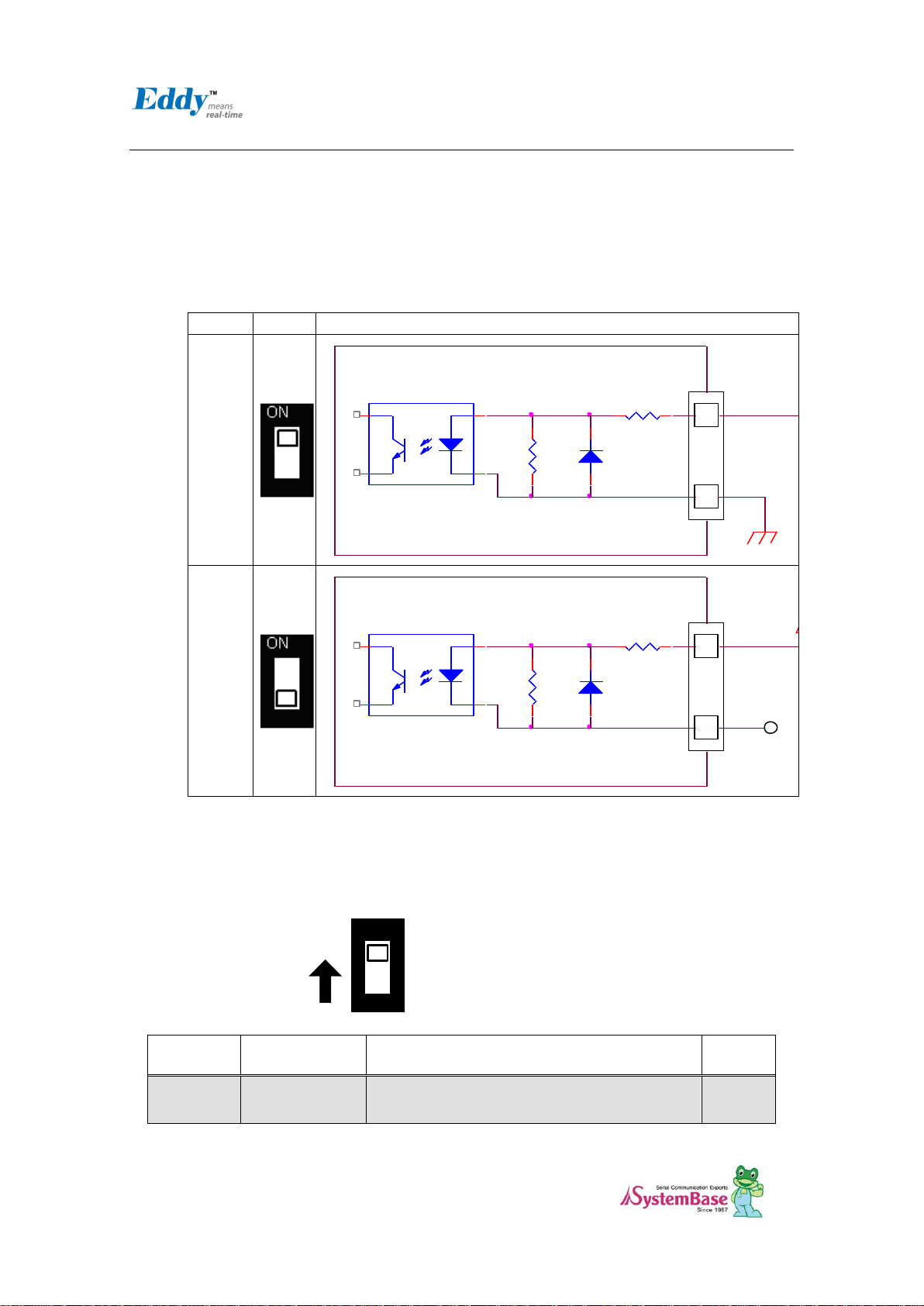

2.4.2.1. S1~S4: Digital In Select

It is possible to select the Distal Input mode with this switch (S1 ~ S4). In order to use VCC Common

Mode, switch down, and to use GNC Common Mode switch up refer to below feature.

This below schematic is just for reference, So you should make you own schematic with the current

and voltage that you want.

Common Input Setting (Switch S1~S4)

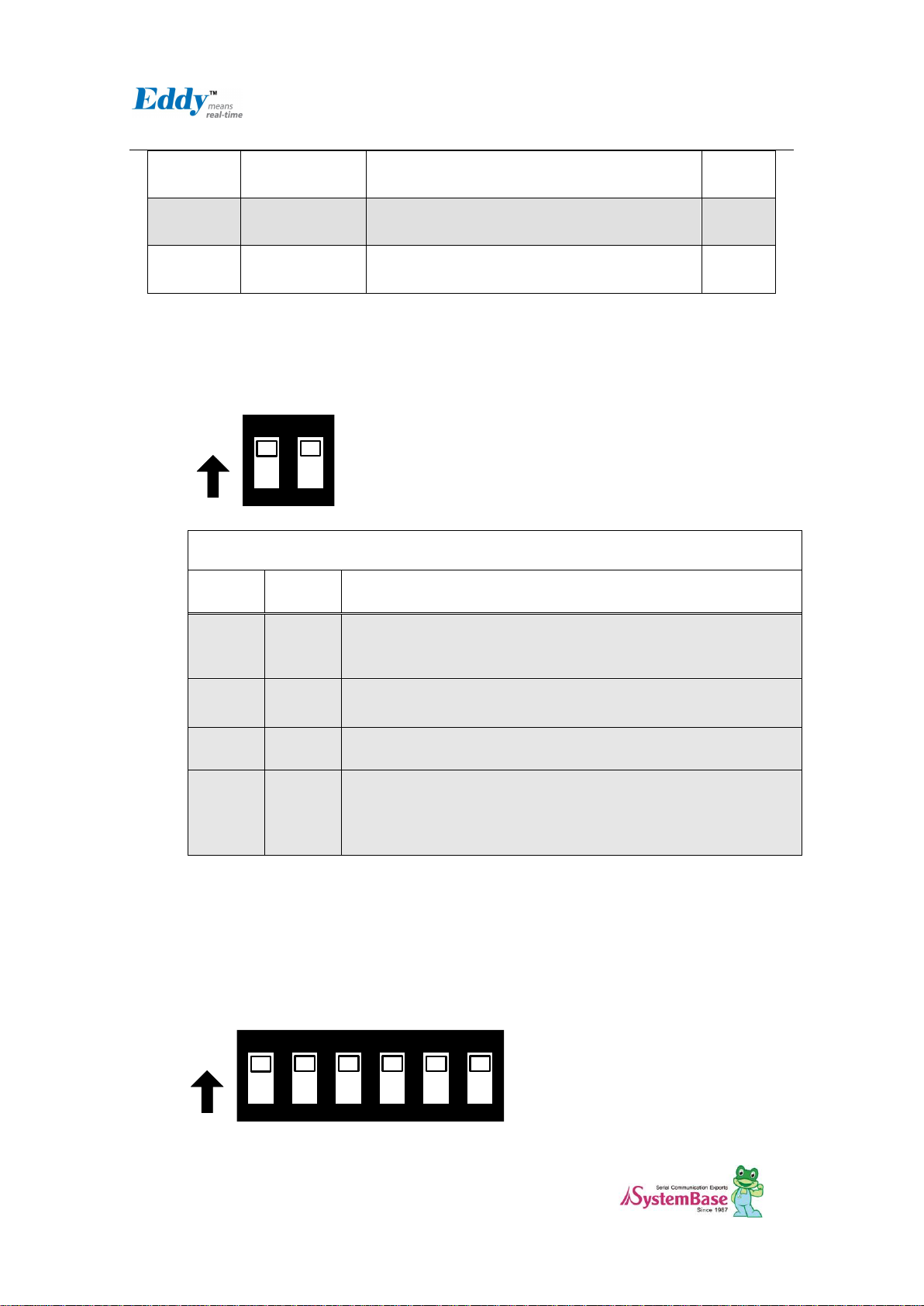

2.4.2.2. S5: ADC Select

You can choice the GPIO and ADC function with this switch. In order to use the ADC device, you

should switch off. And In order to use the GPIO function, you should switch on.

Page 27

Chapter 3. Development

27

PC1

ADC1

Lux. Sensor Input(BH1600), RN: U26

IN

PC2

ADC2

Temp. Sensor Input(TMP300), RN: U24

IN

PC3

ADC3

N/A

IN

ON

ON

1 2

Flash Programming & Booting device Selection

Switch

No 1

Switch

No 2

Operation descriotion

OFF

OFF

For Flash Programming

This setting is needed in firmware Programming. refer to 9.2 System

recovery via USB

OFF

ON

Boot from Data Flash.

ON

OFF

Boot from Nand Flash

ON

ON

Boot from Data Flash or Nand Flash which have bootloader. if Both

devices have the bootloader, algorithm in CPU select the bootloader

of Data Flash.

(Reference : CPU Datasheet 13 장 AT91SAM9260 Boot Program)

ON

ON

1 2 3 4 5 6

Environment

* RN = Reference Number

2.4.2.3. S6: NAND Flash & Data Flash Chip Select

This switch is Nand Flash & Data Flash Chip select switch. This switch is needed in firmware

Programming.

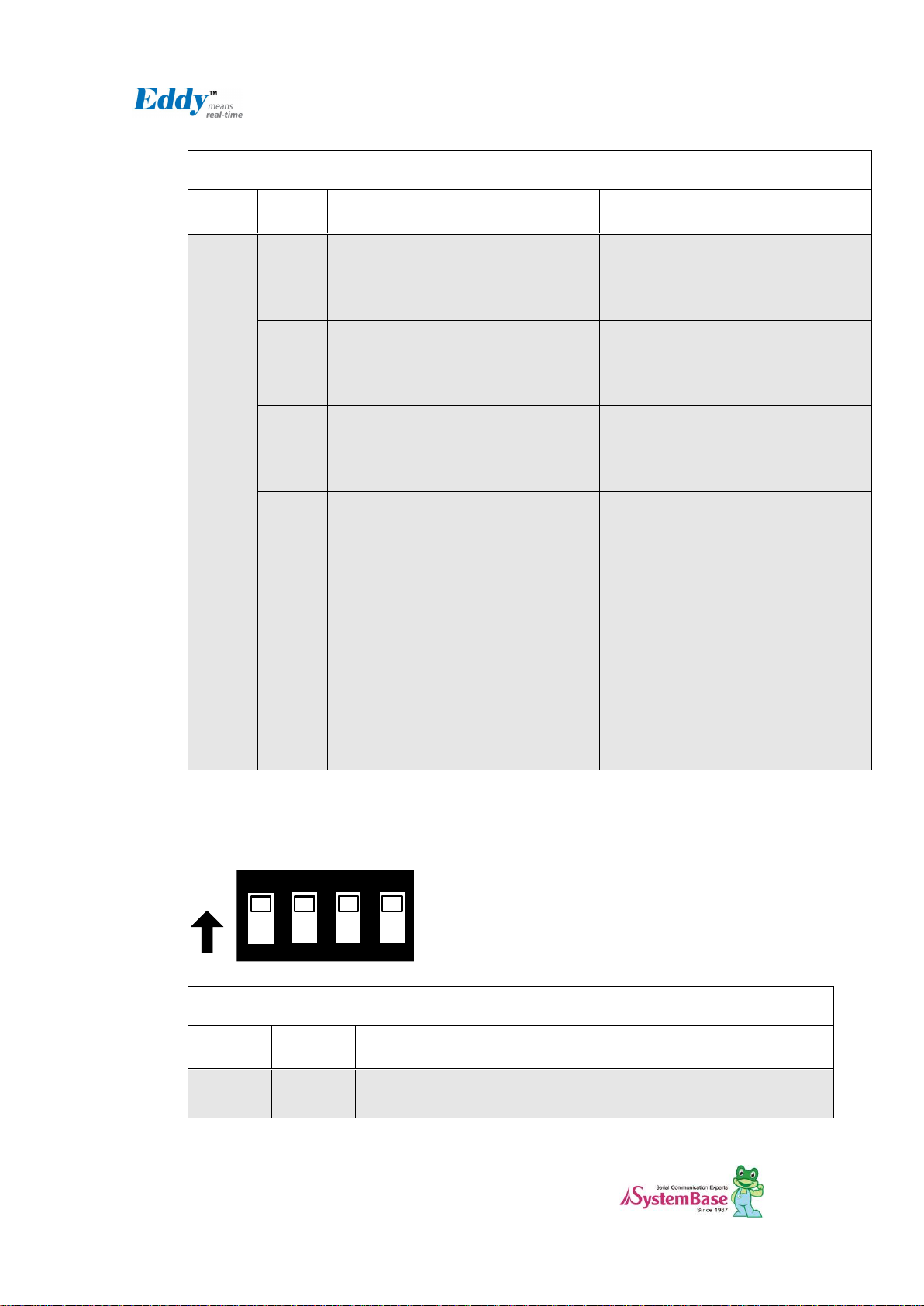

2.4.2.4. S7:UART Select

In order to test Serial Port, UART Select Switches are pulled down. It means that UARTs in CPU are

connected to Serial Port. If switches are pulled up, GPIO Ports are enabled and LEDs are controlled

by GPIO Ports. And if Switch No.6 is pulled up, GPIO ports are connected with the Expansion

Headers.

Page 28

Environment

28

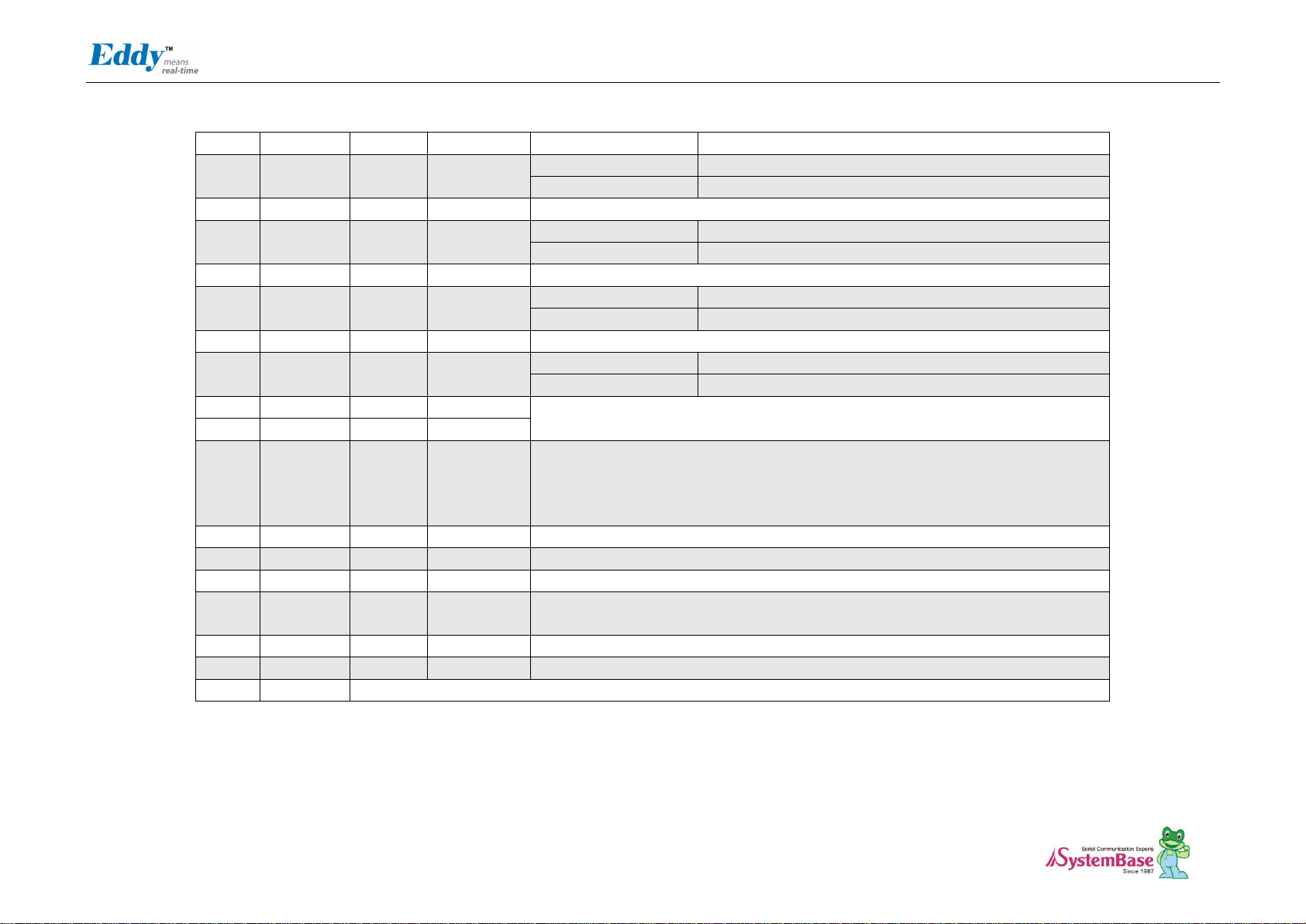

Serial Port & LED

Switch

Bank

Switch

No

Down Position(OFF)

Serial Port Test

UP Position(ON)

GPIO TEST (High : LED On)

S7

1

UART#0 TEST

UART#0 의 TXD, RXD, RTS, CTS

signals are connected with UART#0

RS232 driver IC.

GPIO (PB4, PB5, PB26, PB27) ports are

connected with the GPIO LED of DK

board and disconnected with the

UART#0 RS232 driver IC.

2

UART#0 TEST

UART#0 의 DTR, DSR, DCD, RI signals

are connected with UART#0 RS232

driver IC.

GPIO (PB24, PB22, PB23, PB25) ports

are connected with the GPIO LED of DK

board and disconnected with the

UART#0 RS232 driver IC.

3

UART#1 TEST

UART#1 의 TXD, RXD, RTS, CTS

signals are connected with UART#1

RS232 driver IC.

GPIO (PB6, PB7, PB28, PB29) ports are

connected with the GPIO LED of DK

board and disconnected with the

UART#1 RS232 driver IC.

4

UART#2 TEST

UART#2 의 TXD, RXD, RTS, CTS

signals are connected with UART#2

RS422/485 driver IC.

GPIO (PB8, PB9, PA4, PA5) ports are

connected with the GPIO LED of DK

board and disconnected with the

UART#2 RS422/485 driver IC.

5

UART#3 TEST

UART#3 의 TXD, RXD, RTS, CTS

signals are connected with UART#3

RS422/485 driver IC.

GPIO (PB10, PB11, PC8, PC10) ports

are connected with the GPIO LED of DK

board and disconnected with the

UART#3 RS422/485 driver IC.

6

For Serial Port & GPIO Test

Serial Port and GPIO LED of DK board

are enabled.

Connect to Expansion Header

UART#0~#3 and GPIO LEDs are

disconnected with the Eddy-CPU board

and directly connected with the

Expansion Header(J2, J4)

ON

ON

1 2 3 4

COM PORT#3, #4 settings

Switch

Bank

Switch

No

Down Position(OFF)

UP Position(ON)

S8

Port#3

1

RS485 Half-Duplex mode

RS422 Full-Duplex mode

Chapter 3. Development

2.4.2.5. S8:COM3 & S9: COM4 Select

COM Port #3 and COM Port #4 set the RS422/RS485 mode.

Page 29

Chapter 3. Development

29

2

RS422(RX enabled)

RS485 echo-mode

RS485 non echo-mode

3

RS422 Termination Resistor

not connected

RS422 Termination Resistor

Connected

4

RS485 Termination Resistor

not connected

RS422 Termination Resistor

Connected

S9

Port#4

1

RS485 Half-Duplex mode

RS422 Full-Duplex mode

2

RS422(RX enabled)

RS485 echo-mode

RS485 non echo-mode

3

RS422 Termination Resistor

not connected

RS422 Termination Resistor

Connected

4

RS485 Termination Resistor

not connected

RS422 Termination Resistor

Connected

P10-P17

4x4 Key matrix

I/O

PB20

First Row line

IN

PB21

Second Row line

IN

PB30

Third Row line

IN

PB31

Forth Row line

IN

PC20

First Column line from left

IN

PC21

Second Column line from left

IN

PC22

Third Column line from left

IN

PC23

Fourth Column line from left

IN

Environment

2.4.2.6. SW1~SW16: Key Pad

Key Pad of DK board are consisted with the 4x4 matrix. GPIOs are set to Input mode to read the Key

value. and Key 2, 4, 6, 8 also have the ▲(UP), ▼(DN), ◀(LEFT), ▶(RIGHT) direction function for

LCD menu.

2.4.2.7. SW17: Power

In order to power up, pull up this switch.

Page 30

Chapter 3. Development

30

Pin name

Function

Discription

I/O

PC16

nRESET

Polling Input signal continually from External Reset

key, implement as below with checking the constant

time of "Low."

Less than 5 seconds: General reset function.

More than 5 seconds: Factory Default function.

IN

PIN name

Function

Discription

I/O

PC10

CTS3

UART #3 Clear to Send

I

PC8

RTS3

UART #3 Request to Send

O

PB11

RXD3

UART #3 Receive Data

I

PB10

TXD3

UART #3 Transmit Data

O

Environment

2.4.2.8. Reset1: Reset

2.4.3 LED Description

2.4.3.1. GPIO LED

Eddy-CPU v2.1 supports Max 56 GPIO ports. DK board has 20 GPIO LEDs of all GPIO to test. This

GPIO LEDs are controlled by UART select switches.(refer to 2.4.2.4 UART Select )

Page 31

Environment

31

PA5

CTS2

UART #2 Cleat to Send

I

PA4

RTS2

UART #2 Request to Send

O

PB9

RXD2

UART #2 Receive Data

I

PB8

TXD2

UART #2 Transmit Data

O

PB29

CTS1

UART #1 Cleat to Send

I

PB28

RTS1

UART #1 Request to Send

O

PB7

RXD1

UART #1 Receive Data

I

PB6

TXD1

UART #1 Transmit Data

O

PB25

RI0

UART #0 Ring Indicator

I

PB23

DCD0

UART #0 Data Carrier Detection

I

PB22

DSR

UART #0 Data Set Ready

O

PB24

DTR0

UART #0 Data Terminal Ready

I

PB27

CTS0

UART #0 Clear to Send

I

PB26

RTS0

UART #0 Request to Send

O

PB5

RXD0

UART #0 Receive Data

I

PB4

TXD0

UART #0 Transmit Data

O

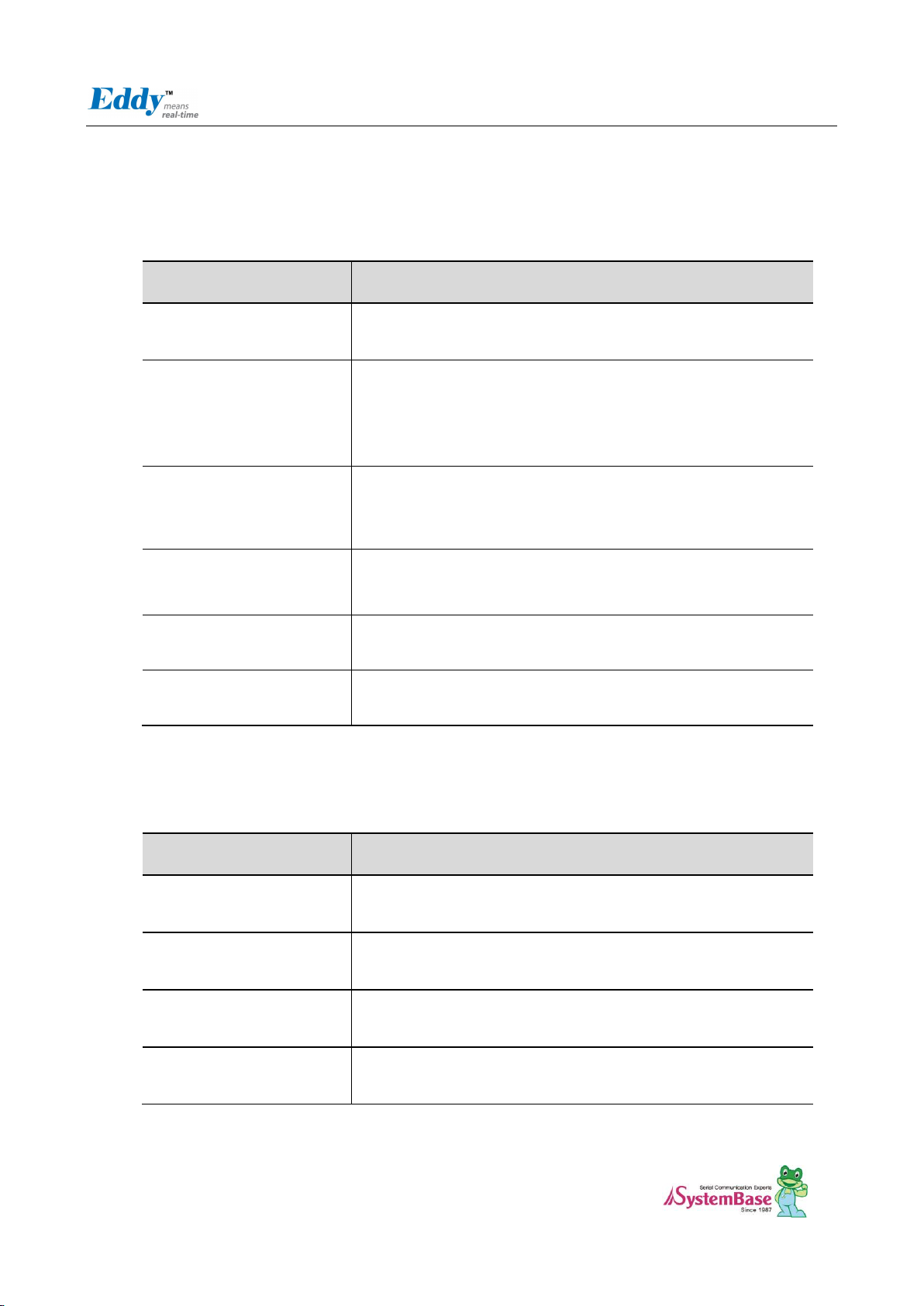

Symbol

Parameter

Conditions

Min

Typ

Max

Units

Io

Output Current

PA0-PA31 PB0-PB31

PC0-PC3

16

PC4 - PC31 in 3.3V range

2*

mA

PC4 - PC31 in 1.8V range

4

Chapter 3. Development

41.2 DC Characteristics

* Eddy DK v2.1 has 3.3V range, so PC4-PC31 PIO is set to 2mA.

(Refer to CPU Datasheet의 41.2 DC characteristics )

2.4.3.2. Power, Ready LED

System Ready (RDY): Indicates that the system is operating normally. (Normal: LED blinks)

Power (PWR): Indicates that the 5 V power is being supplied. (Supplying power: Red LED ON)

2.4.3.3. Debug Port LED

DTXD (Debug Port Transmit Dta LED) : Shows transmission status of the Debug Port.

DRXD (Debug Port Receive Data LED) : Shows reception status of the Debug Port.

Page 32

Chapter 3. Development

32

Environment

2.4.3.4. COM Port 1 LED

COM Port 1 Transmit LED : Shows transmission status of COM1 Port.

COM Port 1 Receive LED : Shows reception status of COM1 Port.

2.4.3.5. COM Port 2 LED

COM Port 2 Transmit LED : Shows transmission status of COM2 Port.

COM Port 2 Receive LED : Shows reception status of COM2 Port.

2.4.3.6. COM Port 3 LED

COM Port 3 Transmit LED : Shows transmission status of COM3 Port.

COM Port 3 Receive LED : Shows reception status of COM3 Port.

2.4.3.7. COM Port 4 LED

COM Port 4 Transmit LED : Shows transmission status of COM4 Port.

COM Port 4 Receive LED : Shows reception status of COM4 Port.

2.4.4 External Device Interface Description

Page 33

Environment

33

Pin

Signal

Description

1

TXD+

Transmit Data +

2

TXD-

Transmit Data -

3

RXD+

Receive Data +

6

RXD-

Receive Data -

LED

Description

Left Green

Upon 100BaseT link, it lights

Upon 10BaseT link, it off

Right Yellow

Default Lights, When the data

is sent or received, it blinks.

Chapter 3. Development

2.4.4.1. WAN & LAN Interface

WAN & LAN Port automatically recognizes Cross/ Direct.(auto MDIX)

Page 34

Chapter 3. Development

34

Pin

Signal

Description

1

DCD

Data Carrier Detection (Input) (COM Port 1 only)

2

RXD

Receive Data (Input)

3

TXD

Transmit Data (Output)

4

DTR

Data Terminal Ready (Output) (COM Port 1 only)

5

GND

Ground

6

DSR

Data Set Ready (input) (COM Port 1 only)

7

RTS

Request to Send (Output)

8

CTS

Clear to Send (Input)

9

RI

Ring Indicator (Input)

Pin

Signal

Description

1

TXD+

Transmit differential data positive (Output)

2

TXD-

Transmit differential data negative (Output)

3

GND

Ground 4 RXD+

Receive differential data positive (Input)

5

RXD-

Receive differential data negative (input)

Environment

2.4.4.2. COM Port 1 & COM Port 2

RS232

2.4.4.3. COM Port 3 & COM Port 4

RS422 Full Duplex

Page 35

Chapter 3. Development

35

Pin

Signal

Description

1

TRX+

Transmit/Receive differential data positive

2

TRX-

Transmit/Receive differential data negative

Contact

Polarity

Center (D : 2mm)

9-48VDC

Outer (D: 6.5mm)

Ground

Environment

RS485 Half Duplex

2.4.4.4. Debug Port

You can check debug message or status information with debug port.

Environment Setting

Debug port is configured as follows so user has to set his or her PC serial port connected to debug

port as follows.

Speed: 115200 bps

Data bit: 8 bit

Parity bit: Non Parity

Stop bit: 1 bit

2.4.4.5. Power Jack

Page 36

Chapter 3. Development

36

Signal Name

Function

Description

I/O

P[00:07]

Data bits

Used for data transfer between the CPU and the LCD

module.

I/O

P10

/CS1

Chip enable for D2 (Segment 1 to 64)

IN

P11

/CS2

Chip enable for D3 (Segment 65 to 128)

IN

P12

R/W

R/W signal input is used to select the read /write

mode

High = Read mode, Low = Write mode

IN

P13

D/ I

Register selection input

High = Data register

Low = Instruction register (for write)

Busy flag address counter (for read)

IN

Environment

2.4.5 Internal Device Description

2.4.5.1. EEPROM

Eddy-DK v2.1 has the AT25160, 2Kx8bit SPI EEPROM.

2.4.5.2. LCD Module

Graphic LCD Module (PowerTIP PG12864LRU-JCNH11Q and I2C-Bus I/O Expander IC PCA9539)

Page 37

Chapter 3. Development

37

P14 E Start enable signal to read or write the data.

IN

Function

Description

I/O

P00-P07

DIO Output, Connected with DO[0:7]

OUT

P00

DIO output, DO0

P01

DIO output, DO1

P02

DIO output, DO2

P03

DIO output, DO3

P04

DIO output, DO4

P05

DIO output, DO5

P06

DIO output, DO6

P07

DIO output, DO7

P10-P17

DIO Intput, Connected with DI[0:7]

IN

P10

DIO Input, DI0

P11

DIO Input, DI1

P12

DIO Input, DI2

P13

DIO Input, DI3

P14

DIO Input, DI4

P15

DIO Input, DI5

P16

DIO Input, DI6

P17

DIO Input, DI7

/INT

Connected with PB16 of Eddy-CPU

OUT

Environment

2.4.5.3. 16bit I2C Bus GPIO

This 16-bit I2C Bus GPIO (PCA9539) provides general-purpose remote I/O expansion.

Slave address of this chip is set to 0x74 in DK board. and Address can be changed with A1,A0

address input from 0x74 to 0x77.

16-bit I/O is used to Digital Input/Output as below, and this is connected with the Expansion Header

also. If you use for GPIO, it is possible to configure individually.

2.4.5.4. RTC

- DS1340 (Dallas, I2C interface)

- 12.5pF load capacitance crystal must be used. (Refer to Crystal Spec below)

- Do not use another RTC Chip.

- Backup Battery: CR2032 (235mAh) Lithium Battery.

Page 38

Chapter 3. Development

38

Parameter

Symbol

MIN

TYP

MAX

Units

Normal Frequency

fo

32.768

KHz

Series Resistance

ESR

45,60

KΩ

Load Capacitance

CL

12.5

pF

EddyCPUv2.1

Signal Name

Function

Discription

I/O

A22

CLE

COMMAND LATCH ENABLE

The CLE input controls the activating path for

commands sent to the command register.

OUT

Environment

DS1340 Crystal Specifications

2.4.5.5. Temp Sensor

AD0(PC0)에 National LM50

2.4.5.6. Light Sensor

BH1600FVC (Rohm)

Viout = 0.6 x10-6 x Ev x R1

Where, Viout = IOUT output voltage [V]

Ev = lilluminance of the ALS(Ambient Light Sensor) surface [lx]

R1 = IOUT output resistor [Ω]

2.4.5.7. NAND Flash

- 256MB, 8bit Flash (Samsung K9F2G08U0A-PCB0)

- Chip Select #3 used, Address range : 0x4000_0000~0x4FFF_FFFF.

The Output voltage is caculated as below

Page 39

Environment

39

A21

ALE

ADDRESS LATCH ENABLE

The ALE input controls the activating path for

address to the internal address registers.

OUT

NANDOE

NANDOE

data-out control

OUT

NANDWE

NANDWE

controls writes to the I/O port

OUT

PC14(NCS3)

NANDCS

device selection control

OUT

PC17

RDYBSY

(R/B)

READY/BUSY OUTPUT

The R/B output indicates the status of the device

operation. When low, it indicates that a program,

erase or random read operation is in process and

returns to high state upon completion. It is an

open drain output and

does not float to high-z condition when the chip

is deselected or when outputs are disabled.

IN

D[0:7]

DATA

bits

DATA INPUTS/OUTPUTS

The I/O pins are used to input command,

address and data, and to output data during read

operations. The I/O pins float to high-z when the

chip is deselected or when the outputs are

disabled.

I/O

Eddy-CPU v2.1

Signal Name

DM9000B

Signal Name

Description

I/O

PC12/NCS7

CSN

Chip Select #7

Address : 0x8000 0000-0x8FFF FFFF

OUT

PC15/IRQ1

INTRN

Interrupt depend on EECK(pin20) setting.

1 : INT pin low active

0 : INT pin high active

EECK is not connected in DK board, so Interrupt is

acted with active high.

IN

A2

CMD

Command Type

When high, Data port

When low, INDEX port

OUT

D[0:15]

Data Bus

16-bit mode

I/O

Chapter 3. Development

2.4.5.8. Ethernet Controller (WAN Port)

- Davicom DM9000B Ethernet Controller

- 16 bit mode set.

- EECS pin should be connected with pull-up resistor to use link/speed LED.

- RJ45 Transformer Center Tap is powered by DM9000B AVDD18.

Page 40

Chapter 3. Development

40

Environment

2.5 Eddy-S4M v2.1

Eddy-S4M is a high-performance mini PCI type embedded module which include ATMEL

AT91SAM9260-CJ porcessor 32MB SDRAM, 8MB DataFlash, 10/100Base-T Ethernet port, Serial 4

Channel, RTC with Battery, minroSD, 4ch ADC, temperature sensor, max 34 programmable GPIO

pins. Eddy-S4M is 59.75 x 61.8mm size. If using Eddy-S4M-JIG board, user could develop their

customized device without other H/W development, which minimizing time and cost to develop.

Referring Example code and Evaluation Kit circuit allow developer to design device they want.

Page 41

Environment

41

Pin

Signal

Pin

Signal

Pin

Signal

Pin

Signal

1

JTAG_TDI

2

JTAG_TDO

63

3.3V

64

PB13

Key Key

65

PB16

66

PB17

2

JTAG_TMS

4

JTAG_RTCK

67

PB18

68

PB19

3

JTAG_TCK

6

ICE_NTRST

69

GND

70

3.3V

7

LAN_RX+

8

LAN_TX+

71

PB20

72

PB21

9

LAN_RX-

10

LAN_TX-

73

PB30

74

GND

11

LAN_Speed

12

LAN_LINK

75

PC0

76

PB31

13

P3_RX-

14

RDY#

77

GND

78

PC1

15

GND

16

NC

79

PC2

80

PC3

17

P3_RX+

18

NC

81

PC5

82

GND

19

3.3V

20

DCD0

83

GND

84

PC9

21

P3_TX+

22

DTR0

85

PC10

86

PC12

Chapter 3. Development

2.5.1 5.1 miniPCI Card Type III Connector Pinout (J5)

Page 42

Environment

42

23

GND

24

3.3V

87

PC13

88

3.3V

25

P3_TX-

26

nRESET

89

3.3V

90

PC14

27

GND

28

3.3V

91

PC15

92

PC17

29

P4_RX+

30

RxD0#

93

PC18

94

PC19

31

3.3V

32

GND

95

PC24

96

PC20

33

P4_RX-

34

RTS0

97

NC

98

PC25

35

P4_TX+

36

TxD0#

99

I2C_TWCK

100

I2C_TWD

37

GND

38

CTS0

101

GND

102

GND

39

P4_TX-

40

3.3V

103

DDM

104

DDP

41

DEBUG_TxD

42

DSR0

105

DM2

106

DP2

43

DEBUG_RxD

44

RI0

107

DM3

108

DP3

45

PA5

46

RxD1#

109

DM4

110

DP4

47

PA22

48

RTS1

111

SDDATA0

112

SDDATA1

49

GND

50

GND

113

SDDATA2

114

GND

51

PA30

52

TxD1#

115

SDCMD

116

SDDATA3

53

NC

54

CTS1

117

SDCDN

118

SDCLK

55

GND

56

NRST

119

JTAG_SEL

120

SDWP

57

PB0

58

PB1

121

NC

122

BMS

59

PB2

60

PB3

123

NC

124

3.3V

61

PB12

62

GND

S4M

Pin No

(124)

Name

S4M-JIG

Pin HDR

(46*2)

S4M-DK

Pin HDR

(46*2)

Description

1

TDI - -

Test Data IN

2

TDO - -

Test Data Out

3

TMS - -

Test Mode Select

4

RTCK - -

Return Test Clock

5

TCK - -

Test Clock

6

NTRST

-

-

Test Reset

119

JTAGSEL

-

-

JTAG boundary scan can be used by connecting J3.

This pin should not be connected when using ICE (In-Circuit

Emulator) or in normal operation status.

S4M

Pin No

(124)

Name

S4M-JIG

Pin HDR

(46*2)

S4M-

DK

Pin

HDR

(46*2)

Description

7

LAN_RX+

J5 pin2

J7 Pn2

Ethernet PHY Physical receive or transmit signal (+ differential) in CPU

8

LAN_TX+

J5 pin1

J7 Pin1

Ethernet PHY Physical receive or transmit signal (- differential) in CPU

9

LAN_RX-

J5 pin3

J7 pin3

Ethernet PHY Physical receive or transmit signal (+ differential) in CPU

Chapter 3. Development

2.5.2 Connector Pinout of Boards

2.5.2.1. ICE and JTAG

2.5.2.2. Ethernet signal from or to PHYceiver

Page 43

Chapter 3. Development

43

10

LAN_TX-

J5 pin4

J7 pin4

Ethernet PHY Physical receive or transmit signal (- differential) in CPU

11

LAN_Speed

J5 pin6

J7 pin6

LAN connection status LED

Link/Activity

Pin State

LED Definition

No Link

H

OFF

Link L ON

Activity

Toggle

Blinking

12

LAN_Link

J5 pin5

J7 pin5

Link/Activity

Pin State

LED Definition

No Link

H

OFF

Link L ON

Activity

Toggle

Blinking

S4M

Pin No

(124)

Name

S4M-JIG

Pin HDR

(46*2)

S4M-DK

Pin HDR

(46*2)

Description

13

P2_RX-

J4 pin20

J6 pin20

COM port #3 Receive differential data negative (Input)

RS422/485 inverting receiver input of Eddy-S4M module

14

RDY#

J4 pin45

J6 pin45

Indicate state of CPU ( normal : blinking)

17

P2_RX+

J4 pin19

J6 pin19

COM port #3 Receive differential data positive (Input)

RS422/485 Noninverting receiver input of Eddy-S4M module

20

DCD0

J4 pin9

J6 pin9

COM port #1 Data Carrier Detection signal

RS232 receiver input of Eddy-S4M module

21

P2_TX+

J4 pin17

J6 pin17

COM port #3 Transmit differential data positive (Output)

RS422/485 Noninverting driver ouput of Eddy-S4M module

22

DTR0

J4 pin7

J6 pin7

COM port #1 Data Terminal Ready signal

RS232 driver output of Eddy-S4M module

25

P2_TX-

J4 pin18

J6 pin18

COM port #3 Transmit differential data negative (Output)

RS422/485 inverting driver ouput of Eddy-S4M module

26

nRESET

J4 pin46

J6 pin46

Reset Input. In S/W, continuously check the interval of ‚LOW‛

when polling input signal from external Reset Key.

Under 5sec : Normal reset function

Over 5sec : Factory Default function

29

P3_RX+

J4 pin23

J6 pin23

COM port #4 Receive differential data negative (Input)

RS422/485 Noninverting receiver input in Eddy-S4M module

30

RxD0#

J4 pin4

J6 pin4

COM port #1 Receive Data signal

RS232 receiver input in Eddy-S4M module

Environment

2.5.2.3. Serial (RS232 & COMBO) and PIOA (Peripheral I/O Controller A)

Page 44

Environment

44

33

P3_RX-

J4 pin24

J6 pin24

COM port #4 Receive differential data negative (Input)

RS422/485 inverting receiver input in Eddy-S4M module

34

RTS0

J4 pin5

J6 pin5

COM port #1 Request To Send signal

RS232 driver output in Eddy-S4M module

35

P3_TX+

J4 pin21

J6 pin21

COM port #4 Transmit differential data positive (Output)

RS422/485 Noninverting driver ouput in Eddy-S4M module

36

TxD0#

J4 pin3

J6 pin3

COM port #1 Transmit Data signal

RS232 driver output in Eddy-S4M module

38

CTS0

J4 pin6

J6 pin6

COM port #1 Request to Send signal

RS232 receiver input in Eddy-S4M module

39

P3_TX-

J4 pin22

J6 pin22

COM port #4 Transmit differential data negative(Output)

RS422/485 inverting driver ouput in Eddy-S4M module

41

DTxD#

J4 pin1

J6 pin1

Transmit Data signal of Debug Port

RS232 driver output in Eddy-S4M module

42

DSR0

J4 pin8

J6 pin8

COM port #1 Data Set Ready signal

RS232 receiver input in Eddy-S4M module

43

DRxD

J4 pin2

J6 pin2

Receive Data signal of Debug Port

RS232 receiver input in Eddy-S4M module

44

RI0

J4 pin8

J6 pin8

COM port #1 Ring Indicator signal

RS232 receiver input in Eddy-S4M module

45

PA5

J5 pin7

J7 pin7

Only used for GPIO

46

RxD1#

J4 pin12

J6 pin12

COM port #1 Receive Data signal

RS232 receiver input in Eddy-S4M module

47

PA22

J5 pin8

J7 pin8

Only used for GPIO

48

RTS1

J4 pin13

J6 pin13

COM port #1 Request to Send signal

RS232 driver output in Eddy-S4M module

51

PA30

J5 pin9

J7 pin9

Only used for GPIO

52

TxD1#

J4 pin11

J6 pin11

COM port #1 Request to Send signal

RS232 driver output in Eddy-S4M module

54

CTS1

J4 pin14

J6 pin14

COM port #1 Request to Send signal

RS232 receiver input in Eddy-S4M module

56

NRST

J5 pin46

J7 pin46

External device Reset output signal (active low)

Chapter 3. Development

Page 45

Chapter 3. Development

45

S4M

Pin No

(124)

Name

S4M-JIG

Pin HDR

(46*2)

S4M-DK

Pin HDR

(46*2)

Description

57

PB0

J5 pin11

J7 pin11

Peripheral A : SPI1_MISO

SPI1(Serial Peripheral Interface)

Master In Slave Out

Peripheral B : TIOA3

Timer Counter ch3 I/O Line A

58

PB1

J5 pin12

J7 pin12

Peripheral A : SPI1_MOSI

SPI1(Serial Peripheral Interface)

Master Out Slave In

Peripheral B : TIOB3

Timer Counter ch3 I/O Line B

59

PB2

J5 pin13

J7 pin13

Peripheral A : SPI1_SPCK

SPI1(Serial Peripheral Interface) Serial

Clock

60

PB3

J5 pin14

J7 pin14

Peripheral A : SPI1_NPCS0

SPI1(Serial Peripheral Interface)

Peripheral Chip Select 0

Peripheral B : TIOA5

Timer Counter ch5 I/O Line A

61

PB12

J5 pin17

J7 pin17

Peripheral A : TXD5

USART5 Transmit Data

64

PB13

J5 pin18

J7 pin18

Peripheral A : RXD5

USART5 Receive Data

65

PB16

J5 pin119

J7 pin119

Peripheral A : TK0

SSC Transmit Clock

Peripheral B : TCLK3

Timer Counter ch3 External CLK IN

66

PB17

J5 pin20

J7 pin20

Peripheral A : TF0

SSC Transmit Frame Sync

Peripheral B : TCLK4

Timer Counter ch4 External CLK IN

67

PB18

J5 pin21

J7 pin21

Peripheral A : TD0

SSC Transmit Data

Peripheral B : TIOB4

Timer Counter ch4 I/O Line B

68

PB19

J5 pin22

J7 pin22

Peripheral A : RD0

SSC Receive Data

Peripheral B : TIOB5

Timer Counter ch5 I/O Line B

71

PB20

J5 pin23

J7 pin23

Peripheral A : RK0

SSC Receive Clock

72

PB21

J5 pin24

J7 pin24

Peripheral A : RF0

SSC Receive Frame Sync

73

PB30

J5 pin25

J7 pin25

Peripheral A : PCK0

Programmable Clock Output 0

75

PC0

J5 pin27

J7 pin27

Peripheral A : AD0

Analog to Digital Converter Input Ch0

76

PB31

J5 pin26

J7 pin26

Peripheral A : PCK1

Programmable Clock Output 1

Environment

2.5.2.4. PIOB and PIOC (Peripheral I/O Controller B/C)

Page 46

Environment

46

78

PC1

J5 pin28

J7 pin28

Peripheral A : AD1

Analog to Digital Converter Input Ch1

Peripheral B : PCK0

Programmable Clock Output 0

79

PC2

J5 pin29

J7 pin29

Peripheral A : AD2

Analog to Digital Converter Input Ch2

Peripheral B : PCK1

Programmable Clock Output 1

80

PC3

J5 pin30

J7 pin30

Peripheral A : AD3

Analog to Digital Converter Input Ch3

Peripheral B : SPI1_NPCS3

SPI1(Serial Peripheral Interface)

Peripheral Chip Select 3

81

PC5

J5 pin33

J7 pin33

Peripheral B : SPI1_NPCS1

SPI1(Serial Peripheral Interface)

Peripheral Chip Select 1

84

PC9

J5 pin34

J7 pin34

Only GPIO

85

PC10

J5 pin35

J7 pin35

Only GPIO

86

PC12

J5 pin36

J7 pin36

Only GPIO

87

PC13

J5 pin37

J7 pin37

Only GPIO

90

PC14

J5 pin38

J7 pin38

Only GPIO

91

PC15

J5 pin39

J7 pin39

Only GPIO

92

PC17

J5 pin40

J7 pin40

Only GPIO

93

PC18

J5 pin41

J7 pin41

Peripheral B : SPI1_NPCS1

SPI1(Serial Peripheral Interface)

Peripheral Chip Select 1

94

PC19

J5 pin42

J7 pin42

Peripheral B : SPI1_NPCS2

SPI1(Serial Peripheral Interface)

Peripheral Chip Select 2

95

PC24

J5 pin44

J7 pin44

Only GPIO

96

PC20

J5 pin43

J7 pin43

Peripheral B : SPI1_NPCS3

SPI1(Serial Peripheral Interface)

Peripheral Chip Select 3

98

PC25

J5 pin45

J7 pin45

Only GPIO

S4M

Pin No

(124)

Name

S4M-JIG

Pin HDR

(46*2)

S4M-DK

Pin HDR

(46*2)

Description

99

I2C_TWCK

J4 pin43

J6 pin43

Two-wire Serial Clock.

This can be used GPIO pin unless RTC function is used.

100

I2C_TWD

J4 pin44

J6 pin44

Two-wire Serial Data. This can be used GPIO pin unless

RTC function is used.

Chapter 3. Development

2.5.2.5. Two Wire Interface

Page 47

Chapter 3. Development

47

S4M

Pin No

(124)

Name

S4M-JIG

Pin HDR

(46*2)

S4M-DK

Pin HDR

(46*2)

Description

103

DDM

J4 pin25

J6 pin25

USB Device Port Data –

104

DDP

J4 pin26

J6 pin26

USB Device Port Data +

105

DM2

J4 pin27

J6 pin27

USB Port2 Data –. Connected to DSPORT2 of GL850A

USB 2.0 Hub Controller.

106

DP2

J4 pin27

J6 pin27

USB Port2 Data +. Connected to DSPORT2 of GL850A

USB 2.0 Hub Controller.

107

DM3

J4 pin29

J6 pin29

USB Port3 Data –. Connected to DSPORT2 of GL850A

USB 2.0 Hub Controller.

108

DP3

J4 pin30

J6 pin30

USB Port3 Data +. Connected to DSPORT2 of GL850A

USB 2.0 Hub Controller.

109

DM4

J4 pin33

J6 pin33

USB Port4 Data -. Connected to DSPORT2 of GL850A

USB 2.0 Hub Controller.

110

DP4

J4 pin34

J6 pin34

USB Port4 Data +. Connected to DSPORT2 of GL850A

USB 2.0 Hub Controller.

S4M

Pin No

(124)

Name

S4M-JIG

Pin HDR

(46*2)

S4M-DK

Pin HDR

(46*2)

Description

111

SDDATA0

J4 pin35

J6 pin35

SD Data0

112

SDDATA1

J4 pin36

J6 pin36

SD Data1

113

SDDATA2

J4 pin37

J6 pin37

SD Data2

115

SDCMD

J4 pin38

J6 pin38

SD command

116

SDDATA3

J4 pin39

J6 pin39

SD Data3

117

SDCDN

J4 pin40

J6 pin40

SD card detect

118

SDCLK

J4 pin41

J6 pin41

SD Clock

120

SDWP

J4 pin42

J6 pin42

SD Write Protect

122

BMS

-

-

Boot Mode Select signal

BMS = 1, Boot on Embedded ROM

BMS = 0, Boot on External Memory

Environment

2.5.2.6. Universal Serial Bus

2.5.2.7. Multimedia Card Interface

Page 48

Environment

48

S4M

Pin No

(124)

Name

S4M-JIG

Pin HDR

(46*2)

S4M-DK

Pin HDR

(46*2)

Description

16, 18, 53,

97,

121, 123

NC

J5 pin10

J5 pin10

No Connection

15, 23, 27,

32, 37, 49,

50, 55, 62,

69, 74, 77,

82, 83, 101,

102, 114

GND

J4: 31,32

J5: 31,32

J6: 31,32

J7: 31,32

Ground

19, 24, 28,

31, 40, 63,

70, 88, 89,

124

3.3V

J4: 15,16

J6: 15,16

3.0 to 3.6V power input

ON

1

ON

Switch No 1

Operation descriotion

OFF

For Flash Programming

Store firmware image to Flash memory through USB Device. (Only

via Window Host). For more information, please refer to chapter 9,

system recovery.

ON

Normal booting via Eddy-S4M v2.1 Data Flash

2.5.2.8. etc

Chapter 3. Development