Page 1

10/100 Mbps TX/FX/10BT

Fast Ethernet Physical Layer Device (PHY)

Features

• Single-Chip 100BASE-TX/FX/10BASE-T Fast

Ethernet Physical Layer Solution

• Dual-Speed - 10/100 Mbits /sec

• Half-Duplex And Full-D uplex Support

• MII Interface to Ethernet Co ntroller

• MI Interface for Configu ration and Status

• Optional Repeater Interfa ce

• AutoNegotiation: 10/100, F ull/Half-Duplex

• Meets All Applicab le IEEE 802.3 Stand ards

• On-Chip Wave Shaping - No Ex ternal Filters

Required

• Adaptive Equaliz er

• Baseline Wander Correction

LAN83C183

PRELIMINARY

• Interface to External 1 00BASE-T4 PHY

• LED Outputs

– Link

– Activity

– Collision

– Full Duplex

– 10/100

– User-Programmable

• Many User Features and O ptions

• Few External Components

• 3.3V Supply with 5V-Tolerant I/O

• 64-Pin TQFP Packa ge (1.4-mm Body

Thickness)

GENERAL DESCRIPTION

The SMSC LAN83C183 is a hi ghly integrated analog interface IC for twisted pai r Ethernet applic ations.

The LAN83C183 can be c onfigured for either 100- Mbps (100BASE-TX or 100 BASE-FX) or 10-Mbps

(10BASE-T) Ether net operation. The 100 BASE-FX is packaged in a 64-Pin TQFP pa ck-age.

The LAN83C183 consists of a 4B5B/Manchester enco der/decoder, scrambler/descrambler, transmitter

with wave shaping and o utput driver, twisted pair receiver with on-c hip equalizer and baselin e wander

correction, clock a nd data recovery, AutoNegotiation, contr oller interface (MII ), and serial port (MI).

The addition of internal outp ut waveshaping circuit ry and on-chip filters elim inates the need for external

filters normally re quired in 100BASE-TX and 10BASE-T applicati ons.

The LAN83C183 can automati cally co nfigure itsel f for 100- or 10-Mbps and ful l- or half-duplex operation

with the on-chip AutoNe gotiation algorithm.

The eleven 16-bit regist ers of the LAN83C18 3 can be acce ssed through the Managemen t Interface (MI)

serial port. These r egisters contain configu ration inputs, stat us outputs, and device c apabilities.

The LAN83C183 is ideal a s a media interface for 100BASE-TX/10BASE- T adapter cards, PC Cards,

motherboards, mobil e applications, repeaters , switching hubs, and external PHYs.

The LAN83C183 operate s from a single 3.3V suppl y. All inputs and outputs are 5V-tolerant and can

directly interface to other 5V devices.

SMSC DS – LAN83C 183 Rev. 12/14/2000

Page 2

ORDERING INFORMATION

Order Number:

LAN83C183-JD

64-Pin TQFP Package

Hauppauge, NY 11788

(631) 435-6000

FAX (631) 273-3123

80 Arkay Drive

Copyright © SMSC 2004. All rights reserved.

Circuit diagrams and other information relating to SMSC products are included as a means of illustrating typical applications. Consequently, complete

information sufficient for construction purposes is not necessarily given. Although the information has been checked and is believed to be accurate, no

responsibility is assumed for inaccuracies. SMSC reserves the right to make changes to specifications and product descriptions at any time without

notice. Contact your local SMSC sales office to obtain the latest specifications before placing your product order. The provision of this information does

not convey to the purchaser of the described semiconductor devices any licenses under any patent rights or other intellectual property rights of SMSC

or others. All sales are expressly conditional on your agreement to the terms and conditions of the most recently dated version of SMSC's standard

Terms of Sale Agreement dated before the date of your order (the "Terms of Sale Agreement"). The product may contain design defects or errors

known as anomalies which may cause the product's functions to deviate from published specifications. Anomaly sheets are available upon request.

SMSC products are not designed, intended, authorized or warranted for use in any life support or other application where product failure could cause

or contribute to personal injury or severe property damage. Any and all such uses without prior written approval of an Officer of SMSC and further

testing and/or modification will be fully at the risk of the customer. Copies of this document or other SMSC literature, as well as the Terms of Sale

Agreement, may be obtained by visiting SMSC’s website at http://www.smsc.com. SMSC is a registered trademark of Standard Microsystems

Corporation (“SMSC”). Product names and company names are the trademarks of their respective holders.

SMSC DISCLAIMS AND EXCLUDES ANY AND ALL WARRANTIES, INCLUDING WITHOUT LIMITATION ANY AND ALL IMPLIED WARRANTIES

OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE, AND AGAINST INFRINGEMENT AND THE LIKE, AND ANY AND

ALL WARRANTIES ARISING FROM ANY COURSE OF DEALING OR USAGE OF TRADE.

IN NO EVENT SHALL SMSC BE LIABLE FOR ANY DIRECT, INCIDENTAL, INDIRECT, SPECIAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES;

OR FOR LOST DATA, PROFITS, SAVINGS OR REVENUES OF ANY KIND; REGARDLESS OF THE FORM OF ACTION, WHETHER BASED ON

CONTRACT; TORT; NEGLIGENCE OF SMSC OR OTHERS; STRICT LIABILITY; BREACH OF WARRANTY; OR OTHERWISE; WHETHER OR

NOT ANY REMEDY OF BUYER IS HELD TO HAVE FAILED OF ITS ESSENTIAL PURPOSE, AND WHETHER OR NOT SMSC HAS BEEN

ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

SMSC DS – LAN83C183 2 Rev. 12/14/2000

Page 3

Contents

Chapter 1 LAN83C183 Functional Des cription

1.1 OVERVIEW . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

1.1.1 Channel Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

1.1.2 Data Paths . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

1.2 BLOCK DIAGRAM DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

1.2.1 Oscillator and Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

1.2.2 Controller Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

1.2.3 Encoder. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

1.2.4 Decoder. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

1.2.5 Scrambler . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

1.2.6 Descrambler . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

1.2.7 Twisted-Pair Transmitters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

1.2.8 Twisted-Pair Receivers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

1.2.9 FX Transmitter and Receiver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

1.2.10 Clock and Data Recovery. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

1.2.11 Link Integrity and AutoNegotiation . . . . . . . . . . . . . . . . . . . . . . . . . 31

1.2.12 Link Indication. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

1.2.13 Collision. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

1.2.14 LED Drivers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

1.3 START OF PACKET . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

1.3.1 100 Mbits/s . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

1.3.2 10 Mbits/s . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

1.4 END OF PACKET . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

1.4.1 100 Mbits/s . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

1.4.2 10 Mbits/s . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

1.5 FULL/HALF DUPLEX MODE. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

1.5.1 Forcing Full/Half Duplex Operation . . . . . . . . . . . . . . . . . . . . . . . . 41

1.5.2 Full/Half Duplex Indication . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

1.5.3 Loopback. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

1.6 REPEATER MODE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

1.7 10/100 MBITS/S SELECTION. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

1.7.1 Forcing 10/100 Mbits/s Operation . . . . . . . . . . . . . . . . . . . . . . . . . 42

1.7.2 Autoselecting 10/100 Mbits/s Operation. . . . . . . . . . . . . . . . . . . . . 42

1.7.3 10/100 Mbits/s Indication . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

1.8 JABBER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

SMSC DS – LAN83C183 3 Rev. 12/14/2000

Page 4

1.9 AUTOMATIC JAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

1.9.1 100 Mbits/s JAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

1.9.2 10 Mbits/s JAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

1.10 RESET . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

1.11 POWERDOWN . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

1.12 RECEIVE POLARITY CORRECTION. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Chapter 2 Signal Descriptions

2.1 MEDIA INTERFACE SIGNALS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

2.2 CONTROLLER INTERFACE SIGNALS (MII) . . . . . . . . . . . . . . . . . . . . . . . . 47

2.3 MANAGEMENT INTERFACE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

2.4 MISCELLANEOUS SIGNALS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

2.5 LEDS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

2.6 POWER SUPPLY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Chapter 3 Registers

3.1 BIT TYPES. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

3.2 MI SERIAL PORT REGISTER SUMMARY. . . . . . . . . . . . . . . . . . . . . . . . . . 55

3.3 REGISTERS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

3.3.1 Control Register (Register 0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

3.3.2 Status Register (Register 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

3.3.3 PHY ID 1 Register (Register 2) . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

3.3.4 PHY ID 2 Register (Register 3) . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

3.3.5 AutoNegotiation Advertisement Register (Register 4) . . . . . . . . . . 61

3.3.6 AutoNegotiation Remote E nd Capability Register (Register 5 ) . . . 63

3.3.7 Configuration 1 Register (Register 16). . . . . . . . . . . . . . . . . . . . . . 64

3.3.8 Configuration 2 Register (Register 17). . . . . . . . . . . . . . . . . . . . . . 66

3.3.9 Status Output Register (Register 18) . . . . . . . . . . . . . . . . . . . . . . . 68

3.3.10 Interrupt Mask Register (Register 19) . . . . . . . . . . . . . . . . . . . . . . 69

3.3.11 Reserved Register (Register 20) . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Chapter 4 Management Interface

4.1 SIGNAL DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

4.2 GENERAL OPERATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

4.3 MULTIPLE REGISTER ACCESS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

4.4 FRAME STRUCTURE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

4.5 REGISTER STRUCTURE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

4.6 INTERRUPTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

Chapter 5 Specifications

5.1 ABSOLUTE MAXIMUM RATINGS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

5.2 ELECTRICAL CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

5.2.1 Twisted-Pair DC Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . 84

5.2.2 FX Characteristics, Transmit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

5.3 AC ELECTRICAL CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

5.3.1 25 MHz Input/Output Clock Timing Characteristics . . . . . . . . . . . . 90

SMSC DS – LAN83C183 4 Rev. 12/14/2000

Page 5

5.3.2 Transmit Timing Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

5.3.3 Receive Timing Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

5.3.4 Collision and JAM Timing Characteristics . . . . . . . . . . . . . . . . . . . 97

5.3.5 Link Pulse Timing Characteristics . . . . . . . . . . . . . . . . . . . . . . . . 100

5.3.6 Jabber Timing Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

5.4 LED DRIVER TIMING CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . 104

5.4.1 MI Serial Port Timing Characteristics. . . . . . . . . . . . . . . . . . . . . . 105

5.5 PINOUTS AND PACKAGE DRAWINGS. . . . . . . . . . . . . . . . . . . . . . . . . . . 107

5.5.1 Pinouts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

5.5.2 LAN83C183 Pin Layout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

5.6 MECHANICAL DRAWING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

SMSC DS – LAN83C183 5 Rev. 12/14/2000

Page 6

SMSC DS – LAN83C183 6 Rev. 12/14/2000

Page 7

Figures

1.1 LAN83C183 Device Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

1.2 100BASE-TX/FX and 10BASE-T Frame Format . . . . . . . . . . . . . . . . . . . . . 13

1.3 MII Frame Format. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

1.4 TP Output Voltage Template . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

1.5 TP Input Voltage Template (10 Mbits/s). . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

1.6 Link Pulse Output Voltage Template (10 Mbits/s) . . . . . . . . . . . . . . . . . . . . 32

1.7 NLP vs FLP Link Pulse . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

1.8 SOI Output Voltage Template - 10 Mbits/s . . . . . . . . . . . . . . . . . . . . . . . . . 40

2.1 Device Logic Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

4.1 MI Serial Port Frame Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

4.2 MI Serial Frame Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

4.3 MDIO Interrupt Pulse . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

5.1 25 MHz Output Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

5.2 Transmit Timing - 100 Mbits/s . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

5.3 Transmit Timing - 10 Mbits/s . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

5.4 Receive Timing, Start of Packet - 100 Mbits/s . . . . . . . . . . . . . . . . . . . . . . 94

5.5 Receive Timing, End of Packet - 100 Mbits/s . . . . . . . . . . . . . . . . . . . . . . . 95

5.6 Receive Timing, Start of Packet - 10 Mbits/s . . . . . . . . . . . . . . . . . . . . . . . 95

5.7 Receive Timing, End of Packet - 10 Mbits/s . . . . . . . . . . . . . . . . . . . . . . . . 96

5.8 RX_EN Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

5.9 Collision Timing, Receive 100 Mbits/s . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

5.10 Collision Timing, Receive 10 Mbits/s . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

5.11 Collision Timing, Transmit - 100 Mbits/s . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

5.12 Collision Timing, Transmit - 10 Mbits/s . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

5.13 Collision Test Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

5.14 JAM Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

5.15 NLP Link Pulse Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

5.16 FLP Link Pulse Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

5.17 Jabber Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

5.18 LED Driver Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

5.19 MI Serial Port Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

5.20 MDIO Interrupt Pulse Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

5.21 LAN83C183 64-Pin LQFP, Top View . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

5.22 64-Pin LQFP Mechanical Drawing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

SMSC DS – LAN83C183 7 Rev. 12/14/2000

Page 8

SMSC DS – LAN83C183 8 Rev. 12/14/2000

Page 9

Tables

1.1 Transmit Preamble and SFD Bits at MAC Nibble Interface . . . . . . . . . . . . 14

1.2 Receive Preamble and SFD Bits at MAC Nibble Interface. . . . . . . . . . . . . 15

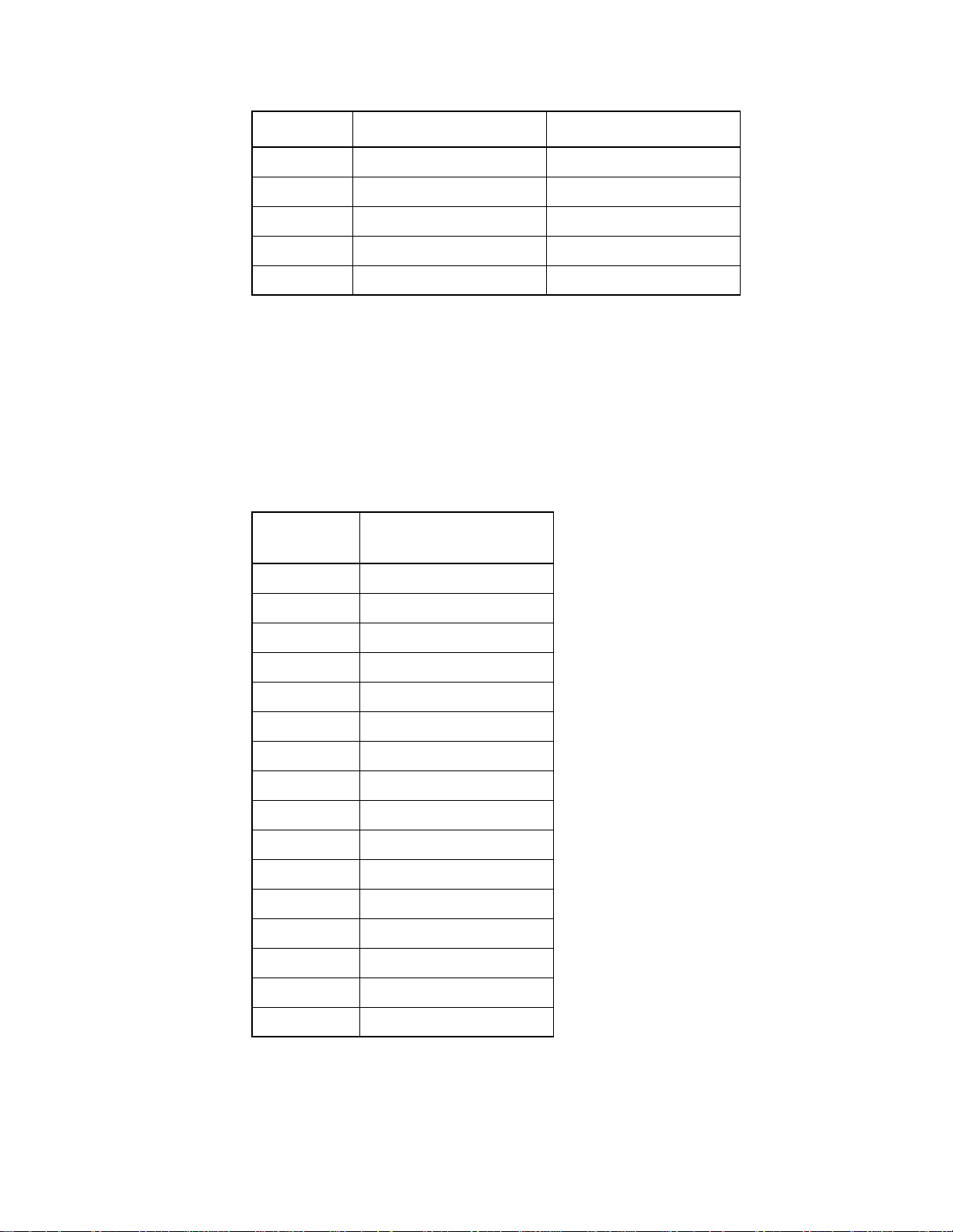

1.3 4B/5B Symbol Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

1.4 4B/5B Symbol Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

1.5 TP Output Voltage - 10 Mbits/s . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

1.6 Transmit Level Adjust . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

1.7 FX Transmit Level Adjust . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

1.8 PLED_[1:0] Output Select Bit Encoding. . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

1.9 LED Normal Function Definition. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

1.10 LED Event Definition. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

3.1 MI Register Bit Type Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

4.1 MI Serial Port Register Summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

5.1 Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

5.2 DC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

5.3 Twisted Pair Characteristics (Transmit ). . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

5.4 Twisted Pair Characteristics (Receive ) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

5.5 FX Characteristics, Transmit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

5.6 FX Characteristics, Receive . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

5.7 Test Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

5.8 25 MHz Input/Output Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

5.9 Transmit Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

5.10 Receive Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

5.11 Collision and Jam Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

5.12 Link Pulse Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

5.13 Jabber Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

5.14 LED Driver Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

5.15 MI Serial Port Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

5.16 LAN83C183 Pin List (by Signal Category) . . . . . . . . . . . . . . . . . . . . . . . . 107

5.17 LAN83C183 Pin List (by Pin Number) . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

SMSC DS – LAN83C183 9 Rev. 12/14/2000

Page 10

SMSC DS – LAN83C183 10 Rev. 12/14/2000

Page 11

Chapter 1

LAN83C183

Functional Description

This chapter is a functi onal descr iption of the PHY device wi th the followi ng sections :

• Section 1.1, “Overview”

• Section 1.2, “Blo ck Diagram Description”

• Section 1.3, “Start of Packet”

• Section 1.4, “End of Packet”

• Section 1.5, “Fu ll/Half Duplex Mode”

• Section 1.6, “R epeater Mode”

• Section 1.7, “1 0/100 Mbits/s Sele ction”

• Section 1.8, “Jabber”

• Section 1.9, “Automatic Jam”

• Section 1.10, “Reset”

• Section 1.11, “Powerdown”

• Section 1.12, “Receive Po larity Correction”

1.1 OVERVIEW

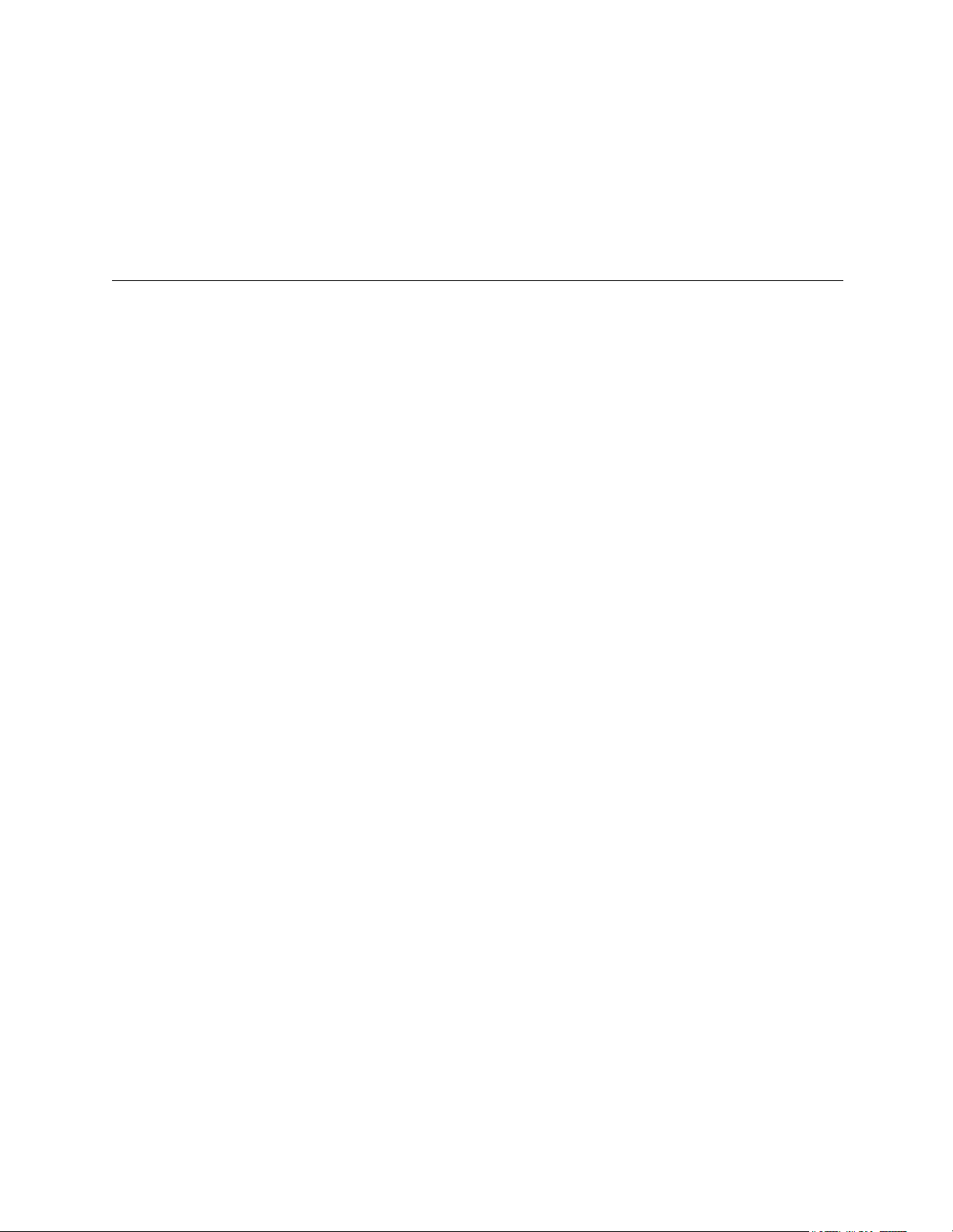

This section gives a brief overview of the dev ice functional operatio n. The

LAN83C183 is a comple te 10/100 Mbits/s Ether net Media Interface IC. A bl ock

diagram is shown in Figure 1.1.

1.1.1 Channel Operation

The PHY operates in the 100BASE -TX or 100B ASE-FX mode s at 100 M bits/s, or in

the 10BASE-T mode at 10 Mbits/ s. The 100 Mbits/s mode s and the 10 Mbits/s mode

differ in data rate, signalin g protocol, and allowed wi ring as follows:

• 100BASE-TX mode uses two pairs of catego ry 5 or better UTP or STP twisted-

pair cable with 4B5B en coded, scrambled, an d MLT3 coded 62.5-MHz ter nary

data to achieve a thro ughput of 100 Mbits /s.

• The 100BASE-FX mode u ses two fiber cables with 4B 5B encoded, 125-MHz

binary data to achieve a throughput of 100 Mbits/s .

• 10 Mbits/s mode uses two pairs of category 3 or better UTP or STP twisted-pai r

cable with Mancheste r encoded 10-MHz binary data to achieve a 10 Mbits/ s

throughput

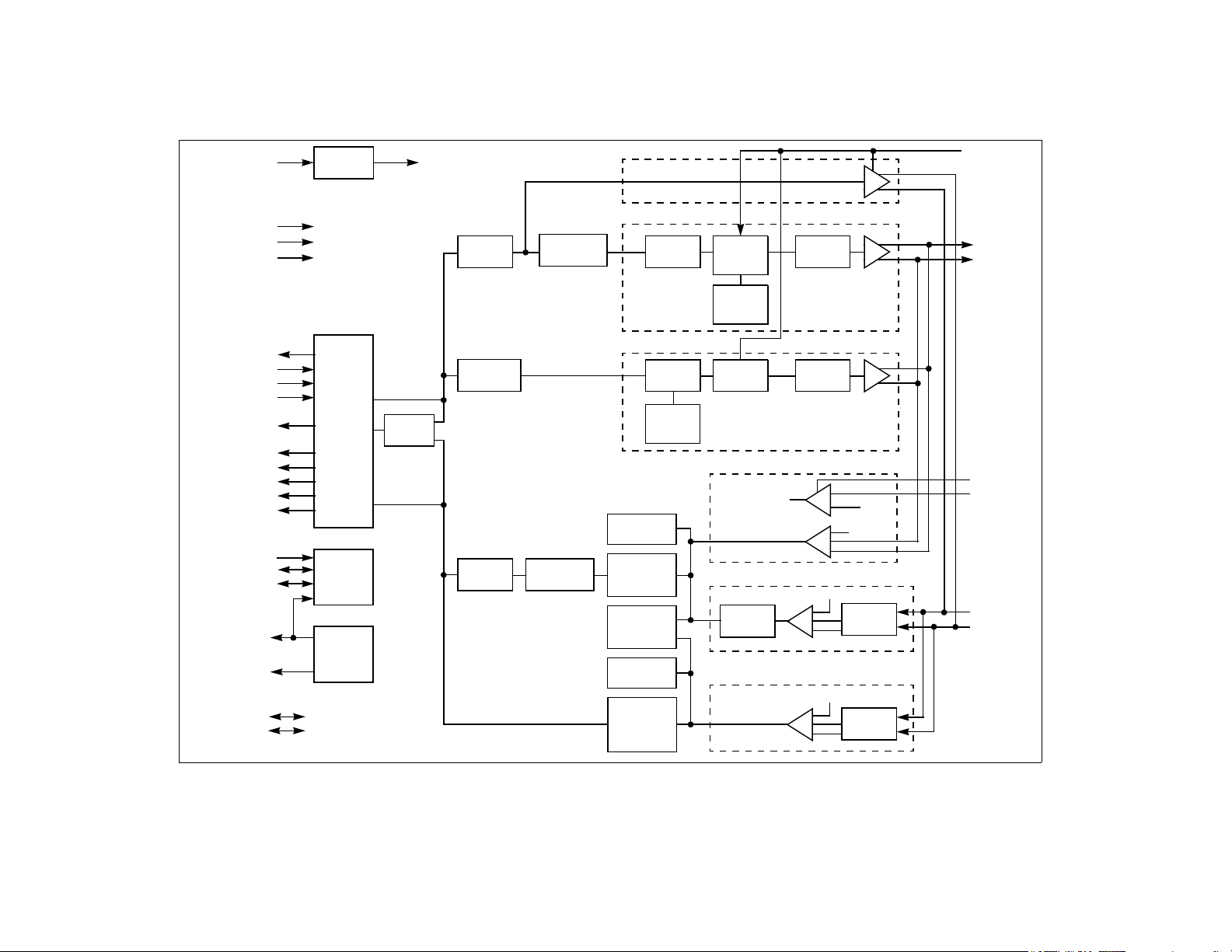

The data symbol format on the twisted-pair cable for the 100 and 10 Mbits/s modes

is defined in IEEE 80 2.3 specifications and shown in Figure 1.2.

1.1.2 Data Paths

In each device, there is a transmit data path and a receive data path associated with

each PHY channel. T he transmit data path is from the Controller Interfac e to the

twisted-pair transmitter. The receive data pa th is from the tw isted- pair r eceive r to th e

Controller Interface.

SMSC DS – LAN83C183 11 Rev. 12/14/2000

Page 12

SMSC DS – LAN83C183 12 Rev. 12/14/2000

Figure 1.1 LAN83C183 Device Block Diagram

OSCIN

RESETn

RX_EN/JAMn

RPTR

TX_CLK

TXD[3:0]

TX_EN

TX_ER/TXD4

COL

RX_CLK

RXD[3:0]

CRS

RX_DV

RX_ER/RXD4

MDC

MDINTn/MDA4n

MDIO

PLED[3:0]n

MDA[3:0]n

PLED[5:4]n

VDD[6:1]

GND[6:1]

Oscillator

Controller

Interface

(MII

or

FBI)

Serial

Port

(MI)

LED

Drivers

Collision

4B5B

Encoder

Manchester

Encoder

4B5B

Decoder

Scrambler

Descrambler

100BASE-FX Transmitter

100BASE-TX Transmitter

MLT3

Encoder

10BASE-T Receiver

ROM DAC

Clock

Generator

PLL

Squelch

Clock

& Data

Recovery

Auto-

Negotiation

& Link

Squelch

Clock & Data

Recovery

(Manchester

Decoder)

Switched

Current

Sources

Clock

Generator

PLL

100BASE-TX Receiver

100BASE-TX Receiver

MLT3

Encoder

10BASE-TX Receiver

+

+

−

+

+

−

LP

Filter

LP

Filter

+/−

+/−

+

−

+

+

−

Vth

Vth

+

-

+

-

+

−

Vth

+/−

Vth

Adaptive

Equalizer

LP

Filter

REXT

+/

FXI

TPO

TPO−/FXI

SD_THR

SD/FXDISn

TPI+/FXO

TPI−/FXO

−

+

−

+

Page 13

Figure 1.2 100BASE-TX /FX and 10BASE-T Frame For mat

Interframe

Gap

IDLE PREAMBLE SFD ESD IDLE

IDLE PREAMBLE SFD ESD IDLE

PREAMBLE SFD DA SA LN

SSD DA SA LN LLC DATA FCS

PREAMBLE =

DA, SA, LN, LLC D ATA, FCS =

SSD DA SA LN LLC DATA FCS

PREAMBLE =

DA, SA, LN, LLC D ATA, FCS =

Ethernet MAC Frame

100BASE-TX Data Symbols

[ 1 1 1 1 ...]

IDLE =

[ 1 1 0 0 0 1 0 0 0 1 ]

SSD =

[ 1 0 1 0 ...] 62 Bits Long

[ 1 1 ]

SFD =

[ DATA ]

[ 0 1 1 0 1 0 0 1 1 1 ]

ESD =

100BASE-FX Data Symbols

[ 1 1 1 1 ...]

IDLE =

[ 1 1 0 0 0 1 0 0 0 1 ]

SSD =

[ 1 0 1 0 ...] 62 Bits Long

[ 1 1 ]

SFD =

[ DATA ]

[ 0 1 1 0 1 0 0 1 1 1 ]

ESD =

LLC Data

Before/After

4B5B Encoding,

Scrambling, and

MLT3 Coding

Before/After

4B5B Encoding

FCS

Interframe

Gap

10BASE-T Data Symbols

IDLE PREAMBLE SFD SOI IDLE

IDLE =

PREAMBLE =

SFD =

DA, SA, LN, LLC D ATA, FCS =

DA SA LN LLC DATA FCS

[ No Transitions ]

[ 1 0 1 0 ...] 62 Bits Long

[ 1 1 ]

[ DATA ]

[ 1 1 ] With No MID Bit

SOI =

Transition

Before/After

Manchester

Encoding

SMSC DS – LAN83C183 13 Rev. 12/14/2000

Page 14

1.1.2.1 100BASE-TX

In 100BASE-TX transm it operation, data is received on th e Controller Inte rface from

an external Ethernet cont roller in the format shown in Figure 1.3 and Table 1.1. The

data is sent to the 4B5B encoder, which scrambles the encoded data. The scrambled

data is then sent to the TP tr ansm itter. The TP transmitter conv erts the enc oded an d

scrambled data into MLT 3 ternary format, presha pes the output, and drives the

twisted-pair cable.

TX_EN = 0

IDLE

First Bit

First

Nibble

TXD0/RXD0

MII

Nibble

Stream

TXD1/RXD1

TXD2/RXD2

TXD3/RXD3

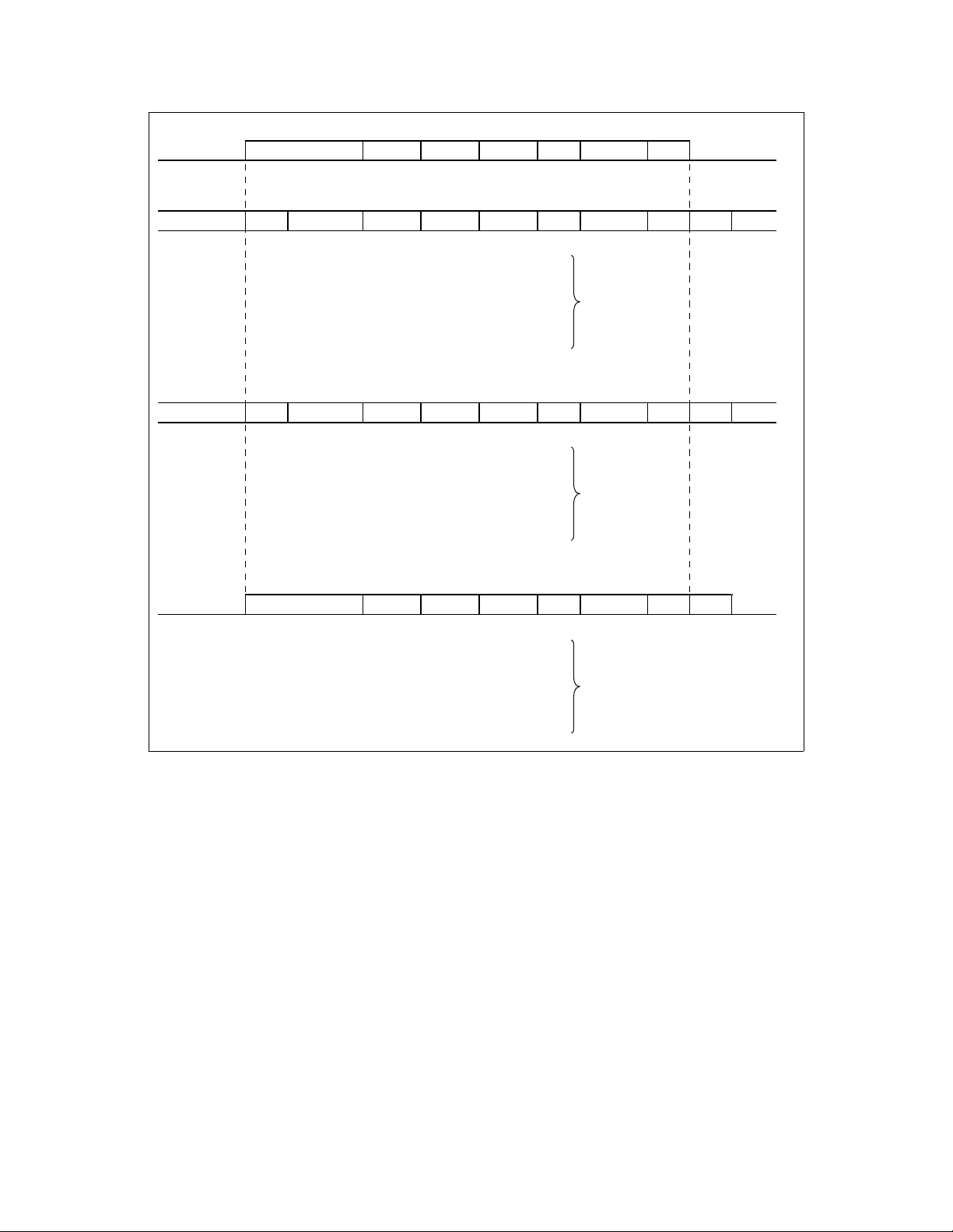

Figure 1.3 MII Fram e Format

a. MII Frame Format

Start

of

PREAMBLE

PRMBLE SFD DATA 1

62 Bits 2 Bits

LSB

D0

Frame

PREAMBLE =

SFD =

DATAn =

IDLE =

b. MII Nibble Order

MAC Serial Bit Stream

D1 D2 D3 D4

TX_EN = 1

DATA Nibbles

DATA 2 DATA N-1 DATA N

[ 1 0 1 0 ...] 62 Bits Long

[ 1 1 ]

[Between 64

[TX_EN = 0]

−1518 Data Bytes]

TX_EN = 0

IDLE

D5 D6 D7

MSB

Second

Nibble

Table 1.1 Transmit Preamble and SFD Bit s at MAC Nibble Interface

Signals Bit Value

TXDO X X 1

TXD1XX0000000000000000D1D5

TXD2XX1111111111111111D2D6

TXD3XX0000000000000001D3D7

TX_EN00111111111111111111

1

11111111111111

2

3

1D0

D4

1. 1st preamb le nibble tr ansmitted.

2. 1st SFD nibble transmitted.

3. 1st data nibble transmitted.

4. D0 through D7 are the first 8 bits of the data field.

In 100BASE-TX rece ive operation, the TP r eceiver takes incom ing encoded and

scrambled MLT3 data from the twisted-pair cab le , re mov es an y hi gh -fr eq uen cy no is e

from the input, eq ualizes the inp ut signal t o compensate fo r the effects of th e cable,

performs baseline wande r correc ti on, qua li fie s the dat a with a squelc h alg or ithm, and

converts the data from MLT3-encoded levels to internal digital level s. The output of

the receiver then goes to a clock a nd data rec overy block that recover s a clock from

the incoming data, uses the clock to latch valid data into the device, and converts

the data back to NRZ form at. The 4B5B decoder and descr amb le r th en d ec odes an d

unscrambles the NRZ data, res pectively, and sends it out of the Controller Interface

4

SMSC DS – LAN83C183 14 Rev. 12/14/2000

Page 15

to an external Ether net controller. The format of the received data at the Controller

interface is as sh own in Table 1.2.

Table 1.2 Receive Pre amble and SFD Bits at MAC Nib ble Interface

Signals Bit Value

RXDO X 1

RXD1X00000000000000000D1D5

RXD2X11111111111111111D2D6

RXD3X00000000000000001D3D7

RX_DV01111111111111111111

1. First preamble nibble received. Depending on the mode, the device may eliminate either all or some

of the preamble nibbles, up to the first SFD nibble.

2. First SFD nibble received.

3. First data nibble received.

4. D0 through D7 are the first 8 bits of the data field.

1

11111111111111121D03D4

1.1.2.2 100BASE-FX

100BASE-FX oper ation is similar to 10 0BASE-TX operation except:

• The transmit output/r eceive input is not scrambled or MLT3 encoded

• The transmit data is output to a FX transmitter instead of the TP waveshaper/

transmitter

• The receive data is inp ut to the FX ECL level dete ctor instead of the equali zer

and associated T P circuitry

• The FX Interface has a signal detect input

4

1.1.2.3 10BASE-T

10BASE-T operation is similar to the 100B ASE-TX operation exce pt:

• There is no scrambler /descrambler

• The encoder/decode r is Manchester inst ead of 4B5B

• The data rate is 10 M bits/s instead of 100 M bits/s,

• The twisted-pair s ymbol data is two-leve l Manchester instead of ternary MLT-3.

• The transmitter generates link pulses during the idle period

• The transmitter de tects the jabber conditi on

• The receiver detects l ink pulses and implements th e AutoNegotiation algor ithm

SMSC DS – LAN83C183 15 Rev. 12/14/2000

Page 16

1.2 BLOCK DIAGRAM DESCRIPTION

The LAN83C183 PHY dev ice has the following main b locks:

• Oscillator and Clock

• Controller Interface

• 4B5B/Manchester En coder/Decoder

• Scrambler/Descrambler

• Twisted-Pair Transmitters

• Fiber Transmitter

• Twisted-Pair Receivers

• Fiber Receiver

• Clock and Data Recovery

• AutoNegotiation/Link I ntegrity

• Descrambler

• Collision Detection

• LED Drivers

A Management Interfa ce (MI) serial port prov ides access to 11 internal PHY

registers.

Figure 1.1 sh ows the main bloc ks, along with the ir associated signals. The fo llowing

sections describe each of the blocks in Figure 1.1. The perfo rmance of the device in

both the 10 and 100 Mbi ts/s modes is descri bed.

1.2.1 Oscillator and Clock

The LAN83C183 requir es a 25 MHz reference f requency for internal si gnal

generation. This 25 MHz refer ence freq uency is genera ted with ei ther an ex ternal 25

MHz crystal connecte d between OSCIN and GND or w ith the application of an

external 25-MHz clock to OSCIN.

The device provides eit her a 2.5-MHz or 25-MHz refer ence clock at the TX_CLK or

RX_CLK output pins f or 10-MHz or 100-MHz o peration, respectivel y.

1.2.2 Controller Interface

This section desc ribes the controller inter face operation. The LA N83C183 has two

interfaces to an exte rnal controller:

• Media Independent Int erface (MII)

• Five Bit Interface (FBI)

1.2.2.1 MII INTERFACE

The device has an M II interface to an external E thernet Media Access Cont roller

(MAC).

MII (100 Mbits/s) – The MII is a nibble wide packet dat a interface defined in IEEE

802.3 and shown in Figure 1.3. The LAN83C183 mee ts all the MII requireme nts

outlined in IEEE 802.3 . The LAN83C183 can dire ctly connect, without any external

logic, to any Ethern et controller or other devi ce that also complies wi th the IEEE

802.3 MII specificati ons.

SMSC DS – LAN83C183 16 Rev. 12/14/2000

Page 17

The MII interface co ntains the following sign als:

• Transmit data bits (TXD[3:0])

• Transmit clock (TX _CLK)

• Transmit enable (TX_EN)

• Transmit error (TX_ER)

• Receive data bits (RXD[3 :0])

• Receive cloc k (RX_CLK)

• Carrier sense (CRS)

• Receive data valid (RX _DV)

• Receive data error (RX_ER)

• Collision (COL)

The transmit and re ceive clocks operate a t 25 MHz in 100 Mbits/s mode.

On the transmit side, the TX_CLK output runs continuously at 25 MHz. When no data

is to be transmit ted, TX_EN must be deass erted. While TX_EN is dea sserted,

TX_ER and TXD[3:0] are ignored and no data is cl ocked into the device. Whe n

TX_EN is asserted on the rising edge of TX_CLK, data on TXD[3:0] is clocked into

the device on the risin g edge of the TX_CLK output c lock. TXD[3:0] input da ta is

nibble wide packet data whos e format must be the sam e as specified in IEEE 802.3

and shown in Figure 1.3. When a ll data on TXD[3:0] has been l atched into the

device, TX_EN must be deasserted on the rising e dge of TX_CLK.

TX_ER is also clocked in on the rising edge of TX_CLK. TX_ER is a trans mit error

signal. When th is signal is asserted, the device substitutes an er ror nibble in place

of the normal data nibble that was clocked in on TXD[3: 0]. The erro r nib ble is defined

to be the /H/ symbol, whic h is defined in IEEE 80 2.3 and shown in Table 1.3.

SMSC DS – LAN83C183 17 Rev. 12/14/2000

Page 18

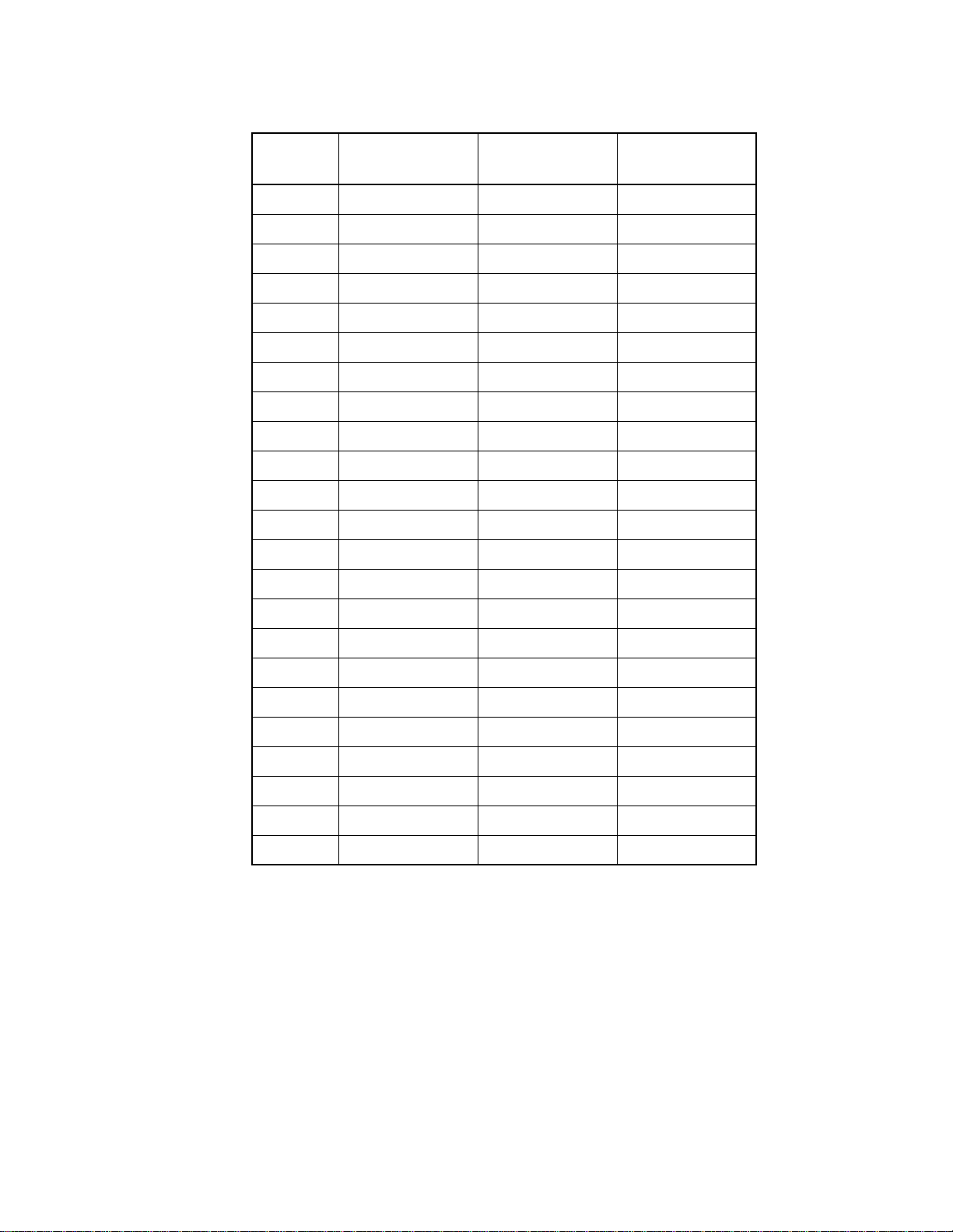

Ta ble 1.3 4B/5B Symbol Mapping

Symbol

Name Description 5B Code 4B Code

0 Data 0 0b11110 0b0000

1 Data 1 0b01001 0b0001

2 Data 2 0b10100 0b0010

3 Data 3 0b10101 0b0011

4 Data 4 0b01010 0b0100

5 Data 5 0b01011 0b0101

6 Data 6 0b01110 0b0110

7 Data 7 0b01111 0b0111

8 Data 8 0b10010 0b1000

9 Data 9 0b10011 0b1001

A Data A 0b10110 0b1010

B Data B 0b10111 0b1011

C Data C 0b11010 0b1100

D Data D 0b11011 0b1101

E Data E 0b11100 0b1110

F Data F 0b11101 0b1111

I Idle 0b11111 0b0000

J SSD #1 0b11000 0b0101

K SSD #2 0b10001 0b0101

T ESD #1 0b01101 0b0000

R ESD #2 0b00111 0b0000

H Halt 0b00100 Undefined

1

– Invalid codes All others

1. These 5B codes are not used. The decoder decodes these 5B codes to

4B 0000. The encoder encodes 4B 0000 to 5B 11110, as shown in symbol

Data 0.

0b0000*

Because the OSCIN in put clock generates the TX_CLK output clock, the T XD[3:0],

TX_EN, and TX_ER sig nals are also clocked i n on rising edges of OSCIN.

On the receive side, a s lon g as a val id dat a pa ck et i s not d etected, CRS and RX_DV

are deasserted and the RXD[3:0] sig nals are held L OW. When the start of pack et is

detected, CRS and RX_ DV are asserted on the fal ling edge of RX_CLK. The

assertion of RX_DV indicates that valid data is clocked out on RXD[3:0] on the falling

edge of the RX_CLK. The R XD[3:0] data has the same frame structure as the

TXD[3:0] data and is specified in IEE E 80 2.3 an d sho wn in Figure 1.3. When the end

SMSC DS – LAN83C183 18 Rev. 12/14/2000

Page 19

of the packet is detec ted, CRS and RX_DV are deas serted, and RXD[3:0] is hel d

LOW. CRS and RX_DV also stay deasser ted if the device is in the L ink Fail State.

RX_ER is a receive erro r output tha t is as serte d when ce rtain errors ar e detec ted on

a data nibble. RX_ER i s asserted on the falling edge of RX_ CLK for the duratio n of

that RX_CLK clock cyc le during which the nibble c ontaining the error is ou tput on

RXD[3:0].

The collision output, COL, is asserted whenev er the collision cond ition is detected.

MII (10 Mbits/s) – MII 10 Mbits/s operation is identical to 100 Mbits/s operation except:

• The TX_CLK and RX_CLK c lock frequency is reduc ed to 2.5 MHz

• TX_ER is ignored

• RX_ER is disable d and always held LOW

• Receive operation is modified as follows:

On the receive side, w hen the squelch circuit d etermines that invalid data is

present on the TP in puts, the receiver is id le. During idle, RX_CLK follows

TX_CLK, RXD[3:0] is held LOW, and CRS and RX_DV are dea sserted. When a

start of packet is d etected on the TP receive i nputs, CRS is asserted and the

clock recovery pr ocess starts on the i ncoming TP input data. After the receive

clock has been recov ered from the data, the RX_ CLK is switched over to the

recovered clock an d the data valid signal RX_DV is asserted on a falling e dge

of RX_CLK. Once RX_DV is asse rted, valid data is clocked out on RXD [3:0] on

the falling edge of RX_CL K. The RXD[3:0] data has the same packet structure

as the TXD[3:0] data and is formatted on RXD[3:0] as specified in IEEE 802.3

and shown in Figure 1.3. When the end o f packet is detect ed, CRS and RX_DV

are deasserted. CR S and RX_DV also stay deasserted as long as the devic e is

in the Link Fail Sta te.

1.2.2.2 FBI INTERFACE

The Five Bit Interface (als o referred to as FBI) is a five- bit wide interface that is

produced when the 4B 5B encoder/decoder is b ypassed. The FBI is prim arily used

for repeaters or Ethe rnet controllers that hav e integrated encoder/dec oders.

The FBI is identical to the MII except:

• The FBI data path is fiv e bits wide, not nibble wid e like the MII

• The TX_ER pin is recon figured to be the fifth transm it data bit (TXD4)

• The RX_ER pin is reco nfigured to be the fifth recei ve data bit (RXD4)

• CRS is asserted as long as the device is i n the Link Pass State

• COL is not valid

• RX_DV is not valid

• The TX_EN pin is ignored

There is no FBI operati on in the 10 Mbits/s mode.

1.2.2.3 SELECTION OF M II OR FBI

FBI Selection – The FBI is automa tical ly enab led when the 4B 5B en coder/ deco der is

bypassed. Bypassing the encoder/decoder passes the 5B symbols between th e

receiver/transm itter directly to the FBI without any alterations o r substitutions. To

SMSC DS – LAN83C183 19 Rev. 12/14/2000

Page 20

bypass the 4B5B encoder/decoder, set the Bypass Encoder bit (BYP_ENC) in the MI

serial port Configu ration 1 register.

When the FBI is enab led, it may also be des irable to bypass the

scrambler/descr ambler and disable the internal CRS loopbac k function. To bypass

the scrambler/descramb le r, set the Bypass Scramb ler bit (BYP_SCR) in the MI ser ia l

port Configuration 1 r egister. To disable the internal CRS loopback, set the TX_E N

to CRS loopback disab le bit (TXEN_CRS) in the MI serial port Configura tion 1

register.

MII Selection – To disable the MII (and FBI) in puts and outpu ts, set the MII_DIS bi t in

the MI serial por t Control register. When the MII is disabled, the MII an d FBI inputs

are ignored, and the MII, FBI, and TPI outputs ar e place d in a high-im pedanc e state.

The MII pins affected are:

• RX_CLK

• RXD[3:0]

• RX_DV

• RX_ER

• COL

If the MI address line s, MDA[4:0]n, are pulled HIGH during reset or poweru p, the

LAN83C183 powers up and resets with the MII and FBI d isabled. Otherwise, the

LAN83C183 powers up and resets with the MII and FBI e nabled.

In addition, when the R/ J_CFG bit in the MI serial port Configuration 1 re gister is

LOW, the RX_EN/JAMn pin is configu red for RX_EN ope ration. If the RX_E N pin is

LOW in this situation, the MII controller inter face outputs are placed in the highimpedance state.

1.2.3 Encoder

This section descr ibes the 4B5B e ncoder, which is used in 100 Mbi ts/s operatio n. It

also describes the Ma nchester Encoder, used in 10BASE-T oper ation.

1.2.3.1 4B5B ENCODER (10 0 MBITS/S)

100BASE-TX ope ration requires that the d ata be 4B 5B en co ded. The 4B5B Encoder

block shown in Figure 1.1 converts the four-bit da ta nibbles into five-bit data words.

The mapping of the 4 B nibbles to 5B codew ords is specified in IEE E 802.3 and is

shown in Table 1.4.

SMSC DS – LAN83C183 20 Rev. 12/14/2000

Page 21

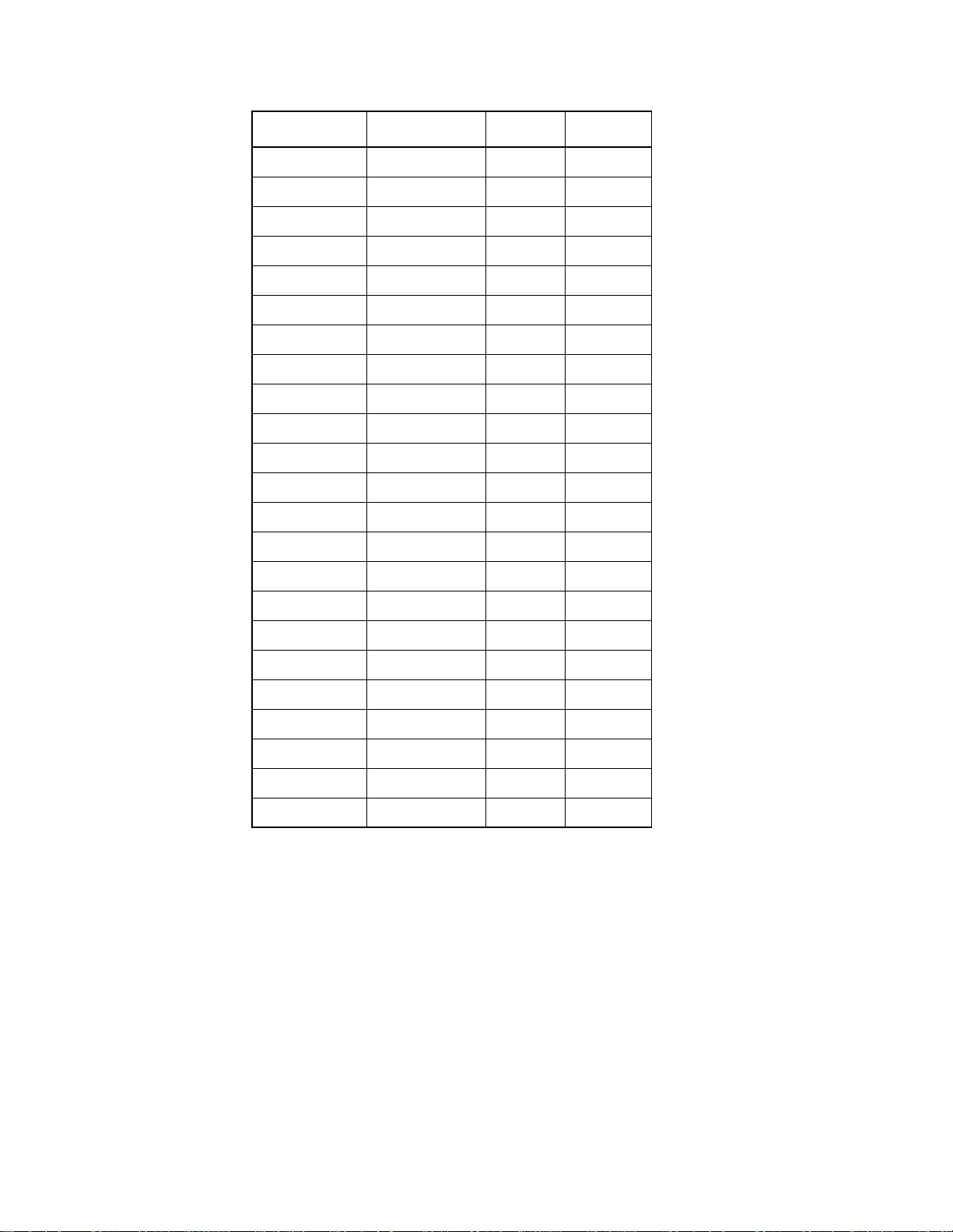

Table 1.4 4B/5B Symbol Mapping

Symbol Name Description 5B Code 4B Code

0 Da t a 0 1111 0 00 0 0

1 Data 1 01001 0001

2 Data 2 10100 0010

3 Data 3 10101 0011

4 Data 4 01010 0100

5 Data 5 010 11 0101

6 Data 6 01110 0110

7 Da t a 7 0 1111 0 111

8 Data 8 10010 1000

9 Data 9 100 11 1001

A Data A 10110 1010

B Da t a B 10 111 1 0 11

C Data C 11010 1100

D Data D 11011 1101

E Data E 111 00 1110

F D a t a F 1110 1 1111

I Idle 11111 0000

J SSD #1 11000 0101

K SSD #2 10001 0101

T ESD #1 01101 0000

R ESD #2 00111 0000

H Halt 00100 Undefined

1

--- Invalid codes All others

1. These 5B codes are not used. The decoder converts them

to a 4B code of 0000. The encoder converts the 4B 0000

co d e t o t h e 5 B 1111 0 c od e , a s s h o w n i n sy m b o l 0 .

0000

The 4B5B encoder takes 4B (four-bit) nibbles from the Transmit MAC block, converts

them into 5B (five-bit) words accordin g to Table 1.4, a nd sends the 5B words to the

scrambler. The 4B5B encoder also substitutes the first eight bits of the preamble with

the Start of Stream Del imiter (SSD) (/J/K/ symb ols) and adds an End of S tream

Delimiter (ESD) (/T/R/ symb ols) to the end of each pack et, as defined in IE EE 802.3

and shown in Figure 1.2. The 4B5 B encoder also fills t he period between packets

(idle period), with a c ontinuous stream of idl e symbols, as shown in Figure 1.2.

1.2.3.2 MANCHESTER ENCODER (10 MBITS/S)

The Manchester Enc oder shown in Figure 1.1 is used for 10 Mbits/s operation. It

combines clock and non-retu rn to zero inverte d (NRZI) data suc h that the first half of

SMSC DS – LAN83C183 21 Rev. 12/14/2000

Page 22

the data bit contains the c ompleme nt of the data, a nd the second half of the da ta bit

contains the true data , as specified in IEEE 802.3. This process guar antees that a

transition always oc curs in the middle o f the bi t cell . The Ma nches ter en coder o n the

device converts the 10 Mbits/s NRZI data from the Ethernet co ntroller interface into

a single data stream for the T P tran smitter and adds a start of id le puls e (S OI) at the

end of the packet as sp ecified in IEEE 802.3 and shown in Figure 1.2. The

Manchester encodin g process is only do ne on actual packet data; du ring the idle

period between packe ts, no signal is transm itted except for period ic link pulses.

1.2.3.3 ENCODER BYPASS

Setting the Bypass Encoder/Decoder bit (BYP_ENC) in the MI serial port

Configuration 1 regis ter bypasses the 4B5B encoder. When this bit is set, 5B code

words are passed directly from the c ontroller interface to the scrambler without any

of the alterations described in Section 1.2.3 .1, “4B5B Encoder (100 Mbits/s ),”

page 1-20. S etting the bit automatically places the device in the FBI mode as

described in the subsection entitled “FB I Selection” on page 1-19.

1.2.4 Decoder

This section desc ribes the 4B5B decode r, used in 100 Mbits/s operation, whic h

converts 5B encoded data to 4B nib bles. It also describes th e Manchester D ecoder,

used in 10BASE-T oper ation.

1.2.4.1 4B5B DECODER (10 0 MBITS/S)

Because the TP inp ut data is 4B5B encode d on the transmi t side, th e 4B5B decod er

must decode it on the r eceive side. The mapping of the 5B codewords to the 4 B

nibbles is specifi ed in IEEE 802.3. T he 4B5B dec oder takes th e 5B codewords f rom

the descrambler, converts them int o 4B nibbles according to Table 1.4, and s ends

the 4B nibbles to the r eceive Ethernet contr oller.

The 4B5B decoder also strips off the SSD delimiter (/J/K/ symbols), and replaces it

with two 4B Data 5 nibb les (/5/ symbol). It also strips off the ESD delimiter (/T /R/

symbols), and rep laces it with two 4B Data 0 nibb les

(/I/ symbol), per IEEE 8 02.3 specifications (see Figure 1.2).

The 4B5B decoder detec ts SSD, ESD, and codeword er rors in the incoming dat a

stream as specifi ed in IEEE 802.3. To indicate these errors, the device asser ts the

RX_ER output as well as the SS D, ESD, and CWRD bits in the MI seria l port Status

Output register while the errors are being transm itted across RXD[3:0 ].

1.2.4.2 MANCHESTER DECODER (10 MBITS/S)

In Manchester coded data, the first half of the data bit contains the com plement of

the data, and the s econd half of the da ta bit contains the true dat a. The M ancheste r

Decoder converts the s ing le data str ea m from the TP receiver into n on- retur n to z ero

(NRZ) data for the cont roller interface. To do this, it decodes the data and s trips off

the SOI pulse. Becau se the Clock and Data Recovery bloc k has already s eparated

the clock and data fr om the TP receiver, that block inherentl y performs the the

Manchester deco ding.

1.2.4.3 DECODER BYPASS

Setting the Bypass Encoder/Decoder bit (BYP_ENC) in the MI serial port

Configuration 1 regis ter bypasses the 4B5B decoder. When this bit is set, 5B code

words are passed directly to the controller interface from the descrambler without any

of the alterations described in Sect ion 1.2.4, “Decoder,” page 1-22. Additionally, the

SMSC DS – LAN83C183 22 Rev. 12/14/2000

Page 23

CRS pin is continuous ly asserted whenever the device is in the Link P ass state.

Setting the bit autom atically places the devi ce in the FBI mode as des cribed in the

subsection entitled “FBI Selection” on page 1-19.

1.2.5 Scrambler

100BASE-TX tran smission requi res scramblin g to reduce the radi ated emission s on

the twisted pair. The scrambler takes the NRZI encoded data from the 4B5B encoder,

scrambles it per the IEEE 8 02.3 specific ations, and se nds it to the TP transmitter. A

scrambler is not used for 10 Mbits/s oper ation.

1.2.5.1 SCRAMBLER BYPASS

Setting the Bypass Encoder/Decoder bit (BYP_SCR) in the MI serial port

Configuration 1 register bypasses the scrambler. When this bit is set, 5B data

bypasses the scramb ler and goes directly to the 100BASE-TX trans mitter.

1.2.6 Descrambler

The descramble r block shown in Figure 1.1 is us ed in 100BASE-TX operati on. The

device descrambler tak es the scrambled NRZI data from the data recovery block,

descrambles it acco rding to IEE E 802.3 specifi cations , alig ns the data on t he corr ect

5B word boundaries, and sends it to the 4B5B decoder.

The algorithm for sync hronization of the descr ambler is the same as the algorithm

outlined in the IEE E 802.3 specificatio n.

After the descrambl er is synchronize d, it maintains synchr onization as long as

enough descrambled idle pattern ones are det ected within a given i nterval. To st ay

in synchronizati on, the descrambler nee ds to detect at least 25 consecutive

descrambled idle patte rn ones in a 1 ms interv al. If 25 consecuti ve descram bled idle

pattern ones are not d etected within the 1 ms interval, the descram bler goes out of

synchronization and restarts the synch ronization process.

If the descrambler i s in the unsynchronized state, the descrambl er Loss of

Synchronization D etect bit (LOSS_SYNC) is s et in the MI serial port S tatus Output

register. The bit stays set until t he descrambler achie ves synchronization.

The descrambler is disabled for 10BAS E-T operation.

1.2.6.1 DESCRAMBLER BYPASS

Setting the Bypass Encoder/Decoder bit (BYP_SCR) in the MI serial port

Configuration 1 regis ter bypasses the des crambler. When this bit is set, 5B data

bypasses the descra mbler and goes directly f rom the

100BASE-T rece iver to the 4B5B decoder.

SMSC DS – LAN83C183 23 Rev. 12/14/2000

Page 24

1.2.7 Twisted-Pair Transmitters

This section desc ribes the operation of t he 10 and 100 Mbits/s TP transmitters.

1.2.7.1 100 MBITS/S TP TRANSMITTER

The TP transmitter co ns ists of an M LT3 encoder, waveform generator, and line driver.

The MLT3 encoder converts the NRZI data from the scrambler into a three-level code

required by IEEE 802.3 . MLT3 coding uses three l evels, converting ones t o

transitions between the three le vels, and z eros to no tr ansitions or changes i n level.

The purpose of the wavefo rm generator is to sha pe the transmit output puls e. The

waveform generator tak es the MLT3 three level encoded waveform and uses a n

array of switched c urrent sources to c ontrol the shape of the tw isted-pair output

signal. The wave form generator consists of switched curren t sources, a clock

generator, filter, and logic. The switched current sources contr ol the rise and fall time

as well as signal l evel to meet IEEE 802.3 req uirement s. The output of t he switc hed

current sources goe s through a second orde r low-pass filter that “smooths” the

current output and removes any high-fr equency components. In this way, the

waveform generator preshapes the output waveform transmitted onto the twisted-pair

cable such that the wav eform meets the pulse templ ate requirements outlined i n

IEEE 802.3. The waveform genera tor eliminates the need for an y external fi lters on

the TP transmit output.

The line driver c onverts the shap ed and smoot hed waveform to a c urrent output that

can drive greater than 100 meters of category 5 uns hi eld ed twisted-pair cable or 1 50ohm shielded twisted- pair cable.

1.2.7.2 10 MBITS/S TP TRANSMITTER

Even though the 10 Mbits /s transmitter operation is m uch different than that of 100

Mbits/s, it also con sists of a waveform gene rator and line driver ( see Figure 1.1).

The waveform generator, which consists of a ROM, DAC, clock generator, and filter,

shapes the output tr an sm it pul se . T he DAC gen er ates a stair-stepped repre se ntat ion

of the desired output waveform. The stairstepped DAC output then is passed through

a low-pass filter to “smooth” the DAC outpu t and remove any high-fre quency

components. The DAC va lues are determined fr om the data at the ROM addres ses.

The data is chosen to shape the pulse to the desired templ ate. The clock generato r

clocks the data into the DAC at high speed. In this way, the waveform generat or

preshapes the output wave form to be tra nsmitted on to the twis ted-p air cable to me et

the pulse template r equirements outlined i n IEEE 802.3 Clause 14 and shown in

Figure 1.4 an d Table 1.5. The waveshaper replaces and el imi na tes ex ter na l filte rs on

the TP transmit output.

The line driver c onverts the shap ed and smoot hed waveform to a c urrent output that

can drive greater than 100 meters of category 3/4/5 100- o hm un shi el ded twis ted -p air

cable or 150-ohm s hielded twisted-pair cabl e without any external fi lters.

During the idle period, no output signals are tran smitted on the TP outputs ex cep t for

link pulses.

SMSC DS – LAN83C183 24 Rev. 12/14/2000

Page 25

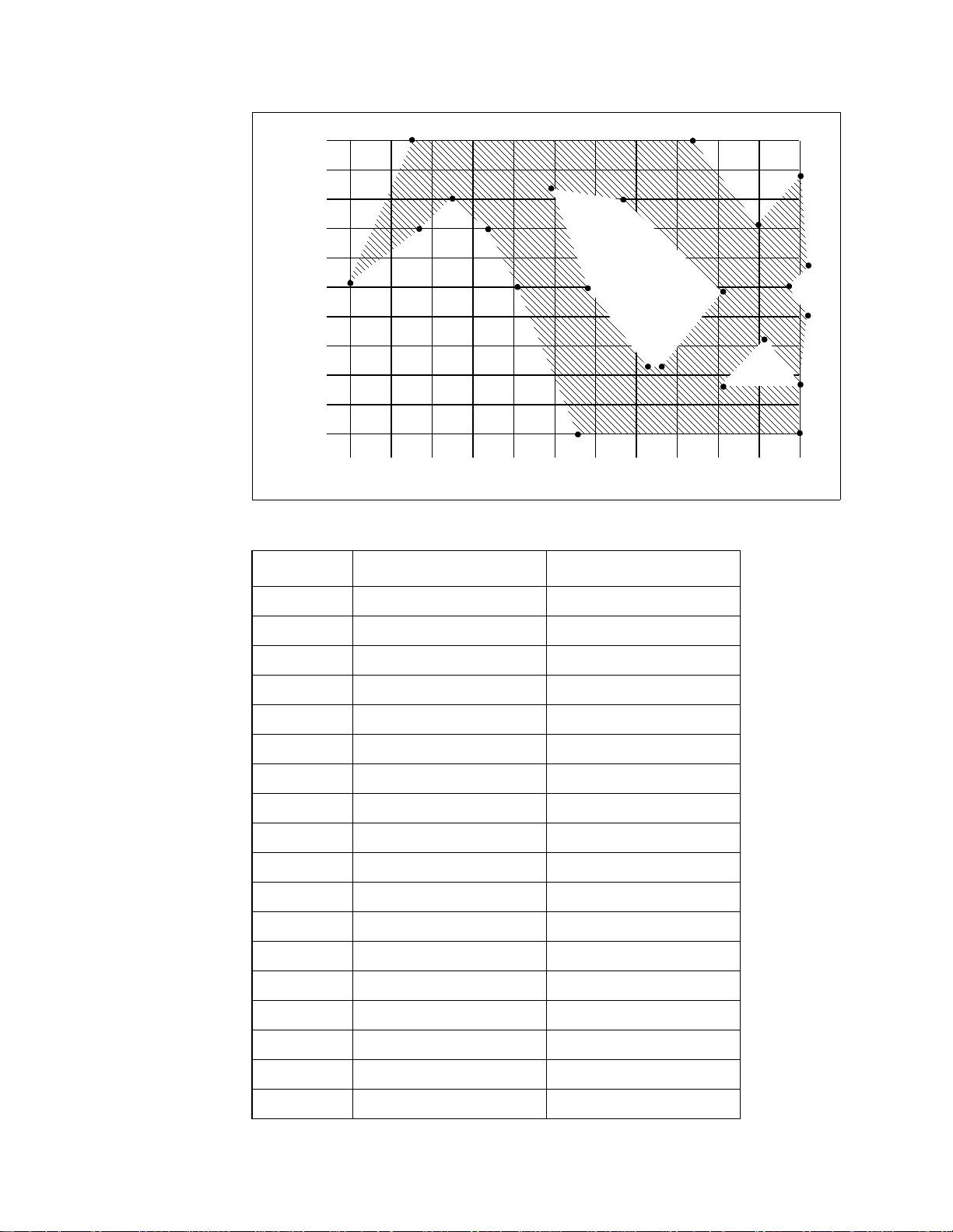

Figure 1.4 TP Output Voltage Template

T

Voltage (V)

1.0

0.8

0.6

0.4

0.2

0.0

- 0.2

- 0.4

- 0.6

- 0.8

- 1.0

A

0102030405060708090100110

B

D

C

E

Time (ns)

H

F

G

I

M

Table 1.5 TP Outpu t Vo ltage - 10 Mbits/s

Reference Time (ns) Internal MAU Voltage (V)

L K

N

P

O

Q

J

W

R

S

U

V

T

A0 0

B15 1.0

C15 0.4

D25 0.55

E32 0.45

F39 0

G57 −1.0

H48 0.7

I67 0.6

J89 0

K74 −0.55

L73 −0.55

M61 0

N85 1.0

O100 0.4

P 110 0.75

Q 111 0.15

R 111 0

SMSC DS – LAN83C183 25 Rev. 12/14/2000

Page 26

Table 1.5 TP Output Voltage - 10 Mbits/s (Cont.)

Reference Time (ns) Internal MAU Voltage (V)

S 111 −0.15

T110 −1.0

U100 −0.3

V110 −0.7

W90 −0.7

1.2.7.3 TRANSMIT LEVEL ADJUST

The transmit output c urrent level is deriv ed from an internal refe rence voltage and

the external resisto r on the REXT pin. The trans mit leve l can be adjusted with either :

• The external resis tor on the REXT pin, or

• The four Transmit Level Adjus t bi ts (T LVL[3:0]) in the MI serial p ort Conf igu ra tio n

1 register as shown in Table 1.6. The adjustment range is approx imately -14%

to +16% in 2% steps.

Table 1.6 Transmit Level Adjust

TLVL[3:0]

Bits Gain

0000 1.16

0001 1.14

0010 1.12

0011 1.10

0100 1.08

0101 1.06

0110 1.04

0111 1.02

1000 1.00

1001 0.98

1010 0.96

1011 0.94

1100 0.92

1101 0.90

1110 0.88

1111 0.86

SMSC DS – LAN83C183 26 Rev. 12/14/2000

Page 27

1.2.7.4 TRANSMIT RISE AND FALL TIME ADJUST

The transmit output ri se and fal l t ime c an b e ad jus te d wi th th e two Transmit Rise/ F all

time adjust bits (TRF[1:0]) in the MI serial port Configuration 1 register. The

adjustment range is

−0.25 ns to +0.5 ns in 0.25 ns steps.

1.2.7.5 STP (150 OHM) CABLE MODE

The transmitter can b e configured to drive 15 0 Ω shielded twisted-pair cable. To

enable this configurati on, set the Cable Type Select bit (CABLE) in the MI serial port

Configuration 1 regis ter. When STP mode is enabled, the ou tput current is

automatically ad justed to comply with IEE E 802.3 levels.

1.2.7.6 TRANSMIT ACTIVITY INDICATION

Appropriately setting the programmable LED Output Sel ect bits in the MI serial port

LED Configuration 2 re gister programs trans mit activity to appear on s ome of the

PLED[5:0]n pins. When one or more of t he PLE D[5:0]n p ins is program med to b e an

activity or transmit a ctivity detect outpu t, that pin is asserted LOW for 100 ms eve ry

time a transmit pa cket occurs. The PLED[5:0]n outp uts are open-drain with resistor

pullup and can driv e an LED from V

1.2.14, “LED Drivers,” page 1-36 for more detailed i nformation on the LED output s.

1.2.7.7 TRANSMIT DISABLE

Setting the Transmit Disable bi t (XMT_DIS) in the MI se rial port Configuration 1

register disables the TP trans mitter. When the bit is set, the TP transmitter is forced

into the idle state, n o data is t ransmitted, no link p ulses are transmitted , and inter nal

loopback is disab led.

or can drive othe r digital inpu ts. See Section

DD

1.2.7.8 TRANSMIT POWERDOWN

Setting the Transmit Powerdown b it (XMT_PDN) in the MI serial p ort Configuration

1 register powers down the TP transmitte r. When the bit is set, the TP transm itter is

powered down, the TP tr ansmit outputs are high impedance, and the rest of the

LAN83C183 operates normall y.

1.2.8 Twisted-Pair Receivers

The device is capabl e of operating at either 10 - or 100-Mbits/s. This section

describes the twisted-pa ir receivers and squelc h operation for both modes of

operation.

1.2.8.1 100 MBITS/S TP RECEIVE R

The TP receiver de tects input si gnals from the twi sted-pair inpu t and converts them

to a digital data bit stream ready for clock and data recovery. The receiver can

reliably detect 100BASE-TX compliant transmitter data that has been passed through

0 to 100 meters of

Ω category 5 UTP or 150-ohm STP cable.

100

The 100 Mbits/s rec eiver consists of an adaptive equalizer, baseline wander

correction circuit, c omparators, and an MLT3 decoder. The TP inputs first go to an

adaptive equalizer. The adaptive equal izer compensates for the low-pass

characteristics of the cable, and can adapt and compensate for 0 to 10 0 meters of

category 5, 100-ohm o r 150-ohm STP cable. T he baseline wander correction circuit

restores the DC compone nt of the input waveform th at the external transforme rs

have removed. The com parators convert the e qualized signal back to digital levels

and qualify the data with th e squel ch circ uit. T he MLT3 decoder takes the three- leve l

SMSC DS – LAN83C183 27 Rev. 12/14/2000

Page 28

MLT3 encoded outpu t data from the comparator s and converts it to nor mal digital

data to be used for clock and data recovery.

1.2.8.2 10 MBITS/S TP RECEIVER

The 10 Mbits/s rece iver detects input signa ls from the twisted-pai r cable that are

within t h e te m pl a te sh o w n i n Figure 1.5 The TP inputs are biased by internal resistors

and go through a low-pa ss filter designed to e liminate any high-freq uency input

noise. The output of the receive filter goes t o two different types of comparator s:

squelch and zero c rossing. The squelch comp arator determines wheth er the signal

is valid, and the zero crossing comparator senses the actual data transitions after the

signal is determin ed to be valid. The out put of the squelch comparator goes to the

squelch circuit and is also used fo r link pulse detec tion, SOI detection, and reverse

polarity detection. T he output of the zero-crossi ng comparator is used for clock and

data recovery in the M anchester decoder.

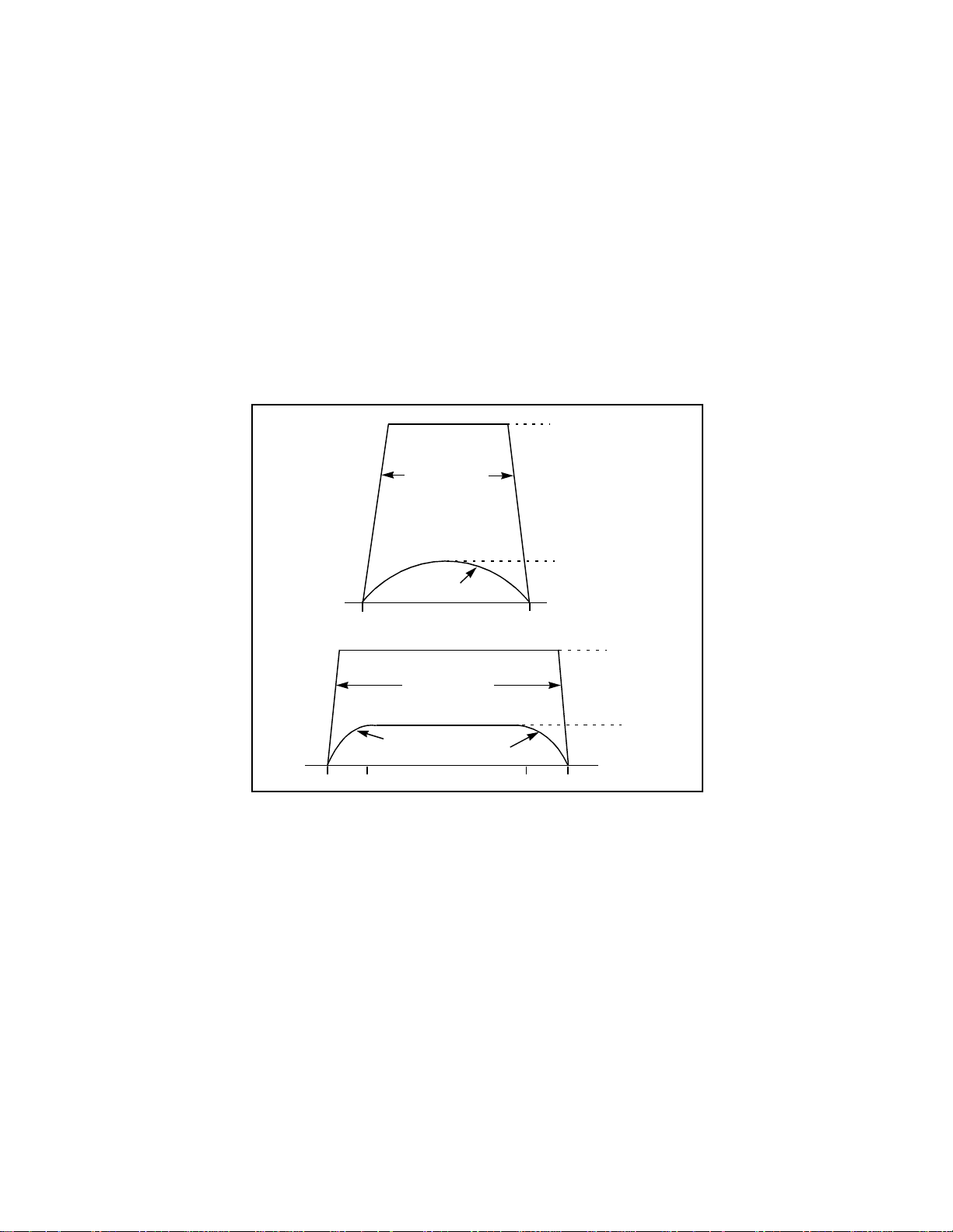

Figure 1.5 TP Input Voltage Template (10 Mbits/s)

0 PW/4 3PW/4 PW

1.2.8.3 SQUELCH (100 MBITS/S)

The Squelch block determines if the TP inpu t contains valid data. T he 100 Mbits/s

TP squelch is one of th e criteria used to deter mine link integrity. The squelch

comparators compa re the TP inputs agains t fixed positive and nega tive thresholds,

called squelch lev els. The output from the squelch comparat or goes to a digital

squelch circuit, which d eter mines whether the rec ei ve inpu t data on that po rt i s vali d.

If the data is invalid , the receiver is in th e squelched state. If the in put voltage

exceeds the squelch levels at least fou r times with a lternating p olarity within a 10

interval, the squel ch circuit det ermines that th e data is valid a nd the receiv er enters

into the unsquelch state.

Short Bit

Slope 0.5 V/ns

585 mV sin (π ∗ t/PW)

0PW

Long Bit

Slope 0.5 V/ns

585 mV sin (

585 mV sin[2

π ∗ t/PW)

π (t − PW2)/PW)]

3.1 V

585 mV

3.1 V

585 mV

µs

In the unsquelch state, the receive thres hold level is re duced by approxim ately 30%

for noise immunity reasons and is called the unsquelch level. When the receiver is

in the unsquelch stat e, the input signal is considered valid.

SMSC DS – LAN83C183 28 Rev. 12/14/2000

Page 29

The device stays in the unsquelch state un til loss of data is detec ted. Loss of data

is detected if no alter nating polarity unsque lch trans ition s are de tected during any 10

µs interval. When a l oss of data is detected, the receive squelc h is turned on again .

1.2.8.4 SQUELCH (10 MBITS/S)

The TP squelch algo rithm for 10 Mbits/s mod e is identical to the

100 Mbits/s mode, except:

• The 10 Mbits/s TP squelch algorithm is not used for link integrity, but to sense

the beginning of a pa cket

• The receiver goes into the unsquelch state if the input voltage exceeds th e

squelch levels for three bit times with altern ating polarity within a 50 to 250 ns

interval

• The receiver goes i nto the squelch state w hen SOI is detected

• Unsquelch detection h as no effect on link integr ity (link pulses are u sed in 10

Mbits/s mode for that p urpose)

• Start of packet is de termined when the receiv er goes into the unsq uelch state

and CRS is asserted

• The receiver meets the s quelch requirements defi ned in IEEE 802.3 Clause 14.

1.2.8.5 EQUALIZER DISABLE

Setting the Equali zer Disable bit (EQLZR) in th e MI serial port Configu ration 1

register disables th e adaptive equaliz er. When disabled, the equalizer is for ced into

the response it would normally have if zer o cable length was detecte d.

1.2.8.6 RECEIVE LEVEL ADJUST

Setting the Receiv e Level Adjust bit (RLV0) in the MI serial po rt Configuration 1

register lowers the receiver squelch and unsquelch level s by 4.5 dB. Setting this bit

may allow the device to support longer cabl e lengths.

1.2.8.7 RECEIVE ACTIVITY INDICATION

Appropriately settin g the programmable LED ou tput select bits in the MI s erial port

LED Configuration 2 re gister programs receiv e activity to appear on so me of the

PLED[5:0]n pins. When one or more of the PLED[5:0]n pins is programmed to be a

receive activity or activity detect output, that pin is asserted LOW for 100 ms every

time a receive p acket occurs. The PLED[ 5:0]n outputs are open- drain with resistor

pullup and can drive a n LE D from V

1.2.14, “LED Drivers,” page 1-36 for more detailed i nformation on the LED output s.

1.2.9 FX Transmitter and Receiver

The FX transmitter and receiver implement the 100BASE-FX function defined in IEEE

802.3. 100BASE-FX is intended for transmission and reception of data over fiber and

is specified to oper ate at 100 Mbits/s. Th us, the FX transmitter and receiver in the

device only operat e when the device is pl aced in 100 Mbits/s m ode.

1.2.9.1 TRANSMITTER

The FX transmitter converts data fr om the 4B5B encoder into binary NRZI data and

outputs the data onto t he FXO+/- pins. The output dri ver is a differential current

source that is abl e to dr ive a 100

drive an external fibe r optic transceiver. The FX transmitter meets all the

requirements defined i n IEEE 802.3.

or can drive another digi tal input. S ee Section

DD

Ω load to ECL lev els. The FX O+/- p ins can direct ly

SMSC DS – LAN83C183 29 Rev. 12/14/2000

Page 30

1.2.9.2 RECEIVER

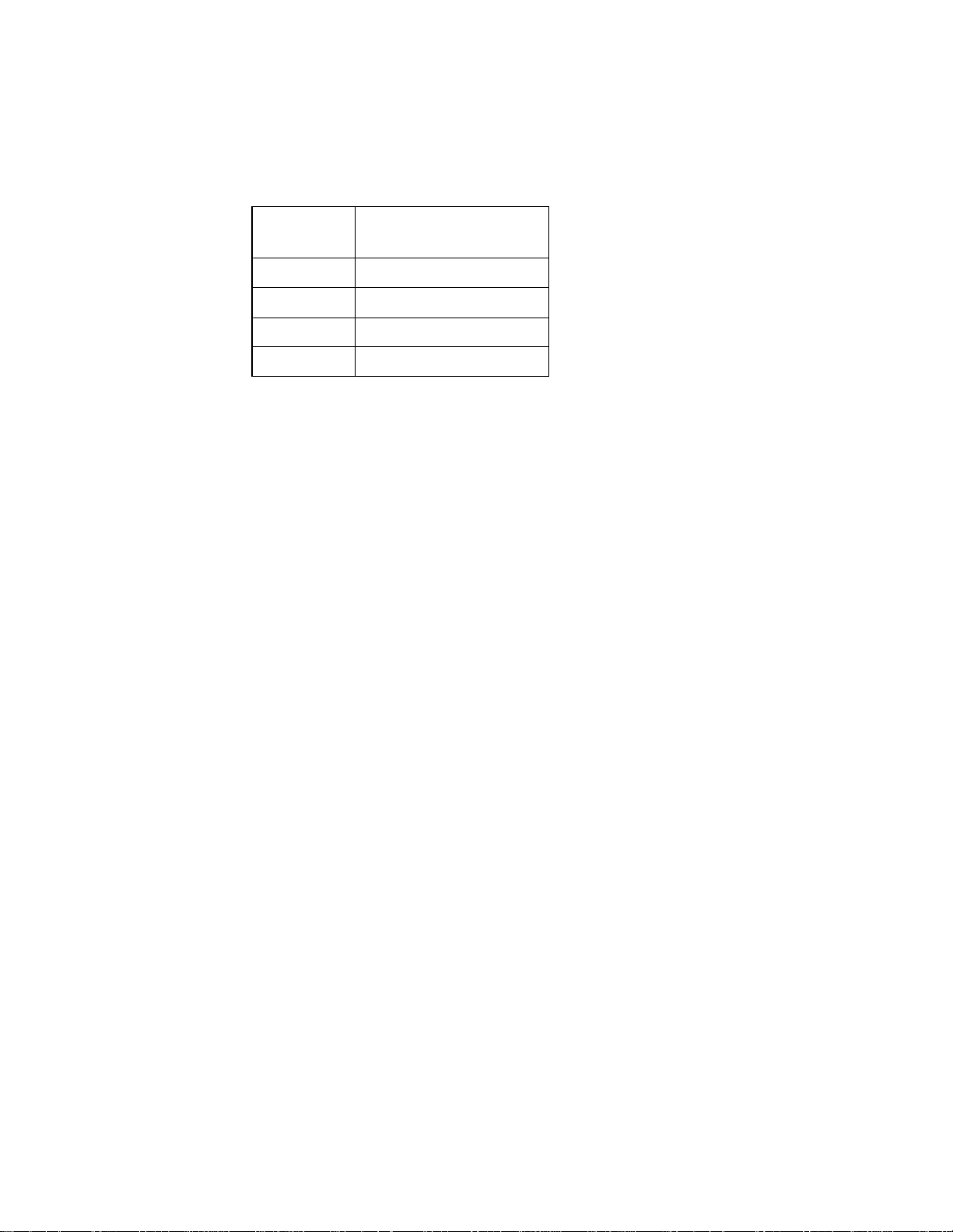

The FX transmit output current level is derived from an internal reference voltage and

the external resistor on the REXT pin. The FX tra nsmit level can be adju sted with

this resistor or it can also be adjusted w ith the two FX Transmit Level Ad just bits

(FXLVL[1:0]) in the MI serial port Mask r egister as shown in Table 1.7.

Table 1.7 FX Transmit Level Adjust

FXLVL[1:0]

Bits Gain

11 1.30

10 1.15

01 0.85

00 1.00

The FX receiver:

• Converts the differential EC L inputs on the FXI+/- pi ns to a digital bit stre am

• Validates the data o n FXI+/- with the SD/FXDIS n input pin

• Enable or disables the FX interface with the SD/F XDISn pin.

The FX receiver meets all requirements defi ned in IEEE 802.3.

The input to the FXI+/- pins can be directly dr iven from a fiber opti c transceiver a nd

first goes to a comparator. The comparator co mpa res the inpu t wav eform agai ns t the

internal ECL threshold levels to produce a low jitter serial bit stream with internal logic

levels. The data fr om the comparator output i s then passed to the cloc k and data

recovery block, pr ovided that the signal detect input, SD/FXDISn, is asserted.

Signal Detect – The FX r eceiver has a signal de tect input pin, SD/FXDISn , which

indicates whether the incoming da ta on FXI+/- is valid or not. Th e SD/FXDISn inpu t

can be driven dire ctly from an external fibe r optic transceiver and me ets all

requirements define d in the IEEE 802.3 specific ations.

The SD/FXDISn input goe s directly to a com parator. The comparator compares the

input waveform agains t the internal ECL threshol d level to produce a digital signal

with internal logi c le ve ls . T h e o utpu t o f the signal det ect c om par ato r the n goes to the

link integrity and squelch blocks. If t he SD/FXDISn input is asserted, the device i s

placed in the Link Pass state and the input data on FXI+/- is determined to be vali d.

If the SD/FXDISn input i s deasserted, t he device is plac ed in the Link F ail state and

the input data on FXI+ /- is determined to be in valid.

The SD_THR pin adjus ts the ECL trip point of the SD/FXDISn input. When the

SD_THR pin is tied to a v oltage between GND and GN D + 0.45V, the trip point of

the SD/FXDISn ECL inp ut buffer i s inter nally s et to V DD

− 1.3 V. When the SD_THR

pin is set to a voltage gr eater than GND + 0.85 V, the trip point of the SD/FXDISn

ECL input buffer is set to the voltage that is applied to the SD_THR pin. The trip level

for the SD/FXDISn input b uffer must be set to VDD

− 1.3 V. Having external control

of the SD/FXDISn buffer t rip level with the SD_TH R pin allows this trip leve l to be

referenced to an exte rnal supply, which facilitates connection to a n external fiber

optic transceiver. If the device is to be connected to a 3.3V e xternal fiber optic

transceiver, SD_THR must be tied to GND.

SMSC DS – LAN83C183 30 Rev. 12/14/2000

Page 31

If the device is to be connected to a 5V external fiber optic transceiver, SD_THR must

be tied to VDD

Refer to the ?Application Note? for more details on connections to external fiber optic

transceivers.

1.2.9.3 FX DISABLE

The FX interface is d isabled if the SD/ FXDISn pin is con nected to GND; otherwi se,

the FX interface is enabled. Disab ling the FX interfac e automatically enables the TP

interface. Converse ly, enabling the TP inte rface disables the FX inter face.

− 1.3V, which can be accomplished with an external resistor divider.

1.2.10 Clock and Data Recovery

This section descr ibes clock and dat a recovery method s implemented in the dev ice

for both the 100 Mbit s/s and 10 Mbits/s modes .

1.2.10.1 100 MBITS/S CLOCK AND DATA RECOVERY

Clock recovery is accomplished with a pha se-locked-loop (PLL) . If valid data is not

present on the receive inputs, the PLL is locked t o the

25-MHz TX_CLK signa l. When the squelch circui t detects valid data on the rece ive

TP input, and if the device i s in the Link Pass s tate, the PLL input is switched to the

incoming data on th e receive input s. The PLL then locks on to th e transitions in the

incoming signal to recover the clock. The recovered data clo ck is then used to

generate the 25 MHz nibble clock, RX_CLK, whic h clocks data into the contr oller

interface section.

The recovered cloc k extracted by the PLL latches in data from th e TP receiver to

perform data recovery. The data is then converted from a single bit stream into nibble

wide data words accor ding to the format shown i n Figure 1.3

1.2.10.2 10 MBITS/S CLOCK AND DATA RECOVERY

The clock recovery proces s for 10 Mbits/s mode is iden tical to the 100 Mbits /s mode

except:

• The recovered cl ock frequency is a 2. 5 MHz nibble clock

• The PLL is switche d from TX_CLK to the TP inp ut when the squelch indic ates

valid data

• The PLL takes up to 12 transitions (bit times) to lock onto the preamble, so some

of the preamble data symbols are lost. Howev er, the clock recovery block

recovers enough p reamble symbols to pass at least six nibbles of pr eamble to

the receive contro ller interface as sho wn in Figure 1.3.

The data recovery pr ocess for 10 Mbits/s mod e is identical to that of th e

100 Mbits/s mode. As mentioned in the Manche ster Decoder section, the d ata

recovery process inherently performs decoding of Manchester encoded data from the

TP inputs.

1.2.11 Link Integrity and AutoNegotiation

The device can be con figured to implement ei ther the standard link int egrity

algorithms or the AutoN egotiation algorithm.

The standard link integrity algori thms are used so lely to establish a link to and from

a remote device. The A utoNegotiation algorit hm is used to establish a l ink to and

from a remote device and automatically conf igure the device for 10 or 100 Mbits/s

and Half or Full Duplex oper ation. The different standard l ink integrity algo rithms for

10 and 100 Mbits/s m odes are described in fo llowing subsections.

SMSC DS – LAN83C183 31 Rev. 12/14/2000

Page 32

The AutoNegotiation algorithm in the device meets all requirements specified in IEEE

802.3.

AutoNegotiation is onl y specified for 100BA SE-TX and 10BASE-T operation, and

must be disabled when the device is placed in

100BASE-FX mode .

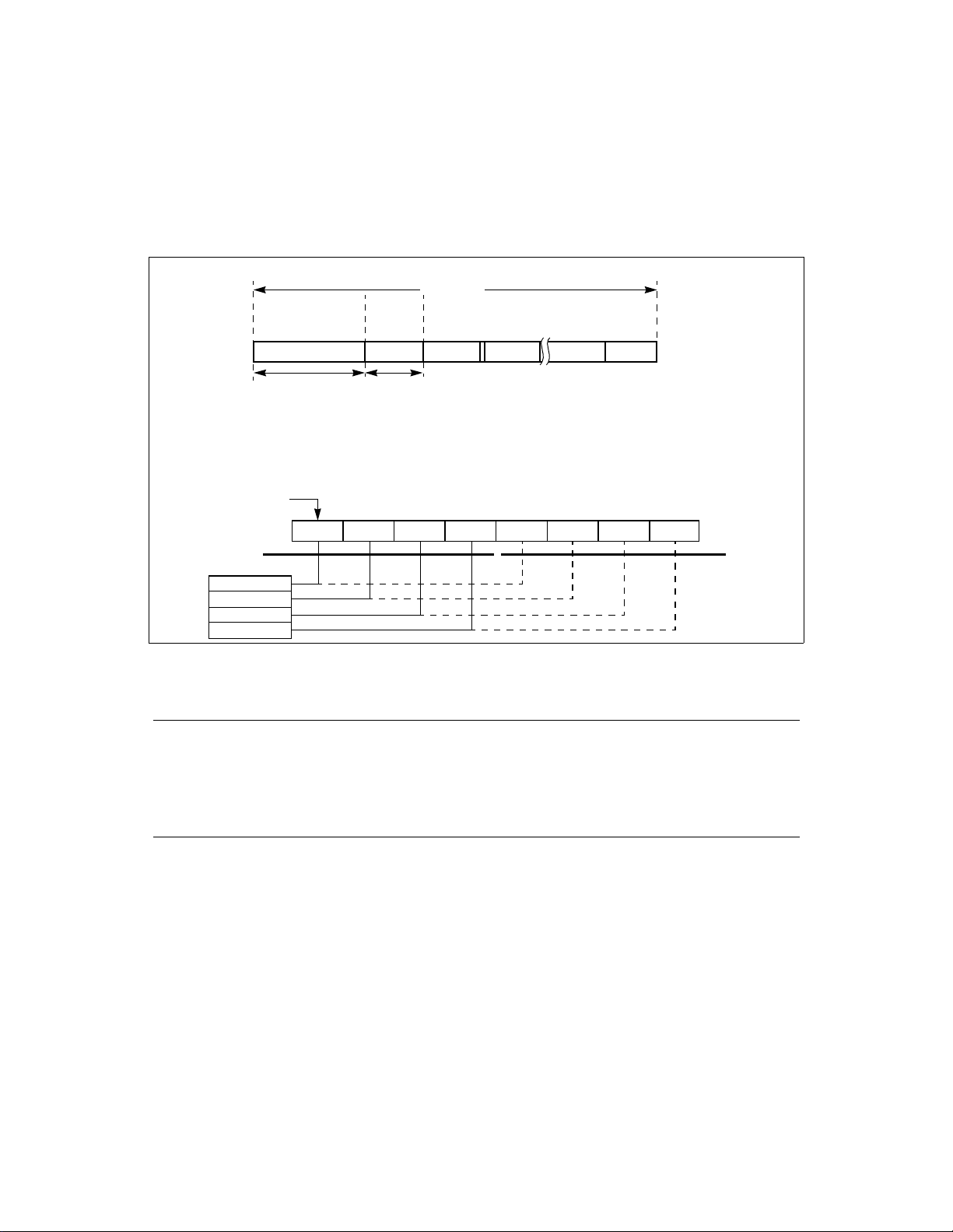

1.2.11.1 10BASE-T LINK INTEGRITY ALGORITHM (10 MBITS/S)

The device imple ments the same 10BASE-T link integrity algo rithm defined in IEEE

802.3. This algorithm u ses normal link pulses (NLPs), which are transmi tted during

idle periods, to determine if a device has successfully established a link with a remote

device (called Link Pass state). The tra nsmit link pulse meet s the template

requirements define d in IEEE 802.3 and shown i n Figure 1.6. Refer to IEEE 802.3

for more details if need ed.

Figure 1.6 Link Pulse Output Voltage Template (10 Mbits/s)

0.6 BT

1.3 BT

2.0 BT

200 mV

2.0 BT0.85 BT

+ 50 mV

− 50 mV

3.1 V

585 mV

0 BT

0.5 V/ns

0.5 BT

0.25 BT

− 3.1 V

1.2.11.2 100BASE-TX LINK INTEGRITY ALGORITHM (100 MBITS/S)

Because the IEEE 802.3 specification defines 100BASE-TX to have an active idle signal, there is no need to have separate link pulses such as those defined for 10BASET. The LAN83C183 uses the squelch criteria and descrambler synchronization algorithm on the input data to determine if the device has successfully established a link

with a remote device (called Link Pass state). Refer to IEEE 802.3 for more details if

needed.

300 mV

4.0 BT

4.0 BT

+ 50 mV

− 50 mV

42.0 BT

1.2.11.3 AUTONEGOTIATION ALGORITHM

As stated previously, the AutoNegotiation alg orithm is used for two pur poses:

• To establi sh a link to and from a remo te device

• To automa tically configu re the device for ei ther 10 or 100 Mbi ts/s operation and

either Half- or Full-Du plex operation.

The AutoNegotiation algori thm is the same algorithm defined in IE EE 802.3 Clause

28. AutoNegotiation uses a burst of link pulses, called fast link pulses (FLPs), to pass

up to 16 bits of signaling data back and for th between the LAN83 C183 and a remo te

device. The trans mit FLP pulses meet the template specified in IEEE 802.3 and

SMSC DS – LAN83C183 32 Rev. 12/14/2000

Page 33

shown in Figure 1.6. A timi ng diagram contras ting NLPs and FLPs is sh own in

Figure 1.7.

Figure 1.7 NLP vs FLP Link Pulse

Normal Link Pulse (NLP)

TPO±

Fast Link Pulse (FLP)

TPO±

D0 D1 D2 D3 D14 D15

Clock Clock Clock Clock Clock Clock Clock

Data Data Data Data Data Data

Any of the followin g events initiates the Au toNegotiation algorithm:

• Power up

• Device reset

• The AutoNegotiation E nable (ANE G_EN) b it in the M I se rial po rt Contro l regis ter

for that port is cleare d, then set

• The AutoNegotiation Reset (ANEG_ RST) bit in the MI serial port Control register

is set

• The channel enters the Link Fail state

Once a negotiation has been initiated, the device first determines if the remote device

has AutoNegotiation capability. If the remote device is not AutoNeg otiation capable

and is just transmitting eit her 10BASE-T or 100 BASE-TX signa ls, the device se nses

it and places itself in the same mode as the remote device.

If the device detects FLPs from the remote device , the remote device is dete rmined

to have AutoNegotiatio n capability, and the device then uses the contents of the MI

serial port Aut oNegotiation Advertisem ent register for that port t o advertise its

capabilities to t he remote device.

The remote device does the same, and the capabil ities read back from the r emote

device are stored in the MI serial port AutoNegoti ation Remote End Capabil ity

register. The LAN83C183 negotiatio n algorithm then matches its capabilities to the

remote device’s capabilities and determines the device configuration according to the

priority resolutio n algorithm defined in IEE E 802.3 Clause 28.

When the negotiation process is complete d, the LAN83C183 then conf igures itself

for either 10 or 100 M bits/s mode and either Full- or Half- Duplex mod es (depend ing

on the outcome of the n egotiation process), and it switches to either the 100BASETX or 10BASE-T link i ntegrity algorithms (depend ing on which mode was en abled

through AutoNegotiatio n). Refer to IEEE 802.3 Cla use 28 for more details.

1.2.11.4 AUTONEGOTIATION OUTCOME INDICATION

The outcome or result of the AutoNegotiation process is stored in the 10/100 Speed

Detect (SPD_DET) an d Duplex Detect (DPL X_DET) bits in th e MI serial port St atus

Output register.

SMSC DS – LAN83C183 33 Rev. 12/14/2000

Page 34

1.2.11.5 AUTONEGOTIATION STATUS

To monitor the status of the AutoNegotiation process, simply read the AutoNegotiation

Acknowledgement (ANEG_ACK) bit in the MI serial port Status register. The

ANEG_ACK bit is 1 when an AutoNegotiation has been initiated and successfully

completed.

1.2.11.6 AUTONEGOTIATION ENABLE

To enable the AutoNegotiation algorith m, set the AutoNegotiatio n Enable bit

(ANEG_EN) in the M I seria l por t Contr ol regis ter, or assert the AN EG pin. To disable

the AutoNegotiation alg orithm, clear the ANEG_EN bi t, or deassert the ANEG pin .

When the AutoNegotia tion algorithm is enabl ed, the device halts all transmissions

including link pulse s for 1 200 to 15 00 m s, ente rs the Li nk Fail State, a nd resta rts th e

negotiation process. When the AutoNegotiation algorithm is disabled, the selection of

100 Mbits/s or

10 Mbits/s mode is de termined with the SPE ED bit in the MI serial por t Control

register, and the selection of Half- or Full-Duple x mode determin ed from the state of

the DPLX bit in the MI se rial port Control register.

1.2.11.7 AUTONEGOTIATION RESET

Appropriately setting the Au toNeg oti ati on Reset (A NE G_RST ) bit in the MI serial port

Control register can initiate or reset the Aut oNegotiation algorithm at a ny time.

1.2.12 Link Indication

Receive link detect ac tivity can be monitored thr ough the Link Detect bit (LINK ) in

the MI serial port Status register and the Link Fail Detect bit (LNK_FAIL) in the Status

Output register. Link detect activity can also be programmed to a ppear on the

PLED3n or PLED0n pins. To do this, appropriately set the Programmable LED Output

Select bits in the MI serial port Conf iguratio n 2 register as show n in Table 1.9. When

either the PLED3n or PLED0n pins are programmed to be a link de tect output, they

are asserted LOW when ever the device is in the L ink Pass State.

The PLED3 output is a n open-drain pin with pullu p resistor and can drive an LED

from V

addition to a weak pull up resistor, so it can drive an LED from eith er V

Both the PLED3n and PLED0n outputs can also drive anoth er digital input. Refer to

Section 1.2.14, “LED Drivers,” pa ge 1-36 for a de scription on how to program th e

PLED[3:0]n pins and their default values.

. The PLED0 output has both pullup and pulld own driver transistors in

DD

DD

or GND.

SMSC DS – LAN83C183 34 Rev. 12/14/2000

Page 35

1.2.13 Collision

Collisions occur whenev er transmit and receiv e operations occur simu ltaneously

while the device is in Half-Duplex mode.

1.2.13.1 100 MBITS/S

In 100 Mbits/s oper ation, a collision occurs and is sensed whenever there is

simultaneous transmi ssion (packet transmis sion on TPO+/-) and reception (non- idle