SLS SL70D0948 Datasheet

SLS System Logic Semiconductor SL70D0948

48 OUTPUT LED DRIVER / 9 BIT PWM CONTROLLER

SL70D0948

System Logic Semiconductor

SLS System Logic Semiconductor SL70D0948

CONTENTS

INTRODUCTION

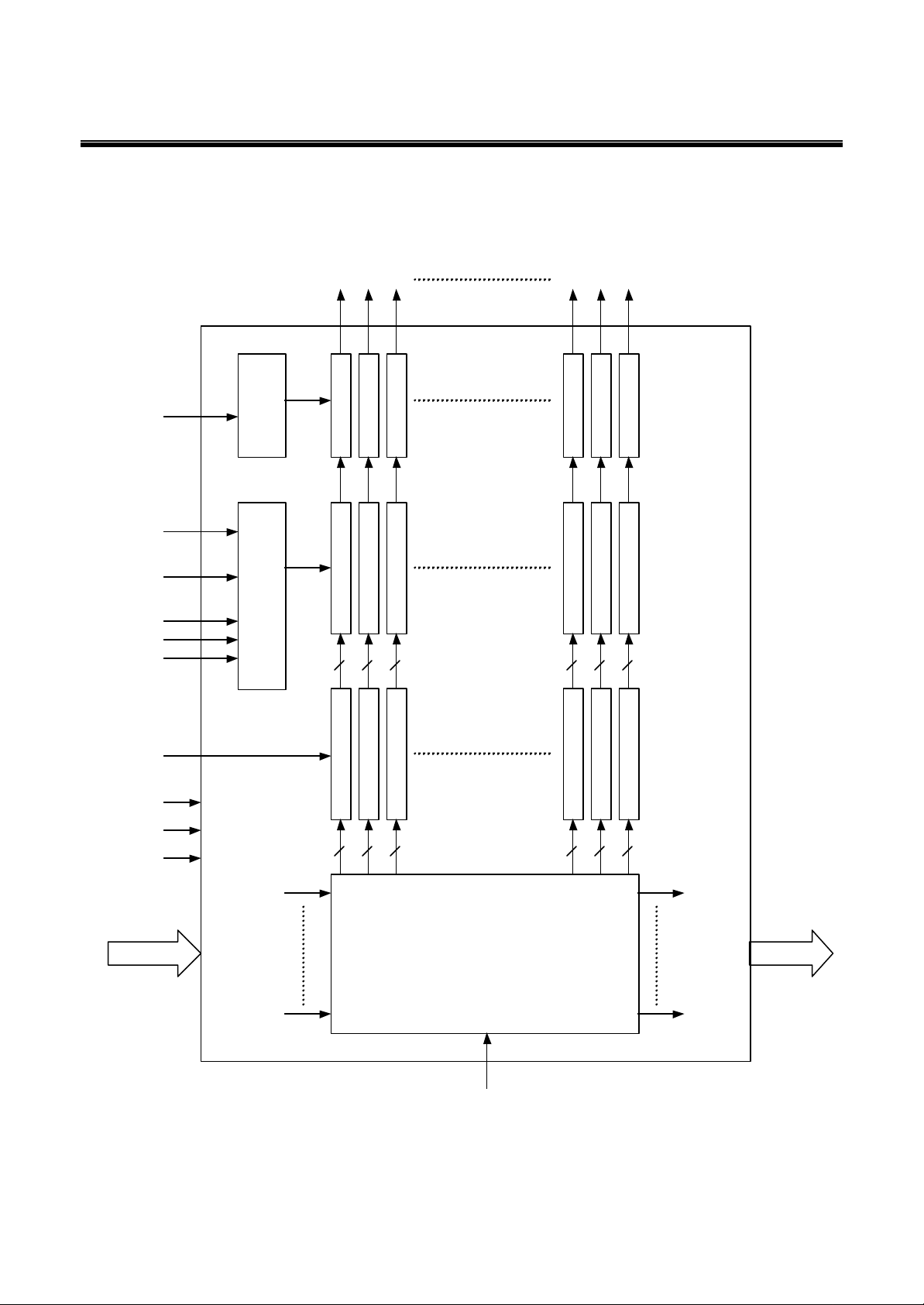

BLOCK DIAGRAM

PIN ASSIGNMENT

PIN DESCRIPTION

FUNCTION DESCRIPTION

SPECIFICAIONS

REFERENCE APPLICATIONS

SLS System Logic Semiconductor SL70D0948

INTRODUCTION

The SL70D0948 is LED driver / controller IC for LED display panel. This is consisted of 48 channel

LED driver , 9Bit PWM controller and 48 bit shift register. Also it is very convenient to application

because all display data can transfer by serial method.

FEATURES

Driver Output Circuits

- 48 LED Driver Outputs : N-ch Open Drain MOS Transistor Output

- LED Driving Voltage : Max. 16V (When Transistor Off)

- LED Driving Current : Max. 90mA

- LED Driving Current Control

- Outputs are 9bit PWM controlled

Data Interface

- 48bit Shift Register for 9bit data input

- 9bit parallel data format selectable

PWM controller

- 9bit PWM control ( 512 Gray scale )

- 3bit Brightness / 4bit Brightness input selectable

Package Type

- 100 pin MQFP

SLS System Logic Semiconductor SL70D0948

BLOCK DIAGRAM

OE

PWCLK

BRMODE

BRD2

BRD1

BRD0

Control

Driver Output

9 bit PWM Counter

9 9 9 9 9 9

LED1

LED2

LED3

LED Driver (1)

LED Driver (2)

LED Driver (3)

PWM Generator (1)

PWM Generator (2)

PWM Generator (3)

LED47

LED46

LED Driver (46)

PWM Generator (46)

LED48

LED Driver (47)

LED Driver (48)

PWM Generator (47)

PWM Generator (48)

STROBE

CE2

/CE1

/RESET

DIN8

DIN0

9bit Data Register (1)

9bit Data Register (2)

9bit Data Register (3)

9

9 9 9 9 9

48bit x9bit Shift RegisterDIN 9bit DOUT 9bit

SHCLK

9bit Data Register (46)

9bit Data Register (47)

9bit Data Register (48)

DOUT8

DOUT0

SLS System Logic Semiconductor SL70D0948

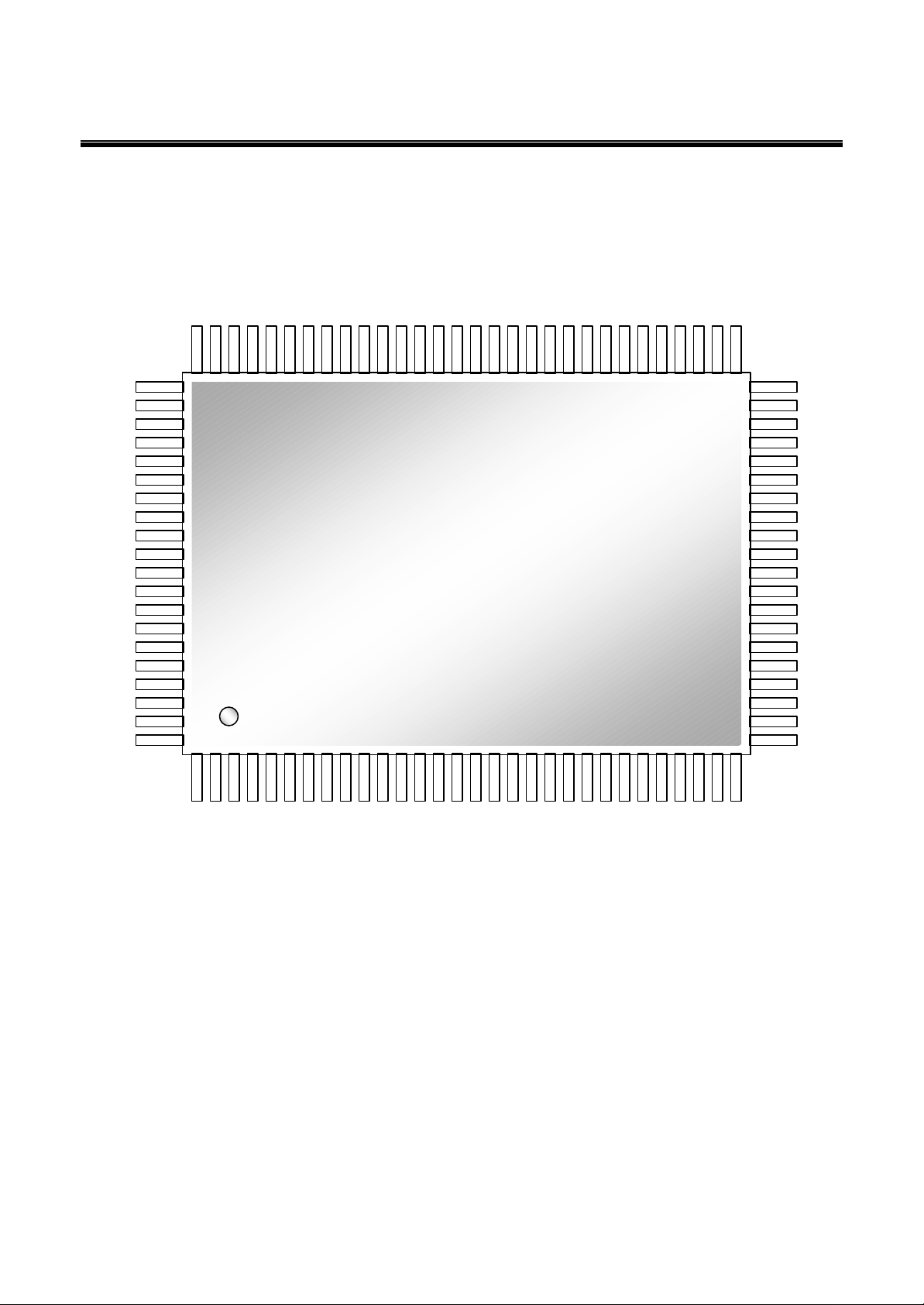

PIN ASSIGNMENT(MQFP)

5180

VDD

81

100

STROBE

SHCLK

/RESET

GND

LED31

LED32

LED33

LED34

LED35

LED36

GND

LED37

LED38

LED39

LED40

LED41

LED42

GND

VDD

DIN8

/CE1

CE2

OEB

GND

PWCLK

BRMODE

GND

LED30

LED29

LED28

LED27

LED26

LED25

GND

LED24

LED23

LED22

SL70D0948

System Logic

Semiconductor

LED21

LED20

LED19

GND

BRD0

BRD1

BRD2

GND

VDD

VDD

VDD

GND

NC

VDD

GND

LED18

LED17

LED16

LED15

LED14

LED13

GND

LED12

LED11

LED10

LED9

LED8

LED7

GND

GND

DOUT8

DOUT7

50

31

DIN7

DIN6

DIN5

DIN4

DIN3

DIN2

DIN1

DIN0

GND

LED43

LED44

LED45

LED46

1

LED47

LED48

GND

LED1

LED2

LED3

LED4

LED5

LED6

GND

DOUT0

DOUT1

DOUT2

DOUT3

DOUT4

DOUT5

DOUT6

30

SLS System Logic Semiconductor SL70D0948

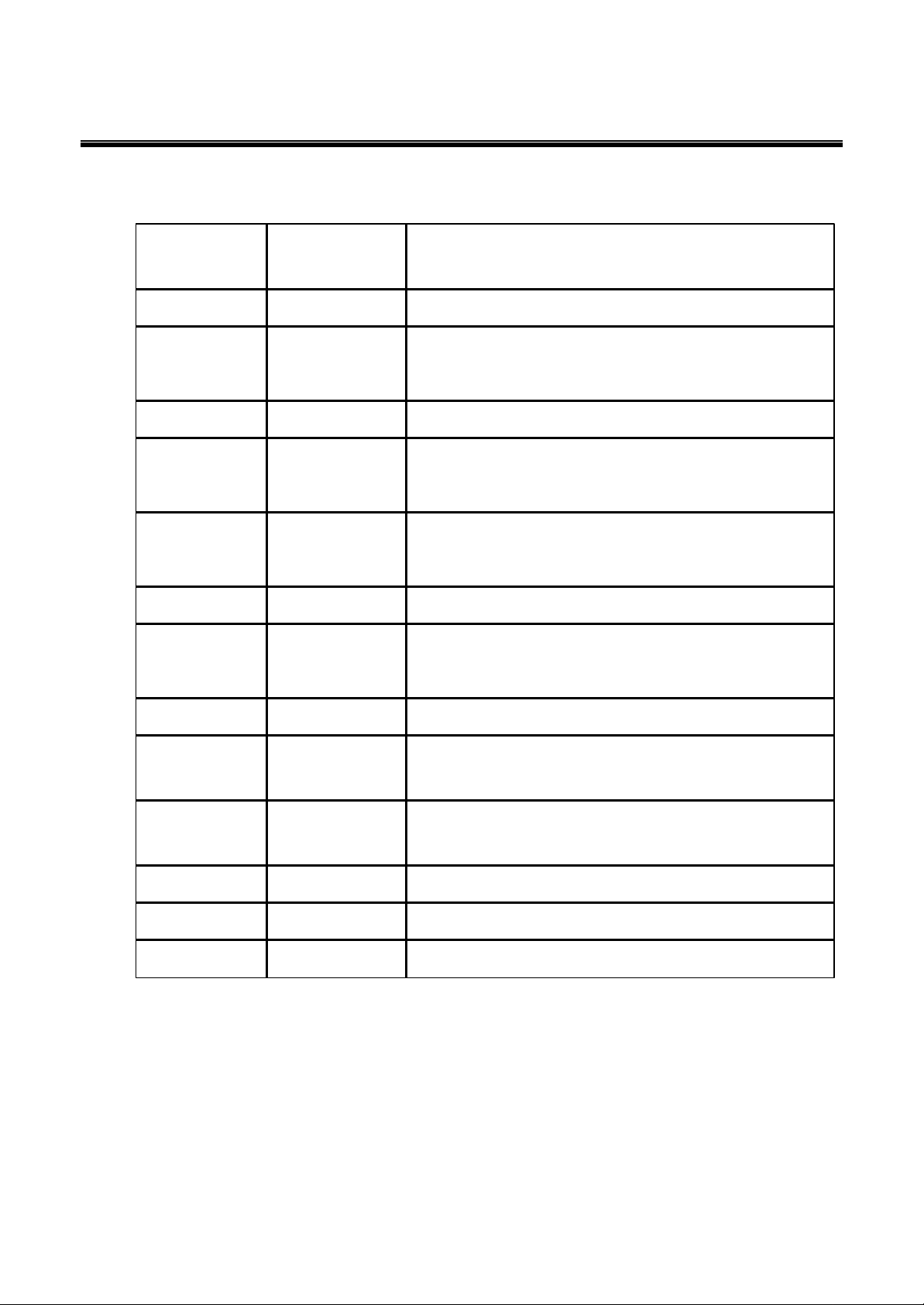

PIN DESCRIPTION

PIN No.

(MQFP)

49,52,53,54,78,99

9, 16, 23, 33,

34, 41, 48,

59, 65, 72,74

84, 91, 98

83

100, 1, 2,

3, 4, 5,

6, 7, 8

32, 31, 30,

29, 28, 27,

26, 25, 24

82

81

PIN NAME FUNCTION

VDD 5 V Power supply terminal.

GND terminals for LED Drivers and control logic.

GND

/RESET Reset input terminal (Low active).

DIN8 ~ DIN0

DOUT8 ~ DOUT0

SHCLK Shift register clock input terminal.

STROBE

All GND terminals must be connected to GND level.

Do not left any GND terminal to NC.

Data input terminals for 9bit R, G, B data.

Shift register accepts R, G, B data from these terminals.

(at rising edge of SHCLK)

Output terminals of shift register output data for next

DIN8 ~ DIN0 terminals.

Strobe signal input terminal. At rising edge of strobe signal,

48 channels of 9 bit data registers copy R, G, B data from

shift register.

80

79

76

77

75

56, 57, 58

/CE1 Chip enable signal input terminal (Low active).

Chip enable signal input terminal (High active).

CE2

OEB

PWCLK PWM generator reference clock input terminal.

BRMODE Brightness control mode input terminal.

BRD2 ~ BRD0 Brightness control data input terminal.

The device accepts SHCLK and STROBE when /CE1 = “L ”

and CE2 = “H ”.

Output enable signal input terminal.

The device outputs data when OEB = “L ”. When OEB = “H ”

all R, G, B output terminals hold high-impedance state.

Loading...

Loading...