8K

一次性编程/掩膜, 液晶驱动及10位

特性

基于 SH6610D, 液晶驱动及 10 位 ADC 型 4 位单片机

OTP ROM: 8K X 16 位(SH69P55A)

MASK ROM: 8K X 16 位 (SH69K55A)

RAM: 515 X 4 位

- 99 个系统控制寄存器

- 376 个数据存储器

- 40 个 LCD 数据存储器

工作电压:

- f

OSC = 30kHz - 4MHz, VDD = 2.4V - 5.5V

OSC = 30kHz - 8MHz, VDD = 4.5V - 5.5V

- f

42 个双向 I/O 端口

PORTA - PORTK 内建上拉电阻

8 层堆栈 (包括中断)

两个 8 位和一个 16 位自动重载定时/计数器

LCD 驱动器:

- 16 SEG X 8 COM (1/8 占空比, 1/4 偏置)

- 18 SEG X 6 COM (1/6 占空比, 1/3 偏置)

- 20 SEG X 4 COM (1/4 占空比, 1/3 偏置)

LED 驱动器:

- 8 SEG X 6 COM (1/6 占空比)

- 8 SEG X 5 COM (1/5 占空比)

- 8 SEG X 4 COM (1/4 占空比)

中断源:

- 定时器 0 中断

- 定时器 1 中断

- 定时器 2 中断

- 外部中断 (PORTB & PORTC 下降沿中断, 模/数中断,

键扫描中断)

SH69P55A/K55A

ADC

振荡器 (代码选项)

- 晶体谐振器: 32.768kHz, 400kHz - 8MHz

- 陶瓷谐振器: 400kHz - 8MHz

- 外部 RC 振荡器: 400kHz - 8MHz

- 内建 RC 振荡器: 4MHz ±5%

内建 PLL 振荡器 (1, 2, 4, 8MHz)

指令周期时间 (4/f

10 通道 10 位模/数转换器 (ADC)

内建 2 通道可编程音频发生器

内建自动键盘扫描器

交流电过零检测功能

ROM 查表功能

1 个通道 8+2 位 PWM 输出

复位

- 内建看门狗定时器 (WDT) (代码选项)

- 内建上电复位 (POR)

- 内建低电压复位 (LVR) (代码选项)

两种低功耗工作模式: HALT 和 STOP

内建低电压复位功能, 两种监测电平 (代码选项)

预热计数器

OTP 类型/代码保护 (SH69P55A)

MASK 类型 (SH69K55A)

28 引脚 SOP 封装; 32 引脚 DIP 封装; 44 引脚 QFP 封装

OSC)

型4位单片机

概述

SH69P55A/69K55A 是一种先进的 CMOS 4 位单片机。该器件集成了 SH6610D CPU 内核, RAM, ROM, 定时器, LCD/LED 驱

动器, I/O 端口, 看门狗定时器, 10 通道 10 位 ADC, 低电压复位, 自动键盘扫描器, PLL 高频时钟, 交流电过零检测功能。

SH69P55A/69K55A 适应于洗衣机, 微波炉等的应用。

1 V2.1

SH69P55A/K55A

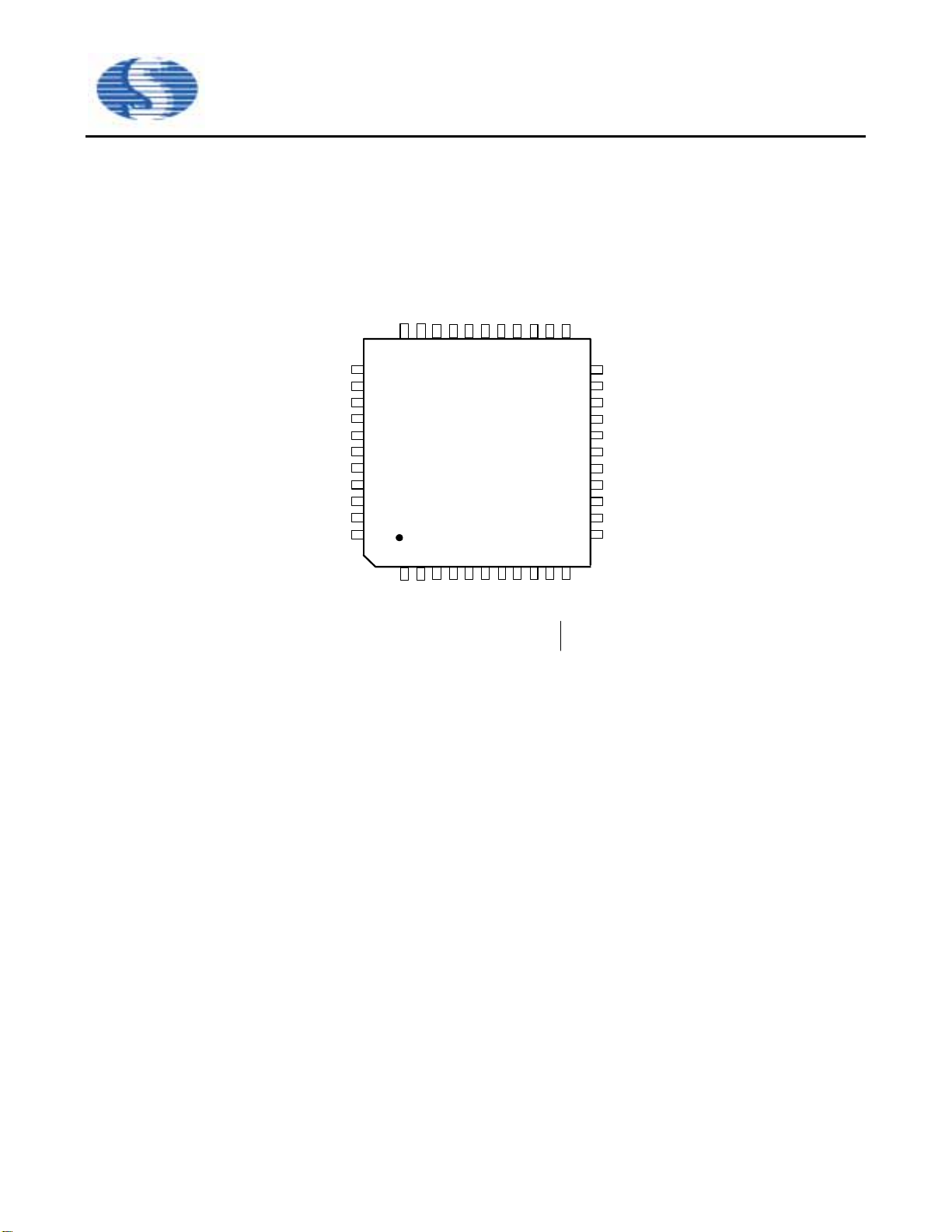

引脚配置 (44 引脚)

PORTD.0/COM4/LED_C4/KEY_04

PORTD.1/COM3/LED_C3/KEY_03

PORTD.2/COM2/LED_C2/KEY_02

PORTD.3/COM1/LED_C1/KEY_01

PORTB.0/AN0

PORTB.1/AN1

PORTB.2/AN2

PORTB.3/AN3

PORTG.0/PWM

PORTG.1/TONE/AN9

PORTG.2/V

REF/T0

PORTE.3/COM5/LED_C5/SEG20

PORTE.2/COM6/LED_C6/SEG19

PORTE.1/COM7/SEG18

PORTE.0/COM8/SEG17

PORTH.3/SEG16

PORTH.2/SEG15

PORTH.1/SEG14

33

34

35

36

37

SH69P55A/69K55A

38

39

40

41

42

43

44

1234567891011

PORTG.3/T2/AN8

PORTK.0

/44 Pin

PORTK.1

PORTJ.0/AN4

PORTJ.1/AN5

PORTJ.2/AN6

PORTJ.3/AN7

PORTH.0/SEG13

PORTC.0/PLL_C

PORTI.1/SEG10

PORTI.3/SEG12

PORTI.2/SEG11

25 24 2332 3 1 30 29 28 27 26

22

PORTI.0/SEG9

21

PORTF.3/SEG8/LED_S8

PORTF.2/SEG7/LED_S7

20

19

PORTF.1/SEG6/LED_S6

18

PORTF.0/SEG5/LED_S5/KEY_I5

17

PORTA.3/SEG4/LED_S4/KEY_I4

16

PORTA.2/SEG3/LED_S3/KEY_I3

15

PORTA.1/SEG2/LED_S2/KEY_I2

14

PORTA.0/SEG1/LED_S1/KEY_I1

13

V

DD

12

GND

OSCI/PORTC.2

OSCO/PORTC.1

RESET/PORTC.3

2

SH69P55A/K55A

引脚配置 (32 引脚 & 28 引脚)

PORTB.0/AN0

PORTB.1/AN1

PORTB.2/AN2

PORTB.3/AN3

PORTG.0/PWM

PORTG.1/TONE/AN9

PORTG.2/V

PORTG.3/T2 /AN8

PORTC.0/PLL_C

OSCO/PORTC.1

OSCI/PORTC.2

RESET/PORTC.3

PORTA.0/SEG1/LED_S1/KEY_I1

PORTA.1/SEG2/LED_S2/KEY_I2

PORTB.3/AN3

PORTG.0/PWM

PORTG.1/TONE/AN9

PORTG.2/V

PORTG.3/T2/AN8

PORTJ.0/AN4

PORTJ.1/AN5

PORTJ.2/AN6

PORTJ.3/AN7

PORTC.0/PLL_C

OSCO/PORTC.1

OSCI/P ORTC .2

RESET/PORTC.3

REF/T0

GND

VDD

REF/T0

GND

1

2

3

4

5

6

7

8

9

10

11

12

13

14

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

SH69P55A/69K55A

/32Pin

SH69P55A/69K55A

/28Pin

PORTD.3/COM1/LED_C1/KEY_O1

32

PORTD.2/COM2/LED_C2/KEY_O2

31

PORTD.1/COM3/LED_C3/KEY_O3

30

PORTD.0/COM4/LED_C4/KEY_O4

29

PORTE.3/COM5/SEG20/LED_C5

28

PORTE.2/COM6/SEG19/LED_C6

27

PORTE.1/COM7/SEG18

26

PORTE.0/COM8/SEG17

25

PORTH.3/SEG16

24

PORTH.2/SEG15

23

PORTF.3/SEG8/LED_S8

22

PORTF.2/SEG7/LED_S7

21

PORTF.1/SEG6/LED_S6

20

PORTF.0/SEG5/KEY_I5/LED_S5

19

PORTA.3/SEG4/KEY_I4/LED_S4

18

PORTA.2/SEG3/KEY_I3/LED_S3

17

28

27

26

25

24

23

22

21

20

19

18

17

16

15

PORTB.2/AN2

PORTB.1/AN1

PORTB.0/AN0

PORTE.3/COM5/LED_C5

PORTE.2/COM6/LED_C6

PORTE.1/COM7

PORTE.0/COM8

PORTI.1/SEG10

PORTI.0/SEG9

PORTA.3/SEG4/LED_S4

PORTA.2/SEG3/LED_S3

PORTA.1/SEG2/LED_S2

PORTA.0/SEG1/LED_S1

V

DD

3

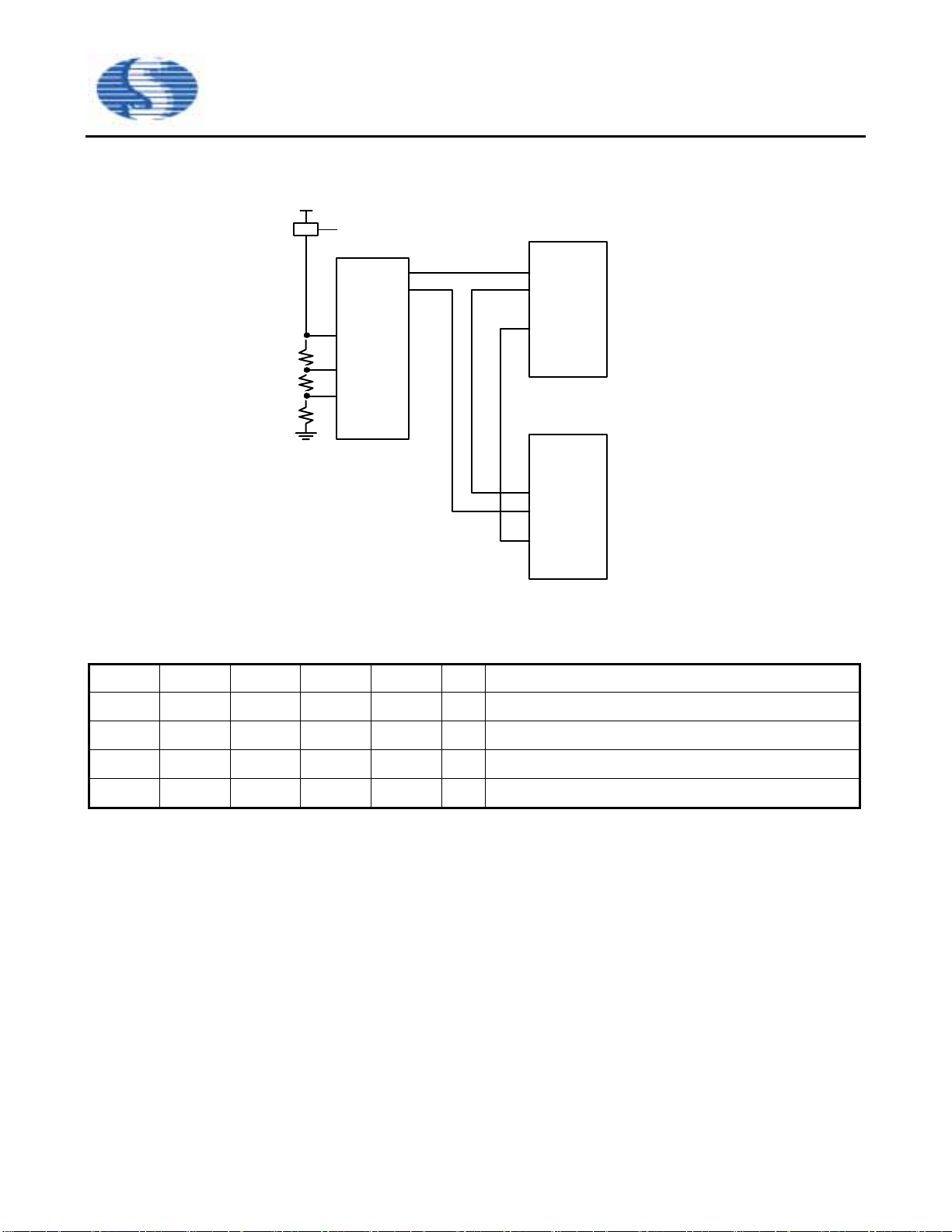

方框图

SH69P55A/K55A

RESET/PORTC.3

Reset Circuit

PORTC.3

RAM

96 X 4 Bits

System Register

RAM

416 X 4 Bits

Data Memory

ROM

8196 X 16 Bits

CPU

WDT RC

Watch Dog

Timer

8ch X 10bits

ADC

1 X ( 8+2) Bits

PWM

Tone generator 1

Tone generator 2

Oscillator

PORTC.2 - 0

PORTA (4-bit)

PORTD (4-bit)

PORTB (4-bit)

PORTE (4-bit)

OSCI/PORTC.2

OSCO/PORTC.1

PORTC.0/PLL_C

PORTA.3 - 0/SEG4 - SEG1/

LED_S4 - LED_S1/

KEY_I4 - KEY_I1

PORTD.3 - 0/COM1 - COM4/

LED_C1 - LED_C4/

KEY_O1 - KEY_O4

PORTB.3 - 0/AN3 - AN0

PORTE.3 - 0/COM5 - COM8/

LED_C5 - LED_C6/

SEG20 - SEG17

V

GND

PORTJ.3 - 0/AN7 - AN4

PORTK.1 - 0

TIMER2

(16 Bits)

PORTF (4-bit)

DD

Power Circuit

PORTJ (4-bit)

PORTK (2-bit)

TIMER1

(8 Bits)

TIMER 0

(8 Bits)

PORTH (4-bit)

PORTG (4-bit)

PORTI (4-bit)

PORTF.3 - 0/SEG8 - SEG5/

LED_S8 - LED_S5/KEY_I5

PORTH.3 - 0/SEG16 - SEG13

PORTG.3 - 0/T2, T0, VREF/

TONE/PWM

PORTI.3 - 0/SEG12 - SEG9

4

SH69P55A/K55A

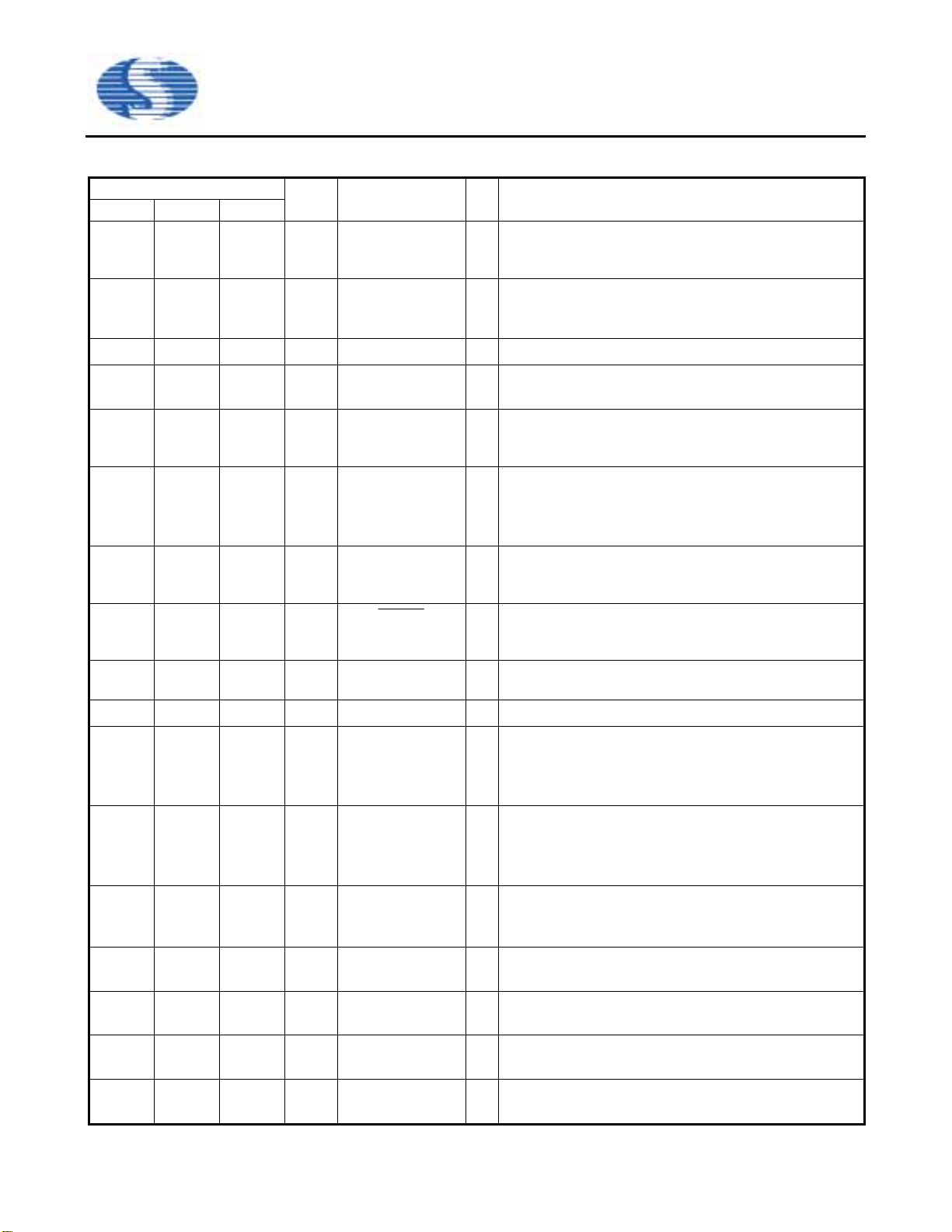

引脚描述

44 引脚 28 引脚 32 引脚

引脚编号

焊垫

编号

44 4 7 1

1 5 8 2

引脚命名

PORTG.2

/T0

REF

/V

PORTG.3

/T2

/AN8

引脚

性质

可编程 I/O

I/O

I

Timer0 定时器/计数器外部信号输入引脚 (施密特触发输入)

I

ADC 外部参考电压输入

可编程 I/O

I/O

I

Timer2 定时器/计数器外部信号输入引脚 (施密特触发输入)

I

ADC 输入通道 8

3 - 2 - - 4 - 3 PORTK.1 - 0 I/O 可编程 I/O

7 - 4 9 - 6 - 8 - 5

8 10 9 10

9 11 10 11

10 12 11 12

11 13 12 13

12 14 13

9,14,35,

36,43

PORTJ.3 - 0

/AN7 - AN4

PORTC.0

/PLL_C

PORTC.1

/OSCO

PORTC.2

/OSCI

RESET

/PORTC.3

GND P 接地引脚

可编程 I/O

I/O

I

ADC 输入通道 7 - 4

可编程 I/O

I/O

外部中断输入 (下降沿)

I

P

连接 PLL 外接阻容网络

I/O

可编程 I/O (代码选项)

I

外部中断输入 (下降沿)

I/O

时钟输出引脚, 连接到晶振, 陶瓷谐振器。使用 RC

振荡时, 无时钟信号输出

可编程 I/O (代码选项)

I/O

外部中断输入 (下降沿)

I

I

时钟输入引脚, 连接到晶振, 陶瓷谐振器或外部电阻

复位引脚 (低电压有效, 施密特触发输入)

I

I

外部中断输入 (下降沿)

I/O

可编程 I/O

13 15 14 15,16 VDD P电源引脚

可编程 I/O

I/O

LCD 显示的 SEG4 - SEG1 信号输出

O

O

LED 显示的 SEG4 - SEG1 信号输出

I

自动键盘扫描输入

可编程 I/O

I/O

LCD 显示的 SEG5 信号输出

O

O

LED 显示的 SEG5 信号输出

I

自动键盘扫描输入

可编程 I/O

I/O

O

LCD 显示的 SEG8 - SEG6 信号输出

O

LED 显示的 SEG8 - SEG6 信号输出

可编程 I/O

I/O

O

LCD 显示的 SEG10 - SEG9 信号输出

可编程 I/O

I/O

O

LCD 显示的 SEG12 - SEG11 信号输出

可编程 I/O

I/O

O

LCD 显示的 SEG14 - SEG13 信号输出

可编程 I/O

I/O

O

LCD 显示的 SEG16 - SEG15 信号输出

17 - 14 19 - 16 18 - 15 20 - 17

18 - 19 21

21 - 19 - 22 - 20 24 - 22

23 - 22 21 - 20 - 26- 25

25 - 24 - - 28 - 27

27 - 26 - - 30 - 29

29 - 28 - 24 - 23 32 - 31

PORTA.3 - 0

/SEG4 - SEG1

/LED_S4 - LED_S1

/KEY_I4 - KEY_I1

PORTF.0

/SEG5

/LED_S5

/KEY_I5

PORTF.3 - 1

/SEG8 - SEG6

/LED_S8 - LED_S6

PORTI.1 - 0

/SEG10 - SEG9

PORTI.3 - 2

/SEG12 - SEG11

PORTH.1 - 0

/SEG14 - SEG13

PORTH.3 - 2

/SEG16 - SEG15

说明

5

SH69P55A/K55A

引脚描述 (续前表

引脚编号

44 引脚 32 引脚 28 引脚

)

焊垫

编号

31 - 30 23 - 22 26 - 25 34 - 33

33 - 32 25 - 24 28 - 27 38 - 37

37 - 34 - 32 - 29 42 - 39

40 - 38 28 - 26 3 - 1 46 - 44

41 1 4 47

42 2 5 48

43 3 6 49

其中, I: 输入; O: 输出; P: 电源; Z: 高阻

引脚命名

PORTE.1 - 0

/COM7 - COM8

/SEG18 - SEG17

PORTE.3 - 2

/COM5 - COM6

/SEG20 - SEG19

/LED_C5 - LED_C6

PORTD.3 - 0

/COM1 - COM4

/LED_C1 - LED_C4

/KEY_O1 -

KEY O4

PORTB.2 - 0

/AN2 - AN0

PORTB.3

/AN3

PORTG.0

/PWM

PORTG.1

/TONE

/AN9

引脚

性质

可编程 I/O

I/O

O

LCD 显示的 COM7 - COM8 信号输出

O

LCD 显示的 SEG18 - SEG17 信号输出

可编程 I/O

I/O

LCD 显示的 COM5 - COM6 信号输出

O

O

LCD 显示的 SEG20 - SEG19 信号输出

O

LED 显示的 COM5 - COM6 信号输出

可编程 I/O

I/O

LCD 显示的 COM1 - COM4 信号输出

O

O

LED 显示的 COM1 - COM4 信号输出

O

自动键盘扫描输出

可编程 I/O

I/O

I

外部中断输入 (下降沿)

I

ADC 输入通道 2 - 0

可编程 I/O

I/O

I

外部中断输入 (下降沿)

I

ADC 输入通道 3

可编程 I/O

I/O

O

PWM 输出

可编程 I/O

I/O

O

音频发生器输出

I

ADC 输入通道 9

说明

OTP 编程引脚说明* (OTP 编程模式)

引脚编号

44 引脚 32 引脚 28 引脚

13 14 15 14, 15 VDD PVDD

11 12 13 12 VPP P

12 13 14 13 GND P GND

10 11 12 11 SCK I OSCI

14 15 16 16 SDA I/O PORTA.0

*: OTP 编程模式只对 SH69P55A 有效, SH69K55A 没有 OTP 编程模式

焊垫

编号

引脚命名

引脚

性质

共用引脚 说明

RESET

编程电源 (+5.5V)

编程高压电源 (+11.0V)

电源地

编程时钟输入引脚

编程数据引脚

6

功能说明

1. CPU

SH69P55A/K55A

CPU 包含以下功能模块: 程序计数器 (PC), 算术逻辑单元

(ALU), 进位标志 (CY), 累加器, 查表寄存器, 数据指针

(INX, DPH, DPM, 和 DPL) 和堆栈。

1.1. PC

程序计数器用于寻址程序 ROM。该计数器有 12 位: 页寄存器

(PC11), 和循环递增计数器 (PC10, PC9, PC8, PC7, PC6,

PC5, PC4, PC3, PC2, PC1, PC0)。

程序计数器装入与该条指令相关的数据。对于目标地址大于

2K 的 ROM 空间, 可通过无条件跳转指令 (JMP) 中设置页寄

存器位的值实现跳转。

程序计数器只能寻址 4K 程序 ROM 空间 (参考 ROM 说明)。

1.2. ALU 和 CY

ALU 执行算术运算和逻辑操作。ALU 具有下述功能:

二进制加法/减法 (ADC, ADCM, ADD, ADDM, SBC, SBCM,

SUB, SUBM, ADI, ADIM, SBI, SBIM)

加法/减法的十进制调整 (DAA, DAS)

逻辑操作 (AND, ANDM, EOR, EORM, OR, ORM, ANDIM,

EORIM, ORIM)

条件跳转 (BA0, BA1, BA2, BA3, BAZ, BNZ, BC, BNC)

逻辑移位 (SHR)

进位标志 (CY) 记录 ALU 算术运算操作中的进位/借位状态。

在中断或子程序调用过程中, 进位标志被压入堆栈中并于执

行 RTNI 指令时由堆栈中弹出。它不受 RTNW 指令的影响。

1.3. 累加器 (AC)

累加器是一个 4 位寄存器, 用于保存算术逻辑单元的运算结

果。它和 ALU 一起, 完成与系统寄存器数据存储器之间的数

据传送。

2. RAM

1.4. 查表寄存器 (TBR)

通过查表指令 (TJMP) 和常数返回指令 (RTNW) 可以实现

读取保存在程序存储器中的表格数据。查表指令执行时,查表

寄存器 TBR和 AC 中存放的是待读取ROM 的低 8 位地址。

TJMP 指令指向的 ROM 地址为 ((PC11 - PC8) X (2

8

) + (TBR,

AC))。由 RTNW 指令将查表所得值返回至 (TBR, AC) 中。

表格数据的第 7 位至第 4 位存放在 TBR 中, 第 3 位至第 0 位

存放在 AC 中。

1.5. 数据指针

数据指针能直接寻址数据存储器。指针地址储存在寄存器

DPH (3 位), DPM (3 位) 和 DPL (4 位)。最大寻址范围为

3FFH。通过索引寄存器 (INX), 可以读写由 DPH, DPM 和

DPL 指定的数据存储器。

1.6. 堆栈

堆栈是一组寄存器, 在每次子程序调用或中断时能顺序保存

CY 和 PC (11-0) 中的值, 最高位保存 CY 值。其结构为 13

位 X 8 层。当遇到返回指令 (RTNI/RTNW) 时, 堆栈中的内

容将按顺序返回到 PC 中。堆栈中的数据按照先进后出的方

式处理。

注意:

堆栈嵌套包括子程序调用和中断请求子程序调用, 其最大值

为 8 层。如果程序调用和中断请求的数量超过 8 层, 堆栈底部

将溢出, 程序将无法正常执行。

内建 RAM 由通用数据存储器和系统寄存器组成。由于 RAM 的静态特性, 数据存储器能在 CPU 进入 STOP 或者 HALT 方式后

保持其中的数据不变。

2.1. RAM 寻址

用一条指令能直接访问数据存储器和系统寄存器。下列为存储器空间分配:

系统寄存器: $000 - $02F, $380 - $3AF,$3C0 - $3C2

数据存储器: $030 - $1A7

LCD RAM 空间: $300 - $313, $320 - $333

RAM 页切换如下所示:

Bank 0

B = 0

$000 - $07F $080 - $0FF $100 - $17F $180 - $1FF $200 - $27F $280 - $2FF $300 - $37F

Bank 1

B = 1

Bank 2

B = 2

Bank 3

B = 3

Bank 4

B = 4

Bank 5

B = 5

Bank 6

B = 6

Bank 7

B = 7

$380 - $3AF

$3C0 - $3C2

其中, B 在指令集中代表 RAM 页

7

SH69P55A/K55A

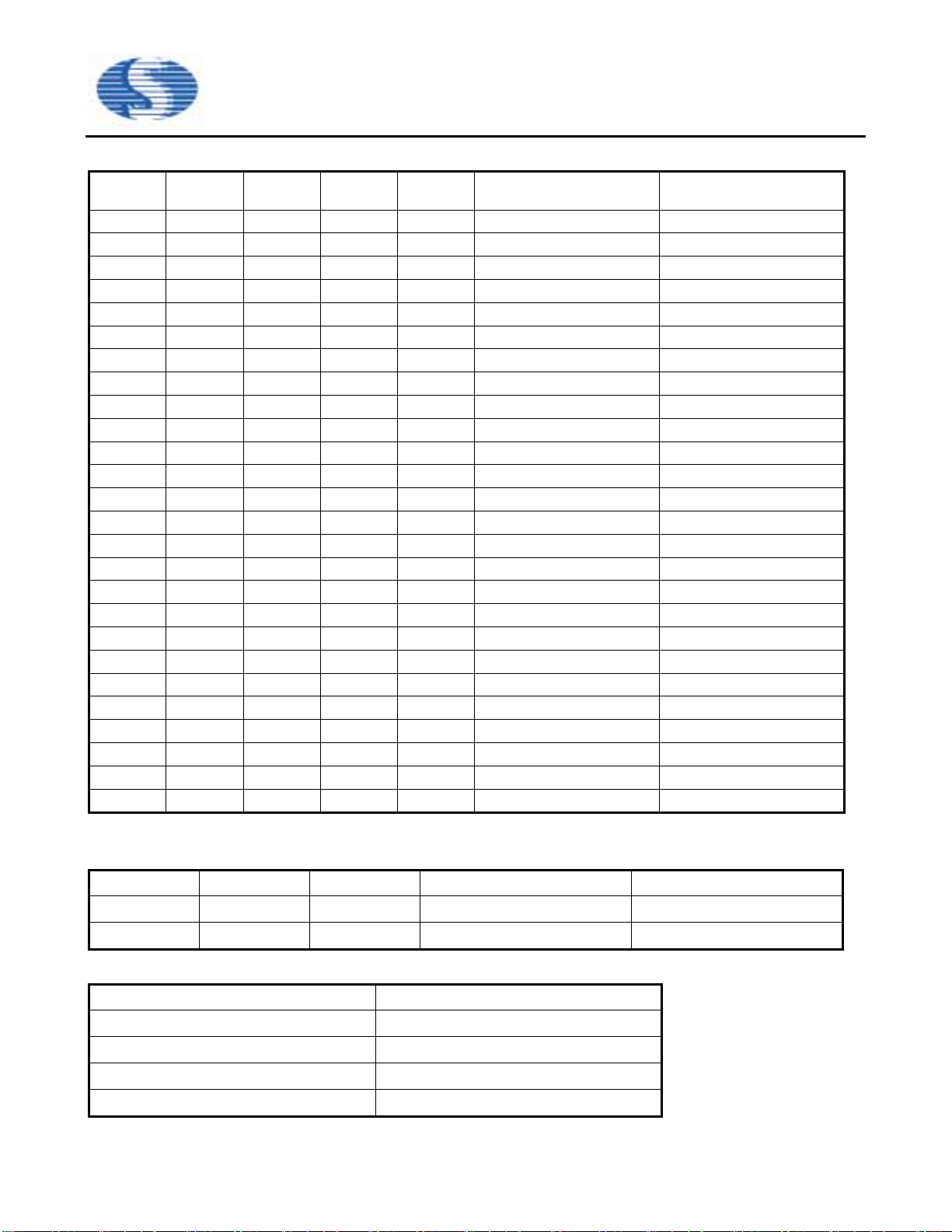

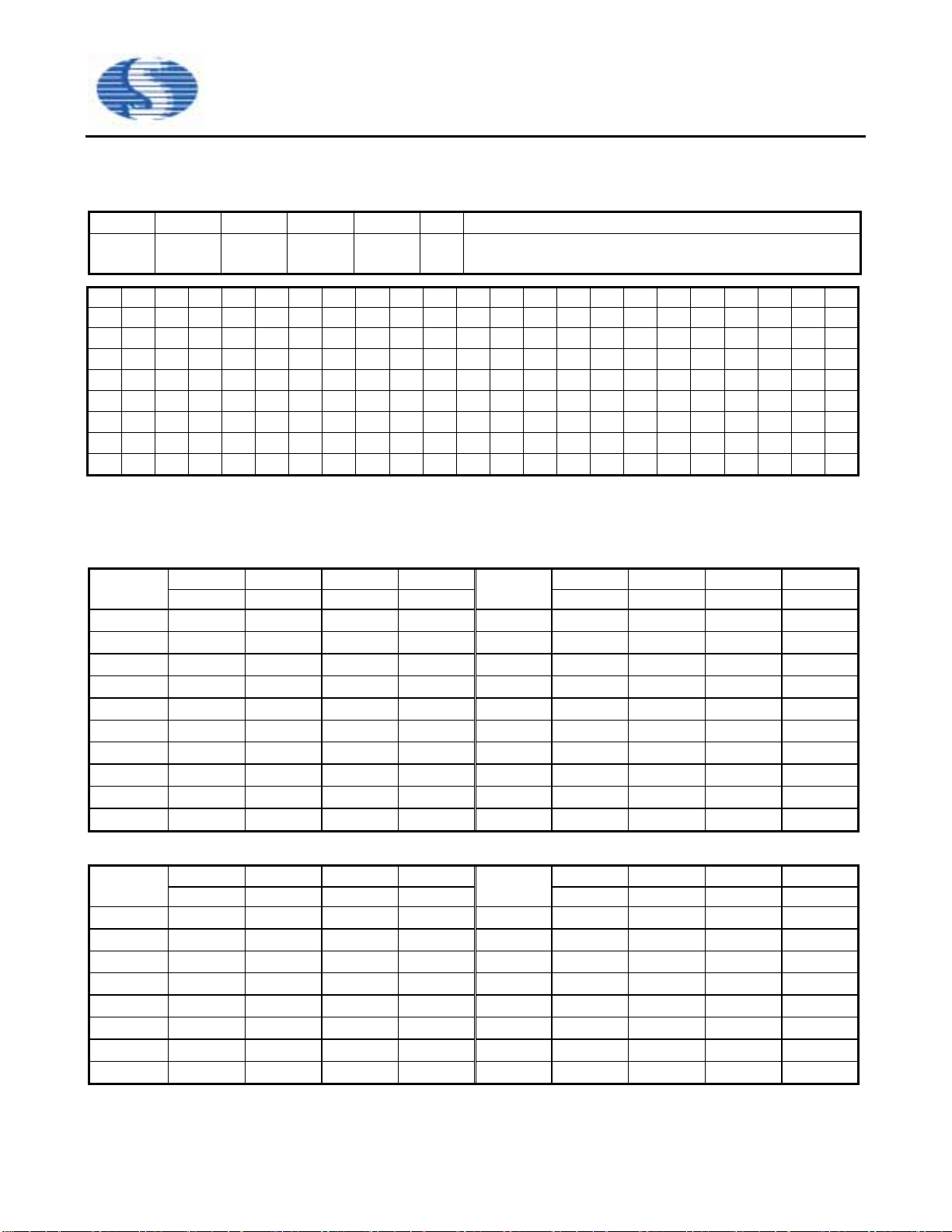

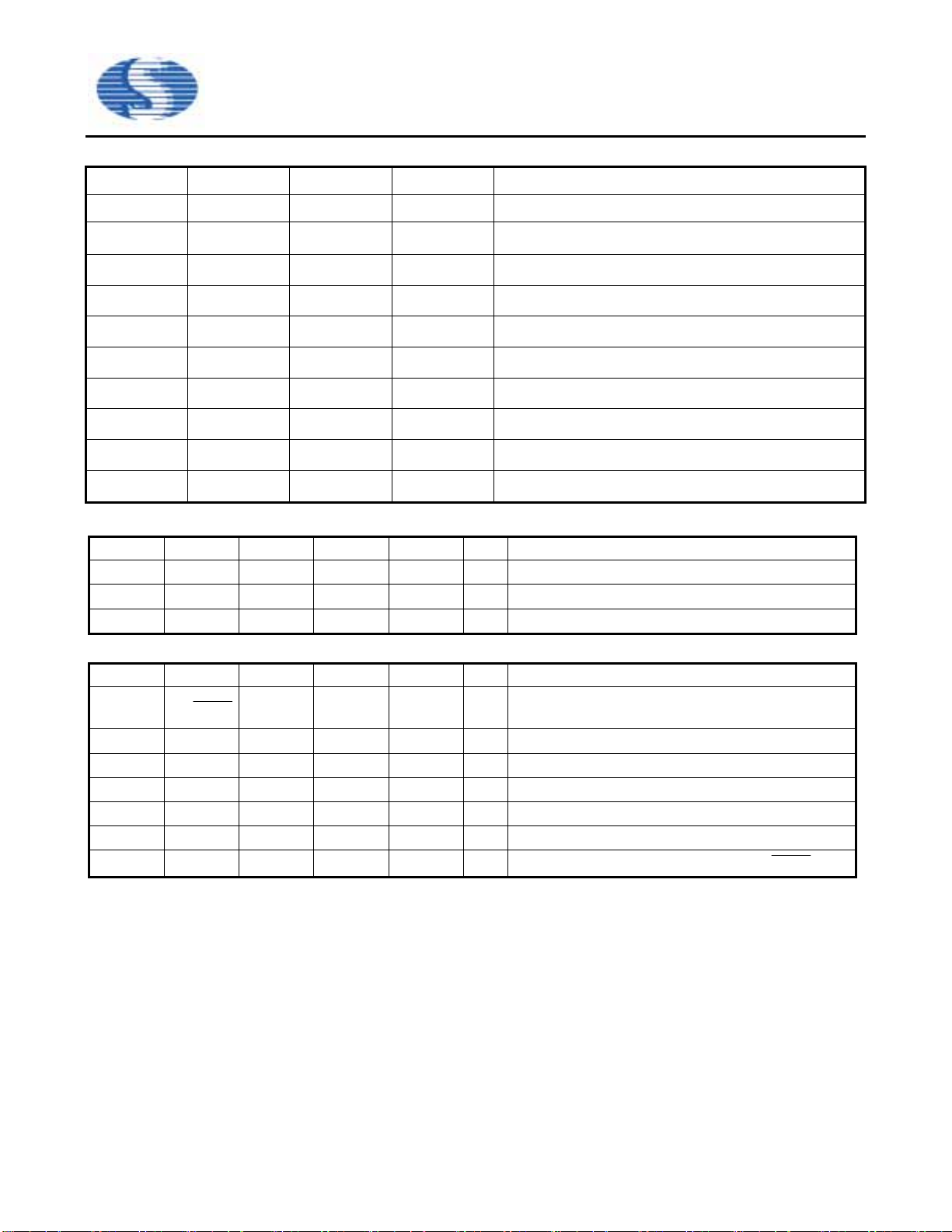

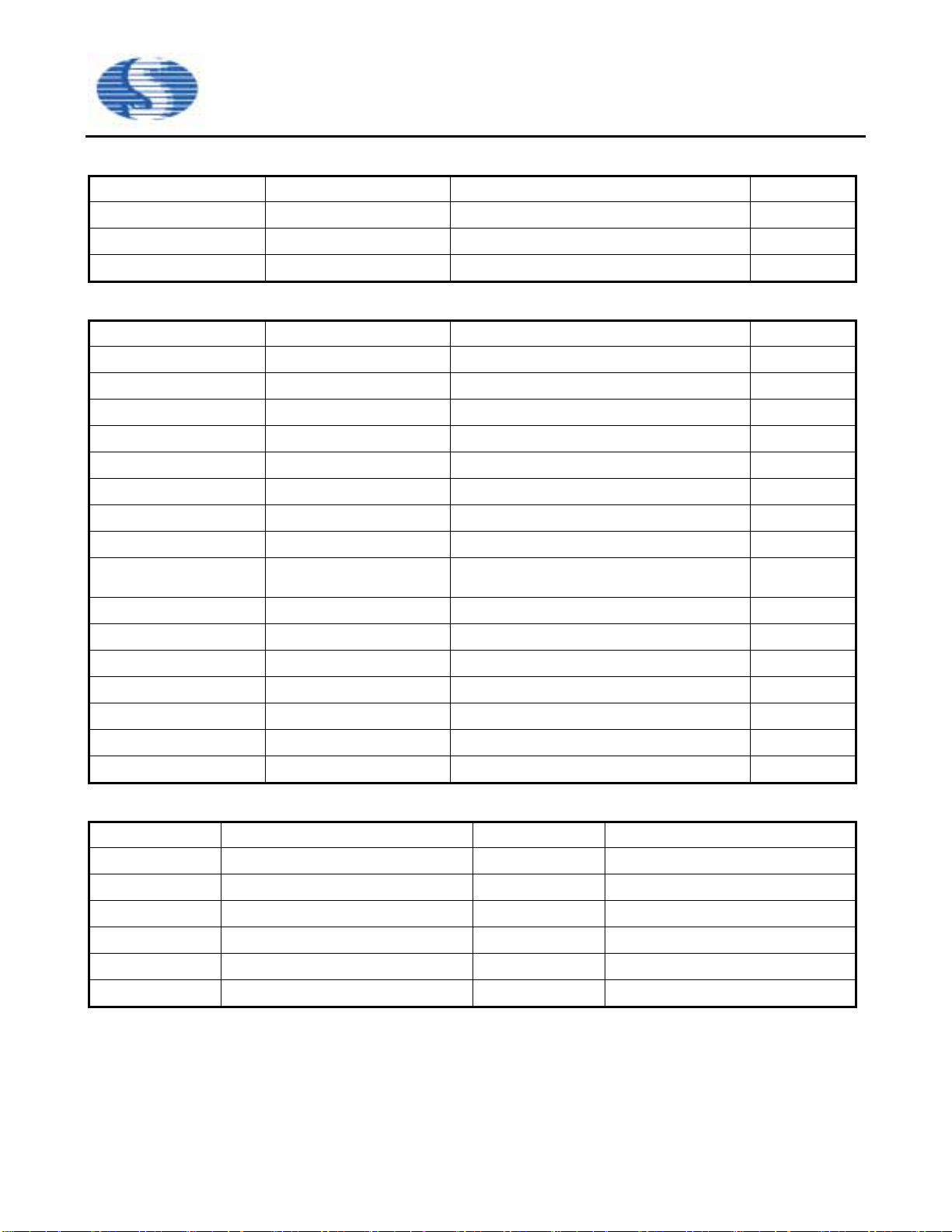

2.2. 系统寄存器的结构:

地址 第3位 第2位 第1位 第0位

$00 IET0 IET1 IET2 IEEX 读/写 中断允许标志寄存器

$01 IRQT0 IRQT1 IRQT2 IRQEX

$02 T0S T0M.2 T0M.1 T0M.0 读/写

$03 T0E T1M.2 T1M.1 T1M.0 读/写

$04 T0L.3 T0L.2 T0L.1 T0L.0

$05 T0H.3 T0H.2 T0H.1 T0H.0

$06 T1L.3 T1L.2 T1L.1 T1L.0

$07 T1H.3 T1H.2 T1H.1 T1H.0

$08 PA.3 PA.2 PA.1 PA.0

$09 PB.3 PB.2 PB.1 PB.0

$0A PC.3 PC.2 PC.1 PC.0

$0B PD.3 PD.2 PD.1 PD.0

$0C PE.3 PE.2 PE.1 PE.0

$0D PF.3 PF.2 PF.1 PF.0

$0E TBR.3 TBR.2 TBR.1 TBR.0

$0F INX.3 INX.2 INX.1 INX.0

$10 DPL.3 DPL.2 DPL.1 DPL.0

$11 - DPM.2 DPM.1 DPM.0

$12 - DPH.2 DPH.1 DPH.0

$13 VREF ACR2 ACR1 ACR0 读/写

$14 ADCON CH2 CH1 CH0 读/写

$15 T2E T2SC.2 T2SC.1 T2SC.0 读/写

$16 FS1 FS0 OXS OXON

$17 LVR - - -

$18 PACR.3 PACR.2 PACR.1 PACR.0

$19 PBCR.3 PBCR.2 PBCR.1 PBCR.0

$1A PCCR.3 PCCR.2 PCCR.1 PCCR.0

$1B PDCR.3 PDCR.2 PDCR.1 PDCR.0

$1C PECR.3 PECR.2 PECR.1 PECR.0

$1D PFCR.3 PFCR.2 PFCR.1 PFCR.0

$1E

$1F - - BNK1 BNK0

WDT

WDT.2 WDT.1 WDT.0

读/写 说明

读/写 中断请求标志寄存器

第 2-0 位: Timer0 模式寄存器

第 3 位: T0 信号源选择寄存器

第 2-0 位: Timer1 模式寄存器

第 3 位: T0 信号沿选择寄存器

读/写 Timer0 载入/计数器低位寄存器

读/写 Timer0 载入/计数器高位寄存器

读/写 Timer1 载入/计数器低位寄存器

读/写 Timer1 载入/计数器高位寄存器

读/写 PORTA 数据寄存器

读/写 PORTB 数据寄存器

读/写 PORTC 数据寄存器

读/写 PORTD 数据寄存器

读/写 PORTE 数据寄存器

读/写 PORTF 数据寄存器

读/写 查表寄存器

读/写 索引寄存器

读/写 索引地址低位寄存器 (4 位)

读/写 索引地址中位寄存器 (3 位)

读/写 索引地址高位寄存器 (3 位)

第 2-0 位: 模/数转换端口配置控制寄存器

第 3 位: 内部/外部参考电压选择寄存器

第 2-0 位: ADC 转换通道选择寄存器

第 3 位: 设置 ADC 转换允许选择寄存器

第 2-0 位: Timer2 预分频器分频比选择寄存器

第 3 位: T2 外部信号沿选择寄存器

第 0 位: 打开 PLL 寄存器

读/写

第 1 位: 时钟源选择 (1: PLL, 0: 32.768kHz) 寄存器

第 3-2 位: PLL 频率选择寄存器

读/写 第 3 位: 低电压复位标志寄存器 (只读和写 0)

读/写 PORTA 输入/输出控制寄存器

读/写 PORTB 输入/输出控制寄存器

读/写 PORTC 输入/输出控制寄存器

读/写 PORTD 输入/输出控制寄存器

读/写 PORTE 输入/输出控制寄存器

读/写 PORTF 输入/输出控制寄存器

读/写读第 2-0 位: 看门狗定时器控制寄存器

第 3 位: 看门狗定时器溢出标志寄存器 (只读)

读/写 第 1-0 位: ROM 页寄存器

8

SH69P55A/K55A

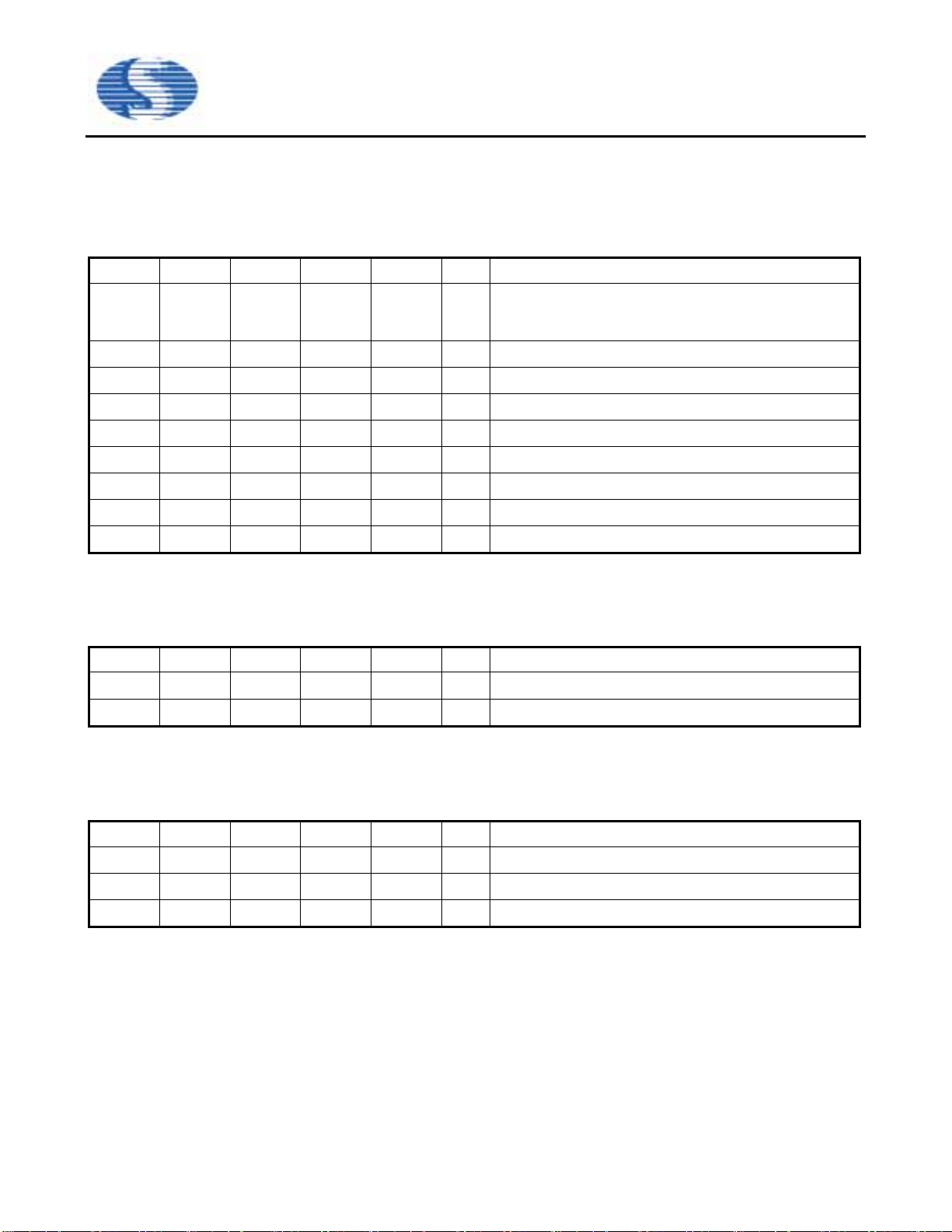

系统寄存器的结构 (续前表 1):

地址

$20 PWMS TCK1 TCK0 PWM_EN 读/写

$21 PP.3 PP.2 PP.1 PP.0 读/写 PWM 周期低位寄存器 (4 位)

$22 PP.7 PP.6 PP.5 PP.4 读/写 PWM 周期高位寄存器 (4 位)

$23 - FSTP - - 读/写 第 2 位: 在 STOP 模式下 32.768kHz 谐振器设置寄存器

$24 - - PDF.1 PDF.0 读/写 PWM 占空比微调寄存器 (2 位)

$25 PD.3 PD.2 PD.1 PD.0 读/写 PWM 占空比低位寄存器 (4 位)

$26 PD.7 PD.6 PD.5 PD.4 读/写 PWM 占空比高位寄存器 (4 位)

$27 T2GO DEC TM2S1 TM2S0

$28 KEYNUM1

$29 LCDON DUTY2 DUTY1 DUTY0 读/写

$2A -

$2B LEDEN LEDON EDUTY1 EDUTY0

$2C KEYC3 KEYC2 KEYC1 KEYC0 只读 第 3-0 位: KEY_O4 - 1 键盘扫描结果寄存器

$2D KEYL3 KEYL2 KEYL1 KEYL0 只读 第 3-0 位: KEY_I5 - 1 键盘扫描结果寄存器

$2E RLCD PS2 PS1 PS0 读/写

$2F

$380 RDT.3 RDT.2 RDT.1 RDT.0 读/写 ROM 数据列表地址/数据寄存器

$381 RDT.7 RDT.6 RDT.5 RDT.4 读/写 ROM 数据列表地址/数据寄存器

$382 RDT.11 RDT.10 RDT.9 RDT.8 读/写 ROM 数据列表地址/数据寄存器

$383 RDT.15 RDT.14 RDT.13 RDT.12 读/写 ROM 数据列表地址/数据寄存器

$384 T2D.3 T2D.2 T2D.1 T2D.0 读/写 Timer2 载入/计数器低位寄存器

$385 T2D.7 T2D.6 T2D.5 T2D.4 读/写 Timer2 载入/计数器中低位寄存器

$386 T2D.11 T2D.10 T2D.9 T2D.8 读/写 Timer2 载入/计数器中高位寄存器

$387 T2D.15 T2D.14 T2D.13 T2D.12 读/写 Timer2 载入/计数器高位寄存器

$388 PBIEN.3 PBIEN.2 PBIEN.1 PBIEN.0 读/写 PORTB 中断允许标志寄存器

$389 PBIF.3 PBIF.2 PBGIF.1 PBIF.0 读/写 PORTB 中断请求标志寄存器

$38A PCIEN.3 PCIEN.2 PCIEN.1 PCIEN.0 读/写 PORTC 中断允许标志寄存器

$38B PCIF.3 PCIF.2 PCIF.1 PCIF.0 读/写 PORTC 中断请求标志寄存器

$38C - - KEYIE ADIE 读/写

$38D - - KEYIF ADIF 读/写

GO/

第3位

DONE

KEYNUM0

第2位

KEYEND

- - -

TADC1 TADC0 - 读/写

第1位

第0位

KEYEN

读/写 说明

第 0 位: PWM 输出允许设置寄存器

第 2-1 位: PWM 时钟选择寄存器

第 3 位: PWM 占空比的输出模式设置寄存器

第 1-0 位: Timer2 模式选择寄存器

读/写

第 2 位: Timer2 方向沿有效允许寄存器

第 3 位: Timer2 功能启动控制寄存器

第 0 位: 键盘扫描器允许控制寄存器

读/写

第 1 位: 键扫描中止/工作寄存器

只读

第 3-2 位: 键盘扫描结果寄存器

第 2-0 位: 设置寄存器

第 3 位: LCD 打开设置寄存器

读/写 保留

第 1-0 位: 占空比和 COM 设置寄存器

读/写

第 2 位: LED 驱动器设置寄存器

第 3 位: LED 方式选择寄存器

第 2-0 位: SEG 配置寄存器

第 3 位: LCD 偏置电阻设置寄存器

第 2-1 位: 模/数转换时间选择寄存器

第 3 位: ADC 启动/状态标志寄存器

第 0 位: AD 中断允许标志寄存器

第 1 位: 键盘扫描中断允许标志寄存器

第 0 位: AD 中断请求标志寄存器

第 1 位: 键盘扫描中断请求标志寄存器

9

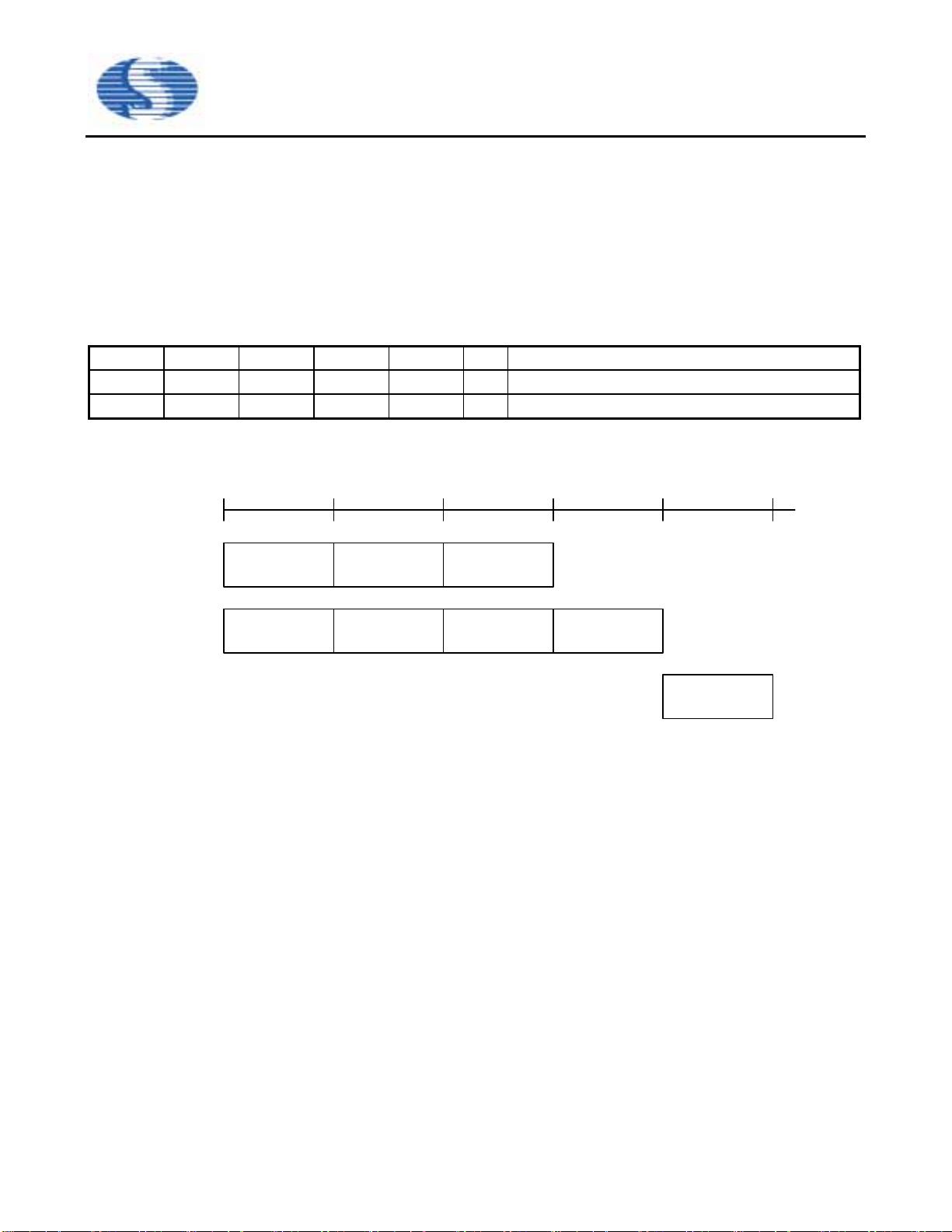

SH69P55A/K55A

系统寄存器的结构 (续前表 2):

地址

$38E PG.3 PG.2 PG.1 PG.0 读/写 PORTG 数据寄存器

$38F PH.3 PH.2 PH.1 PH.0 读/写 PORTH 数据寄存器

$390 PI.3 PI.2 PI.1 PI.0 读/写 PORTI 数据寄存器

$391 PJ.3 PJ.2 PJ.1 PJ.0 读/写 PORTJ 数据寄存器

$392 - - PK.1 PK.0 读/写 PORTK 数据寄存器

$393 PGCR.3 PGCR.2 PGCR.1 PGCR.0 读/写 PORTG 输入/输出控制寄存器

$394 PHCR.3 PHCR.2 PHCR.1 PHCR.0 读/写 PORTH 输入/输出控制寄存器

$395 PICR.3 PICR.2 PICR.1 PICR.0 读/写 PORTI 输入/输出控制寄存器

$396 PJCR.3 PJCR.2 PJCR.1 PJCR.0 读/写 PORTJ 输入/输出控制寄存器

$397 - - PKCR.1 PKCR.0 读/写 PORTK 输入/输出控制寄存器

$398

$399

$39A

$39B

$39C

$39D

$39E

$39F

$3A0

$3A1

$3A2

$3A3 TG1.3 TG1.2 TG1.1 TG1.0

$3A4 TG1.7 TG1.6 TG1.5 TG1.4

$3A5 TG1.11 TG1.10 TG1.9 TG1.8

$3A6 TG2.3 TG2.2 TG2.1 TG2.0

$3A7 TG2.7 TG2.6 TG2.5 TG2.4

$3A8 TG2.11 TG2.10 TG2.9 TG2.8

$3A9

$3AA

$3AB

$3AC TG2EN TV2.6 TV2.5 TV2.4 读/写

$3AD - - A1 A0

$3AE A5 A4 A3 A2

$3AF A9 A8 A7 A6

$3C0 T1S - - - R/W

$3C1 LPS3 LPS2 LPS1 LPS0 R/W

$3C2 ACR3 CH3 - - R/W

PPACR.3 PPACR.2 PPACR.1 PPACR.0

PPBCR.3 PPBCR.2 PPBCR.1 PPBCR.0

PPDCR.3 PPDCR.2 PPDCR.1 PPDCR.0

PPECR.3 PPECR.2 PPECR.1 PPECR.0

PPFCR.3 PPFCR.2 PPFCR.1 PPFCR.0

PPGCR.3 PPGCR.2 PPGCR.1 PPGCR.0

PPHCR.3 PPHCR.2 PPHCR.1 PPHCR.0

PPICR.3 PPICR.2 PPICR.1 PPICR.0

PPJCR.3 PPJCR.2 PPJCR.1 PPJCR.0

第3位

- PPCCR.2 PPCCR.1 PPCCR.0

- - PPKCR.1 PPKCR.0

TV1.3 TV1.2 TV1.1 TV1.0

TG1EN TV1.6 TV1.5 TV1.4 读/写

TV2.3 TV2.2 TV2.1 TV2.0

第2位

第1位

第0位

读/写 说明

读/写 PORTA 上拉控制寄存器

读/写 PORTB 上拉控制寄存器

读/写 PORTC 上拉控制寄存器

读/写 PORTD 上拉控制寄存器

读/写 PORTE 上拉控制寄存器

读/写 PORTF 上拉控制寄存器

读/写 PORTG 上拉控制寄存器

读/写 PORTH 上拉控制寄存器

读/写 PORTI 上拉控制寄存器

读/写 PORTJ 上拉控制寄存器

读/写 PORTK 上拉控制寄存器

读/写 音频发生器 1 低位寄存器

读/写 音频发生器 1 中位寄存器

读/写 音频发生器 1 高位寄存器

读/写 音频发生器 2 低位寄存器

读/写 音频发生器 2 中位寄存器

读/写 音频发生器 2 高位寄存器

读/写 音频发生器 1 音量低位寄存器

读/写 音频发生器 2 音量低位寄存器

只读 ADC 数据低位寄存器

只读 ADC 数据中位寄存器

只读 ADC 数据高位寄存器

第 2-0 位: 音频发生器 1 音量高位寄存器

第 3 位: 音频发生器 1 允许寄存器

第 2-0 位: 音频发生器 2 音量高位寄存器

第 3 位: 音频发生器 2 允许寄存器

Timer1 信号源选择寄存器

LCD 帧频控制寄存器

第 3 位:模/数转换端口配置控制寄存器

第 2 位:ADC 通道控制寄存器

10

SH69P55A/K55A

3. ROM

ROM 能寻址 8192 X 16 位程序空间, 地址由$000H 到$1FFFH。

3.1. 矢量地址区 ($000 到$004)

程序顺序执行。从地址$000 到$004 的区域是为特殊中断服务程序保留的, 作为中断服务的入口地址。

地址 指令 说明

$000 JMP*

$001 JMP*

$002 JMP*

$003 JMP*

$004 JMP*

* JMP 指令能由任意指令代替。

3.2. ROM 页切换

程序计数器 (PC11 - PC0) 只能寻址 4K 的 ROM 空间。页切换技术用于扩展 CPU 寻址范围。CPU 地址空间的前 2K 映像为 ROM

空间的低 2K (BANK0)。CPU 地址空间的高 2K 映像为 3 个页 (BNK.1-0 = 0, 1, 2。)

页切换如下所示:

跳转至 RESET 服务程序

跳转至 Timer0 中断服务程序

跳转至 Timer1 中断服务程序

跳转至 Timer2 中断服务程序

跳转至外部中断服务程序

CPU 地址

低 2K 地址

高 2K 地址

BNK = $00 BNK = $01 BNK = $02

0000 - 07FF

(BANK 0)

0800 - 0FFF

(BANK 1)

ROM 空间

0000 - 07FF

(BANK 0)

1000 - 17FF

(BANK 2)

0000 - 07FF

(BANK 0)

1800 - 1FFF

(BANK 3)

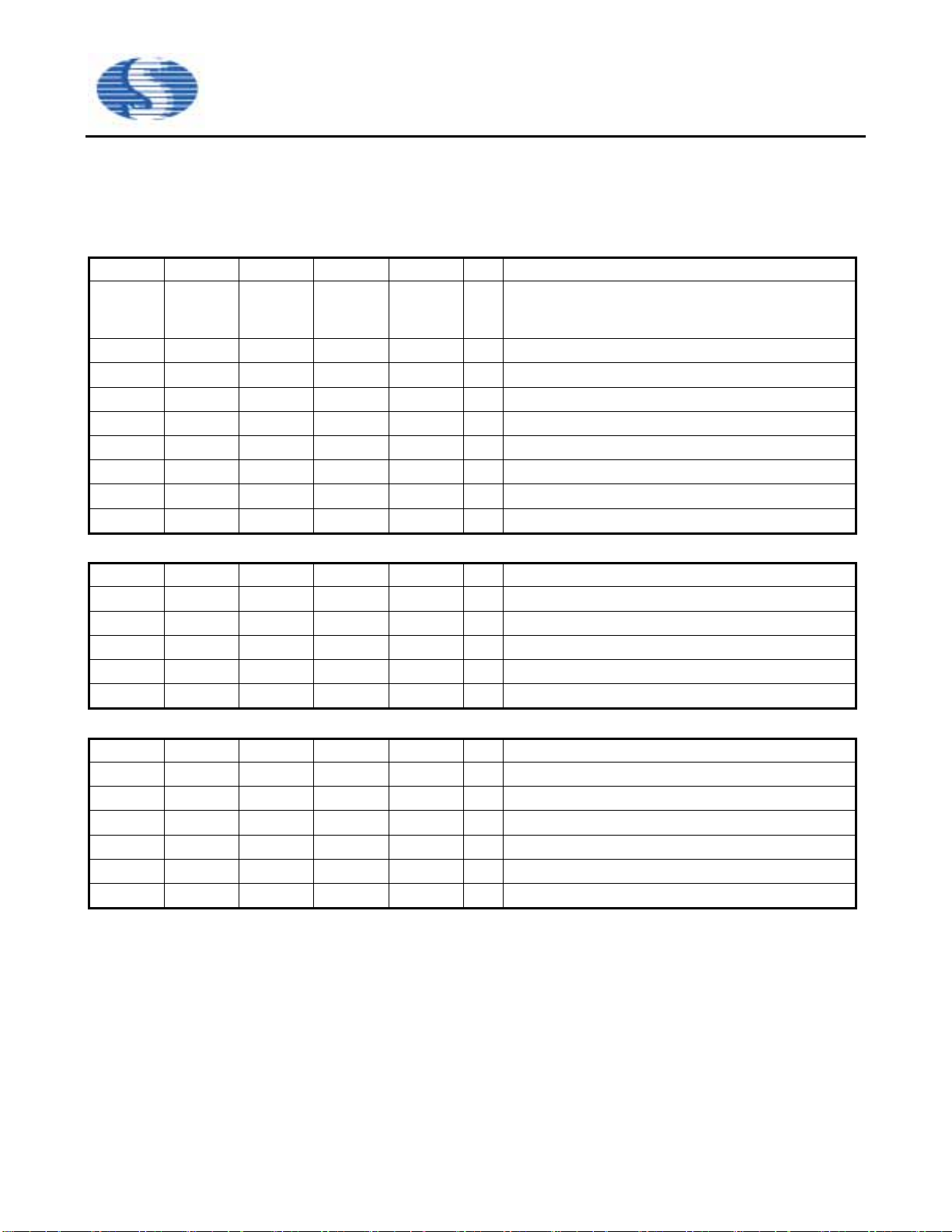

11

SH69P55A/K55A

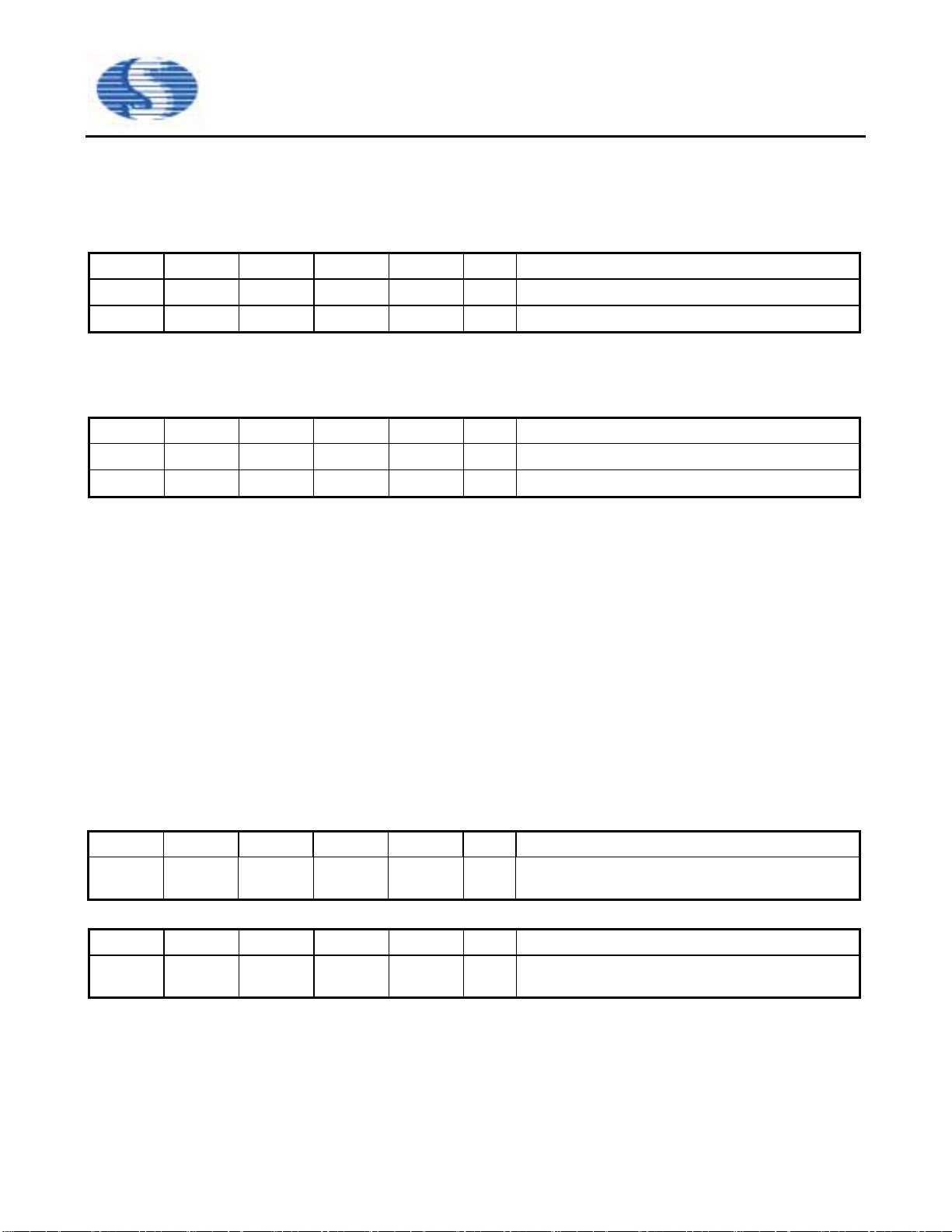

4. 初始状态

4.1. 系统寄存器初始状态:

地址

$00 IET0 IET1 IET2 IEEX 0000 0000

$01 IRQT0 IRQT1 IRQT2 IRQEX 0000 0000

$02 T0S T0M.2 T0M.1 T0M.0 0000 uuuu

$03 T0E T1M.2 T1M.1 T1M.0 0000 uuuu

$04 T0L.3 T0L.2 T0L.1 T0L.0 xxxx xxxx

$05 T0H.3 T0H.2 T0H.1 T0H.0 xxxx xxxx

$06 T1L.3 T1L.2 T1L.1 T1L.0 xxxx xxxx

$07 T1H.3 T1H.2 T1H.1 T1H.0 xxxx xxxx

$08 PA.3 PA.2 PA.1 PA.0 0000 0000

$09 PB.3 PB.2 PB.1 PB.0 0000 0000

$0A PC.3 PC.2 PC.1 PC.0 0000 0000

$0B PD.3 PD.2 PD.1 PD.0 0000 0000

$0C PE.3 PE.2 PE.1 PE.0 0000 0000

$0D PF.3 PF.2 PF.1 PF.0 0000 0000

$0E TBR.3 TBR.2 TBR.1 TBR.0 xxxx uuuu

$0F INX.3 INX.2 INX.1 INX.0 xxxx uuuu

$10 DPL.3 DPL.2 DPL.1 DPL.0 xxxx uuuu

$11 - DPM.2 DPM.1 DPM.0 -xxx -uuu

$12 - DPH.2 DPH.1 DPH.0 -xxx -uuu

$13 VREF ACR2 ACR1 ACR0 0000 uuuu

$14 ADCON CH2 CH1 CH0 0000 0uuu

$15 T2E T2SC.2 T2SC.1 T2SC.0 0000 uuuu

$16 FS1 FS0 OXS OXON 0000 uuuu

$17 LVR - - - 0--- *---

$18 PACR.3 PACR.2 PACR.1 PACR.0 0000 0000

$19 PBCR.3 PBCR.2 PBCR.1 PBCR.0 0000 0000

$1A PCCR.3 PCCR.2 PCCR.1 PCCR.0 0000 0000

$1B PDCR.3 PDCR.2 PDCR.1 PDCR.0 0000 0000

$1C PECR.3 PECR.2 PECR.1 PECR.0 0000 0000

$1D PFCR.3 PFCR.2 PFCR.1 PFCR.0 0000 0000

$1E WDT WDT.2 WDT.1 WDT.0 0000 #000

$1F - - BNK1 BNK0 --00 --00

$20 PWMS TCK1 TCK0 PWM_EN 0000 uuu0

$21 PP.3 PP.2 PP.1 PP.0 xxxx uuuu

$22 PP.7 PP.6 PP.5 PP.4 xxxx uuuu

$23 - FSTP -0-- -0--

第3位

第2位

第1位

第 0 位

上电复位

/Reset 引脚复位

WDT 复位

/低电压复位

12

SH69P55A/K55A

系统寄存器初始状态 (续前表 1):

地址 第 3 位 第 2 位 第 1 位 第 0 位

$24 PDF.1 PDF.0 --xx --uu

$25 PD.3 PD.2 PD.1 PD.0 xxxx uuuu

$26 PD.7 PD.6 PD.5 PD.4 xxxx uuuu

$27 T2GO DEC TM2S1 TM2S0 0000 0uuu

$28 KEYNUM1 KEYNUM0 KEYEND KEYEN 0000 000u

$29 LCDON DUTY2 DUTY1 DUTY0 0000 uuuu

$2A -

$2B LEDEN LEDON EDUTY1 EDUTY0 0000 uuuu

$2C KEYC3 KEYC2 KEYC1 KEYC0 0000 uuuu

$2D KEYL3 KEYL2 KEYL1 KEYL0 0000 uuuu

$2E RLCD PS2 PS1 PS0 0000 uuuu

$2F

$380 RDT.3 RDT.2 RDT.1 RDT.0 xxxx uuuu

$381 RDT.7 RDT.6 RDT.5 RDT.4 xxxx uuuu

$382 RDT.11 RDT.10 RDT.9 RDT.8 xxxx uuuu

$383 RDT.15 RDT.14 RDT.13 RDT.12 xxxx uuuu

$384 T2D.3 T2D.2 T2D.1 T2D.0 xxxx xxxx

$385 T2D.7 T2D.6 T2D.5 T2D.4 xxxx xxxx

$386 T2D.11 T2D.10 T2D.9 T2D.8 xxxx xxxx

$387 T2D.15 T2D.14 T2D.13 T2D.12 xxxx xxxx

$388 PBIEN.3 PBIEN.2 PBIEN.1 PBIEN.0 0000 0000

$389 PBIF.3 PBIF.2 PBIF.1 PBIF.0 0000 0000

$38A PCIEN.3 PCIEN.2 PCIEN.1 PCIEN.0 0000 0000

$38B PCIF.3 PCIF.2 PCIF.1 PCIF.0 0000 0000

$38C - KEYIE ADIE --00 --00

$38D - - KEYIF ADIF --00 --00

$38E PG.3 PG.2 PG.1 PG.0 0000 0000

$38F PH.3 PH.2 PH.1 PH.0 0000 0000

$390 PI.3 PI.2 PI.1 PI.0 0000 0000

$391 PJ.3 PJ.2 PJ.1 PJ.0 0000 0000

$392 - - PK.1 PK.0 --00 --00

$393 PGCR.3 PGCR.2 PGCR.1 PGCR.0 0000 0000

$394 PHCR.3 PHCR.2 PHCR.1 PHCR.0 0000 0000

$395 PICR.3 PICR.2 PICR.1 PICR.0 0000 0000

$396 PJCR.3 PJCR.2 PJCR.1 PJCR.0 0000 0000

$397 - - PKCR.1 PKCR.0 --00 --00

$398 PPACR.3 PPACR.2 PPACR.1 PPACR.0 0000 0000

GO/

DONE

- - -

TADC1 TADC0 - 000- 0uu-

上电复位

/Reset 引脚复位

---- ----

WDT 复位

/低电压复位

13

SH69P55A/K55A

系统寄存器初始状态 (续前表 2):

地址 第 3 位 第 2 位 第 1 位 第 0 位

$399 PPBCR.3 PPBCR.2 PPBCR.1 PPBCR.0 0000 0000

$39A - PPCCR.2 PPCCR.1 PPCCR.0 -000 -000

$39B PPDCR.3 PPDCR.2 PPDCR.1 PPDCR.0 0000 0000

$39C PPECR.3 PPECR.2 PPECR.1 PPECR.0 0000 0000

$39D PPFCR.3 PPFCR.2 PPFCR.1 PPFCR.0 0000 0000

$39E PPGCR.3 PPGCR.2 PPGCR.1 PPGCR.0 0000 0000

$39F PPHCR.3 PPHCR.2 PPHCR.1 PPHCR.0 0000 0000

$3A0 PPICR.3 PPICR.2 PPICR.1 PPICR.0 0000 0000

$3A1 PPJCR.3 PPJCR.2 PPJCR.1 PPJCR.0 0000 0000

$3A2 - - PPKCR.1 PPKCR.0 --00 --00

$3A3 TG1.3 TG1.2 TG1.1 TG1.0 xxxx uuuu

$3A4 TG1.7 TG1.6 TG1.5 TG1.4 xxxx uuuu

$3A5 TG1.11 TG1.10 TG1.9 TG1.8 xxxx uuuu

$3A6 TG2.3 TG2.2 TG2.1 TG2.0 xxxx uuuu

$3A7 TG2.7 TG2.6 TG2.5 TG2.4 xxxx uuuu

$3A8 TG2.11 TG2.10 TG2.9 TG2.8 xxxx uuuu

$3A9 TV1.3 TV1.2 TV1.1 TV1.0 xxxx uuuu

$3AA TG1EN TV1.6 TV1.5 TV1.4 xxxx uuuu

$3AB TV2.3 TV2.2 TV2.1 TV2.0 xxxx uuuu

$3AC TG2EN TV2.6 TV2.5 TV2.4 xxxx uuuu

$3AD - - A1 A0 --xx --uu

$3AE A5 A4 A3 A2 xxxx uuuu

$3AF A9 A8 A7 A6 xxxx uuuu

$3C0 T1S - - - 0--- u---

$3C1 LPS3 LPS2 LPS1 LPS0 0000 uuuu

$3C2 ACR3 CH3 - - 00-- uu--

上电复位

/Reset 引脚复位

WDT 复位

/低电压复位

说明: x = 不定; u = 未更改; - = 未使用, 读出值为'0'。

*, #: 其他详细信息, 请参考下表:

WDT复位 低电压复位 WDT复位及低电压复位 上电复位/Reset引脚复位

*

#

4.2. 其它初始状态:

程序计数器 (PC)

累加器 (AC) 不定

数据存储器 不定

14

0 1 1 0

1 0 1 0

其它 复位后

$000

CY 不定

SH69P55A/K55A

5. 系统时钟和振荡器

SH69P55A/69K55A 有一个代码选项决定的时钟源。时钟源产生的基本时钟脉冲以提供系统时钟支持 CPU 及片上外围设备。

系统时钟 f

SYS = fOSC/4。

5.1. 指令周期:

(1) 对于 32.768kHz 的振荡器, 为 4/32768Hz (≈ 122µs)。

(2) 对于 8MHz 的振荡器, 为 4/8MHz (= 0.5µs)。

5.2. 振荡器类型

(1) 晶体谐振器: 32.768kHz 或者 400kHz - 8MHz

(2) 陶瓷谐振器: 400kHz - 8MHz

OSCI

OSCO

PLL_C

(3) RC振荡器: 400kHz - 8MHz

OSCI

OSCO

PLL_C

外部RC

(5) PLL 振荡器 (1, 2, 4, 8MHz)

OSCI

OSCO

PLL_C

RPLL = 100K

ROSC

C1

Crystal

C2

VDD

C1

32.768

kHz

C2

C3 = 2200p

C1

OSCI

Ceramic

OSCO

C2

PLL_C

(4) RC 振荡器: 4MHz

OSCI

OSCO

PLL_C

内建RC

注意:

- 如果选择外部 RC 振荡器, OSCO 引脚用作 I/O 端口 (PORTC.1)。

- 如果选择内建 RC 振荡器, OSCO 引脚用作 I/O 端口 (PORTC.1) 同时 OSCI 引脚用作 I/O 端口 (PORTC.2)。

- 如果不使用 PLL 时钟, PLL_C 可用作 I/O 端口 (PORTC.0)。

15

SH69P55A/K55A

5.3. PLL 时钟源的控制

SH69P55A/69K55A 内建一个锁相环路 (PLL), 能在当选择 32.768kHz 谐振器时提供最大等于 8MHz 的时钟源。PLL 时钟通过

系统控制寄存器开启或关闭。当 PLL 时钟开启时, PORTC.0 端口作为 PLL 阻容网络连接端口 (连接阻容网络)。当 PLL 关闭时,

PORTC.0 作为 I/O 端口使用。

PLL 控制寄存器$16

地址

第3位 第2位 第1位 第0位

读/写 说明

第 0 位: 打开 PLL 寄存器

$16 FS1 FS0 OXS OXON 读/写

第 1 位: 时钟源选择 (1: PLL, 0: 32.768kHz) 寄存器

第 3-2 位: PLL 频率选择寄存器

X X X 0 读/写 关闭 PLL

X X X 1 读/写 开启 PLL (代码选项中选择 32.768kHz 谐振器)

X X 0 X 读/写 选择 32.768kHz 谐振器作为时钟源

X X 1 1 读/写 选择 PLL 作为时钟源

0 0 1 1 读/写

PLL 提供 8MHz 的时钟信号作为时钟源

(代码选项中一定需要选择 LVR 的电压范围是 4V)

0 1 1 1 读/写 PLL 提供 4MHz 的时钟信号作为时钟源

1 0 1 1 读/写 PLL 提供 2MHz 的时钟信号作为时钟源

1 1 1 1 读/写 PLL 提供 1MHz 的时钟信号作为时钟源

注意:

1. PLL 时钟使用说明:

首先, 在 PLL 控制寄存器, 设置 FS1 和 FS0

其次, 设置 OXON = 1, 打开 PLL

第三, 延时至少 2ms

最后, 设置 OXS = 1, 选择 PLL 作为时钟源。

2. 如果在代码选项中选择 LVR 的电压范围是 2.5V, 则 PLL 只能提供低于 8MHz 的时钟信号作为时钟源。

系统寄存器$23

地址

$23 - FSTP - -

X 1 X X 读/写

X 0 X X 读/写

第3位 第2位 第1位 第0位

读/写 说明

读/写 第 2 位: 在 STOP 模式下 32.768kHz 谐振器设置寄存器

在 STOP 模式下关闭 32.768kHz 谐振器

(代码选项中选择 32.768kHz 谐振器)

在 STOP 模式下不关闭 32.768kHz 谐振器

(代码选项中选择 32.768kHz 谐振器)

16

SH69P55A/K55A

5.4. 谐振器负载电容选择

陶瓷谐振器

频率

455kHz 47 - 100pF 47 - 100pF

3.58MHz - -

4MHz - -

*- 已经内建有负载电容

频率

32.768kHz 5 - 12.5pF 5 - 12.5pF

4MHz 8 - 15pF 8 - 15pF

8MHz 8 - 15pF 8 - 15pF

C1 C2

晶体谐振器

C1 C2

推荐型号 生产厂

ZTB 455KHz

ZT 455E

ZTT 3.580M

ZT 3.58M*

ZTT 4.000M

ZT 4M* 深圳东光晶博电子有限公司

推荐型号 生产厂

DT 38 (φ3x8)

φ3x8 - 32.768KHz 威克创通讯器材有限公司

HC-49U/S 4.000MHz

49S-4.000M-F16E

HC-49U/S 8.000MHz

49S-8.000M-F16E

威克创通讯器材有限公司

深圳东光晶博电子有限公司

威克创通讯器材有限公司

深圳东光晶博电子有限公司

威克创通讯器材有限公司

KDS

威克创通讯器材有限公司

深圳东光晶博电子有限公司

威克创通讯器材有限公司

深圳东光晶博电子有限公司

注意事项:

1. 表中负载电容为设计参考数据!

2. 以上电容值可通过谐振器基本的起振和运行测试, 并非最优值。

3. 请注意印制板上的杂散电容, 用户应在超过应用电压和温度的条件下测试谐振器的性能。

在应用陶瓷谐振器/晶体谐振器之前, 用户需向谐振器生产厂要求相关应用参数以获得最佳性能。

请登陆http://www.sinowealth.com

以取得更多的推荐谐振器生产厂。

17

SH69P55A/K55A

6. I/O 端口

SH69P55A/69K55A 提供包括 1 个开漏输出在内的 42 个可编程双向 I/O 端口。端口数据在寄存器$08 - $0D 和$38E - $392 中。

端口控制寄存器 ($18 - $1D 和$393 - $397) 控制端口为输入或者输出。每个 I/O 端口 (不包括那些开漏输出端口) 包含上拉电

阻, 通过各自端口上拉电阻控制寄存器 ($398 - $3A2) 相应的值来控制。

当端口被选择作为输入口, 写“1”到各自相对的端口上拉控制寄存器 ($398 - $3A2) 可以打开上拉电阻, 写“0”可以关闭上拉电阻。

不论各自端口上拉控制寄存器 (398 - $3A2) 相对应位的值是多少, 当端口作为输出端口时, 上拉电阻将会自动关闭。

当 PORTB 和 PORTC 被选择作为输入端口, 它们可以通过下降沿触发端口中断 (若端口中断已经允许)。

系统寄存器$08 - $0D, $38E - $392: 端口数据寄存器

地址

$08 PA.3 PA.2 PA.1 PA.0 读/写 PORTA 数据寄存器

$09 PB.3 PB.2 PB.1 PB.0 读/写 PORTB 数据寄存器

$0A PC.3 PC.2 PC.1 PC.0 读/写 PORTC 数据寄存器

$0B PD.3 PD.2 PD.1 PD.0 读/写 PORTD 数据寄存器

$0C PE.3 PE.2 PE.1 PE.0 读/写 PORTE 数据寄存器

$0D PF.3 PF.2 PF.1 PF.0 读/写 PORTF 数据寄存器

$38E PG.3 PG.2 PG.1 PG.0 读/写 PORTG 数据寄存器

$38F PH.3 PH.2 PH.1 PH.0 读/写 PORTH 数据寄存器

$390 PI.3 PI.2 PI.1 PI.0 读/写 PORTI 数据寄存器

$391 PJ.3 PJ.2 PJ.1 PJ.0 读/写 PORTJ 数据寄存器

$392 - - PK.1 PK.0 读/写 PORTK 数据寄存器

系统寄存器$18 - $1D, $393 - $397: 端口控制寄存器

地址

$18 PACR.3 PACR.2 PACR.1 PACR.0

$19 PBCR.3 PBCR.2 PBCR.1 PBCR.0

$1A PCCR.3 PCCR.2 PCCR.1 PCCR.0

$1B PDCR.3 PDCR.2 PDCR.1 PDCR.0

$1C PECR.3 PECR.2 PECR.1 PECR.0

$1D PFCR.3 PFCR.2 PFCR.1 PFCR.0

$393 PGCR.3 PGCR.2 PGCR.1 PGCR.0

$394 PHCR.3 PHCR.2 PHCR.1 PHCR.0

$395 PICR.3 PICR.2 PICR.1 PICR.0

$396 PJCR.3 PJCR.2 PJCR.1 PJCR.0

$397 - - PKCR.1 PKCR.0

第3位

第3位

第2位

第2位

第1位

第1位

第0位 读/写 说明

第0位 读/写 说明

读/写 PORTA 输入/输出控制寄存器

读/写 PORTB 输入/输出控制寄存器

读/写 PORTC 输入/输出控制寄存器

读/写 PORTD 输入/输出控制寄存器

读/写 PORTE 输入/输出控制寄存器

读/写 PORTF 输入/输出控制寄存器

读/写 PORTG 输入/输出控制寄存器

读/写 PORTH 输入/输出控制寄存器

读/写 PORTI 输入/输出控制寄存器

读/写 PORTJ 输入/输出控制寄存器

读/写 PORTK 输入/输出控制寄存器

PA (/B/C/D/E/F/G/H/I/J) PCR.n, (n = 0, 1, 2, 3), PKPCR.n (n = 0, 1)

0: 设置为输入口。(初始值)

1: 设置为输出口。

18

SH69P55A/K55A

系统寄存器$398 - $3A2: 端口上拉控制寄存器

地址

第3位

第2位

第1位

第0位 读/写 说明

$398 PPACR.3 PPACR.2 PPACR.1 PPACR.0 读/写 PORTA 上拉控制寄存器

$399 PPBCR.3 PPBCR.2 PPBCR.1 PPBCR.0

$39A - PPCCR.2 PPCCR.1 PPCCR.0

$39B PPDCR.3 PPDCR.2 PPDCR.1 PPDCR.0

$39C PPECR.3 PPECR.2 PPECR.1 PPECR.0

$39D PPFCR.3 PPFCR.2 PPFCR.1 PPFCR.0

$39E PPGCR.3 PPGCR.2 PPGCR.1 PPGCR.0

$39F PPHCR.3 PPHCR.2 PPHCR.1 PPHCR.0

$3A0 PPICR.3 PPICR.2 PPICR.1 PPICR.0

$3A1 PPJCR.3 PPJCR.2 PPJCR.1 PPJCR.0

$3A2 - - PPKCR.1 PPKCR.0

读/写 PORTB 上拉控制寄存器

读/写 PORTC 上拉控制寄存器

读/写 PORTD 上拉控制寄存器

读/写 PORTE 上拉控制寄存器

读/写 PORTF 上拉控制寄存器

读/写 PORTG 上拉控制寄存器

读/写 PORTH 上拉控制寄存器

读/写 PORTI 上拉控制寄存器

读/写 PORTJ 上拉控制寄存器

读/写 PORTK 上拉控制寄存器

PA (/B/D/E/F/G/H/I/J) CR.n, (n = 0, 1, 2, 3), PKCR.n (n = 0, 1), PCCR.n (n = 0, 1, 2)

0: 禁止内部上拉电阻。(初始值)

1: 允许内部上拉电阻。

I/O引脚的等效电路

Pull hi gh

Register

VDD

VDD

Pull high

I/O Control

Register

I/O Pad

DATA

Register

GND

DATA

READ DATA I N

READ

M2T 1

0

1

s

19

SH69P55A/K55A

PORTA.3 - 0 共用为 LCD 或 LED 显示 SEG4 - SEG1 信号输出, 也可以共用为自动键盘扫描 KEY_I4 - 1 输入。

PORTB.3 - 0

PORTC.0

当 SH69P55A/69K55A 使用外部 RC 振荡器或者内部 RC 振荡器作为系统振荡器时, OSCO 引脚可以通过代码选项设置为

共用为 ADC AN3 - 0 输入通道。

共用为 PLL_C, 如果允许 PLL, 该端口须连接阻容网络。

PORTC.1。

当 SH69P55A/69K55A 使用内部 RC 振荡器作为系统振荡器时, OSCI 引脚可以通过代码选项设置为 PORTC.2。

RESET

PORTD.3 - 0

PORTE.3 - 0

- COM6

PORTF.3 - 0

PORTG.0

PORTG.1

PORTG.2

PORTG.3

PORTH.3 - 0

PORTI.3 - 0

PORTJ.3 - 0

重要事项:

在 32 引脚封装中, 须选择PORTH.0, PORTH.1 和 PORTI - K输出为 0 (端口控制寄存器 (PCR): $394 = xx11B, $395 - $396 =

在 28 引脚封装中, 须选择 PORTD, PORTF, PORTH, PORTI.3 - 2 和 PORTK 输出为 0 (端口控制寄存器 (PCR): $1B, $1D,

在 SH69P55A/69K55A, 每个输出端口包含一个锁存器, 用来保存输出数据。在输出模式下写端口数据寄存器 (PDR) 可以直

引脚可以通过代码选项, 设置为 PORTC.3。

共用为 LCD 或 LED 显示的 COM1 - COM4 信号输出, 也可以共用为自动键盘扫描 KEY_O4 - 1 信号输出。

共用为 LCD 显示的 COM5 - COM8 或 SEG20 - SEG17 信号输出, 且 PORTE.3 - 2 可以共用为 LED 显示的 COM5

信号输出。

共用为 LCD 或 LED 显示的 SEG8 - SEG5 信号输出, 且 PORTF.0 共用为自动键盘扫描的 KEY_I 信号输入。

共用为 PWM 输出。

共用为 TONE 输出或 ADC AN9 输入。

共用为 T0 输入或 ADC 参考电压输入。

共用为 T2 输入 ADC AN8 输入。

共用为 LCD 显示的 SEG16 - SEG13 信号输出。

共用为 LCD 显示的 SEG12 - SEG9 信号输出。

共用为 ADC AN7 - 4 输入通道。

1111B , $397 = 0011B

$3 9 4 = 1111 B , $ 395 = 11xxB, $397 = 0011B

0000B)

。

接传输数据到相应的端口。所有输入端口不包含锁存器, 所以外部输入电平要一直保持到端口读取动作完成。端口控制寄存器

的内容决定每个双向 I/O 端口是输入或输出端口, 写“0”到端口控制寄存器 (PCR) 设置端口为输入模式, 写“1”到端口控制寄存

器 (PCR) 设置端口为输出模式。当选择一个数字 I/O 端口作为输出端口时, 相应端口位读取输出数据锁存器的值, 而非端口

的外部电平。当选择一个数字 I/O 端口作为输入端口时, 相应端口位读取的值与相应端口的外部电平相关。无论端口控制寄存

器 (PCR) 的状态如何, 输出数据锁存器总是可写入。因此, 当使用输入和输出混合模式下的端口时, 选择这些端口的输出锁

存器的内容作为输入可能通过执行逻辑指令而重写。所以强烈要求在从输入模式转换到输出模式时, 改变在端口控制寄存器

和端口数据寄存器 (PDR): $38F = xx00B 和$390 - $391 = 0000B, $392 = 0000B)。

和端口数据寄存器 (PDR): $0B $0D, $38F = 0000B, $390 = 00xxB, $392 =

(PCR) 的相应位之前在端口数据寄存器 (PDR) 中写入适当的数据, 避免干扰相关端口。

20

SH69P55A/K55A

端口中断

PORTB 和 PORTC 用作端口中断源。由于 PORTB 和 PORTC 是位可编程的 I/O, 因此只有 PORTB 和 PORTC 用作通用输入端

口时

, 引脚上 VDD 到 GND 的跳变才能产生端口中断。而当 PORTB 和 PORTC 用作模拟输入 (ADC 输入等) 时, 无法产生中断

请求。

中断控制标志映像为系统寄存器的$388, $38A。通过软件可以读写这两个寄存器。芯片复位后所有标志被清 0。端口中断可以

用来将 CPU 从 HALT 或者 STOP 模式唤醒。

系统寄存器$388, $38A: 端口中断允许标志寄存器

地址

第3位

第2位

第1位

第0位 读/写

$388 PBIEN.3 PBIEN.2 PBIEN.1 PBIEN.0

$38A PCIEN.3 PCIEN.2 PCIEN.1 PCIEN.0

PB/CIEN.n, (n = 0, 1, 2, 3)

0:

禁止端口中断。(初始值)

1:

允许端口中断。

系统寄存器$389, $38B: 端口中断请求标志寄存器

地址

第3位

第2位

第1位

第0位 读/写

$389 PBIF.3 PBIF.2 PBIF.1 PBIF.0

$38B PCIF.3 PCIF.2 PCIF.1 PCIF.0

PB/CIF.n, (n = 0, 1, 2, 3)

没有发生端口中断。(初始值)

0:

1:

已经发生端口中断。

该寄存器只能清 0。

以下为端口中断功能模块图, 仅供参考。

PB.3 - 0

PBCR.3 - 0

PC.3 - 0

PCCR.3 - 0

Falling Edge

Detector

Falling Edge

Detector

Request Flag

(PBIF.3 - 0)

Request Flag

(PCIF.3 - 0)

说明

读/写 PORTB 中断允许标志寄存器

读/写 PORTC 中断允许标志寄存器

说明

读/写 PORTB 中断请求标志寄存器

读/写 PORTC 中断请求标志寄存器

PBIEN.3 - 0

PCIEN.3 - 0

IRQEX

external interrupt

request generator

IEEX

Interrupt CPU

端口中断编程注意事项

PORTB & PORTC端口的任何一个引脚上电平出现由 VDD 到 GND 的转换将置PBIF.x 或 PCIF.x为 1, 而跟 PORTB 和 PORTC

:

其它引脚上的电平无关。

如果 PBIEN.x (或者 PCIEN.x) = 1 和 IEEX = 1, PORTB (或者 PORTC) 的 x 输入引脚上电平出现由 VDD 到 GND 的转换将产

生一个中断请求

(PBIF.x = 1 或者 PCIF.x = 1) 并中断 CPU, 而跟 PORTB (或者 PORTC) 其它引脚上的电平无关。

21

SH69P55A/K55A

7. 定时器/计数器 (Timer)

SH69P55A/69K55A 有3 个定时器: 两个8 位定时器 (Timer0,

Timer1)

8

- 8

-

- 8

-

和一个 16 定时器 (Timer2)。

位 Timer 有下述特性:

位递增计数

自动重载

级预分频

计数值由$FF 到$00 时, 产生溢出中断请求。

Timer 框图:

System

clock

EOR

T0

T0E

功能:

Timer

可编程定时功能

-

-

计数值可读

MUX

T0S

OSC SYNC

t

Prescaler

TM.2 TM.0

TM.1

8-BIT

COUNTER

7.1. Timer0 和 Timer1 结构和操作

Timer0和Timer1都由一个8位只写载入寄存器 (TL0L, TL0H

和 TL1L, TL1H) 和一个8位只读计数器 (TC0L, TC0H 和

TC1L, TC1H) 构成。每个计数器由低四位和高四位组成。将

数据写入载入寄存器 (TL0L, TL0H和TL1L, TL1H) 就可以初

始化Timer。

当高 4位载入寄存器被写入或 Timer 计数值由$FF 到$00 溢出

时

, Timer 将自动载入预设值。

由于寄存器的高 4位控制 Timer 的读写操作, 使用中请根据以

下步骤操作

:

写操作:

先写低四位

再写高四位以更新计数器

读操作:

先读高四位

再读低四位

Load Reg. L

Load Reg. H

8-bit timer counter

Latch Reg. L

7.2. Timer0和Timer1模式寄存器

通过设置

Timer模式寄存器 (T0M, T1M) 可以使Timer工作在不同的模式。

系统时钟经过预分频器分频后, 进入计数器。Timer模式寄存器中的TxM.2-0用于设定分频比。

表 1. Timer0 模式寄存器 ($02)

T0M.2 T0M.1 T0M.0 预分频器分频比 时钟源

0 0 0 /211

0 0 1 /29

0 1 0 /27

0 1 1 /25

1 0 0 /23

1 0 1 /22

1 1 0 /21

1 1 1 /20

系统时钟/T0

系统时钟/T0

系统时钟/T0

系统时钟/T0

系统时钟/T0

系统时钟/T0

系统时钟/T0

系统时钟/T0

表 2. Timer1 模式寄存器 ($03)

T1M.2 T1M.1 T1M.0

预分频器分频

0 0 0 /211

0 0 1 /29

0 1 0 /27

0 1 1 /25

1 0 0 /23

1 0 1 /22

1 1 0 /21

1 1 1 /20

比

时钟源

系统时钟/2.048kHz

系统时钟/2.048kHz

系统时钟/2.048kHz

系统时钟/2.048kHz

系统时钟/2.048kHz

系统时钟/2.048kHz

系统时钟/2.048kHz

系统时钟/2.048kHz

22

SH69P55A/K55A

Timer0 的时钟源则通过下述控制寄存器选择:

系统寄存器:

地址

第3位 第2位 第1位 第0位 读/写

$02 T0S - - -

0 X X X

1 X X X

系统寄存器:

地址

第3位 第2位 第1位 第0位 读/写

$03 T0E - - -

0 X X X

1 X X X

系统寄存器:

地址

第3位 第2位 第1位 第0位 读/写

$3C0 T1S - - - R/W

0 X X X R/W

1 X X X R/W

读/写

读/写

读/写

读/写

读/写

读/写

说明

第

3 位: T0 信号源选择寄存器

Timer0 时钟源为系统时钟

Timer0 时钟源为 T0 引脚输入脉冲

说明

第

3 位: T0 信号沿选择寄存器

T0 输入由高电平到低电平变化时计数

T0 输入由低电平到高电平变化时计数

说明

第 3 位: T1 信号源选择寄存器*

Timer1

Timer1

信号源为系统时钟*

信号源为 2.048kHz*

*: 当振荡器类型选择 32.768kHz 时,T1S 寄存器有效。否则,T1S 寄存器清零。

7.3. 外部时钟/事件 T0 作为 Timer0 的时钟源

当外部时钟

/事件 T0 输入作为 Timer0 的时钟源时, 它由 CPU 的系统时钟进行同步。这个外部信号源必须符合以下条件:

Timer 在一个指令周期中通过系统时钟进行采样, 因此对外部时钟高电平 (至少 2 tOSC) 和低电平 (至少 2 tOSC) 的要求如下:

T0H (T0

T0L (T0

高电平时间) ≥ 2 * tOSC + ∆T

低电平时间) ≥ 2 * tOSC + ∆T ; ∆T = 20ns

当选择其它的分频比时, T0M 通过异步脉冲计数器来分频, 且预分频器的输出信号是对称的。

:

那么

T0 * N

timelow T0 time high T0 ==

2

其中: T0 = Timer0 输入周期

预分频值

N =

因此, 需要满足的条件是:

T0*N

2

OSC ∆+≥

Tt*2

或

T0

OSC ∆+

≥

T*2t*4

N

上述条件仅限于 T0 用作 Timer 输入时钟源, 对 T0 脉宽没有限制。概括如下:

OSC ∆+

period Timer0T0

≥=

T *2t*4

N

23

SH69P55A/K55A

7.4. Timer2

16 位 Timer 有下述特性:

- 16

位递增计数

-

自动重载

- 8

级预分频

-

计数值由$FFFF 到$0000 时, 产生溢出中断请求。

Timer 框图:

System

clock

T2

MUX

EOR

OSC SYNC

t

Prescaler

16-BIT

COUNTER

当高 4 位载入寄存器被写入或Timer 计数值由$FFFF到$0000

溢出时, Timer 将自动载入预设值。

由于寄存器的高 4位控制 Timer 的读写操作, 使用中请根据以

下步骤操作

:

写操作:

先写低四位

再写高四位以更新计数器

读操作:

先读高四位

再读低四位

T2E

TMS1

Timer

功能:

-

可编程定时功能

-

计数值可读

7.5. Timer2 结构和操作

Timer2 由一个 16 位只写载入寄存器 (TL2L, TL2ML, TL2MH,

TL2H)

和一个 16 位只读计数器 (TC2L, TC2ML, TC2MH,

TC2H)

构成。每个计数器由低四位和高四位组成。将数据写

TMS0

SC.2 SC.0

SC.1

Load Reg. L

16-bit timer counter

Latch Reg. L Latch Reg. H

Load Reg. H

入载入寄存器 (TL2L, TL2ML, TL2MH, TL2H) 就可以初始化

Timer。

7.6. Timer2 控制寄存器

Timer2 可工作在不同的模式: 定时器模式, 外部事件计数器模式, 外部触发定时器模式和脉冲宽度测量模式。

Timer2 控制寄存器: $27

地址 第 3 位 第 2 位 第 1 位 第 0 位 读/写 说明

第

$27 T2GO DEC TM2S1 TM2S0

读/写

1-0 位: Timer2 模式选择寄存器

第 3 位: Timer2 功能启动控制寄存器

X X 0 0 读/写 定时器模式

X X 0 1 读/写 外部事件计数器模式 (T2 引脚输入)

X X 1 0 读/写 外部触发定时器模式 (T2 引脚输入)

X X 1 1 读/写 脉冲宽度测量模式 (T2 引脚输入)

0 X X X 读/写 定时器/计数器停止 (读: 状态; 写: 命令) (默认)

1 X X X 读/写 定时器/计数器开启 (读: 状态; 写: 命令)

24

SH69P55A/K55A

(1) 定时器模式

在此模式下

, Timer2 用内部系统时钟进行计数。当 Timer2 载入寄存器最高位 ($387) 被写入数据时, CPU 将 Timer2 载入寄存器

($384 - $387) 载入递增计数器。如果设置 Timer2 控制寄存器 ($27) T2GO (bit3) 为 1 时, 递增计数器将开始计数。假如中断允

许寄存器

($00) IET2 (bit1)为 1, 当递增计数器从 FFFF 到 0000 溢出, 将产生 Timer2 中断。

当 Timer2 控制寄存器 ($27) T2GO (bit3) 已经被设置成 1 之后, 写 Timer2 载入寄存器 ($384 - $387) 不会再影响递增计数器

的工作。只有 Timer2 控制寄存器 ($27) T2GO (bit3) 被清 0 后, 此时 Timer2 载入寄存器最高位 ($387) 被写入数据时, CPU 才

会将 Timer2 载入寄存器 ($384 - $387) 载入递增计数器。

Timer2 预分频器: $15

地址 第 3 位 第 2 位 第 1 位 第 0 位 读/写 说明

第

$15 T2E T2SC.2 T2SC.1 T2SC.0

X 0 0 0

X 0 0 1

X 0 1 0

X 0 1 1

X 1 0 0

X 1 0 1

X 1 1 0

X 1 1 1

0 X X X

1 X X X

读/写

读/写

读/写

读/写

读/写

读/写

读/写

读/写

读/写

读/写 T2 输入由高电平到低电平变化时计数

读/写 T2 输入由低电平到高电平变化时计数

2-0 位: Timer2 预分频器分频比选择寄存器

第 3 位: T2 外部信号沿选择寄存器

Timer2 时钟源: fOSC/213

Timer2 时钟源: fOSC/211

Timer2 时钟源: fOSC/29

Timer2 时钟源: fOSC/27

Timer2 时钟源: fOSC/25

Timer2 时钟源: fOSC/24

Timer2 时钟源: fOSC/23

Timer2 时钟源: fOSC/22

(2) 外部事件计数器模式

在此模式下

, Timer2 对 T2 引脚 (PORTG.3) 的外部时钟输入进行计数。Timer2 的预分频器 ($15) T2E (bit3) 可以选择外部输入

时钟是上升沿有效还是下降沿有效。当 Timer2 载入寄存器最高位 ($387) 被写入数据时, CPU 将 Timer2 载入寄存器 ($384 -

$387)

载入递增计数器。如果设置 Timer2 控制寄存器 ($27) T2GO (bit3) 为 1, 递增计数器将开始计数。假如中断允许寄存器

($00) IET2 (bit1) 为 1, 当递增计数器从 FFFF 到 0000 溢出, 将产生 Timer2 中断。

当 Timer2 控制寄存器 ($27) T2GO (bit3) 已经被设置成 1 之后, 写 Timer2 载入寄存器 ($384 - $387) 不会再影响递增计数器

的工作。只有

Timer2 载入寄存器 ($384 - $387) 载入递增计数器。

会将

Timer2 控制寄存器 ($27) T2GO (bit3) 被清 0 后, 此时 Timer2 载入寄存器最高位 ($387) 被写入数据时, CPU 才

外部时钟源符合如下条件: Timer 在一个指令周期中通过系统时钟进行采样, 因此对外部时钟必须要维持高电平至少 2 个 tOSC 和

低电平至少

频器里面的值。所以

2 个 tOSC。在此模式下, 预分频器电路不会影响外部时钟输入。也就是说, 输入时钟将绕过预分频器电路, 不管预分

, T2 外部时钟源周期 (TE) 的限制描述如下:

T

E (周期时间) ≥ 4 * tOSC + 2 * ∆T ; ∆T = 20ns

25

SH69P55A/K55A

(3) 外部触发定时器模式

在此模式下

号是上升沿有效还是下降沿有效。但是递增计数器的时钟源还是内部时钟。当

CPU

, 计数由一个 T2 引脚 (PORTG.3) 输入的外部信号触发。Timer2 的预分频器 ($15) T2E (bit3) 可以选择外部输入信

Timer2 载入寄存器最高位 ($387) 被写入数据时,

将 Timer2 载入寄存器 ($384 - $387) 载入递增计数器。如果设置 Timer2 控制寄存器 ($27) T2GO (bit3) 为 1, 此时, T2

输入引脚上的适当边沿信号会触发递增计数器将开始计数。假如中断允许寄存器 ($00) IET2 (bit1) 为 1, 当递增计数器从 FFFF

到 0000 溢出, 将产生 Timer2 中断。当 Timer2 中断产生时, 递增计数器被暂停。递增计数器由 T2 输入引脚上的有效边沿信号

重启。

当在 Timer2 控制寄存器 ($27) 内的 DEC (bit2) 为 1 时, T2 输入引脚上的有效上升沿 (下降沿) 开始计数, T2 输入引脚上的下

降沿

(上升沿) 会使计数器停止计数, 并且将 Timer2 载入寄存器 ($384 - $387) 重新载入递增计数器。输入适当的宽度的脉冲

才能产生中断。当在 Timer2 控制寄存器 ($27) 内的 DEC (bit2) 为 0 时, 非有效边沿输入将被忽视, 递增计数器溢出之前, T2

输入的有效边沿也会被忽视。

当 Timer2 控制寄存器 ($27) T2GO (bit3) 已经被设置成 1 之后, 写 Timer2 载入寄存器 ($384 - $387) 不会再影响递增计数器

的工作。只有 Timer2 控制寄存器 ($27) T2GO (bit3) 被清 0 后, 此时 Timer2 载入寄存器最高位 ($387) 被写入数据时, CPU 才

会将 Timer2 载入寄存器 ($384 - $387) 载入递增计数器。

T2 引脚输入信号符合以下条件: 系统时钟在每一个指令周期采样外部触发信号, 因此外部触发信号必须要维持高电平至少 1/2

t

Timer clock 或者低电平 1/2 tTimer clock。在此模式下, Timer2 时钟的实际值由 Timer2 预分频寄存器来选择。所以, 外部触发信号

的周期时间 (TE) 的限制描述如下:

T

E (周期时间) ≥ 1 * tTimer clock + 2 * ∆T ; ∆T = 20ns

T

E (周期时间) ≥ ( M * tOSC) + 2 * ∆T

此处 M = 2

3

, 24, 25, 26, 28, 210, 2

12

14

或 2

Timer2 控制寄存器$27 (在外部触发定时器模式下)

地址 第 3 位 第 2 位 第 1 位 第 0 位 读/写 说明

$27 T2GO DEC TM2S1 TM2S0

X 0 1 0

X 1 1 0

读/写 第 1-0 位: Timer2 模式选择寄存器

读/写 忽视逆向边沿输入

读/写 逆向边沿输入使内部递增计数器重载

Timer2 预分频寄存器$15 (在外部触发定时器和脉冲宽度测量模式下)

地址 第 3 位 第 2 位 第 1 位 第 0 位 读/写 说明

第

$15 T2E T2SC.2 T2SC.1 T2SC.0 读/写

X 0 0 0

X 0 0 1

X 0 1 0

X 0 1 1

X 1 0 0

X 1 0 1

X 1 1 0

X 1 1 1

0 X X X

1 X X X

读/写 Timer2 时钟源: fOSC/2

读/写 Timer2 时钟源: fOSC/2

读/写 Timer2 时钟源: fOSC/2

读/写 Timer2 时钟源: fOSC/2

读/写 Timer2 时钟源: fOSC/2

读/写 Timer2 时钟源: fOSC/2

读/写 Timer2 时钟源: fOSC/2

读/写 Timer2 时钟源: fOSC/2

读/写 T2 输入下降沿有效 (默认)

读/写 T2 输入上升沿有效

2-0 位: Timer2 预分频器分频比选择寄存器

第 3 位: T2 外部信号沿选择寄存器

14

12

10

8

6

5

4

3

Timer2 载入/计数寄存器$384 - $387

地址 第 3 位 第 2 位 第 1 位 第 0 位 读/写 说明

$384 T2D.3 T2D.2 T2D.1 T2D.0

$385 T2D.7 T2D.6 T2D.5 T2D.4

$386 T2D.11 T2D.10 T2D.9 T2D.8

$387 T2D.15 T2D.14 T2D.13 T2D.12

读/写 Timer2 载入/计数器寄存器低位

读/写 Timer2 载入/计数器寄存器中低位

读/写 Timer2 载入/计数器寄存器中高位

读/写 Timer2 载入/计数器寄存器高位

26

T2

Internal clock

SH69P55A/K55A

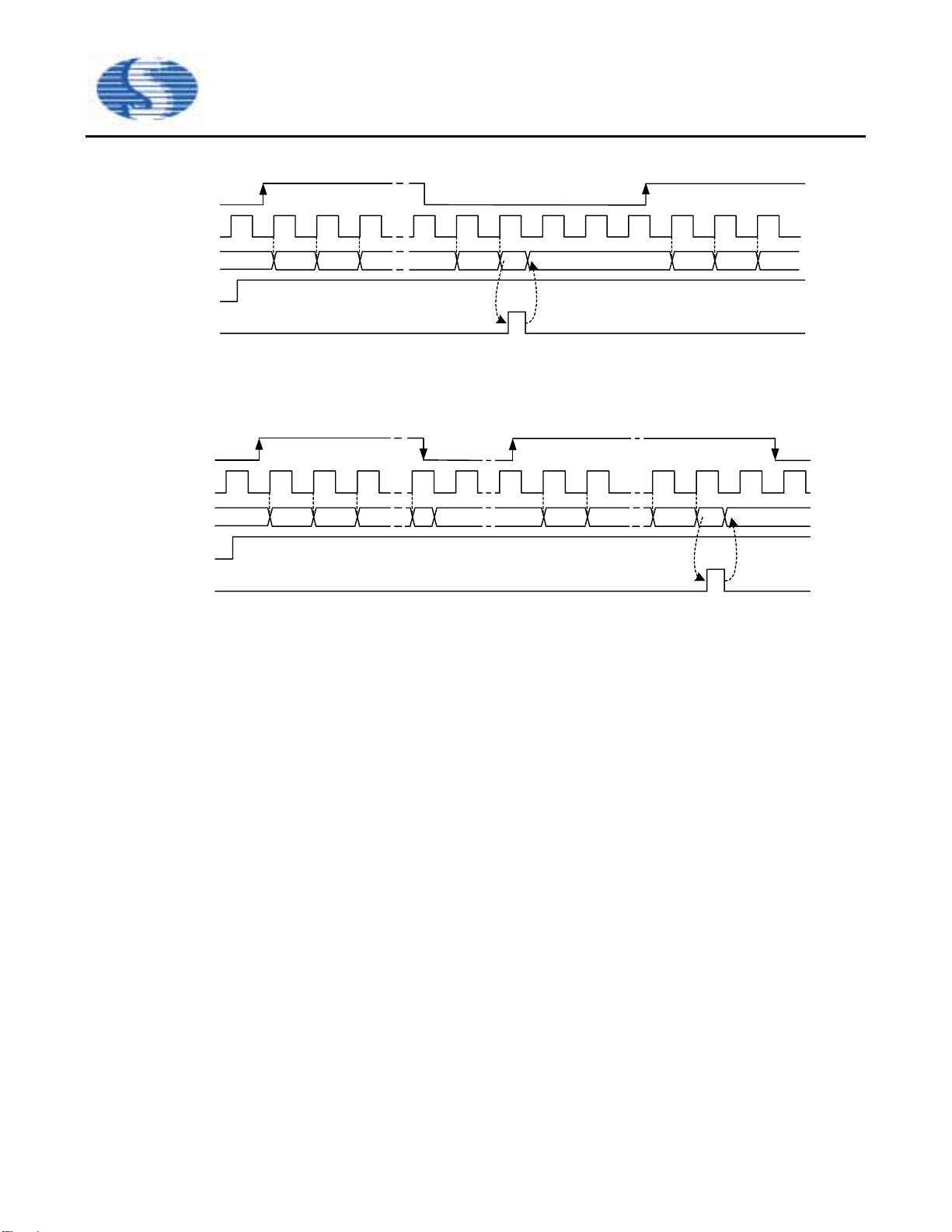

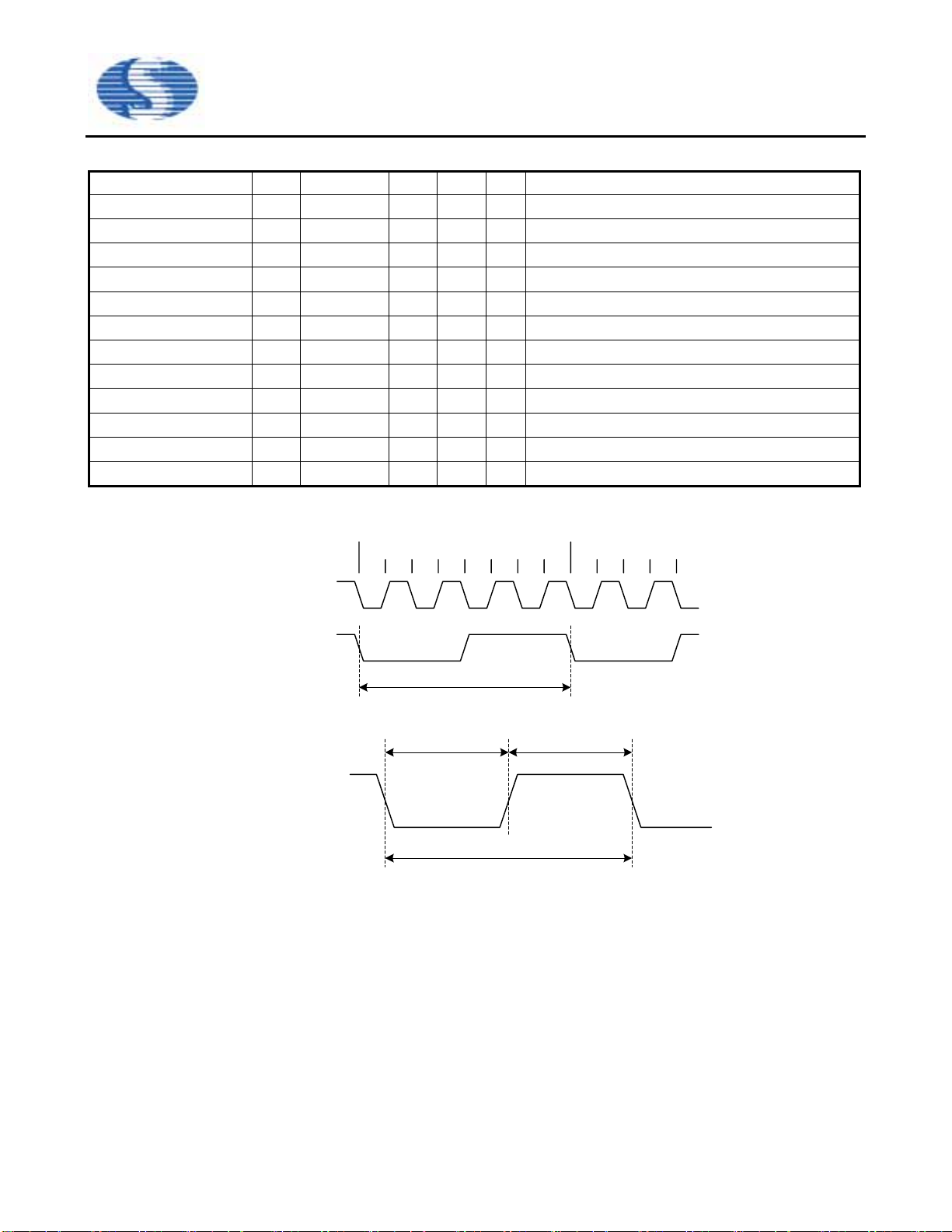

Count start Count start

Up-counter

T2GO

Timer2 INT

FF9E FFFFFF9C FF9D 00 FF9C FF9D FF9FFF9E

Trigger Start (DEC = 0)

Count start

F060

T2

Internal clock

Up-counter

T2GO

Timer2 INT

Count start

Count relooad

F062 M - 1F060 F061 00F061 F062 FFFF F060

M

Trigger Start and Stop (DEC = 1)

(4) 脉冲宽度测量模式

这种模式是

Timer2 在计数器模式下使用的一种特殊功能, 计数开始于 T2 输入引脚上脉冲波形的一个有效边沿。当输入 T2 引脚

的状态发生变化时, 可以通过读取递增计数器的值来测量脉冲波形宽度。设置 Timer2 预分频寄存器 ($15) 中的 T2E (bit3) 来选

择 T2 引脚输入的有效上升沿或下降沿。但是, 递增计数器的时钟源是通过设置 Timer2 预分频寄存器 ($15) 的 T2M (Bit2-Bit0)

来选择的一个内部时钟。当 Timer2 控制寄存器 ($27) 的 T2GO (Bit3) 设置为 1 时, 递增计数器的内容被自动重置为“0000H”。

T2 输入引脚的一个上升 (下降) 沿信号会触发递增计数器开始计数。在下一个下降 (上升) 沿, 计数值被单独载入 Timer2

然后在

载入寄存器。与此同时, 如果中断允许寄存器 ($00) IET2 (Bit1) 设置为 1, Timer2 会产生中断。

当 Timer2 控制寄存器 ($27) DEC (Bit2) 为 0 时, Timer2 工作在单沿捕捉状态下。如果选择上升沿作为计数器触发信号, 在下一

个下降沿

, Timer2 会产生中断请求。与此同时, 递增计数器的内容被载入 Timer2 载入寄存器 ($384 - $387), 然后在计数器暂停,

递增计数器被清零。当下 T2 引脚输入下一个上升沿时, 递增计数器开始为另一个测量周期的计数。

当 Timer2 控制寄存器 ($27) 的 DEC (Bit2) 在为 1 时, Timer2 工作在双沿捕捉状态下。如果上升沿被选择作为计数器触发信号,

在下一个下降沿, Timer2 会产生中断请求。与此同时, 递增计数器的容量内容被载入 Timer2 载入寄存器 ($384 - $387), 然后计

数器继续计数。当

T2 引脚输入下一个上升沿时, Timer2 也会产生中断请求。在这个时候, 递增计数器的值再一次被载入 Timer2

载入寄存器 ($384 - $387), 然后递增计数器被清 0 并且在测量周期内继续计数。

在此模式下, 在任何时候写入 Timer2 载入寄存器 ($384 - $387) 都不会再影响递增计数器的工作。

在此模式下, T2 引脚输入脉冲信号必须符合以下条件。脉冲信号周期 TE 的限制描述如下:

T

E (周期时间) ≥ 1 * tTimer clock + 2 * ∆T ; ∆T = 20ns

T

E (周期时间) ≥ ( M * tOSC) + 2 * ∆T

27

SH69P55A/K55A

在此 M (对于 Timer2 中断时钟的预分频值) = 2

3

, 24, 25, 26, 28, 210, 2

12

14

或 2

但是, 为了在程序运行中得到正确的脉冲宽度测量值, 相应的 Timer2 中断子程序需足够的等待周期。

所以

, 如果在 Timer2 控制寄存器 ($27) DEC (Bit2) 为 0 时, Timer2 为单沿捕捉操作。对于 TE 周期时间的应用限制描述如下:

T

E (周期时间) ≥ 14 * tSystem clock

T

E (周期时间) ≥ 14 * 4 * tOSC

在应用中, 这两个如上所示方程式的最大值有效。

所以, 如果在 Timer2 控制寄存器 ($27) DEC (Bit2) 为 1 时, Timer2 为双沿捕捉操作。对于 T2 输入高或低电平周期时间 (TE) 的

限制描述如下:

T

E (高或低电平周期时间) ≥ 14 * tSystem clock

TE (高或低电平周期时间) ≥ 14 * 4 * tOSC

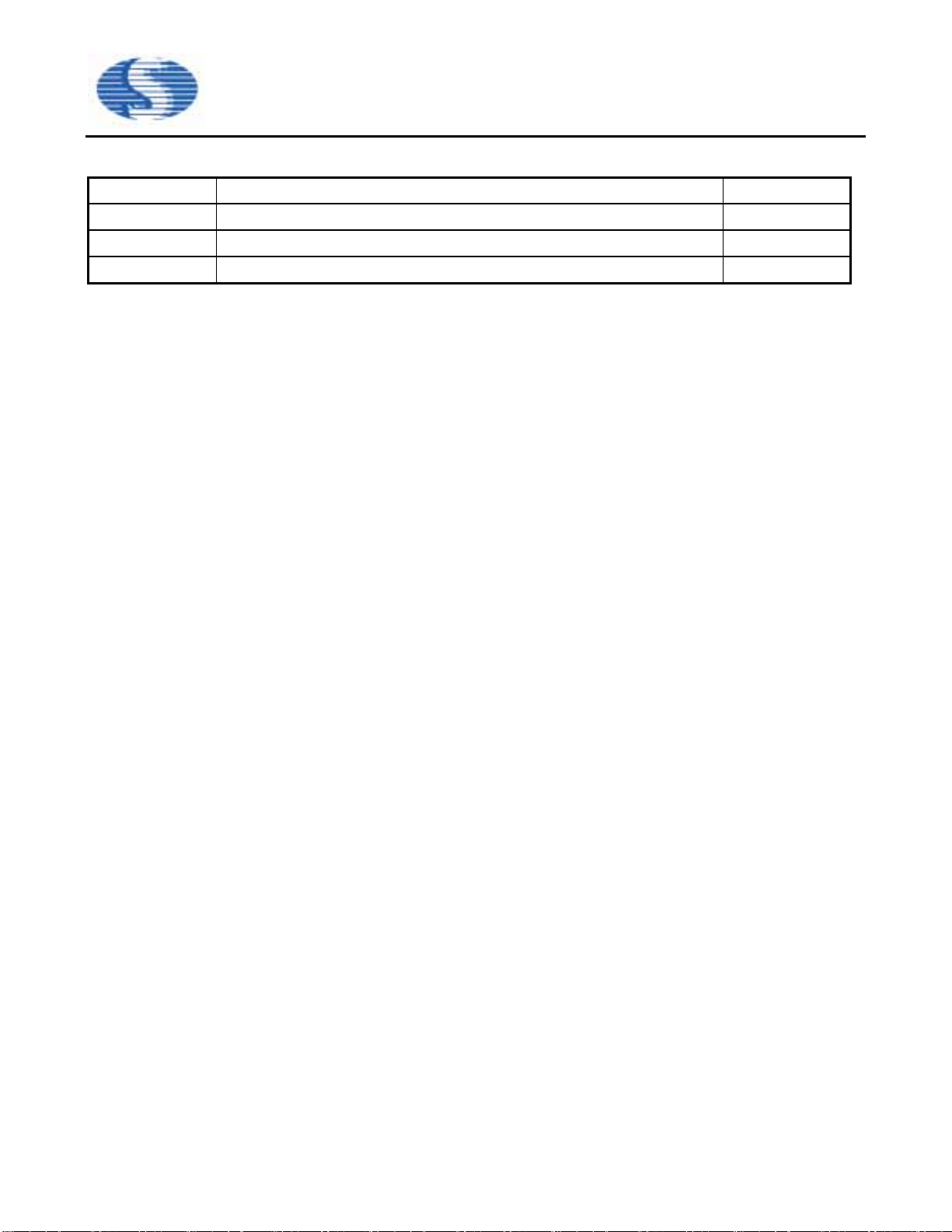

Count start

T2

Internal clock

Up-counter

T2 counter reg. XXXX

Timer2 INT

T2GO

Count start

T2

Internal clock

Up-counter

T2 counter reg. XXXX

Timer2 INT

T2GO

00020000 0001 T

Count start

00020000 0001 N

M

0000

Capture Capture

M

One edge capture (DEC = 0)

Count start

M+1M

Capture Capture

M

0002 N - 1

0001

0001 T - 1 T + 1

0

N

Capture

N

0000

N

T

Double edge capture (DEC = 1)

Timer2 控制寄存器$27 (在脉冲宽度测量模式下)

地址 第 3 位 第 2 位 第 1 位 第 0 位 读/写 说明

第

$27 T2GO DEC TM2S1 TM2S0

X 0 1 1

X 1 1 1

读/写

读/写 设置成单沿捕捉

读/写 设置成双沿捕捉

1-0 位: Timer2 模式选择寄存器

第 2 位: 单/双沿捕捉选择寄存器

28

SH69P55A/K55A

8. 液晶显示 (LCD) 驱动器

LCD

驱动器包含一个控制器, 一个电压发生器, 4-8 COM 驱动器焊垫/引脚和 16-20SEG 驱动器焊垫/引脚。驱动器可编程为三种

驱动模式

控制。当使用 1/4 占空比和1/3 偏置电压模式时, COM8-5被共用为 SEG17-20。当使用1/6 占空比和 1/3 偏置电压模式时, COM8-7

被共用为 SEG17-18。控制器由显示数据 RAM 和占空比发生器组成。

LCD SEG1-20

相同地址 ($08, $0C-$0D, $38F-$390) 的第 3-0 位。LCD COM1-8 可以作为 I/O 端口 (PORTD, PORTE), 通过系统寄存器$29

的第 2 位选择。LCD COM1-6 和 SEG1-8 可以共用为 LED 驱动应用。如果需要, LCD RAM 可以用作数据存储器。

当执行了“STOP”指令后, LCD 驱动器将关闭, 但是 LCD RAM 中的数据将保持不变。

当 LCD 驱动器被关闭时, COM 和 SEG 都输出低电平。

在使用 LCD 驱动器之前, LEDEN 位 (在$2B 中的 Bit3) 必须为“0”。

LCD 控制寄存器: $29

注意:

: 1/4 占空比和 1/3 偏置电压, 1/6 占空比和 1/3 偏置电压和 1/8 占空比和 1/4 偏置电压。驱动模式可通过系统寄存器$29

可以作为输出端口, 通过系统寄存器$2E 的第 2-0 位选择。当 SEG1-20 被选择作为输出端口, 用户应当写数据到

地址 第 3 位 第 2 位 第 1 位 第 0 位 读/写 说明

第

$29 LCDON DUTY2 DUTY1 DUTY0

0 X X X

1 X X X

X 0 X X

X 1 0 0

X 1 0 1

X 1 1 0

X 1 1 1

读/写

读/写 LCD 关闭

读/写 LCD 打开

读/写 PORTD 和 PORTE 作为 I/O 端口

读/写 设置 1/4 占空比。PORTD.3 - 0 作为 COM1 - 4, PORTE 作为 I/O

读/写 设置 1/4 占空比。PORTE.3 - 0 作为 COM5 - 8, PORTD 作为 I/O

读/写

读/写

2-0 位: 占空比和 COM 设置寄存器

第 3 位: LCD 打开设置寄存器

设置

1/6 占空比。PORTD.3 - 0 作为 COM1 - 4, PORTE3 - 2 作为

COM5 - 6, PORTE1 - 0 作为 I/O

1/8 占空比。PORTD.3 - 0 作为 COM1 - 4, PORTE3 - 0 作为

设置

COM5 - 8

1.如果 $3C1≠0000B, $3C1 寄存器控制 LCD 帧频.

COM FOSC 代码选项 Osc 范围 LCD 帧频

00 4M-8M fosc/(20480*(LPS+1))

01 2M-4M fosc/(10240*(LPS+1))

4

10 1M-2M fosc/(5120*(LPS+1))

11 400k-1M fosc/(2560*(LPS+1))

xx 32.768k fosc/(160*(LPS+1))

00 4M-8M fosc/(28672*(LPS+1))

01 2M-4M fosc/(14336*(LPS+1))

6

10 1M-2M fosc/(7168*(LPS+1))

11 400k-1M fosc/(3584*(LPS+1))

xx 32.768k fosc/(224*(LPS+1))

00 4M-8M fosc/(36864*(LPS+1))

10 2M-4M fosc/(18432*(LPS+1))

8

01 1M-2M fosc/(9216*(LPS+1))

11 400k-1M fosc/(4608*(LPS+1))

xx 32.768k fosc/(288*(LPS+1))

*: LPS=LPS3~LPS0

29

SH69P55A/K55A

COM1COM1

下表为推荐设置:

OSC

CLK

8M 00 05H 36 07H 35 0AH 35

7M 00 04H 38 06H 35 0BH 34

6M 00 03H 40 05H 35 07H 36

5M 00 03H 33 04H 35 06H 35

4.0001M 00 02H 36 03H 35 04H 39

4M 01 05H 36 07H 35 0AH 35

3M 01 03H 40 05H 35 07H 36

2.0001M 01 02H 36 03H 35 04H 39

2M 10 05H 36 07H 35 0AH 35

1.0001M 10 02H 36 03H 35 04H 39

1M 11 05H 36 07H 35 0AH 35

500k 11 02H 36 03H 35 04H 39

OTP

选项

代码

LPS

ONE FRAME

LCD 输出帧信号

8COM

F

LCD(Hz)

LPS

6COM

FLCD(Hz)

LPS

4COM

FLCD(Hz)

32.768k xx 02H 38 03H 36 05H 34

2. 如果$3C1=0000B ,LCD 时钟从 OSC 分频, 所以 LCD 帧频将随着 OSC 频率和 FOSC 代码选项的变化而做出相应的变化。

(

具体请参考第 56 页)

COM FOSC 代码选项 LCD 帧频 Osc 范围 举例

00 fosc/40,960 4M-8M fOSC = 4M, fLCD = 97.5Hz

01 fosc/20,480 2M-4M fOSC = 2M, fLCD = 97.5Hz

4

10 fosc/10,240 1M-2M fOSC = 1M, fLCD = 97.5Hz

11 fosc/5,120 400k-1M fOSC = 500k, fLCD = 97.5Hz

xx fosc/320 32.768k f

OSC = 32.768k, fLCD = 102.4Hz

00 fosc/57,344 4M-8M fOSC = 4M, fLCD = 69.5Hz

01 fosc/28,672 2M-4M fOSC = 2M, fLCD = 69.5Hz

6

10 fosc/14,336 1M-2M fOSC = 1M, fLCD = 69.5Hz

11 fosc/7,168 400k-1M fOSC = 500k, fLCD = 69.5Hz

xx fosc/448 32.768k f

OSC = 32.768k, fLCD = 73Hz

00 fosc/73,728 4M-8M fOSC = 4M, fLCD = 54Hz

10 fosc/36,864 2M-4M fOSC = 2M, fLCD = 54Hz

8

01 fosc/18,432 1M-2M fOSC = 1M, fLCD = 54Hz

11 fosc/9,216 400k-1M fOSC = 500k, fLCD = 54Hz

xx fosc/576 32.768k f

OSC = 32.768k, fLCD = 57Hz

30

SH69P55A/K55A

3. SH69P55A/69K55A 有 LCD 驱动器和 LED 驱动器, 同一时间只有一个有效。 如果 LEDEN = 1, LCD 驱动器被禁止; 如果

LEDEN = 0, LED 驱动器被禁止。

SEG 配置寄存器: $2E

地址 第 3 位 第 2 位 第 1 位 第 0 位 读/写 说明

2-0 位: SEG 配置寄存器 (请参考下表)

$2E RLCD PS2 PS1 PS0 读/写

PS2 PS1 PS0 PE.3 PE.2 PE.1 PE.0 PH.3 PH.2 PH.1 PH.0 PI.3 PI.2 PI.1 PI.0 PF.3 PF.2 PF.1 PF.0 PA.3 PA.2 PA.1 PA.0

0 0 0 I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O

0 0 1 I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O S5 S4 S3 S2 S1

0 1 0 I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O S6 S5 S4 S3 S2 S1

0 1 1 I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O S7 S6 S5 S4 S3 S2 S1

1 0 0 I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O S8 S7 S6 S5 S4 S3 S2 S1

1 0 1 I/O I/O I/O I/O I/O I/O I/O I/O S12 S11 S10 S9 S8 S7 S6 S5 S4 S3 S2 S1

1 1 0 I/O I/O I/O I/O S16 S15 S14 S13 S12 S11 S10 S9 S8 S7 S6 S5 S4 S3 S2 S1

1 1 1 S20 S19 S18 S17 S16 S15 S14 S13 S12 S11 S10 S9 S8 S7 S6 S5 S4 S3 S2 S1

第

第 3 位: LCD 偏置电阻设置寄存器

*Sx = SEGx

如果 PORTE3 - 0 共用为 COM5 - 8 的 LCD 显示, 那么 PORTE0 - 3 不能共用为 SEG20 - 17。

在 LCD 打开前请正确配置 SEGs 和 COMs。

LCD RAM 配置: (1/4 占空比, 1/3 偏置, 4COM X 20SEG, COM 用 COM1 - 4, SEG 用 SEG1 - 20)

第 3 位

地址

第 2 位 第 1 位 第 0 位 第 3 位 第 2 位 第 1 位 第 0 位

COM4 COM3 COM2 COM1

地址

COM4 COM3 COM2 COM1

$300 SEG1 SEG1 SEG1 SEG1 $30A SEG11 SEG11 SEG11 SEG11

$301 SEG2 SEG2 SEG2 SEG2 $30B SEG12 SEG12 SEG12 SEG12

$302 SEG3 SEG3 SEG3 SEG3 $30C SEG13 SEG13 SEG13 SEG13

$303 SEG4 SEG4 SEG4 SEG4 $30D SEG14 SEG14 SEG14 SEG14

$304 SEG5 SEG5 SEG5 SEG5 $30E SEG15 SEG15 SEG15 SEG15

$305 SEG6 SEG6 SEG6 SEG6 $30F SEG16 SEG16 SEG16 SEG16

$306 SEG7 SEG7 SEG7 SEG7 $310 SEG17 SEG17 SEG17 SEG17

$307 SEG8 SEG8 SEG8 SEG8 $311 SEG18 SEG18 SEG18 SEG18

$308 SEG9 SEG9 SEG9 SEG9 $312 SEG19 SEG19 SEG19 SEG19

$309 SEG10 SEG10 SEG10 SEG10 $313 SEG20 SEG20 SEG20 SEG20

LCD RAM 配置: (1/4 占空比, 1/3 偏置, 4COM X 16SEG, COM 用 COM5 - 8, SEG 用 SEG1 - 16)

第 3 位

地址

第 2 位 第 1 位 第 0 位 第 3 位 第 2 位 第 1 位 第 0 位

COM8 COM7 COM6 COM5

地址

COM8 COM7 COM6 COM5

$300 SEG1 SEG1 SEG1 SEG1 $308 SEG9 SEG9 SEG9 SEG9

$301 SEG2 SEG2 SEG2 SEG2 $309 SEG10 SEG10 SEG10 SEG10

$302 SEG3 SEG3 SEG3 SEG3 $30A SEG11 SEG11 SEG11 SEG11

$303 SEG4 SEG4 SEG4 SEG4 $30B SEG12 SEG12 SEG12 SEG12

$304 SEG5 SEG5 SEG5 SEG5 $30C SEG13 SEG13 SEG13 SEG13

$305 SEG6 SEG6 SEG6 SEG6 $30D SEG14 SEG14 SEG14 SEG14

$306 SEG7 SEG7 SEG7 SEG7 $30E SEG15 SEG15 SEG15 SEG15

$307 SEG8 SEG8 SEG8 SEG8 $30F SEG16 SEG16 SEG16 SEG16

31

SH69P55A/K55A

LCD RAM 配置: (1/6 占空比, 1/3 偏置, 6COM X 18SEG, COM 用 COM1 - 6, SEG 用 SEG1 - 18)

第 3 位

地址

$300 SEG1 SEG1 SEG1 SEG1 $320 - - SEG1 SEG1

$301 SEG2 SEG2 SEG2 SEG2 $321 - - SEG2 SEG2

$302 SEG3 SEG3 SEG3 SEG3 $322 - - SEG3 SEG3

$303 SEG4 SEG4 SEG4 SEG4 $323 - - SEG4 SEG4

$304 SEG5 SEG5 SEG5 SEG5 $324 - - SEG5 SEG5

$305 SEG6 SEG6 SEG6 SEG6 $325 - - SEG6 SEG6

$306 SEG7 SEG7 SEG7 SEG7 $326 - - SEG7 SEG7

$307 SEG8 SEG8 SEG8 SEG8 $327 - - SEG8 SEG8

$308 SEG9 SEG9 SEG9 SEG9 $328 - - SEG9 SEG9

$309 SEG10 SEG10 SEG10 SEG10 $329 - - SEG10 SEG10

$30A SEG11 SEG11 SEG11 SEG11 $32A - - SEG11 SEG11

$30B SEG12 SEG12 SEG12 SEG12 $32B - - SEG12 SEG12

$30C SEG13 SEG13 SEG13 SEG13 $32C - - SEG13 SEG13

$30D SEG14 SEG14 SEG14 SEG14 $32D - - SEG14 SEG14

$30E SEG15 SEG15 SEG15 SEG15 $32E - - SEG15 SEG15

$30F SEG16 SEG16 SEG16 SEG16 $32F - - SEG16 SEG16

$310 SEG17 SEG17 SEG17 SEG17 $330 - - SEG17 SEG17

$311 SEG18 SEG18 SEG18 SEG18 $331 - - SEG18 SEG18

第 2 位 第 1 位 第 0 位 第 3 位 第 2 位 第 1 位 第 0 位

COM4 COM3 COM2 COM1

地址

- - COM6 COM5

LCD RAM 配置: (1/8 占空比, 1/4 偏置, 8COM X 16SEG, COM 用 COM1 - 8, SEG 用 SEG1 - 16)

第 3 位

地址

$300 SEG1 SEG1 SEG1 SEG1 $320 SEG1 SEG1 SEG1 SEG1

$301 SEG2 SEG2 SEG2 SEG2 $321 SEG2 SEG2 SEG2 SEG2

$302 SEG3 SEG3 SEG3 SEG3 $322 SEG3 SEG3 SEG3 SEG3

$303 SEG4 SEG4 SEG4 SEG4 $323 SEG4 SEG4 SEG4 SEG4

$304 SEG5 SEG5 SEG5 SEG5 $324 SEG5 SEG5 SEG5 SEG5

$305 SEG6 SEG6 SEG6 SEG6 $325 SEG6 SEG6 SEG6 SEG6

$306 SEG7 SEG7 SEG7 SEG7 $326 SEG7 SEG7 SEG7 SEG7

$307 SEG8 SEG8 SEG8 SEG8 $327 SEG8 SEG8 SEG8 SEG8

$308 SEG9 SEG9 SEG9 SEG9 $328 SEG9 SEG9 SEG9 SEG9

$309 SEG10 SEG10 SEG10 SEG10 $329 SEG10 SEG10 SEG10 SEG10

$30A SEG11 SEG11 SEG11 SEG11 $32A SEG11 SEG11 SEG11 SEG11

$30B SEG12 SEG12 SEG12 SEG12 $32B SEG12 SEG12 SEG12 SEG12

$30C SEG13 SEG13 SEG13 SEG13 $32C SEG13 SEG13 SEG13 SEG13

$30D SEG14 SEG14 SEG14 SEG14 $32D SEG14 SEG14 SEG14 SEG14

$30E SEG15 SEG15 SEG15 SEG15 $32E SEG15 SEG15 SEG15 SEG15

$30F SEG16 SEG16 SEG16 SEG16 $32F SEG16 SEG16 SEG16 SEG16

第 2 位 第 1 位 第 0 位 第 3 位 第 2 位 第 1 位 第 0 位

COM4 COM3 COM2 COM1

地址

COM8 COM7 COM6 COM5

32

LCD 电源

SH69P55A/K55A

VLCD

LCD ON

com1

-

com8

seg1

-

seg20

V1

V2

V3

R1

R2

R3

LCD

Power

Supply

Control

Circuit

LCD

common

driver

&

scan

input

LCD

segment

driver

&

scan

output

LCD 偏置电阻选择

SEG 配置寄存器: $2E

地址 第 3 位 第 2 位 第 1 位 第 0 位 读/写 说明

$2E RLCD

- - -

读/写 第 3 位: LCD 偏置电阻设置寄存器

0 X X X 读/写 R1 = R2 = R3 = 90k

1 X X X 读/写 R1 = R2 = R3 = 10k

X X X X 读/写 R1 = R2 = R3 = 3k, 如果 KEYEN = 1

当使用大负载 LCD 面板时, 用户可以通过设置系统寄存器$2E Bit3 的值来增加偏置电流以得到更好的 LCD 显示效果。但是当使

用阻值较小的偏置电阻时将会消耗更多的电流。

当 CPU 在 STOP 模式时, COM1-8 和 SEG1-20 端口输出低电平。

33

SH69P55A/K55A

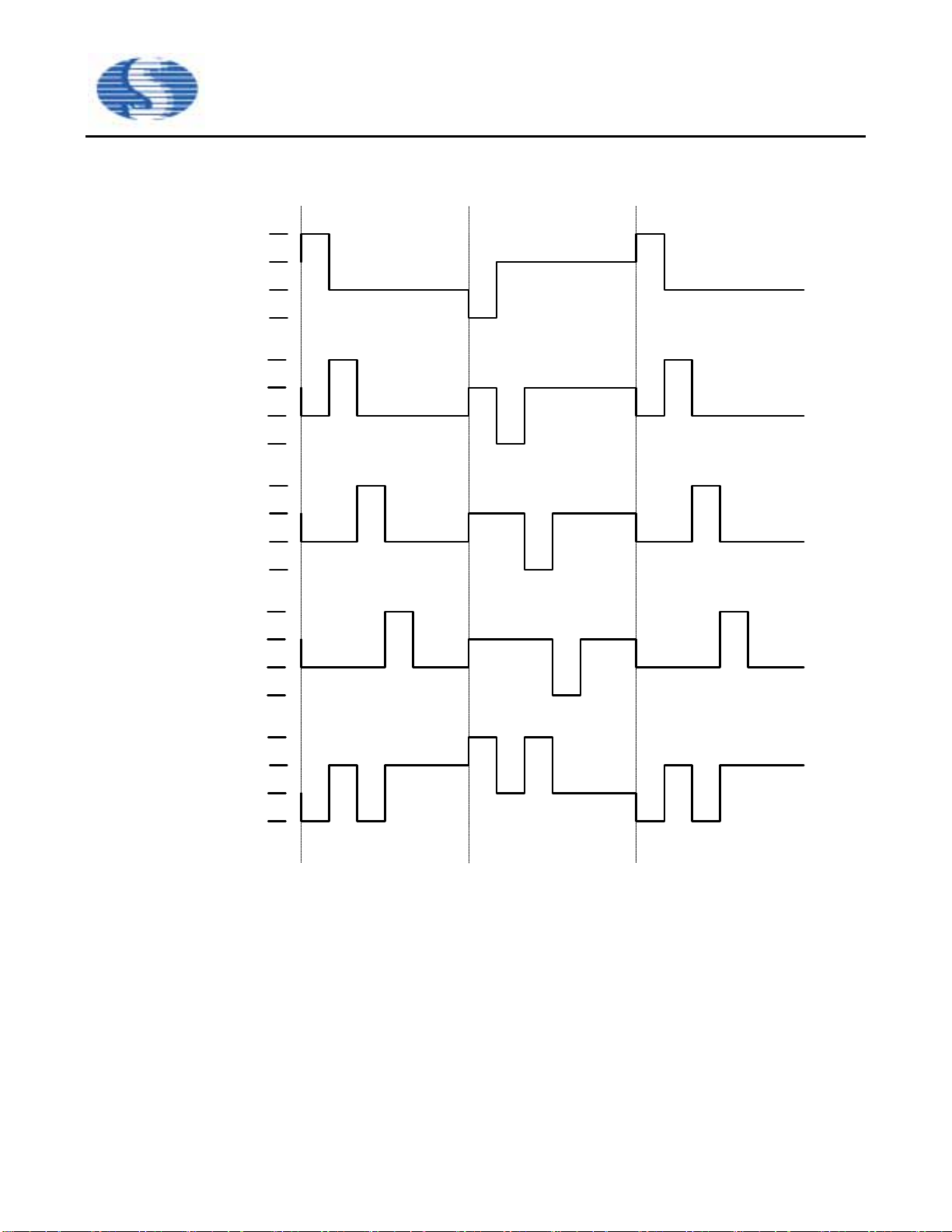

LCD 波形

1/4 占空比, 1/3 偏置 LCD 波形

V1

COM1

COM2

COM3

COM4

V2

V3

GND

V1

V2

V3

GND

V1

V2

V3

GND

V1

V2

V3

GND

V1

SEG

V2

V3

GND

34

SH69P55A/K55A

1/6 占空比, 1/3 偏置 LCD 波形

V1

COM1

COM2

V2

V3

GND

V1

V2

V3

GND

V1

COM3

COM4

SEG

V2

V3

GND

V1

V2

V3

GND

V1

V2

V3

GND

35

SH69P55A/K55A

1/8 占空比, 1/4 偏置 LCD 波形

VDD

V1

COM1

COM2

COM3

V2

V3

GND

VDD

V1

V2

V3

GND

VDD

V1

V2

V3

GND

VDD

V1

SEG

V2

V3

GND

36

SH69P55A/K55A

9. 共用为发光二极管 (LED) 驱动

LED 驱动器包含一个控制器, 一个电压发生器, 4-6 COM 驱动器焊垫/引脚和 8SEG 驱动器焊垫/引脚。驱动器可选择为三种驱动

模式

: 1/4 占空比, 1/5 占空比和 1/6 占空比。驱动模式可通过系统寄存器$2B 控制。控制器由显示数据 RAM 和占空比发生器组成。

LED SEG1-8

bit0-Bit2

内建 LED 驱动器可以直接驱 LED。COM 至少可以接受 200mA 的灌电流。详细信息请参考应用电路。在设置 LED 驱动器之前,

LEDEN (

LED 驱动器占空比控制寄存器: $2B

地址 第 3 位 第 2 位 第 1 位 第 0 位 读/写 说明

$2B LEDEN LEDON EDUTY1 EDUTY0

0 X X X

1 X X X

1 0 X X

1 1 X X

1 X 0 0

1 X 0 1 读/写

1 X 1 0 读/写

1 X 1 1 读/写

可以作为输出端口, 通过系统寄存器$2E 的第 2-0 位选择。当 SEG1-8 被选择作为输出端口, 用户应当写 0 到$2E

。LED COM1 - 6 可以作为 I/O 端口 (PORTD, PORTE), 通过系统寄存器$2B 的第 1-0 位选择。

在$2B 中的 Bit3) 必须设置为 1。

第 1-0 位: 占空比和 COM 设置寄存器

读/写

第 2 位: LED 驱动器设置寄存器

第 3 位: LED 方式选择寄存器

读/写 选择 LCD 模式

读/写 选择 LED 模式

读/写 LED 驱动器关闭

读/写 LED 驱动器打开

读/写 PORTD.3 - 0 和 PORTE.3 - 2 作为 I/O 端口

1/4 占空比, PORTD.3 - 0 作为 COM1 - 4 的 LED

选择

显示和 PORTE.3 - 2 作为正常 I/O

1/5 占空比, PORTD.3 - 0 和 PORTE.3 作为

选择

COM1 - 5

选择

COM1 - 6

的 LED 显示和 PORTE.2 为正常 I/O

1/6 占空比, PORTD.3 - 0 和 PORTE.3 - 2 作为

的 LED 显示

注意:

SH69P55A/69K55A 有 LCD 驱动器和 LED 驱动器, 同一时间只有一个有效。如果 LEDEN = 1, LCD 驱动器禁止; 如果 LEDEN =

0, LED

驱动器禁止。

SEG 配置寄存器: $2E

地址 第 3 位 第 2 位 第 1 位 第 0 位 读/写 说明

$2E RLCD PS2 PS1 PS0 读/写 第 2-0 位: SEG 配置 (请参考下表)

PS2 PS1 PS0 PF3 PF2 PF1 PF0 PA3 PA2 PA1 PA0

0 0 0 I/O I/O I/O I/O I/O I/O I/O I/O

0 0 1 I/O I/O I/O LED_S5 LED_S4 LED_S3 LED_S2 LED_S1

0 1 0 I/O I/O LED_S6 LED_S5 LED_S4 LED_S3 LED_S2 LED_S1

0 1 1 I/O LED_S7 LED_S6 LED_S5 LED_S4 LED_S3 LED_S2 LED_S1

1 0 0 LED_S8 LED_S7 LED_S6 LED_S5 LED_S4 LED_S3 LED_S2 LED_S1

37

SH69P55A/K55A

LED RAM 配置

LED RAM 配置: (1/4 占空比, COM1 - 4, SEG1 - 8)

第 3 位

地址

第 2 位 第 1 位 第 0 位 第 3 位 第 2 位 第 1 位 第 0 位

COM4 COM3 COM2 COM1

地址

COM4 COM3 COM2 COM1

$300 SEG1 SEG1 SEG1 SEG1 $304 SEG5 SEG5 SEG5 SEG5

$301 SEG2 SEG2 SEG2 SEG2 $305 SEG6 SEG6 SEG6 SEG6

$302 SEG3 SEG3 SEG3 SEG3 $306 SEG7 SEG7 SEG7 SEG7

$303 SEG4 SEG4 SEG4 SEG4 $307 SEG8 SEG8 SEG8 SEG8

LED RAM 配置: (1/5 占空比, COM1 - 5, SEG1 - 8)

地址

第 3 位 第 2 位 第 1 位 第 0 位 第 3 位 第 2 位 第 1 位 第 0 位

COM4 COM3 COM2 COM1

地址

- - - COM5

$300 SEG1 SEG1 SEG1 SEG1 $320 - - - SEG1

$301 SEG2 SEG2 SEG2 SEG2 $321 - - - SEG2

$302 SEG3 SEG3 SEG3 SEG3 $322 - - - SEG3

$303 SEG4 SEG4 SEG4 SEG4 $323 - - - SEG4

$304 SEG5 SEG5 SEG5 SEG5 $324 - - - SEG5

$305 SEG6 SEG6 SEG6 SEG6 $325 - - - SEG6

$306 SEG7 SEG7 SEG7 SEG7 $326 - - - SEG7

$307 SEG8 SEG8 SEG8 SEG8 $327 - - - SEG8

LED RAM 配置: (1/6 占空比, COM1 - 6, SEG1 - 8)

地址

第 3 位 第 2 位 第 1 位 第 0 位 第 3 位 第 2 位 第 1 位 第 0 位

COM4 COM3 COM2 COM1

地址

- - COM6 COM5

$300 SEG1 SEG1 SEG1 SEG1 $320 - - SEG1 SEG1

$301 SEG2 SEG2 SEG2 SEG2 $321 - - SEG2 SEG2

$302 SEG3 SEG3 SEG3 SEG3 $322 - - SEG3 SEG3

$303 SEG4 SEG4 SEG4 SEG4 $323 - - SEG4 SEG4

$304 SEG5 SEG5 SEG5 SEG5 $324 - - SEG5 SEG5

$305 SEG6 SEG6 SEG6 SEG6 $325 - - SEG6 SEG6

$306 SEG7 SEG7 SEG7 SEG7 $326 - - SEG7 SEG7

$307 SEG8 SEG8 SEG8 SEG8 $327 - - SEG8 SEG8

LED 波形

COM

SEG

SELECT

SELECT

1/6 DUTY

UNSELECT

SELECT

SELECT

SELECT

VDD

V

GND

DD

COM

SELECT

SELECT

SEG

1/4 DUTY

UNSELECT

SELECT

SELECT

VDD

GND

V

DD

UNSELECT

UNSELECT

UNSELECT

GND

UNSELECT

UNSELECT

GND

38

SH69P55A/K55A

10. 键盘扫描器

SH69P55A/69K55A 内建一个键盘扫描器, 可以自动探测按键。包括 4 个输出 (KEY_O1 - 4 共用为 COM1 - COM4), 5 个输入

(KEY_1 - 5 共用为 SEG1 - SEG5), 可以探测 20 个独立的键。键盘扫描功能是和 LCD 或 LED 的显示驱动电路共用的, 所以必

须选择相应的 LCD 或者 LED 模式下才能工作。

键盘扫描控制寄存器: $28

地址 第 3 位 第 2 位 第 1 位 第 0 位 读/写 说明

第 0 位: 键盘扫描器允许控制寄存器

读/写

第 1 位: 键扫描中止/工作寄存器

只读

第 3 - 2 位: 键盘扫描结果寄存器

读/写 关闭键盘扫描器

读/写 打开键盘扫描器

只读 键扫描结束

只读 键扫描工作

只读 无按键

只读 按键发生

只读 在同一时间一个按键发生

只读 在同一时间多个按键发生

$28

KEYNUM1

KEYNUM0

KEYEND

KEYEN

X X X 0

X X X 1

X X 0 1

X X 1 1

X 0 X 1

X 1 X 1

0 X X 1

1 X X 1

键盘扫描器数据寄存器1: $2C

地址 第 3 位 第 2 位 第 1 位 第 0 位 读/写 说明

$2C KEYC3 KEYC2 KEYC1 KEYC0

0 0 0 1

0 0 1 0

0 1 0 0

1 0 0 0

键盘扫描器数据寄存器2: $2D

地址 第 3 位 第 2 位 第 1 位 第 0 位 读/写 说明

$2D KEYL3 KEYL2 KEYL1 KEYL0

0 0 0 0

0 0 0 1

0 0 1 0

0 1 0 0

1 0 0 0

注意:

1.

如果键盘扫描功能与 LCD 功能共用, LCD 显示必须选择 4com, 6com 或 8com 模式。其中 4com 模式中必须选择 PORTD 作

为 COM 端口 (LCD 控制寄存器$29 bit2-0 能选择作为‘100’, ‘110’和‘111’), 并且 LCD SEG 必须包含 PORTA.0 - 3, PORTF.0

作为 SEG 输出 (SEG 配置寄存器$2E bit2-0 不为‘000’)。

2.

如果键盘扫描功能与 LED 功能共用, LED 显示必须选择 4com, 5com 或 6com (LED 控制寄存器$2B bit1-0 可以为‘01’, ‘10’和

只读 第 3-0 位: 在 KEY_O4 - 1 上的键盘扫描结果寄存器

只读 KEY_O1 上有按键发生

只读 KEY_O2 上有按键发生

只读 KEY_O3 上有按键发生

只读 KEY_O4 上有按键发生

只读 第 3-0 位: 在 KEY_I5 - 1 上的键盘扫描结果寄存器

只读 KEY_I1 上有按键发生

只读 KEY_I2 上有按键发生

只读 KEY_I3 上有按键发生

只读 KEY_I4 上有按键发生

只读 KEY_I5 上有按键发生

‘11’)。LED SEG 必须包含 PORTA.0 - 3, PORTF.0 作为 SEG 输出 (SEG 配置寄存器$2E bit2-0 不为‘000’)。

3.

正确设置情况下, LCD 或 LED 在关闭状态, 自动键盘扫描也是有效的。

任何时间只能有一个按键有效按下, 键盘扫描才能获得正确的键值, 否则将获得不正确的键值。

4.

39

SH69P55A/K55A

11. 模/数转换器 (ADC)

SH69P55A/69K55A 内建有一个 10 通道的 10 位逐次逼近型模/数转换器(ADC)。

ADC 控制寄存器: 这些寄存器定义了模/数转换模拟通道数设置, 转换通道选择, 参考电压选择, 模/数转换时钟选择, 模/数转换

启动控制位和结束标志。模

模/数转换的步骤:

-

设置模拟通道数和选择参考电压。(如果使用外部参考电压, 切记任何模拟输入电压值不能大于 VREF)。

-

运行模/数转换器, 选择需转换的信号通道。

-

设置模/数转换时钟源。

-

置 GO/ DONE= 1, 启动模/数转换。

系统寄存器: (模/数转换端口配置控制寄存器)

/数转换结果寄存器为只读寄存器。

地址 第 3 位 第 2 位 第 1 位 第 0 位 读/写 说明

第

$13 VREFS ACR2 ACR1 ACR0

读/写

2-0 位: 模/数转换端口配置控制寄存器

第 3 位: 内部/外部参考电压选择寄存器

X 0 0 0 读/写 设置模拟通道

0 X X X 读/写 内部参考电压 (VREF = VDD)

1 X X X 读/写 外部参考电压

系统寄存器

地址

$3C2 ACR3 CH3 - - R/W

第3位 第2位 第1位 第0位 读/写

第 2 位: ADC 转换通道选择寄存器

第 3 位: 模/数转换端口配置控制寄存器

1 X - - R/W 设置为模拟通道

X 1 - - R/W ADC 通道控制寄存器

系统寄存器: (模/数转换通道控制寄存器)

地址 第 3 位 第 2 位 第 1 位 第 0 位 读/写 说明

第

$14 ADCON CH2 CH1 CH0

读/写

2-0 位: ADC 转换通道选择寄存器

第 3 位: 设置 ADC 转换允许选择寄存器

0 X X X 读/写 禁止 ADC 工作

1 X X X 读/写 允许 ADC 工作

设置模拟通道

说明

ACR1 ACR0 7 6 5 4 3 2 1 0

ACR2

0 0 0 PJ3 PJ2 PJ1 PJ0 PB3 PB2 PB1 PB0

0 0 1 PJ3 PJ2 PJ1 PJ0 PB3 PB2 PB1 AN0

0 1 0 PJ3 PJ2 PJ1 PJ0 PB3 PB2 AN1 AN0

0 1 1 PJ3 PJ2 PJ1 PJ0 PB3 AN2 AN1 AN0

1 0 0 PJ3 PJ2 PJ1 PJ0 AN3 AN2 AN1 AN0

1 0 1 PJ3 PJ2 PJ1 AN4 AN3 AN2 AN1 AN0

1 1 0 PJ3 PJ2 AN5 AN4 AN3 AN2 AN1 AN0

1 1 1 AN7 AN6 AN5 AN4 AN3 AN2 AN1 AN0

注意:

模拟通道和

果用户使用音频功能,

PORTG.3 和 PORTG.1 共用. 也和 T2 输入口,音频输出共用。如果用户使用 T2 输入功能,ACR3 必须清零。.如

ACR3 – 0 不能为 1xx1B

40

ADC 通道控制

SH69P55A/K55A

CH3 CH2 CH1 CH0

通道 AN0

0 0 0 0

ADC

0 0 0 1 ADC 通道 AN1

ADC

ADC

ADC

ADC

ADC

ADC

ADC

ADC

通道 AN2

通道 AN3

通道 AN4

通道 AN5

通道 AN6

通道 AN7

通道 AN8

通道 AN9

0 0 1 0

0 0 1 1

0 1 0 0

0 1 0 1

0 1 1 0

0 1 1 1

1 x x 0

1 x x 1

系统寄存器: (模/数转换结果寄存器)

地址 第 3 位 第 2 位 第 1 位 第 0 位 读/写 说明

$3AD - - A1 A0

$3AE A5 A4 A3 A2

$3AF A9 A8 A7 A6

只读 ADC 数据低位寄存器

只读 ADC 数据中位寄存器

只读 ADC 数据高位寄存器

说明

系统寄存器: (模数转换控制寄存器)

地址 第 3 位 第 2 位 第 1 位 第 0 位 读/写 说明

2-1 位: 模/数转换时间选择寄存器

$2F

GO/

DONE

TADC1 TADC0 -

X 0 0 X

X 0 1 X

X 1 0 X

X 1 1 X

0 X X X

1 X X X 读/写

第

读/写

第 3 位: ADC 启动/状态标志寄存器

读/写 模/数转换时间 = 13 tOSC*

读/写 模/数转换时间 = 52 tOSC*

读/写 模/数转换时间 = 208 tOSC*

读/写 模/数转换时间 = 416 tOSC*

读/写 模/数转换完成或者没有进行

‘1’启动模/数转换, 转换过程中保持 GO/DONE = 1

置

*: 此处 tOSC 表示时钟源频率, 也就是说, 当使用 PLL 为时钟源时, tOSC 表示 PLL 频率, 当不使用 PLL 时, tOSC 表示振荡器频率。

41

SH69P55A/K55A

CH2:CH0

000

001

010

011

100

101

110

111

A/D Coverter

VDD

V

REF

PORTG.2

/V

REF

VREFS

Input voltage

模/数转换器示意图

注意:

-

正确选择模/数转换时间, 保证模/数转换时间≥25µs。

-

当完成模/数转换后, 将产生模/数转换中断 (如果模/数转换器中断允许)。

模拟输入通道必须将其对应的 PXCR (X = B, J) 位设置为输入。

-

-

如果 I/O 端口已被选择为模拟输入端, 那么 I/O 功能和上拉电阻被禁止。

-

当模/数转换完成后, GO/ DONE 位由硬件自动清零。

-

在转换过程中将 GO/ DONE位清零会中止当前的转换过程。

尚未完成转换过程而将 GO/ DONE位清零的模/数转换将不会更新模/数转换结果寄存器内容。

-

-

在下一个模数转换开始之前需要等待 4tosc 的时间。

- ADC

能在 HALT 方式下继续工作, 但在执行 STOP 指令后自动停止工作。

- ADC

能将 CPU 从 HALT 方式下唤醒 (如果 ADC 中断允许)。

PORTB.0/AN0

PORTB.1/AN1

PORTB.2/AN2

PORTB.3/AN3

PORTJ.0/AN4

PORTJ.1/AN5

PORTJ.2/AN6

PORTJ.3/AN7

42

SH69P55A/K55A

使用注意:

SH69P55A/69K55A A/D 转换器, 在使用外部参考电压时, 需要从 VREF 引脚 (PORTG.2) 输入一定的电流来维持 A/D 的正常转

换。推荐使用图

1, 图 2 的方式建立外部参考电压, 如果 25µs≤A/D 转换时间≤50µs, 可以在 VREF 和 GND 之间加一个 10µF

电解电容来提供 A/D 转换时 VREF 引脚的输入电流 (图 3)。按照图 4 所示方法也可以建立外部参考电压, 但是该方法会使整个系

统的功耗显著增加 (VDD = 5.0V, R1+R2 = 500Ω, 增加约 10mA) (所有图中虚线框部分为 0.1µF 滤波电容, 加上此电容可以减少

VREF 引脚上的干扰)

VDD

VDD

R1

R2

VDD

VDD

2k

REF

V

GND

SH69P55

/69K55

图 1. 图 2.

VDD

VDD

SH69P55

V

REF

/69K55

R1

R2

VDD

REF

V

GND

VDD

V

REF

SH69P55

/69K55

SH69P55

/69K55

GND

GND

图 3. (R1+R2≧50kΩ) 图 4. (R1+R2≦500Ω)

43

SH69P55A/K55A

12. 脉冲宽度调制 (PWM)

SH69P55A/69K55A 包含一个 8+2 位 PWM 模块。PWM 模块可以产生周期和占空比分别可以调整的脉宽调制波形。PWM 模块

的工作模式由

来设置。

系统寄存器$20: PWM 控制寄存器 (PWMC)

PWMC 寄存器来设置。PWM 输出的周期由 PWMP 寄存器来设置。而 PWM 输出波形的占空比由 PWMD 寄存器

地址 第 3 位 第 2 位 第 1 位 第 0 位 读/写 说明

第 0 位: PWM 输出允许设置寄存器

读/写

$20 PWMS TCK1 TCK0 PWM_EN

第 2-1 位: PWM 时钟选择寄存器

第 3 位: PWM 占空比的输出模式设置寄存器

X X X 0 读/写 PWM 功能关闭

X X X 1 读/写 PWM 功能打开

X 0 0 X 读/写 PWM 时钟 = tOSC*

X 0 1 X 读/写 PWM 时钟 = 2 tOSC*

X 1 0 X 读/写 PWM 时钟 = 4 tOSC*

X 1 1 X 读/写 PWM 时钟 = 8 tOSC*

0 X X X 读/写 PWM 占空比输出普通模式 (高电平有效) (初始值)

1 X X X 读/写 PWM 占空比输出反转模式 (低电平有效)

PWM 输出与 PORTG.0 共用

*:

此处 tOSC 表示系统时钟源频率, 也就是说, 当使用 PLL 为系统时钟源时, tOSC 表示 PLL 频率, 当不使用 PLL 时, tOSC 表示振

荡器频率。

系统寄存器$21 - $22: PWM 周期控制寄存器 (PWMP)

地址 第 3 位 第 2 位 第 1 位 第 0 位 读/写 说明

$21 PP.3 PP.2 PP.1 PP.0 读/写 PWM 周期低位寄存器 (4 位)

$22 PP.7 PP.6 PP.5 PP.4 读/写 PWM 周期高位寄存器 (4 位)

PWM 输出周期 = [PP.7, PP.0] X PWM 时钟。

当[PP.7, PP.0] = 00H, 如果 PWMS 位设置为 0, PWM 输出低电平

当[PP.7, PP.0] = 00H, 如果 PWMS 位设置为 1, PWM 输出高电平

系统寄存器$24 - $26: PWM 占空比控制寄存器 (PWMD)

地址 第 3 位 第 2 位 第 1 位 第 0 位 读/写 说明

$24 - - PDF.1 PDF.0 读/写 PWM 占空比微调寄存器 (2 位)

$25 PD.3 PD.2 PD.1 PD.0 读/写 PWM 占空比低位寄存器 (4 位)

$26 PD.7 PD.6 PD.5 PD.4 读/写 PWM 占空比高位寄存器 (4 位)

PWM 平均输出占空比 = ([PD.7, PD.0] + [PDF.1, PDF.0]/4) X PWM 时钟。

如果[PP.7, PP.0] ≤ [PD.7, PD.0], 当 PWMS 位设置为 0, PWM 输出高电平。

如果[PP.7, PP.0] ≤ [PD.7, PD.0], 如果 PWMS 位设置为 1, PWM 输出低电平。

44

SH69P55A/K55A

系统寄存器$24: PWM 占空比微调寄存器 (PWMDF)

地址 第 3 位 第 2 位 第 1 位 第 0 位 读/写 说明

$24 - - PDF.1 PDF.0

- - 0 0

- - 0 1 读/写

- - 1 0 读/写

- - 1 1 读/写

PWMn clock tPWM

[PDF1, PDF0] = 00B

[PDF1, PDF0] = 01B

01 02 03 7F 80 BF C0

Duty cycle

= 7FH X t

PWM

Duty cycle Duty cycle Duty cycle Duty cycle Duty cycle

01 02 03 7F 80 BF C0 01 02 03 7F 80 BF C0 01 02 03 7F 80 BF C0 01 02 03 7F 80 BF C0

Duty cycle

= 7FH X tPWM

= 7FH X tPWM = 7FH X tPWM = 7FH X tPWM= 80H X tPWM = 80H X tPWM

读/写 第 1-0 位: PWM 占空比微调寄存器

读/写 占空比 = [PD.7, PD0]于周期 0, 1, 2, 3

= [PD.7, PD0]+1 于周期 0

占空比

占空比 = [PD.7, PD0]于周期 1, 2, 3

= [PD.7, PD0]+1 于周期 0, 1

占空比

占空比 = [PD.7, PD0] 于周期 2, 3

= [PD.7, PD0]+1 于周期 0, 1, 2

占空比

占空比 = [PD.7, PD0] 于周期 3

Duty cycle

= 7FH X tPWM

Duty cycle

= 7FH X tPWM = 7FH X tPWM

Duty cycle

[PDF1, PDF0] = 10B

Duty cycle Duty cycle Duty cycle Duty cycle Duty cycle

= 80H X tPWM = 80H X tPWM = 7FH X tPWM = 7FH X tPWM = 80H X tPWM

[PDF1, PDF0] = 11B

Duty cycle Duty cycle Duty cycle Duty cycle Duty cycle

Period Cycle0

= C0H X t

PWM

Period Cycle1

= C0H X t

PWM

[PD7, PD0] = 7FH, [PP7, PP0] = C0H

PWMS = 0

Period Cycle2

= C0H X t

PWM

Period Cycle3

= C0H X t

PWM

= 80H X tPWM= 7FH X tPWM= 80H X tPWM= 80H X tPWM= 80H X tPWM

Period Cycle0

= C0H X t

PWM

8+2 bit PWM 输出波形

编程步骤:

1. 选择 PWM 模块时钟源。

2.

通过写适当的值到 PWM 周期控制寄存器 (PWMP) 设置 PWM 周期: 首先设置低四位, 然后设置高四位。

3.

通过写适当的值到 PWM 占空比控制寄存器 (PWMD) 设置 PWM 占空比: 先设置低四位, 然后设置高四位。

通过写 PWM 控制寄存器 (PWMC) 的 PWMS 位选择 PWM 占空比的输出模式。

4.

5.

为了输出适当的 PWM 波形, 通过写 PWM 控制寄存器 (PWMC) 中的 PWM_EN 位为“1”来允许 PWM 模块工作。

6.

如果 PWM 周期或者占空比需要改变, 操作流程如同步骤 2 或者步骤 3 说明。修改后的重载入计数器的值在下一个周期开始有

效。

45

SH69P55A/K55A

注意:

- 如果选择 PORTG.0 作为 PWM 输出, 其 I/O 功能和上拉电阻将无效。

- PWM

在 HALT 模式下仍能继续工作, 当执行 STOP 指令时自动停止。

01 02 03 04 7D 7E 7F05 80 EF F0 01 02 03 04

PWM clock tPWM

PWM output

(PWMS = 0)

PWM output

(PWMS = 1)

[PP.7, PP.0] = F0H

[PD.7, PD.0] = 7FH

[PDF.1, PDF.0] = 00H

PWM output duty cycle = 7FH X tPWM

PWM output period cycle = F0H X tPWM

PWM 输出

01 02 03 04 05 06 07 08 09 0A 0B0C 0D0E 0F 01 02 03 04 05 06 07 08 09 0A0B 0C 0D01 02 03 04 05 06 07 08

PWM clock tPWM

Write [PP.7, PP.0] = 0DH Write [PD.7, PD.0] = 07H

PWM output

(PWMS = 0)

Duty cycle

PWM

= 06H X t

Period cycle = 0FH X tPWM

Duty cycle

PWM

= 06H X t

Period cycle = 0DH X tPWM

Duty cycle

= 07H X t

PWM

PWM 输出周期或者占空比周期变化

46

SH69P55A/K55A

13. 低电压复位 (LVR)

LVR 用于监控电源电压并产生芯片内部复位。它一般用于交流供电电路或有大负载的电路, 这些电路工作时负载的启动会引起器

件工作电压暂时低于电路的最低允许工作电压。

功能可以通过代码选项永久开启或禁止。

LVR

当 LVR 功能开启时其功能如下:

当 VDD ≤ VLV R 时产生系统复位

-

-

当 VDD > VLV R 时释放系统复位

这里, VDD: 电源电压, VLVR: LVR 检测电压, 有两档选择 (代码选项)

标志在 LVR 复位后仍然保存, 用户需通过软件清‘0’。

LVR

系统寄存器: $17

地址 第 3 位 第 2 位 第 1 位 第 0 位 读/写 说明

$17 LVR - - - 读/写 第 3 位: 低电压复位标志寄存器 (只读和写 0)

0 X X X

1 X X X

14. ROM 数据读出列表 (RDT)

系统寄存器:

地址 第 3 位 第 2 位 第 1 位 第 0 位 读/写 说明

读/写 无低电压复位

读/写 低电压复位

$380 RDT.3 RDT.2 RDT.1 RDT.0 读/写 ROM 数据列表地址/数据寄存器

$381 RDT.7 RDT.6 RDT.5 RDT.4 读/写 ROM 数据列表地址/数据寄存器

$382 RDT.11 RDT.10 RDT.9 RDT.8 读/写 ROM 数据列表地址/数据寄存器

$383 RDT.15 RDT.14 RDT.13 RDT.12 读/写 ROM 数据列表地址/数据寄存器

RDT 寄存器由一个 13 位只写地址寄存器 (RDT.12 - RDT.0) 和一个 16 位只读 ROM 表数据读出寄存器组成 (RDT.15 - RDT.0)。

为了读出 ROM 表数据, 用户应该先把寄存器高 3 位 (bit13 - 15) 置 0, 再写入 ROM 表地址到 RDT 寄存器 (先是高字节后低字

节

), 在一条指令后, 指定地址的数据将会自动存入 RDT 寄存器 (写入地址的最低位寄存器将会启动数据读出动作)。

47

SH69P55A/K55A

15. 双通道音频发生器

SH69P55A/69K55A 有两个 12 位的音频发生器。音频发生器可以产生特定频率的方波。

音频发生器控制寄存器 (TGCR)

地址 第 3 位 第 2 位 第 1 位 第 0 位 读/写 说明

$3A3 TG1.3 TG1.2 TG1.1 TG1.0 读/写 音频发生器 1 低位寄存器

$3A4 TG1.7 TG1.6 TG1.5 TG1.4 读/写 音频发生器 1 中位寄存器

$3A5 TG1.11 TG1.10 TG1.9 TG1.8 读/写 音频发生器 1 高位寄存器

$3A6 TG2.3 TG2.2 TG2.1 TG2.0 读/写 音频发生器 2 低位寄存器

$3A7 TG2.7 TG2.6 TG2.5 TG2.4 读/写 音频发生器 2 中位寄存器

$3A8 TG2.11 TG2.10 TG2.9 TG2.8 读/写 音频发生器 2 高位寄存器

音频发生器音量控制寄存器 (TVCR)

地址 第 3 位 第 2 位 第 1 位 第 0 位 读/写 说明

$3A9 TV1.3 TV1.2 TV1.1 TV1.0 读/写 音频发生器 1 音量低位寄存器

第

$3AA TG1EN TV1.6 TV1.5 TV1.4

$3AB TV2.3 TV2.2 TV2.1 TV2.0 读/写 音频发生器 2 音量低位寄存器

$3AC TG2EN TV2.6 TV2.5 TV2.4

音量控制寄存器用 7Bit 寄存器控制音频发生器的输出电平。

TGxEN:

0:

1:

注意: x = 1 or 2

音频发生器 x 允许

音频发生器 x 禁止 (默认)

音频发生器 x 禁止

读/写

读/写

2-0 位: 音频发生器 1 音量高位寄存器

第 3 位: 音频发生器 1 允许寄存器

第

2-0 位: 音频发生器 2 音量高位寄存器

第 3 位: 音频发生器 2 允许寄存器

编程注意事项:

当音频发生器工作时, 为了避免漏电, 不可以执行 HALT 或 STOP 指令。

不要同时允许两个音频发生器通道来产生同一个音调, 否则将产生一些无法预知的错误。如果必须同时使用 2 个通道 (例如. 为

了播放双通道音乐), 不要让曲调长时间产生相同的音调, 这样才不会发生错误, 即使发生错误, 也会被听众忽略。

音频发生器输出波形的频率是从 OSC 频率分频得来, 其具体频率可以从下式得到:

f

frequencyoutputTone

其中, N = FFFH - TGCR (TGx.11 - TGx.0)

x = 1 or 2

OSC

×=8

N

48

SH69P55A/K55A

音乐表 1

下表是音频发生器通道

音符 理想频率 N

1 (或通道 2) 在 OSC = 4MHz 下的音乐范围参考表

TGCR

(TGx.11 - TGx.0)

(x = 1 or 2)

实际频率 差错率% 音符 理想频率 N

TGCR

(TGx.11 - TGx.0)

(x = 1 or 2)

实际频率 差错率%

B2 123.47 4050 02E 123.46 -0.01 #F5 739.99 676 D5C 739.64 -0.05

C3 130.81 3822 112 130.82 0.01 G5 783.99 638 D82 783.70 -0.04

#C3 138.59 3608 1E8 138.58 -0.01 #G5 830.61 602 DA6 830.56 -0.01

D3 146.83 3405 2B3 146.84 0.01 A5 880.00 568 DC8 880.28 0.03

#D3 155.56 3214 372 155.57 0.00 #A5 932.33 536 DE8 932.84 0.06

E3 164.81 3034 426 164.80 -0.01 B5 987.77 506 E06 988.14 0.04

F3 174.61 2863 4D1 174.64 0.02 C6 1046.5 478 E22 1046.0 -0.05

#F3 185.00 2703 571 184.98 -0.01 #C6 1108.7 451 E3D 1108.7 -0.01

G3 196.00 2551 609 196.00 0.00 D6 1174.7 426 E56 1173.7 -0.08

#G3 207.65 2408 698 207.64 -0.01 #D6 1244.5 402 E6E 1243.8 -0.06

A3 220.00 2273 71F 219.97 -0.01 E6 1318.5 379 E85 1319.3 0.06

#A3 233.08 2145 79F 233.10 0.01 F6 1396.9 358 E9A 1396.7 -0.02

B3 246.94 2025 817 246.91 -0.01 #F6 1480.0 338 EAE 1479.3 -0.05

C4 261.63 1911 889 261.64 0.01 G6 1568.0 319 EC1 1567.4 -0.04

#C4 277.18 1804 8F4 277.16 -0.01 #G6 1661.2 301 ED3 1661.1 -0.01

D4 293.66 1703 959 293.60 -0.02 A6 1760.0 284 EE4 1760.6 0.03

#D4 311.13 1607 9B9 311.14 0.00 #A6 1864.7 268 EF4 1865.7 0.05

E4 329.63 1517 A13 329.60 -0.01 B6 1975.5 253 F03 1976.3 0.04

F4 349.23 1432 A68 349.16 -0.02 C7 2093.0 239 F11 2092.1 -0.05

#F4 369.99 1351 AB9 370.10 0.03 #C7 2217.5 225 F1F 2222.2 0.22

G4 392.00 1276 B04 391.85 -0.04 D7 2349.3 213 F2B 2347.4 -0.08

#G4 415.30 1204 B4C 415.28 -0.01 #D7 2489.0 201 F37 2487.6 -0.06

A4 440.00 1136 B90 440.14 0.03 E7 2637.0 190 F42 2631.6 -0.21

#A4 466.16 1073 BCF 465.98 -0.04 F7 2793.8 179 F4D 2793.3 -0.02