SIMTEK STK14C88-3W55I, STK14C88-3W55, STK14C88-3W45I, STK14C88-3W45, STK14C88-3N55I Datasheet

...

STK14C88-3

32K x 8 AutoStore™ nvSRAM

3.3V QuantumTrap™ CMOS

Nonvolatile Static RAM

ADVANCE

FEATURES

•“Hands-off” Automatic STORE with External

68µF Capacitor on Power Down

• STORE to EEPROM Initiated by Software or

AutoStore™ on Power Down

• RECALL to SRAM Initiated by Software or

Power Restore

• 45ns and 55ns Access Times

• 8mA Typical I

at 200ns Cycle Time

CC

• Unlimited READ, WRITE and RECALL Cycles

• 1,000,000 STORE Cycles to EEPROM

• 100-Year Data Retention in EEPROM

• 3.0V-3.6V Operation

• Not Sensitive to Power On/Off Ramp Rates

• Commercial and Industrial Temperatures

• 32-Pin SOIC and DIP Packages

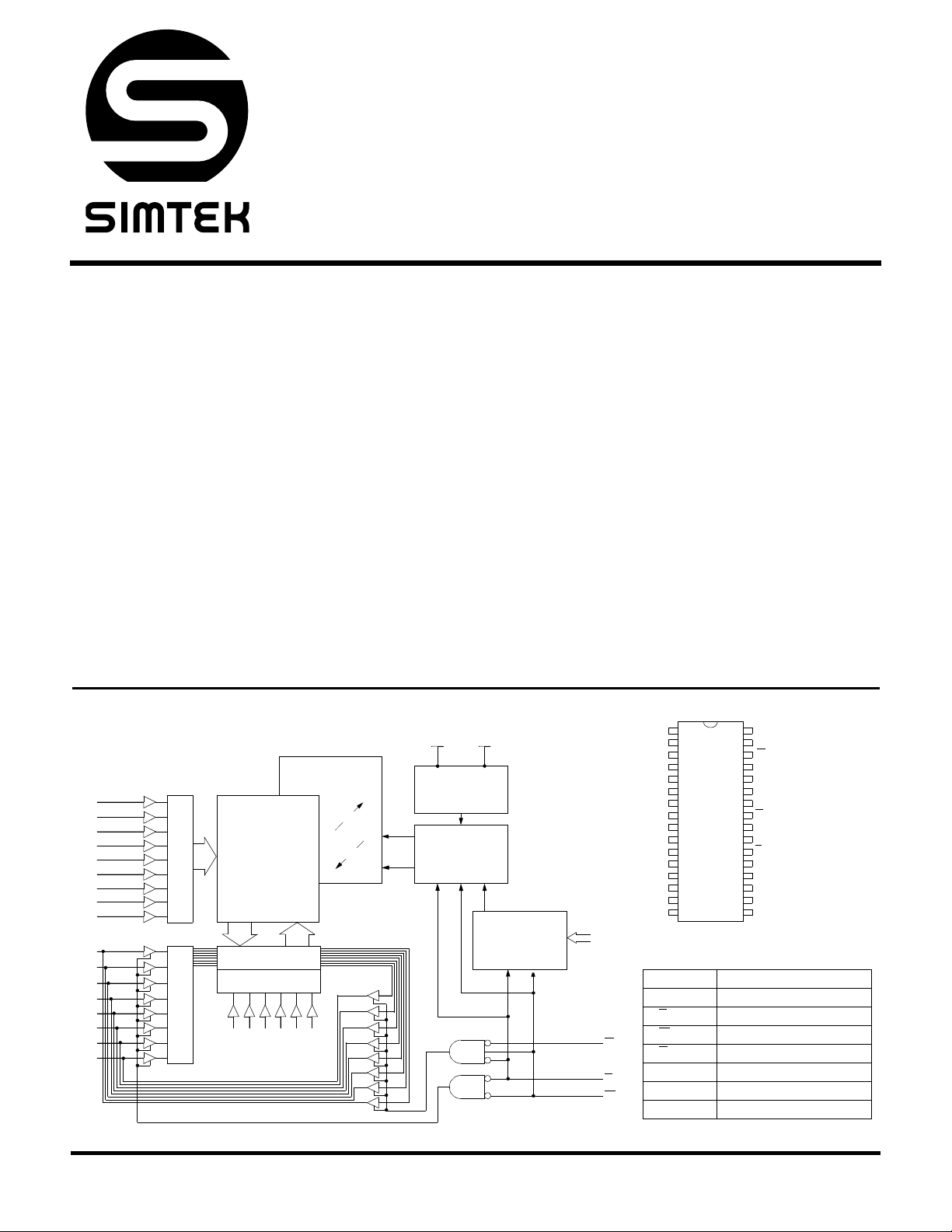

BLOCK DIAGRAM

V

EEPROM ARRAY

512 x 512

A

5

DQ

DQ

DQ

DQ

DQ

DQ

DQ

DQ

A

6

A

7

A

8

A

9

A

11

A

12

A

13

A

14

0

1

2

3

4

5

6

7

ROW DECODER

INPUT BUFFERS

STATIC RAM

ARRAY

512 x 512

COLUMN I/O

COLUMN DEC

A0 A1 A2 A3 A4 A

STORE

RECALL

10

CCXVCAP

POWER

CONTROL

STORE/

RECALL

CONTROL

DESCRIPTION

The Simtek STK14C88-3 is a fast static RAM with a

nonvolatile, electrically erasable

incorporated in each static memory cell. The

PROM element

SRAM

can be read and written an unlimited number of

times, while independent, nonvolatile data resides in

EEPROM. Data transfers from the SRAM to the

EEPROM (the STORE operation) can take place

automatically on power down. A 68µF capacitor

from V

to ground guarantees the STORE opera-

CAP

tion, regardless of power-down slew rate or loss of

power from “hot swapping”. Transfers from the

EEPROM to the SRAM (the RECALL operation) take

place automatically on restoration of power. Initiation of

STORE and RECALL cycles can also be soft-

ware controlled by entering specific read

sequences.

PIN CONFIGUR ATIONS

V

32

CCX

NC

31

30

W

29

A

13

28

A

8

A

27

9

A

26

11

25

G

24

NC

A

23

10

E

22

DQ

21

7

DQ

20

6

19

DQ

5

18

17

Address Inputs

Chip Enable

Write Enable

Output Enable

Power (+ 3.3V)

Capacitor

Ground

32 - 300 SOIC

DQ

4

DQ

3

32 - 600 PDIP

SOFTWARE

DETECT

A0 - A

G

E

W

1

V

CAP

2

A

14

A

3

12

A

4

7

A

5

6

A

6

5

A

7

4

A

8

3

NC

9

A

10

2

A

11

1

A

12

0

DQ

13

0

DQ

14

1

DQ

15

2

V

16

SS

13

PIN NAMES

A0 - A

14

-DQ7Data In/Out

DQ

0

E

W

G

V

CCX

V

CAP

V

SS

July 1999 5-33

STK14C88-3

ABSOLUTE MAXIMUM RATINGS

Volt age on Input Rel ative to VSS . . . . . . . . . .– 0.6V to (VCC + 0.5V)

Volt age on DQ

Temperature under Bias. . . . . . . . . . . . . . . . . . . . . .–55°C to 125°C

Storage Temperature . . . . . . . . . . . . . . . . . . . . . . . .–65°C to 150°C

Power Dissipation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1W

DC Output Current (1 output at a time, 1s duration) . . . . . . . 15mA

or HSB . . . . . . . . . . . . . . . .–0.5V to (VCC + 0.5V)

0-7

a

Note a: Stresses greater than those listed under “Absolute Maximum

Ratings” may cause permanent damage to the device. This is a

stress rating only, and functional operation of the device at conditions above those indicated in the operational sec tions of this

specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

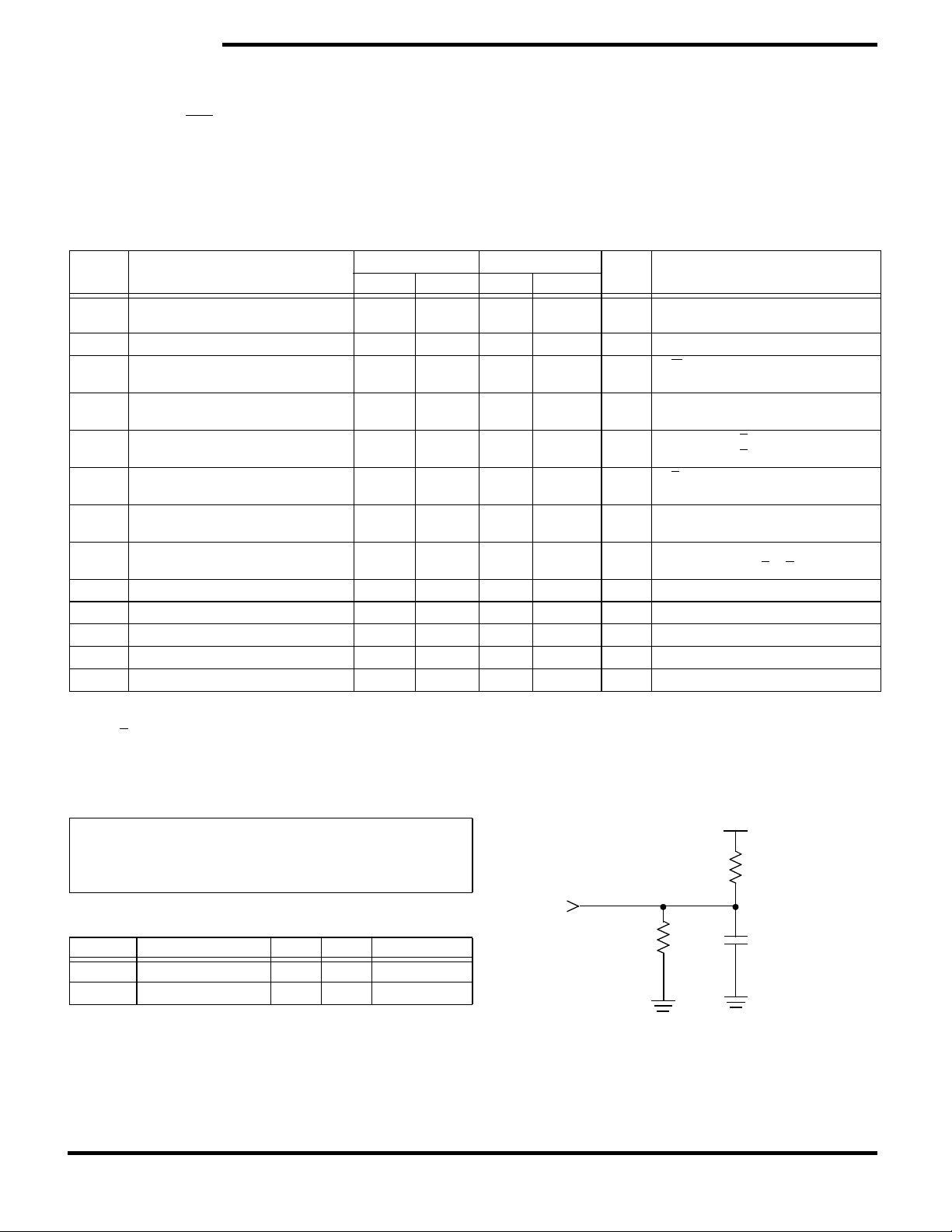

DC CHARACTERISTICS (VCC = 3.0V-3.6V)

SYMBOL PARAMETER

b

I

CC

I

CC

I

CC

I

CC

I

SB

I

SB

I

ILK

I

OLK

V

IH

V

IL

V

OH

V

OL

T

A

Note b: I

Note c: I

Note d: E

Note e: V

Average VCC Current 35

1

c

Average VCC Current during STORE 3 3 mA All Inputs Don’t Care, VCC = max

2

b

Average V

3

3.3V, 25°C, T yp ical

c

Average V

4

AutoStore™ Cycle

d

Average V

1

(Standby, Cycling TT L Input Levels)

d

V

2

CC

(Standby, Stable CMOS Input Levels)

Current at t

CC

Current during

CAP

Current

CC

Standby Current

Input Leakage Current

Off-State Output Leakage Current

Input Logic “1” Voltage 2.2 VCC + .5 2.2 VCC + .5 V All Inputs

Input Logic “0” Voltage VSS – .5 0.8 VSS – .5 0.8 V All Inputs

Output Logic “1” Voltage 2.4 2.4 V I

Output Logic “0” Voltage 0.4 0.4 V I

Operating Temperature 0 70 –40 85 °C

and I

CC

1

and I

CC

2

≥ VIH will not produce standby current levels until any nonvolatile cycle in progress has timed out.

reference levels throughout this datasheet refer to V

CC

nected to ground.

are dependent on output loading and cycle rate. The specified values are obtained with outputs unloaded.

CC

3

are the average currents required for the duration of the respective STORE cycles (t

CC

4

AVAV

= 200ns

COMMERCIAL INDUSTRIAL

MIN MAX MIN MAX

37

30

32

88mA

22mA

9

8

10

9

11mA

±1 ±1 µA

±5 ±5 µA

if that is where the power supply connection is made, or V

CCX

UNITS NOTES

mA

mA

t

= 45ns

AVAV

t

= 55ns

AVAV

W

≥ (V

– 0.2V)

CC

All Others Cycling, CMOS Levels

All Inputs Don’t Care

mA

mA

STORE

t

= 45ns, E ≥ V

AVAV

t

= 55ns, E ≥ V

AVAV

E

≥ (VCC – 0.2V)

All Others V

V

= max

CC

V

= VSS to V

IN

V

= max

CC

V

= VSS to VCC, E or G ≥ VIH

IN

= – 1mA

OUT

= 2mA

OUT

IH

IH

≤ 0.2V or ≥ (VCC – 0.2V)

IN

CC

).

CAP

if V

CCX

is con-

e

AC TEST CONDITIONS

Input Pulse Levels . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0V to 3.0V

Input Rise and Fall Times. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .≤ 5ns

Input and Output Timing Reference Levels . . . . . . . . . . . . . . . 1.5V

Output Load . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . See Figure 1

f

CAPACIT ANCE

(TA = 25°C, f = 1.0MHz)

SYMBOL PARAMETER MAX UNITS CONDITIONS

C

IN

C

OUT

Input Capacitance 5 pF ∆V = 0 to 3V

Output Capacitance 7 pF ∆V = 0 to 3V

Note f: These parameters are guaranteed but not tested.

July 1999 5-34

OUTPUT

3.0V

1.55K Ohms

Figure 1: AC Output Loading

1.1K Ohms

30 pF

INCLUDING

SCOPE AND

FIXTURE

STK14C88-3

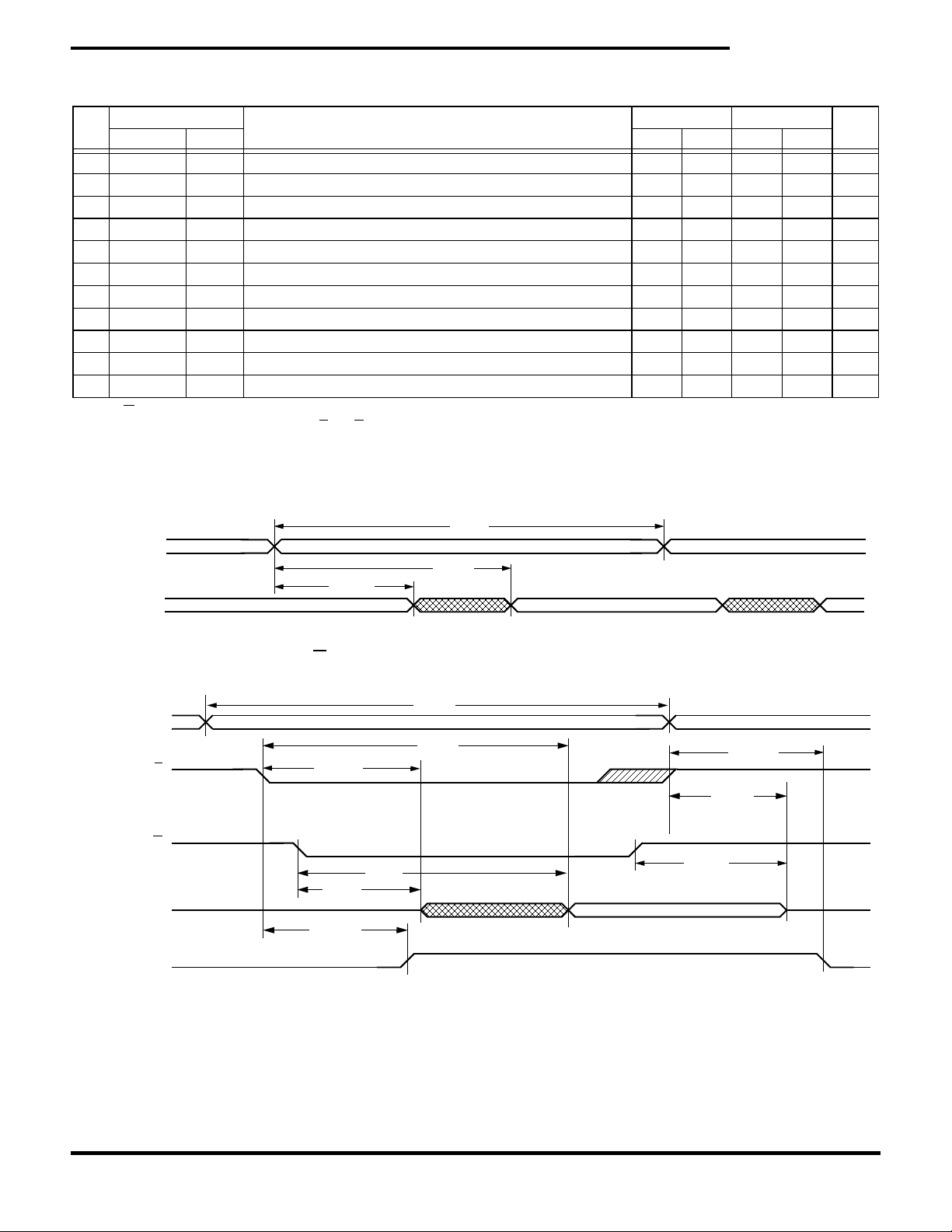

SRAM READ CYCLES #1 & #2 (VCC = 3.0V-3.6V)

NO.

1t

2t

3t

4t

5t

6t

7t

8t

9t

10 t

11 t

SYMBOLS

#1, #2 Alt. MIN MAX MIN MAX

ELQV

AVAV

AVQV

GLQV

AXQX

ELQX

EHQZ

GLQX

GHQZ

ELICCH

EHICCL

t

g

h

h

i

i

ACS

t

RC

t

AA

t

OE

t

OH

t

LZ

t

HZ

t

OLZ

t

OHZ

f

t

PA

f

t

PS

Chip Enable Access Time 45 55 ns

Read Cycle Time 45 55 ns

Address Access Time 45 55 ns

Output Enable to Data Valid 20 25 ns

Output Hold after Address Change 5 3 ns

Chip Enable to Output Active 5 5 ns

Chip Disable to Output I nactive 15 20 ns

Output Enable to Output Active 0 0 ns

Output Disable to Output Inac ti ve 15 20 ns

Chip Enable to Power Active 0 0 ns

Chip Disable to Power Standby 45 55 ns

PARAMETER

Note g: W must be high during SRAM READ cycles.

Note h: Device is continuously selected with E

and G both low.

Note i: Measured ± 200mV from steady state output voltage.

SRAM READ CYCLE #1: Address Controlledg,

2

t

t

AVQV

AVAV

3

ADDRESS

DQ (DATA OUT)

t

AXQX

5

h

DATA VALI D

STK14C88-3-45 STK14C88-3-55

UNITS

e

SRAM READ CYCLE #2: E Controlled

ADDRESS

t

STANDBY

6

t

ELQX

8

t

GLQX

10

ELICCH

t

GLQV

4

DQ (DATA OUT)

I

CC

E

G

g

t

AVAV

t

ELQV

2

1

ACTIVE

DATA VALI D

t

GHQZ

11

t

EHICCL

7

t

EHQZ

9

July 1999 5-35

Loading...

Loading...