SIMTEK STK11C88-W35, STK11C88-W25, STK11C88-W25I, STK11C88-W20, STK11C88-S45I Datasheet

...

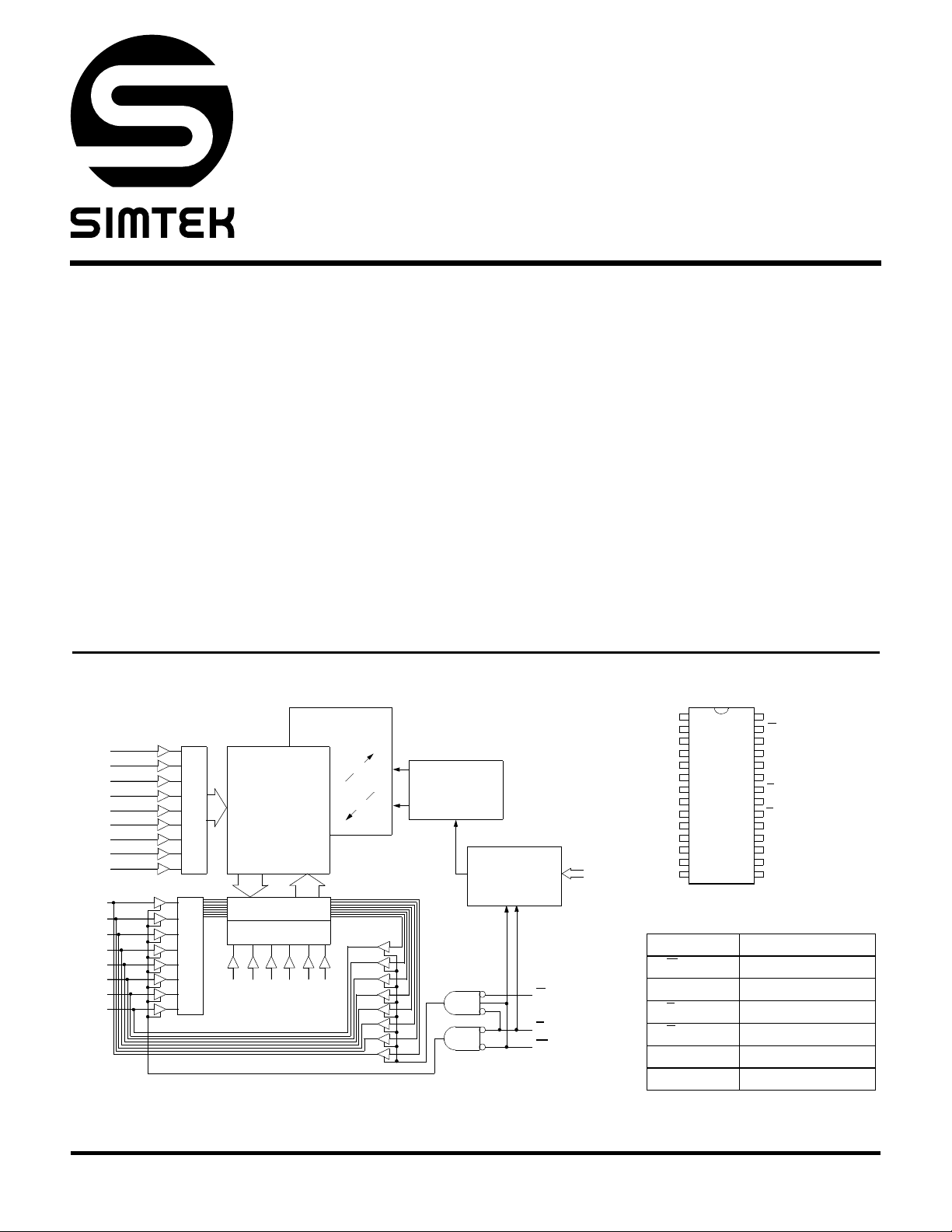

STK11C88

32K x 8 nvSRAM

QuantumTrap™ CMOS

Nonvolatile Static RAM

FEATURES

• 20ns, 25ns, 35ns and 45ns Access Times

• STORE to EEPROM Initiated by Software

• RECALL to SRAM Initiated by Software or

Power Restore

• 10mA T ypical I

at 200ns Cycle Time

CC

• Unlimited READ, WRITE and RECALL Cycles

• 1,000,000 STORE Cycles to EEPROM

• 100-Year Data Retention in EEPROM

• Commercial and Industrial Temperatures

• 28-Pin PDIP and SOIC Packages

BLOCK DIAGRAM

EEPROM ARRAY

512 x 512

STORE

STORE/

RECALL

RECALL

A

A3A

A

2

10

4

CONTROL

DQ

DQ

DQ

DQ

DQ

DQ

DQ

DQ

A

5

A

6

A

7

A

8

A

9

A

11

A

12

A

13

A

14

0

1

2

3

4

5

6

7

INPUT BUFFERS

STATIC RAM

ROW DECODER

COLUMN I/O

COLUMN DEC

A0A

ARRAY

512 x 512

1

DESCRIPTION

The Simtek STK11C88 is a fast static RAM with a

nonvolatile, electrically erasable

incorporated in each static memory cell. The

PROM element

SRAM

can be read and written an unlimited number of

times, while independent nonvolatile data resides in

EEPROM. Data transfers from the SRAM to the

EEPROM (the STORE operation), or from EEPROM to

SRAM (the RECALL operation), take place using a

software sequence. Transfers from the

the

SRAM (the RECALL operation) also take place

EEPROM to

automatically on restoration of power.

The STK11C88 is pin-compatible with industry-

standard

SRAMs.

PIN CONFIGURATIONS

1

SOFTWARE

DETECT

A0 - A

A

14

A

2

12

3

A

7

A

4

6

A

5

5

A

6

4

A

7

3

8

A

2

9

A

1

10

A

0

11

DQ

0

12

DQ

1

13

DQ

2

V

14

13

SS

V

28

CC

W

27

26

A

13

25

A

8

A

24

9

A

23

11

22

G

21

A

10

20

E

19

DQ

7

18

17

16

15

28 - 300 PDIP

DQ

6

28 - 600 PDIP

DQ

5

DQ

28 - 300 SOIC

4

DQ

3

28 - 350 SOIC

PIN NAMES

A0 - A

14

W Write Enable

G

E

W

DQ0 - DQ

E Chip Enable

G Output Enable

V

CC

V

SS

7

Address Inputs

Data In/Out

Power (+5V)

Ground

July 1999 5-1

STK11C88

ABSOLUTE MAXIMUM RATINGS

Volt age on Input Rel ative to VSS. . . . . . . . . . –0.6V to (VCC + 0.5V)

Volt age on DQ

Temperature under Bias . . . . . . . . . . . . . . . . . . . . . –55°C to 125°C

Storage Temperature . . . . . . . . . . . . . . . . . . . . . . . –65°C to 150°C

Power Dissipation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1W

DC Output Current (1 output at a time, 1s duration). . . . . . . . 15mA

. . . . . . . . . . . . . . . . . . . . . . –0.5V to (VCC + 0.5V)

0-7

a

Note a: Stresses greater than those listed under “Absolute Maximum

Ratings” may cause permanent damage to the device. This is a

stress rating only, and functional operation of the device at conditions above those indicated in the operational sections of this

specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

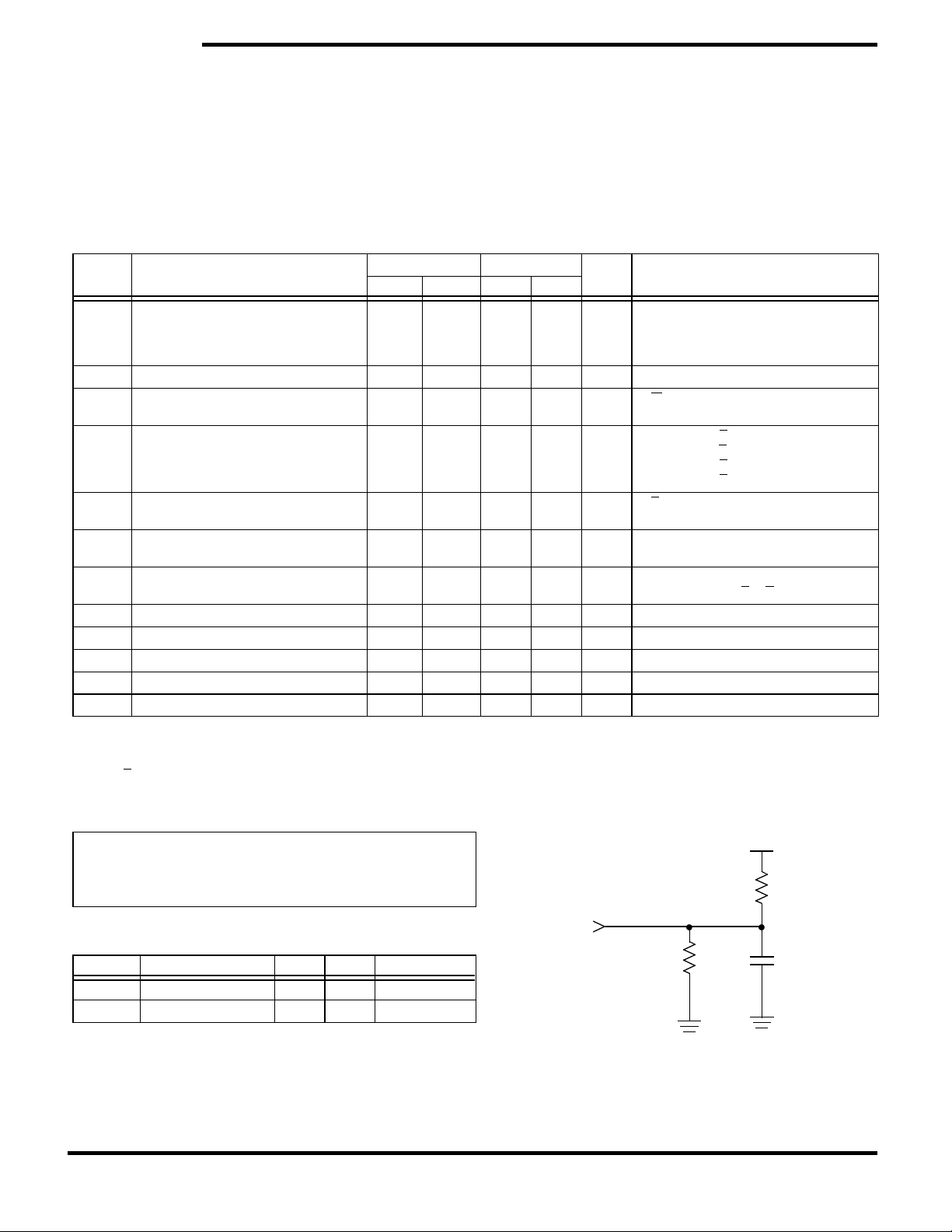

DC CHARACTERISTICS (VCC = 5.0V ± 10%)

SYMBOL PARAMETER

c

I

I

I

I

I

I

I

V

V

V

V

T

CC

CC

CC

SB

SB

ILK

OLK

IH

IL

OH

OL

A

Average VCC Current 110

1

d

Average VCC Current during STORE 33mAAll Inputs Don’t Care, V

2

c

Average VCC Current at t

3

5V, 25°C, Typical

e

Average VCC Current

1

(Standby, Cycling TTL Input Levels)

e

VCC Standby Current

2

(Standby, Stable CMOS Input Levels)

Input Leakage Current

Off-State Output Leakage Current

Input Logic “1” Voltage 2.2 VCC + .5 2.2 VCC + .5 V All Inputs

Input Logic “0” Voltage VSS – .5 0.8 VSS – .5 0.8 V All Inputs

Output Logic “1” Voltage 2.4 2.4 V I

Output Logic “0” Voltage 0.4 0.4 V I

Operating Temperature 0 70 –40 85 °C

AVAV

= 200ns

Note b: The STK11C88-20 requires VCC = 5.0V ± 5% supply to operate at specified speed.

Note c: I

Note d: I

Note e: E

and I

CC

1

is the average current required for the duration of the STORE cycle (t

CC

2

≥ VIH will not produce standby current levels until any nonvolatile cycle in progress has timed out.

are dependent on output loading and cycle rate. The specified values are obtained with outputs unloaded.

CC

3

COMMERCIAL INDUSTRIAL

MIN MAX MIN MAX

N/A

STORE

100

85

70

N/A

31

26

23

).

97

80

70

10 10 mA

35

30

25

22

750 750 µA

±1 ±1 µA

±5 ±5 µA

UNITS NOTES

mA

mA

mA

mA

mA

mA

mA

mA

t

= 20ns

AVAV

t

= 25ns

AVAV

t

= 35ns

AVAV

t

= 45ns

AVAV

W

≥ (V

– 0.2V)

CC

All Others Cycling, CMOS Levels

t

= 20ns, E ≥ V

AVAV

t

= 25ns, E ≥ V

AVAV

t

= 35ns, E ≥ V

AVAV

t

= 45ns, E ≥ V

AVAV

E

≥ (VCC - 0.2V)

All Other s V

V

= max

CC

V

= VSS to V

IN

V

= max

CC

V

= VSS to VCC, E or G ≥ VIH

IN

= – 4mA

OUT

= 8mA

OUT

IH

IH

IH

IH

≤ 0.2V or ≥ (VCC – 0.2V)

IN

CC

CC

= max

b

AC TEST CONDITIONS

Input Pulse Levels . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0V to 3V

Input Rise and Fall Times . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ≤ 5ns

Input and Output Timing Reference Levels. . . . . . . . . . . . . . . 1.5V

Output Load. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .See Figure 1

CAPACITANCE

SYMBOL PARAMETER MAX UNITS CONDITIONS

C

IN

C

OUT

Input Capacitance 5 pF ∆V = 0 to 3V

Output Capacitance 7 pF ∆V = 0 to 3V

f

(TA = 25°C, f = 1.0MHz)

Note f: These parameters are guaranteed but not tested.

July 1999 5-2

OUTPUT

5.0V

480 Ohms

30 pF

255 Ohms

INCLUDING

SCOPE AND

FIXTURE

Figure 1: AC Output Loading

STK11C88

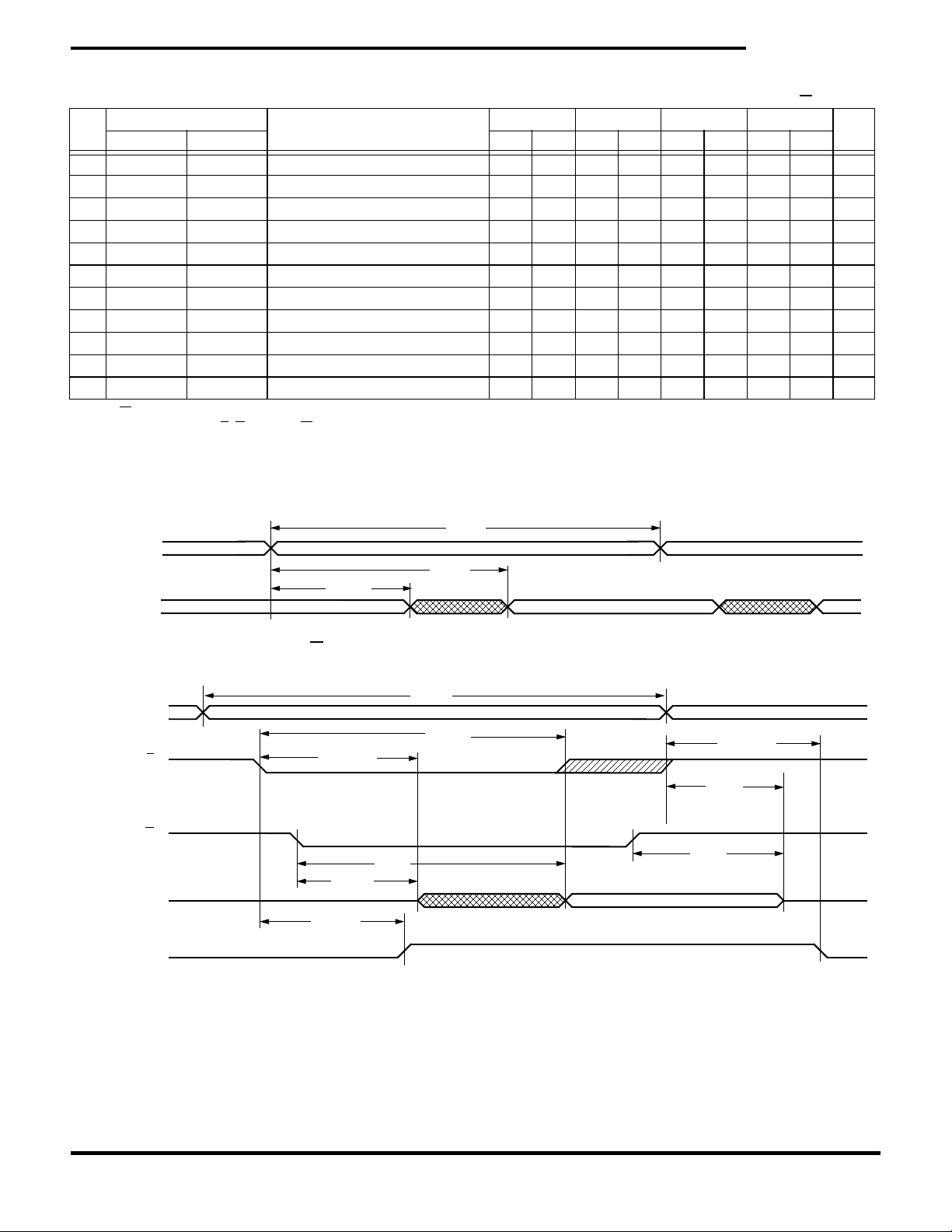

SRAM READ CYCLES #1 & #2 (V

NO.

10 t

11 t

#1, #2 Alt. MIN MAX MIN MAX MIN MAX MIN MAX

1t

ELQV

2t

AVAV

3t

AVQV

4t

GLQV

5t

AXQX

6t

ELQX

7t

EHQZ

8t

GLQX

9t

GHQZ

ELICCH

EHICCL

SYMBOLS

g

h

h

i

i

f

e, f

t

ACS

t

RC

t

AA

t

OE

t

OH

t

LZ

t

HZ

t

OLZ

t

OHZ

t

PA

t

PS

Chip Enable Access Time 20 25 35 45 ns

Read Cycle Time 20 25 35 45 ns

Address Access Time 22 25 35 45 ns

Output Enable to Data Valid 8 10 15 20 ns

Output Hol d after Addres s Change 5 5 5 5 ns

Chip Enable to Output Active 5 5 5 5 n s

Chip Disable to Output Inactive 7 10 13 15 ns

Output Enable to Output Active 0 0 0 0 ns

Output Disa ble to Outp u t Inactive 7 10 13 15 ns

Chip Enable to Power Active 0 0 0 0 ns

Chip Disable to Power Standby 25 25 35 45 ns

PARAMETER

Note g: W must be high during SRAM READ cycles and low during SRAM WRITE cycles.

Note h: I/O state assumes E

, G < V

Note i: Measured ± 200mV from steady state output voltage.

and W > VIH; device is continuously selected.

IL

SRAM READ CYCLE #1: Address Controlled

ADDRESS

3

t

AVQV

DQ (DATA OUT)

t

AXQX

5

STK11C88-20 STK11C88-25 STK11C88-35 STK11C88-45

g, h

2

t

AVAV

DATA VALID

= 5.0V + 10%)

CC

b

UNITS

SRAM READ CYCLE #2: E Controlledg

t

ADDRESS

t

ELQX

10

t

ELICCH

6

t

GLQX

4

t

GLQV

8

DQ (DATA OUT)

I

CC

E

G

STANDBY

2

AVAV

t

ACTIVE

1

ELQV

DATA VALID

t

GHQZ

9

t

EHQZ

7

11

t

EHICCL

July 1999 5-3

Loading...

Loading...