Silicon Storage Technology Inc SST89V564-40-I-TQJ, SST89V564-40-I-TQI, SST89V564-40-I-PJ, SST89V564-40-I-PI, SST89V564-40-I-NJ Datasheet

...

FEATURES:

FlashFlex51 MCU

SST89E564 / SST89V564 / SST89E554 / SST89V554

SST89E/V564 SST89E/VE554 FlashFlex51 MCU

Preliminary Specifications

• 8-bit 8051 Family Compatible Microcontroller

(MCU) with Embedded SuperFlash Memory

• SST89E564/SST 89E 554 is 5V Operatio n

– 0 to 40 MHz Operation at 5V

• SST89V564/SST 89V 554 is 3V Operatio n

– 0 to 25 MHz Operation at 3V

• Fully Software and Developmen t To olset

Compatible as well as Pin -For -Pin Packa ge

Compatible with Stan dar d 8xC5x Micr ocont r oller s

• 1 KByte Register/Data RAM

• Dual Block SuperFlash EEPROM

– SST89E564/SST89V564: 64 KByte primary

block + 8 KByte secondary block

(128-Byte sector size)

– SST89E554/SST89V554: 32 KByte primary

block + 8 KByte secondary block

(128-Byte sector size)

– Individual Block Security Lock

– Concurrent Operation during In-Application

Programming (IAP)

– Block Address Re-mapping

• Support External Address Range up to 64

KByte of Program and Data Memory

• Three High-Current Drive Pins (16 mA each)

• Three 16-bit Timers/Counters

• Full-Duplex Enhanced UART

– Framing error detection

– Automatic address recognition

• Eight Interrupt Sources at 4 Priority Levels

• Watchdog Timer (WDT)

• Four 8-bit I/O Ports (32 I/O Pins)

• Second DPTR register

• Reduce EMI Mode (I nhibi t ALE t hro ugh AUXR SFR )

• SPI Serial Interface

• TTL- and CMOS-Compatible Logic Levels

• Brown-out Detection

• Extended Power-Saving Modes

– Idle Mode

– Power Down Mode with External Interrupt Wake-up

– Standby (Stop Clock) Mode

• PDIP-40, PLCC-44 and TQFP-44 Packages

• Temperature Ranges:

– Commercial (0°C to +70°C)

– Industrial (-40°C to +85°C)

PRODUCT DESCRIPTION

SST89E564, SST89V564, SST89E554, and SST89V554

are members of the FlashF le x51 f amily of 8-bit microcontr ollers. The FlashFlex51 is a family of microcontroller products

designed and m anufactured on the state-of-t he-art SuperFlash CMOS semiconductor process technology. The

device uses th e same powerful instruction se t and is pin-forpin compatible with standard 8xC5x microcontroller devices.

The device comes with 72/40 KByte of on-chip flash

EEPROM program memory using SST’s patented and proprietar y CMO S Super Flash E EPROM tech nolo gy with the

SST’s field-enhancing, tunneling injector, split-gate memory cells. The SuperFlash memory is partitioned into 2

independent program memory blocks. The primary SuperFlash Block 0 occupies 64 /32 KByte of internal program

memory space and the secondary SuperFlash Block 1

occupies 8 KByte of i nt ernal program mem ory space. The

8-KByte second ary SuperFlash block ca n be mapped to

the lowest location of the 64/32 KByte address space; it

can also be hidden from the program counter and used as

an independent EEPROM-like data memory. The flash

memory blocks can be programmed via a standard 87C5x

OTP EPR OM prog ramm er fitted with a specia l adapter and

firmware for SST’s device. During the power-on reset, the

device can be configured as a slave to an external host for

source code storage or as a master to an external host for

In-Application Programming (IAP) o perati on. T he device is

designed to be p rogrammed “In-System ” and “In-Applic ation” on the printed circuit board for maximum flexibility. The

device is pre-programmed with an example of bootstrap

loader in the memo ry, demonstrating the initial user program code loading or su bsequent user c ode updating v ia

the “IAP” operatio n. An example of bootstrap loader is for

the user’s reference and convenience only. SST does not

guarantee the functionality or the usefulness of the sample

bootstrap loader. Chip-Erase or Block-Erase operations will

erase the pr e-pro gra mmed sa mple code .

In addition to 72/ 40 KByte of SuperFlash EEPROM program memory on-chip, the device can address up to 64

KByte of external prog r a m memo ry. In additio n t o 10 24 x 8

bits of on-chip RAM, up to 64 KBy te of exter nal RAM ca n

be addressed.

SST’s highly reliable, patented SuperFlash technology and

memory cell architecture have a number of important

advantages for designing and manufacturing flash

EEPROMs. These advantages translate into significant

cost and reliability benefits for our customers.

©2001 Silicon Storage Technology, Inc.

S71181-03-000 9/01 384

1

FlashFlex, In-Application Programming, IAP, and SoftLock are trademarks of Silicon Storage Technology, Inc.

The SST logo and SuperFlash are registered trademarks of Silicon Storage Technology, Inc.

These specifications are subject to change without notice.

FlashFlex51 MCU

SST89E564 / SST89V564 / SST89E554 / SST89V554

Preliminary Specifications

TABLE OF CONTENTS

PRODUCT DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

LIST OF FIGURES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

LIST OF TABLES. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

1.0 FUNCTIONAL BLOCKS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Functional Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

2.0 PIN ASSIGNMENTS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

2.1 Pin Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

3.0 MEMORY ORGANIZATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

3.1 Program Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

3.2 Program Memory Block Switching . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

3.2.1 Reset Configuration of Program Memory Block Switching. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

3.3 Data Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

3.4 Dual Data Pointers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

3.5 Special Function Registers (SFR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

4.0 FLASH MEMORY PROGRAMMING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

4.1 External Host Programming Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

4.1.1 Product Identification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

4.1.2 Arming Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

4.1.3 Detail Explanation of the External Host Mode Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

4.1.4 External Host Mode Clock Source . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

4.1.5 Flash Operation Status Detection Via External Host Handshake . . . . . . . . . . . . . . . . . . . . . . . . 27

4.1.6 Step-by-step instructions to perform

External Host Mode commands. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

4.1.7 Flash Memory Programming Timing Diagrams with External Host Mode . . . . . . . . . . . . . . . . . . 28

4.2 In-Application Programming Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

4.2.1 In-Application Programming Mode Clock Source. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

4.2.2 Memory Bank Selection for In-Application Programming Mode. . . . . . . . . . . . . . . . . . . . . . . . . . 33

4.2.3 IAP Enable Bit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

4.2.4 In-Application Programming Mode Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

4.2.5 Polling. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

4.2.6 Interrupt Termination . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

5.0 TIMERS/COUNTERS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

6.0 SERIAL I/O . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

6.1 Enhanced Universal Aysnchronous Receiver/Transmitter (UART) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

6.1.1 Framing Error Detection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

6.1.2 Automatic Address Recognition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

6.2 Serial Peripheral Interface (SPI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

©2001 Silicon Storage Technology, Inc. S71181-03-000 9/01 384

2

FlashFlex51 MCU

SST89E564 / SST89V564 / SST89E554 / SST89V554

Preliminary Specifications

7.0 WATCHDOG TIMER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

8.0 SECURITY LOCK. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

8.1 Hard Lock. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

8.2 SoftLock. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

8.3 Security Lock Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

9.0 RESET . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

9.1 Power-On Reset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

9.2 Software Reset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

9.3 Brown-out Detection Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

9.4 Interrupt Priority and Polling Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

9.5 Power-Saving Modes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

9.5.1 Idle Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

9.5.2 Power Down Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

9.5.3 Standby Mode (Stop Clock) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

9.6 Clock Input Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

9.7 Recommended Capacitor Values for Crystal Oscillator. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

10.0 ELECTRICAL SPECIFICATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Absolute Maximum Stress Ratings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

10.1 Operation Range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

10.2 Reliability Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

10.3 DC Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

10.4 AC Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

10.5 AC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

11.0 PRODUCT ORDERING INFORMATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

11.1 Valid Combinations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

12.0 PACKAGING DIAGRAMS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

©2001 Silicon Storage Technology, Inc. S71181-03-000 9/01 384

3

FlashFlex51 MCU

SST89E564 / SST89V564 / SST89E554 / SST89V554

Preliminary Specifications

LIST OF FIGURES

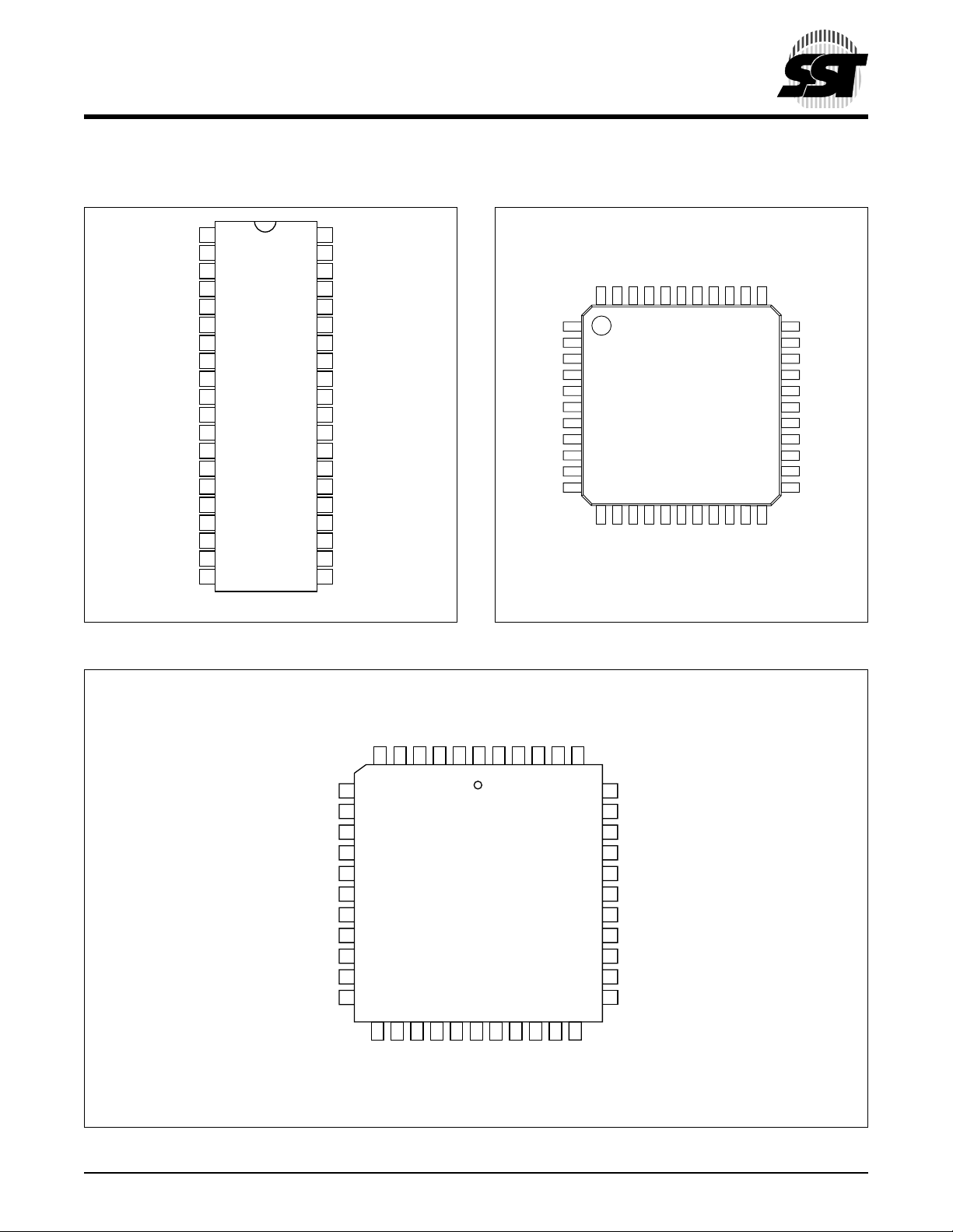

FIGURE2-1: Pin Assignments for 40-pin PDIP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

FIGURE2-2: Pin Assignments for 44-lead TQFP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

FIGURE2-3: Pin Assignments for 44-lead PLCC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

FIGURE3-1: Program Memory Organization for SST89E564 and SST89V564 . . . . . . . . . . . . . . . . . . . . . 10

FIGURE3-2: Program Memory Organization for SST89E554 and SST89V554 . . . . . . . . . . . . . . . . . . . . . 11

FIGURE4-1: I/O Pin Assignments for External Host Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

FIGURE4-2: Read-ID . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

FIGURE4-3: Select-Block1 / Select-Block0. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

FIGURE4-4: Chip-Erase . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

FIGURE4-5: Block-Erase for SST89E564/SST89V564 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

FIGURE4-6: Block-Erase for SST89E554/SST89V554 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

FIGURE4-7: Sector-Erase. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

FIGURE4-8: Byte-Program . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

FIGURE4-9: Prog-SB1 / Prog-SB2 / Prog-SB3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

FIGURE4-10: Prog-SC0 / Prog-SC1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

FIGURE4-11: Byte-Verify . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

FIGURE6-1: SPI Master-slave Interconnection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

FIGURE6-2: SPI Transfer Format with CPHA = 0. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

FIGURE6-3: SPI Transfer Format with CPHA = 1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

FIGURE7-1: Block Diagram of Programmable Watchdog Timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

FIGURE8-1: Security Lock Levels. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

FIGURE9-1: Power-on Reset Circuit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

FIGURE9-2: Oscillator Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

FIGURE10-1: I

FIGURE10-2: I

FIGURE10-3: I

FIGURE10-4: I

FIGURE10-5: AC Testing Input/Output, Float Waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

FIGURE10-6: External Program Memory Read Cycle . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

FIGURE10-7: External Data Memory Read Cycle . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

FIGURE10-8: External Data Memory Write Cycle. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

FIGURE10-9: External Clock Drive Waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

FIGURE10-10: Shift Register Mode Timing Waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Test Condition, Active Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

DD

Test Condition, Idle Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

DD

Test Condition, Power-Down Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

DD

Test Condition, Standby (Stop Clock) Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

DD

©2001 Silicon Storage Technology, Inc. S71181-03-000 9/01 384

4

FlashFlex51 MCU

SST89E564 / SST89V564 / SST89E554 / SST89V554

Preliminary Specifications

LIST OF TABLES

TABLE 2-1: Pin Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

TABLE 3-1: SFCF Values for Program Memory Block Switching for SST89E564/SST89V564 . . . . . . . . 11

TABLE 3-2: SFCF Values for Program Memory Block Switching for SST89E554/SST89V554 . . . . . . . . 12

TABLE 3-3: SFCF Values Under Different Reset Conditions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

TABLE 3-4: FlashFlex51 SFR Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

TABLE 3-5: CPU related SFRs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

TABLE 3-6: Flash Memory Programming SFRs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

TABLE 3-7: Watchdog Timer SFRs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

TABLE 3-8: Timer/Counters SFRs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

TABLE 3-9: Interface SFRs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

TABLE 4-1: External Host Mode Commands for SST89E564/SST89V564. . . . . . . . . . . . . . . . . . . . . . . . 24

TABLE 4-2: External Host Mode Commands for SST89E554/SST89V554. . . . . . . . . . . . . . . . . . . . . . . . 25

TABLE 4-3: Signature Bytes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

TABLE 4-4: IAP Address Resolution for SST89E564/SST89V564 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

TABLE 4-5: In-Application Programming Mode Commands for SST89E564/SST89V564 . . . . . . . . . . . . 35

TABLE 4-6: In-Application Programming Mode Commands for SST89E554/SST89V554 . . . . . . . . . . . . 35

TABLE 4-7: Flash Memory Programming/Verification Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

TABLE 8-1: Security Lock Options. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

TABLE 8-2: Security Lock Access Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

TABLE 9-1: Interrupt Polling Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

TABLE 9-2: Power Saving Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

TABLE 10-1: Operating Range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

TABLE 10-2: Reliability Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

TABLE 10-3: DC Electrical Characteristics: 40MHz devices; 4.5-5.5V . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

TABLE 10-4: DC Electrical Characteristics: 25MHz devices; 2.7-3.6V . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

TABLE 10-5: AC Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

TABLE 10-6: External Clock Drive. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

TABLE 10-7: Serial Port Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

©2001 Silicon Storage Technology, Inc. S71181-03-000 9/01 384

5

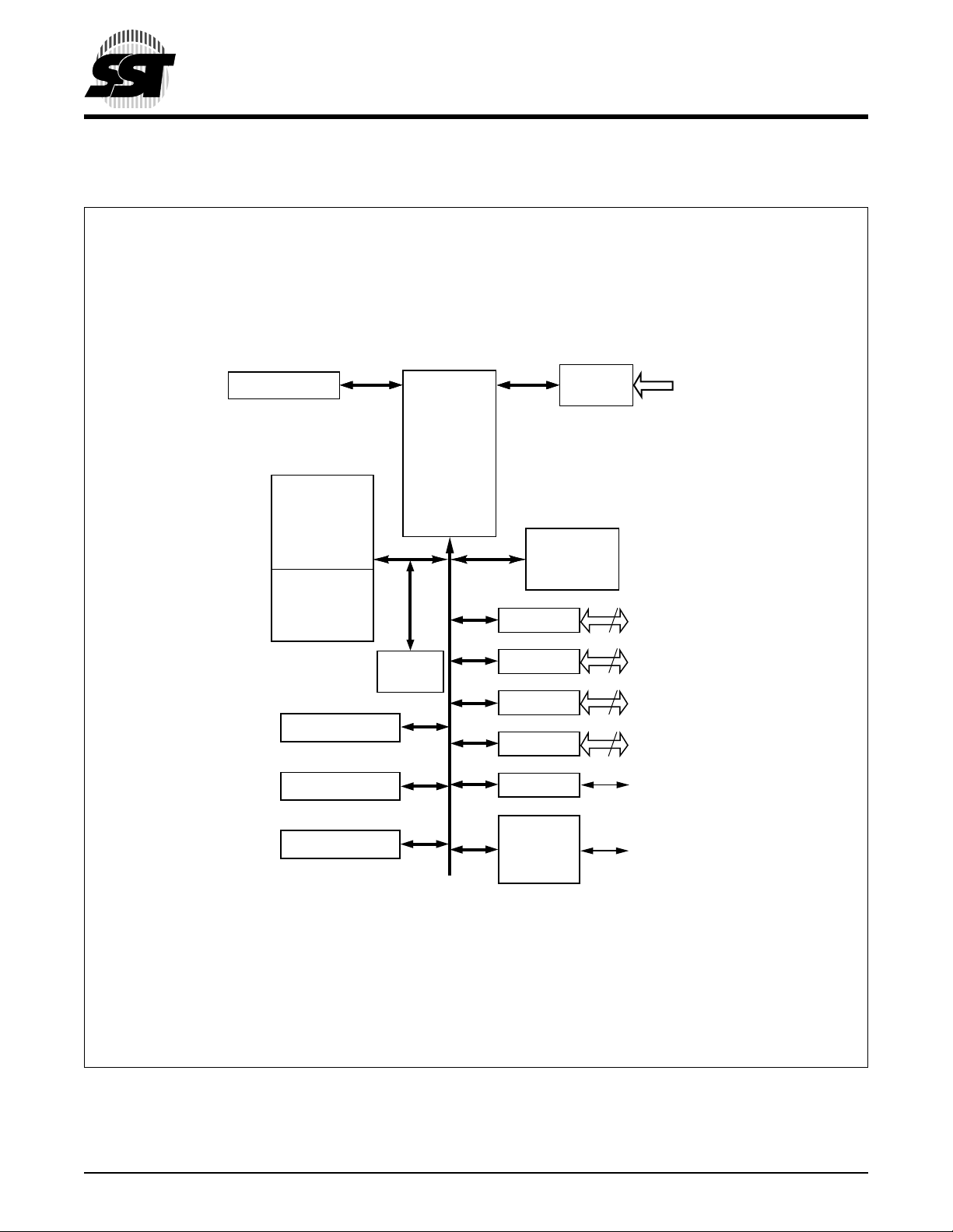

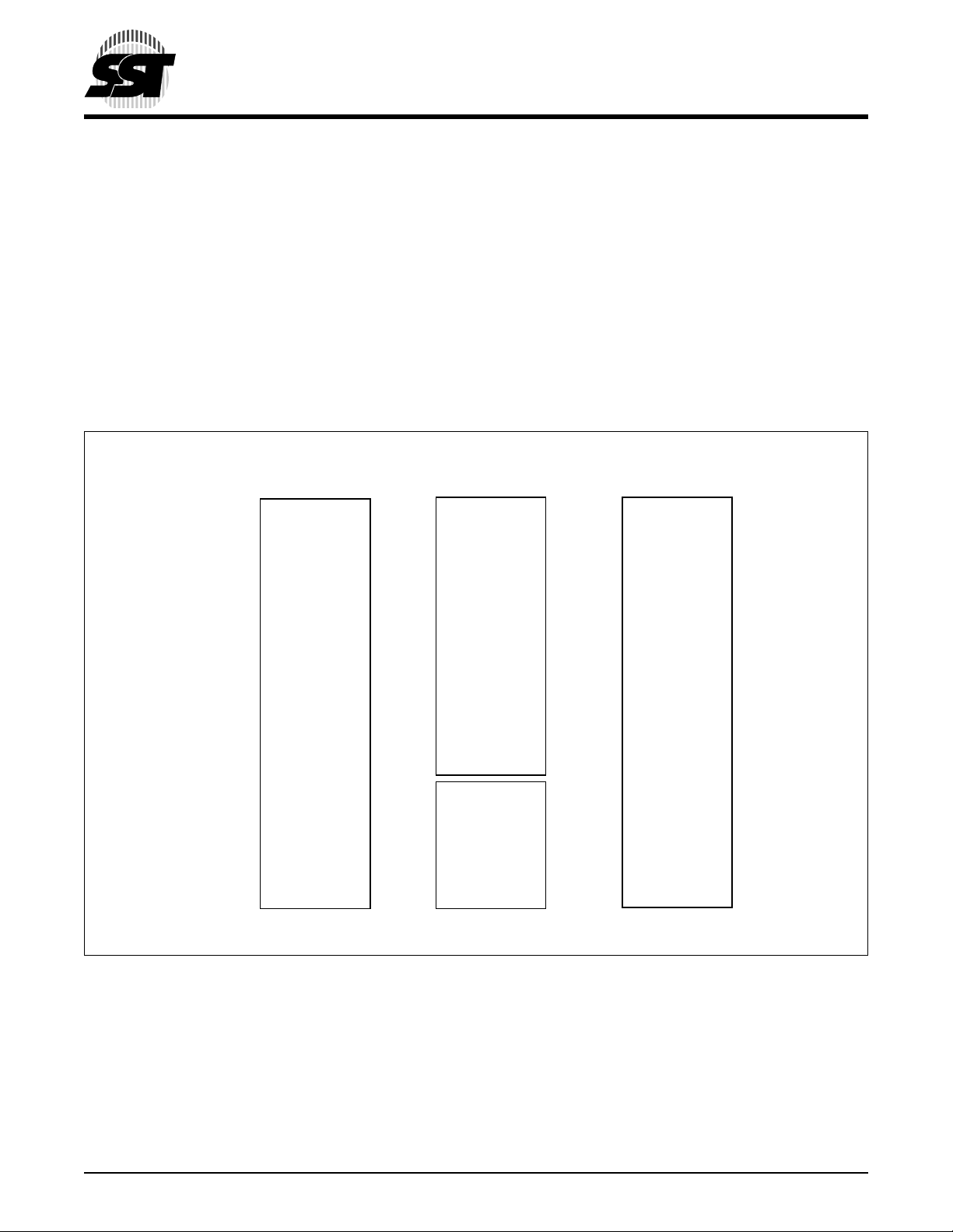

1.0 FUNCTIONAL BLOCKS

FUNCTIONAL BLOCK DIAGRAM

FlashFlex51 MCU

SST89E564 / SST89V564 / SST89E554 / SST89V554

Preliminary Specifications

Watchdog Timer

SuperFlash

EEPROM

Primary

Block

32K/64K x8

Secondary

Block

8K x8

Timer 0 (16-bits)

Timer 1 (16-bits)

Interrupt

Control

8051

CPU Core

1

Security

Lock

RAM

1K x8

I/O Port 0

88

I/O Port 1

8

I/O Port 2

8

I/O Port 3

SPI

8 Interrupts

I/O

I/O

I/O

I/O

Timer 2 (16-bits)

1. 64K x8 for SST89E564 and SST89V564

32K x8 for SST89E554 and SST89V554

©2001 Silicon Storage Technology, Inc. S71181-03-000 9/01 384

8-bit

Enhanced

UART

384 ILL B1.4

6

FlashFlex51 MCU

SST89E564 / SST89V564 / SST89E554 / SST89V554

Preliminary Specifications

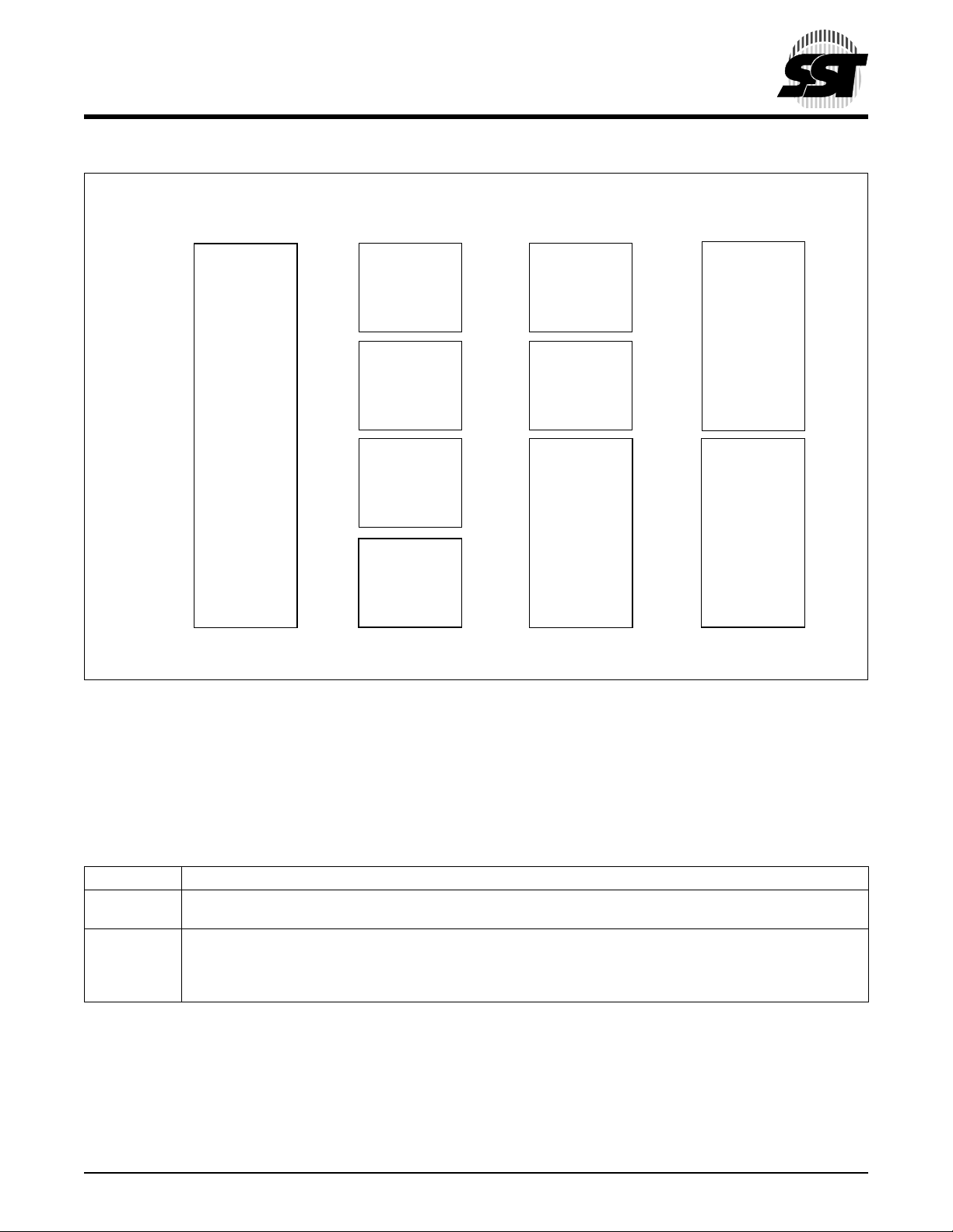

2.0 PIN ASSIGNMENTS

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

V

DD

P0.0 (AD0)

P0.1 (AD1)

P0.2 (AD2)

P0.3 (AD3)

P0.4 (AD4)

P0.5 (AD5)

P0.6 (AD6)

P0.7 (AD7)

EA#

ALE/PROG#

PSEN#

P2.7 (A15)

P2.6 (A14)

P2.5 (A13)

P2.4 (A12)

P2.3 (A11)

P2.2 (A10)

P2.1 (A9)

P2.0 (A8)

(MOSI) P1.5

(MISO) P1.6

(SCK) P1.7

RST

(RXD) P3.0

Reserved

(TXD) P3.1

(INT0#) P3.2

(INT1#) P3.3

(T0) P3.4

(T1) P3.5

(T2) P1.0

(T2 Ex) P1.1

P1.2

P1.3

(SS#) P1.4

(MOSI) P1.5

(MISO) P1.6

(SCK) P1.7

RST

(RXD) P3.0

(TXD) P3.1

(INT0#) P3.2

(INT1#) P3.3

(T0) P3.4

(T1) P3.5

(WR#) P3.6

(RD#) P3.7

XTAL2

XTAL1

V

SS

1

2

3

4

5

6

7

40-pin PDIP

8

T op View

9

10

11

12

13

14

15

16

17

18

19

20

P1.4 (SS#)

P1.3

P1.2

P1.1 (T2 Ex)

P1.0 (T2)

Reserved

VDDP0.0 (AD0)

P0.1 (AD1)

44 43 42 41 40 39 38 37 36 35 34

1

2

3

4

5

6

7

8

9

10

11

44-lead TQFP

T op Vie w

12 13 14 15 16 17 18 19 20 21 22

SS

V

XTAL2

(RD#) P3.7

(WR#) P3.6

XTAL1

Reserved

(A8) P2.0

(A9) P2.1

(A10) P2.2

P0.2 (AD2)

P0.3 (AD3)

33

32

31

30

29

28

27

26

25

24

23

(A12) P2.4

(A11) P2.3

P0.4 (AD4)

P0.5 (AD5)

P0.6 (AD6)

P0.7 (AD7)

EA#

Reserved

ALE/PROG#

PSEN#

P2.7 (A15)

P2.6 (A14)

P2.5 (A13)

384 ILL F19.5

384 ILL F18.3

FIGURE 2-1: PIN ASSIGNMENTS FOR 40-PIN PDIP FIGURE 2-2: PIN ASSIGNMENTS FOR 44-LEAD TQFP

P1.4 (SS#)

P1.3

P1.2

P1.1 (T2 Ex)

P1.0 (T2)

Reserved

VDDP0.0 (AD0)

P0.1 (AD1)

P0.2 (AD2)

P0.3 (AD3)

6 5 4 3 2 1 44 43 42 41 40

7

8

9

10

11

12

44-lead PLCC

T op Vie w

13

14

15

16

17

18 19 20 21 22 23 24 25 26 27 28

SS

V

XTAL2

(RD#) P3.7

(WR#) P3.6

XTAL1

Reserved

(A8) P2.0

(A9) P2.1

(A10) P2.2

39

38

37

36

35

34

33

32

31

30

29

(A12) P2.4

(A11) P2.3

384 ILL F20.4

P0.4 (AD4)

P0.5 (AD5)

P0.6 (AD6)

P0.7 (AD7)

EA#

Reserved

ALE/PROG#

PSEN#

P2.7 (A15)

P2.6 (A14)

P2.5 (A13)

FIGURE 2-3: P

(MOSI) P1.5

(MISO) P1.6

(SCK) P1.7

RST

(RXD) P3.0

Reserved

(TXD) P3.1

(INT0#) P3.2

(INT1#) P3.3

(T0) P3.4

(T1) P3.5

IN ASSIGNMENTS FOR 44-LEAD PLCC

©2001 Silicon Storage Technology, Inc. S71181-03-000 9/01 384

7

FlashFlex51 MCU

SST89E564 / SST89V564 / SST89E554 / SST89V554

Preliminary Specifications

2.1 Pin Descriptions

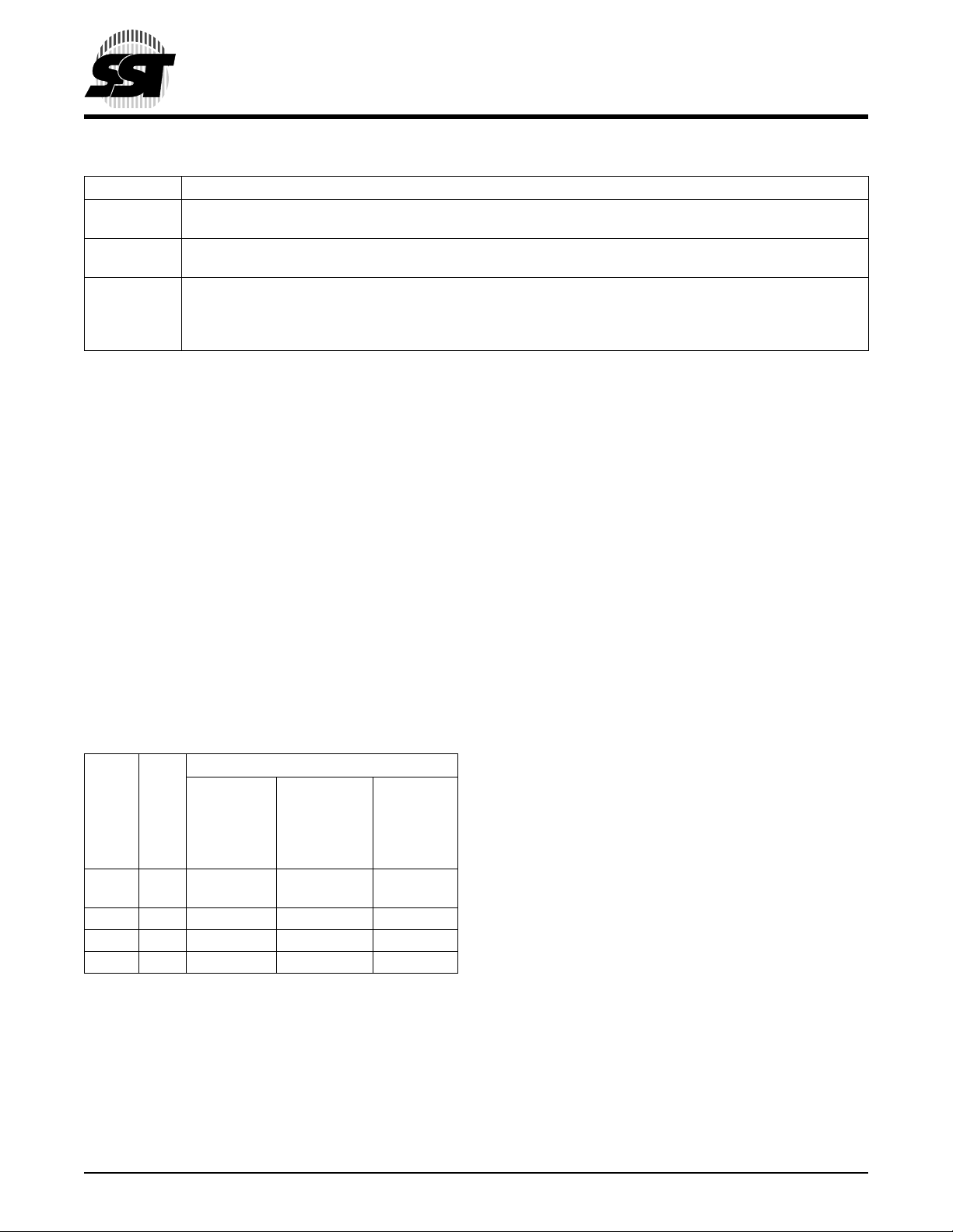

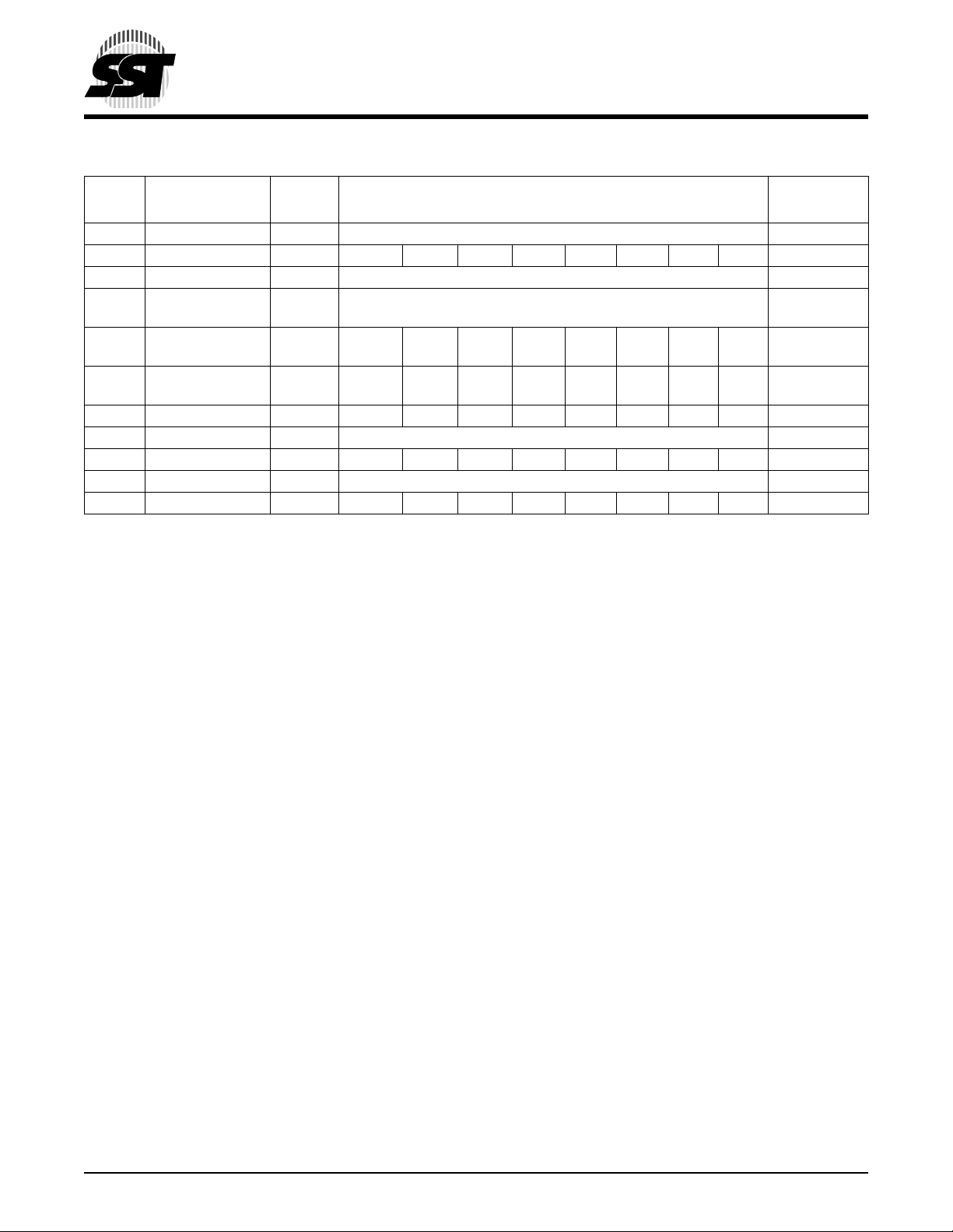

TABLE 2-1: PIN DESCRIPTIONS (1 OF 2)

pull-ups

pull-ups

pull-ups

1

Name and Functions

sink seve ral LS TTL inputs. Port 0 pins float that have “1”s written to them, and in this state

can be used as high-impedance inputs. Port 0 is also the multiplexed low-order address and

data bus during accesses to external memory. In this application, it uses strong internal pullups when transitioning to V

. Port 0 also receives the code bytes during the external host

OH

mode programming, and outputs the code bytes during the external host mode verification.

External pull-u ps are required during program verification.

Port 1: Port 1 is an 8-bit bi-directional I/O port with internal pull-ups. The P ort 1 output buffers

can drive LS TTL inputs. Port 1 pins are pulled high by the internal pull-ups when “1”s are

written to them and can be used as inputs in this state. As inputs, Port 1 pins that are externally pulled lo w will source cu rren t (I

, see Tables 10-3 and 10-4 ) beca use of t he inte rnal pull-

IL

ups. P1[5, 6, 7] have high current drive of 16 mA. Port 1 also receives the low-order address

bytes during the external host mode p rogramming and verification.

Port 2: Port 2 is an 8-bit bi-directional I/O port with internal pull-ups. Port 2 pins are pulled

high by the internal pull-ups when “1”s are written to them and can be used as inputs in this

state. As inputs, Port 2 pins that are externally pulled low will source current (I

, see Tables

IL

10-3 and 10-4) because of the internal pull-ups. Port 2 sends the high-order address byte

during fetches from exte rnal Program memory and during acce sses to e xternal Data Mem ory

that use 16-bit address (MOVX@DPTR). In this application, it uses strong internal pull-ups

when transitioning to V

. Port 2 also receives some control signals and a partial of high-

OH

order address bits during the external host mode programming and verification.

Port 3: Port 3 is an 8-bit bidirection al I / O po rt with internal pul l-u ps. The Port 3 output buff e rs

can drive LS TTL inputs. Port 3 pins are pulled high by the internal pull-ups when “1”s are

written to them and can be used as inputs in this state. As inputs, Port 3 pins that are externally pulled lo w will source cu rren t (I

, see Tables 10-3 and 10-4 ) beca use of t he inte rnal pull-

IL

ups. P ort 3 also receives some control signals and a partial of high-order addre ss bits during

the external host mode programming and verification.

device is executing from Internal Program Memory, PSEN# is inactive (V

). When the

OH

device is executing code from External Program Memory, PSEN# is activated twice each

machine cycle, ex ce pt whe n acce ss to Exte rnal Data Memory while one PSEN# activation is

skipped in each machine cycle. A forced high-to-low input transition on the PSEN# pin while

the RST input is conti n ual ly hel d hi gh for more than ten machine cycles will ca us e the device

to enter External Host mode for programming.

Symbol Type

P0[7:0] I/O Port 0: Port 0 is an 8-bit open drain bi-directional I/O port. As an output port each pin can

P1[7:0] I/O with internal

P1[0] I/O T2: External count input to Timer/Counter 2 or Clock-out from Timer/Counter 2

P1[1] I T2EX: Timer/Counter 2 capture/reload trigger and direction control

P1[4] I/O SS#: Master Input or Slave Output for SPI

P1[5] I/O MOSI: Master Output line, Slave Input line for SPI

P1[6] I/O MISO: Master Input line, Slave Output line for SPI

P1[7] I/O SCK: Master clock output, slave clock input line for SPI

P2[7:0] I/O with internal

P3[7:0] I/O with internal

P3[0] I RXD: Serial input line

P3[1] O TXD: Serial output lin e

P3[2] I INT0#: External Interrupt 0 Input

P3[3] I INT1#: External Interrupt 1 Input

P3[4] I T0: External count input to Timer/Counter 0

P3[5] I T1: External count input to Timer/Counter 1

P3[6] O WR#: External Data Memory Write strobe

P3[7] O RD#: External Data Memory Read strobe

PSEN# I/O Program Store Enable: PSEN# is the Read strobe to External Program Store. When the

©2001 Silicon Storage Technology, Inc. S71181-03-000 9/01 384

8

FlashFlex51 MCU

SST89E564 / SST89V564 / SST89E554 / SST89V554

Preliminary Specifications

TABLE 2-1: PIN DESCRIPTIONS (CONTINUED) (2 OF 2)

Symbol Type

RST I Reset: Whil e the oscill ator is running, a hi gh logic sta te on this pin for tw o machi ne cycles will

EA# I External Access Enable : EA# must be driven to V

ALE/PROG# I/O Address Latch Enable: ALE is the output signal for latching the low byte of the address dur-

XTAL1

XTAL2

V

DD

Vss I Ground: Circuit ground. (0V reference)

1. I = Input; O = Output

2. It is not necessary to receive a 12V programming supply voltage during flash programming.

1

Name and Functions

reset the device. After a reset, if the PSEN# pin is driven by a high-to-low input transition

while the RST input pin is held high, the device will enter the External Host mode, otherwise

the device will enter the Normal operation mode.

in order to enable the device to fetch

code from the External Program Memory. EA# must be driven to V

IL

for internal program exe-

IH

cution. However, Security lock level 4 will disable EA#, and program execution is only possible from internal program memory. The EA# pin can tolerate a high voltage

2

of 12V

(see “Absolute Maximum Stress Ratings” on page 47).

ing acces s es to external memory. This pin is also the programming pulse input (PROG#) for

the external host mode. ALE is activated twice each machine cycle, except when access to

External Data Memory, one ALE activation is skipped in th e seco nd mac hine cy cle . Ho wever,

if AO is set to 1, ALE is disabled. (see “Auxiliary Register (AUXR)” on page 20)

I

O

Oscillator: Input and output to the inverting oscillator amplifier. XTAL1 is input to internal

clock generation circuits from an external clock source.

I Power Supp ly: Supply voltage during normal, Idle, Power Down, and Standby Mode opera-

tions.

T2-1.6 384

©2001 Silicon Storage Technology, Inc. S71181-03-000 9/01 384

9

3.0 MEMORY ORGANIZATION

FlashFlex51 MCU

SST89E564 / SST89V564 / SST89E554 / SST89V554

Preliminary Specifications

The device has separate addr e ss s pa ce s for program an d

data memory.

3.1 Program Memory

There are two internal flash memor y blocks in the device.

The primary flash memory block (Block 0) has 64/32

KByte. The secondary flash memory block (Block 1) has 8

KByte. Since the total program address space is limited to

64/32 KByte, the SFCF[1:0] bit are used to control Program

FFFFH

EA# = 0

FFFFH

SFCF[1:0] = 00

Bank Selectio n. Please re fer to Figure 3-1 and F igure 3-2

for the program memory configurations. Program Bank

Select is described in the next section.

The 64K/32K x8 primary SuperFlash block is organized as

512/256 sectors, each sector consists of 128 Bytes.

The 8K x8 secondary SuperFlash block is organized as 64

sectors, each sector consists also of 128 Bytes.

For both blocks, the 7 least significant program address bits

select the byte within the sector. The remainder of the program addr ess bi ts selec t the sect or with in the bloc k.

EA# = 1

EA# = 1

SFCF[1:0] = 01, 10, 11

FFFFH

56 KByte

Block 0

0000H

FIGURE 3-1: P

External

64 KByte

64 KByte

Block 0

2000H

1FFFH

8 KByte

Block 1

0000H

ROGRAM MEMORY ORGANIZATION FOR SST89E564 AND SST89V564

0000H

384 ILL F48.5

©2001 Silicon Storage Technology, Inc. S71181-03-000 9/01 384

10

FlashFlex51 MCU

SST89E564 / SST89V564 / SST89E554 / SST89V554

Preliminary Specifications

FFFFH

0000H

EA# = 0

External

64 KByte

FFFFH

E000H

DFFFH

8000H

7FFFH

2000H

1FFFH

0000H

EA# = 1

SFCF[1:0] = 00

8 KByte

Block 1

External

24 KByte

24 KByte

Block 0

8 KByte

Block 1

FFFFH

E000H

DFFFH

8000H

7FFFH

0000H

EA# = 1

SFCF[1:0] = 01

8 KByte

Block 1

External

24 KByte

32 KByte

Block 0

EA# = 1

SFCF[1:0] = 10, 11

FFFFH

External

32 KByte

8000H

7FFFH

32 KByte

Block 0

0000H

384 ILL F48b.3

FIGURE 3-2: PROGRAM MEMORY ORGANIZATION FOR SST89E554 AND SST89V 554

3.2 Program Memory Block Switching

The prog r am mem ory block switching feature of the device

allows either Block 1 or the lowest 8 KByte of Block 0 to be

used for the lowest 8 KByte of the program address space.

SFCF[1:0] controls program memory block switching.

TABLE 3-1: SFCF VALUES FOR PROGRAM MEMORY BLOCK SWITCHING FOR SST89E564/SST89V 564

SFCF[1:0] Program Memory Block Switching

01, 10, 11 Block 1 is not visible to the PC;

Block 1 is reachable only via In-Application Programming from 000H - 1FFFH.

00 Block 1 is overlaid onto the low 8K of the program address space; occupying address locations 0000H - 1FFFH.

When the PC falls within 0000H - 1FFFH, the instruction will be fetched from Block 1 instead of Block 0.

Outside of 0000H - 1FFFH, Block 0 is used. Locations 0000H - 1FFFH of Block 0 are reachable through

In-Application Programming.

T3-1.0 384

©2001 Silicon Storage Technology, Inc. S71181-03-000 9/01 384

11

FlashFlex51 MCU

SST89E564 / SST89V564 / SST89E554 / SST89V554

Preliminary Specifications

TABLE 3-2: SFCF V

SFCF[1:0] Program Memory Block Switching

10, 11 Block 1 is not visible to the PC;

Block 1 is reachable only via In-Application Programming from E000H - FFFFH.

01 Both Block 0 and Block 1 are visible to the PC.

Block 0 is occupied from 0000H - 7FFFH. Block 1 is occupied from E000H - FFFFH.

00 Block 1 is overlaid onto the low 8K of the program address space; occupying address locations 0000H - 1FFFH.

When the PC falls within 0000H - 1FFFH, the instruction will be fetched from Block 1 instead of Block 0.

Outside of 0000H - 1FFFH, Block 0 is used. Locations 0000H - 1FFFH of Block 0 are reachable through

In-Application Programming.

3.2.1 Reset Configuration of Program Memory

Block Switching

Program memory block switching is initialized after reset

according to the state of the Start-up Configuration bit SC0.

The SC0 bit is programmed via an External Host Mode

command or an IAP Mode command. Se e Table 4-2 and

Table 4-6.

Once out of reset, the SFCF[0] bit can be changed dynamically by the progr am f or desir ed eff ects . Changing SFCF[0]

will not change the SC0 bit.

Caution must be taken when dynamically changing the

SFCF[0] bit. Since this will cause different physical memory

to be mapped to t he logical program address s pace. The

user must avoid executing block switching instructions

within the address range 0000H to 1FFFH.

ALUES FOR PROGRAM MEMORY BLOCK SWITCHING FOR SS T8 9E554/S ST89V 554

3.3 D ata Memory

The device has 1024 x 8 bits of on-chip RAM and can

address up to 64 KByte of external data memory .

The device has f our sect ions of internal dat a memory:

1. The lower 128 Bytes of RAM (00H to 7FH) are

directly and indirectly addressable.

2. The higher 128 Bytes of RAM (80H to FFH) are

indirectly addressable.

3. The Special Function Registers (SFRs, 80H to

FFH) are directly addressable only.

4. The expanded RAM of 768 Bytes (00H to 2FFH) is

indirectly addressable by the move external

instruction (MOVX) and clearing the EXTRAM bit.

(See “Auxiliary Register (AUXR)” on page 20)

T3-2.2 384

TABLE 3-3: SFCF VALUES UNDER DIFFERENT

ESET CONDITIONS

R

State of SFCF[1:0] after:

WDT

Power-on

or

1

SC1

SC0

11 00

10 01 x1 11

0 1 10 10 10

0 0 11 11 11

1. SC1 only applies to SST89E554 and SST89V554.

External

Reset

(default)

Reset

or

Brown-out

Reset

x0 10

Software

Reset

T3-3.2 384

3.4 Dual Data Pointers

The device has two 16-bit data pointers. The DPTR Select

(DPS) bit in AUXR1 determines which of the two data

pointers is accessed. When DPS=0, DPTR0 is selected;

when DPS=1, DPTR1 is selected. Quickly switching

between the two data pointers can be accomplished by a

single INC instruction on AUXR1.

3.5 Special Function Registers (SFR)

Most of the unique features of the Flash Flex51 microcontroller family are contr o ll ed by bits in s pecial function r eg isters (SFRs) located in the SFR Memory Map shown in

Table 3-4. Individual descriptions of each SFR are provided

and Reset values indicated in T ables 3-5 to 3-9.

©2001 Silicon Storage Technology, Inc. S71181-03-000 9/01 384

12

FlashFlex51 MCU

SST89E564 / SST89V564 / SST89E554 / SST89V554

Preliminary Specifications

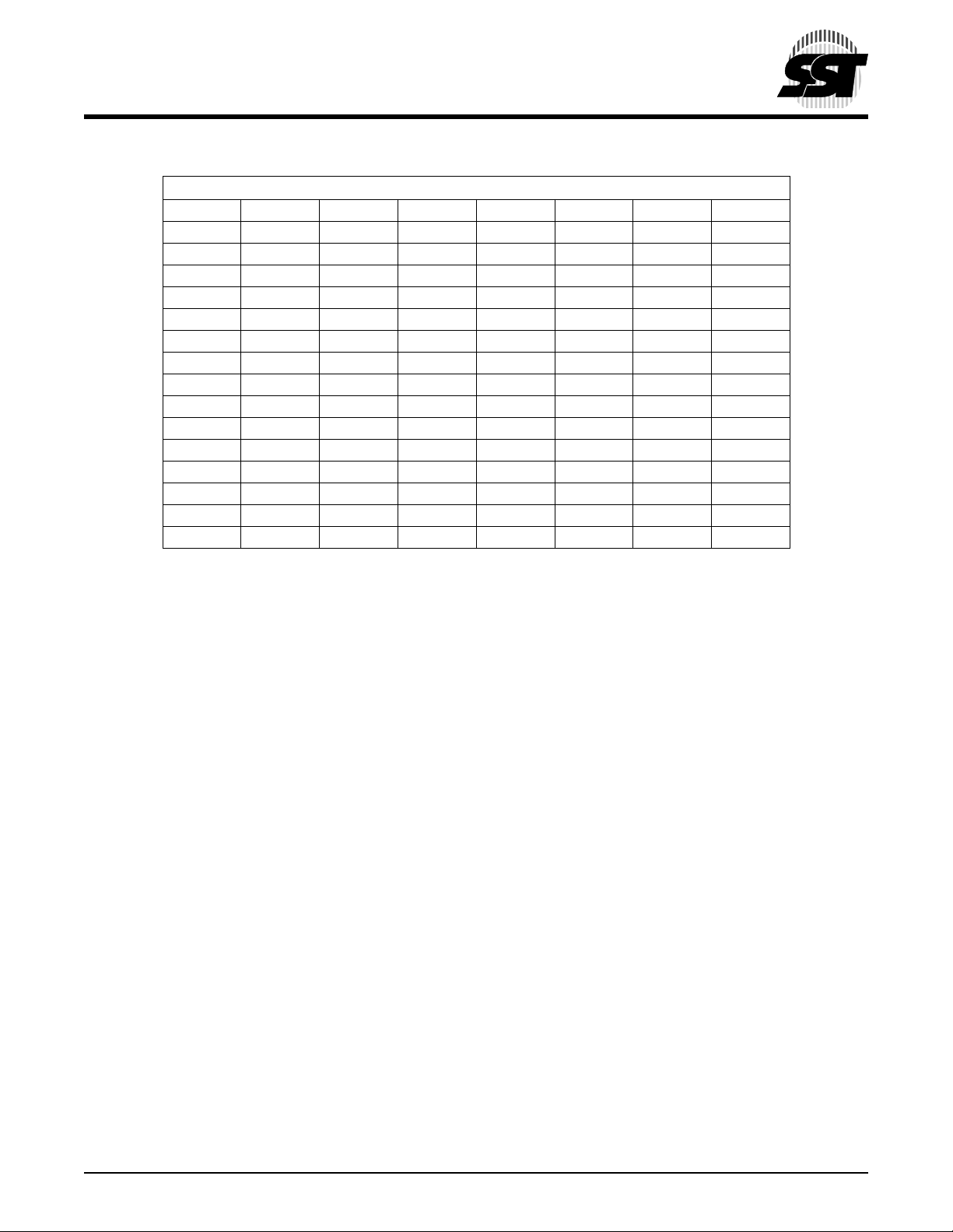

TABLE 3-4: FLASHFLEX51 SFR MEMORY MAP

8 BYTES

F8H IPA

F0H B

E8H IEA

E0H ACC

D8H DFH

D0H PSW

C8H T2CON

C0H WDTC

B8H IP

B0H P3

A8H IE

A0H P2

98H SCON

90H P1

88H TCON

80H P0

1. SFRs are bit addressable.

1

1

1

1

1

1

T2MOD RCAP2L RCAP2H TL2 TH2 CFH

1

1

1

1

1

1

1

SADEN BFH

SFCF SFCM SFAL SFAH SFDT SFST IPH B7H

SADDR SPSR AFH

AUXR1 A7H

1

SBUF 9FH

1

TMOD TL0 TL1 TH0 TH1 AUXR 8FH

SP DPL DPH WDTD SPDR PCON 87H

SPCR D7H

IPAH F7H

FFH

EFH

E7H

C7H

97H

T3-4.3 384

©2001 Silicon Storage Technology, Inc. S71181-03-000 9/01 384

13

FlashFlex51 MCU

SST89E564 / SST89V564 / SST89E554 / SST89V554

Preliminary Specifications

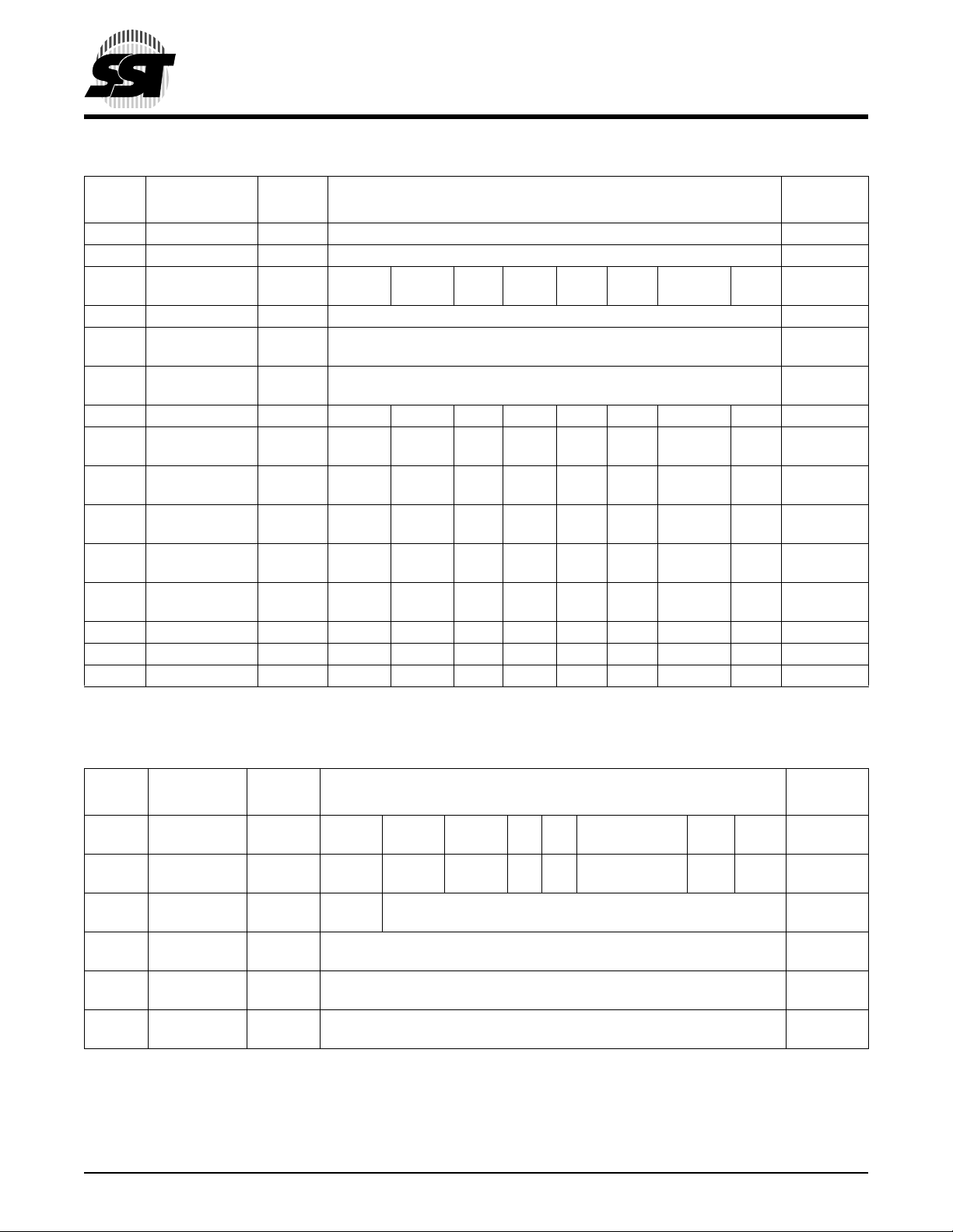

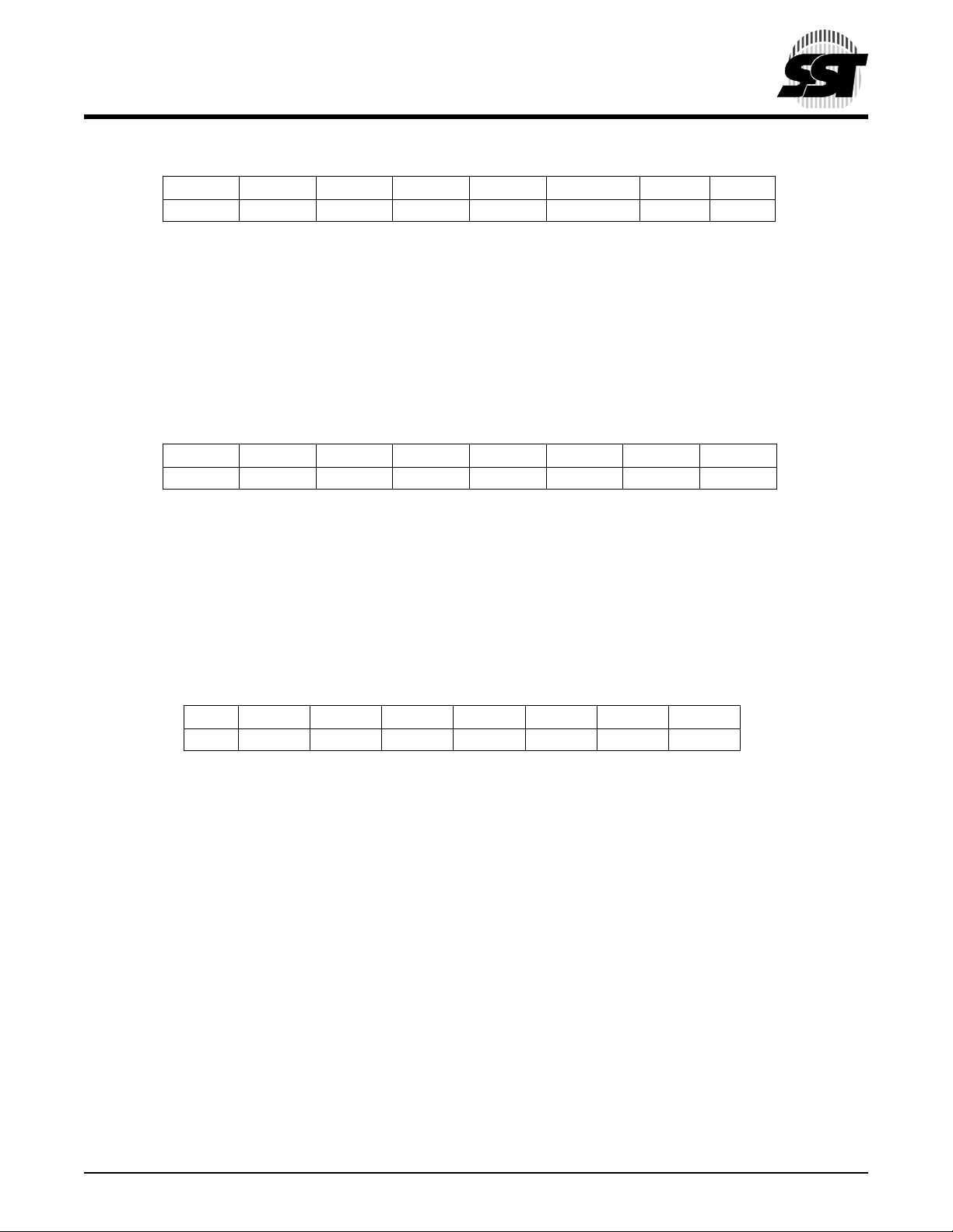

TABLE 3-5: CPU RELATED SFRS

Bit Address, Symbol, or Alternative Port Function

Symbol Description

1

ACC

1

B

PSW

Accumulator E0H ACC[7:0] 00H

B Register F0H B[7:0] 00H

1

Program Status

Direct

Address

D0H CY AC F0 RS1 RS0 OV F1 P 00H

Word

SP Stack Pointer 81H SP[7:0] 07H

DPL Data Pointer

82H DPL[7:0] 00H

Low

DPH Data Pointer

83H DPH[7:0] 00H

High

1

IE

IEA

Interrupt Enable A8H EA - ET2 ES0 ET1 EX1 ET0 EX0 40H

1

Interrupt

E8H - - - - EBO - - - xxxx0xxxb

Enable A

IP

1

Interrupt Priority

B8H - - PT2 PS PT1 PX1 PT0 PX0 xx000000b

Reg

IPH Interrupt Priority

B7H - - PT2H PSH PT1H PX1H PT0H PX0H xx000000b

Reg High

1

IPA

Interrupt Priority

F8H - - - - PBO - - - xxxx0xxxb

Reg A

IPAH Interrupt Priority

Reg A High

F7H - - - - PBO

H

- - - xxxx0xxxb

PCON Power Control 87H SMOD1 SMOD0 BOF POF GF1 GF0 PD IDL 00010000b

AUXR Auxiliary Reg 8EH - - - - - - EXTRAM AO xxxxxxx00b

AUXR1 Auxiliary Reg 1 A2H - - - - GF2 0 - DPS xxxx00x0b

1. Bit Addressable SFRs

RESET

ValueMSB LSB

T3-5.10 384

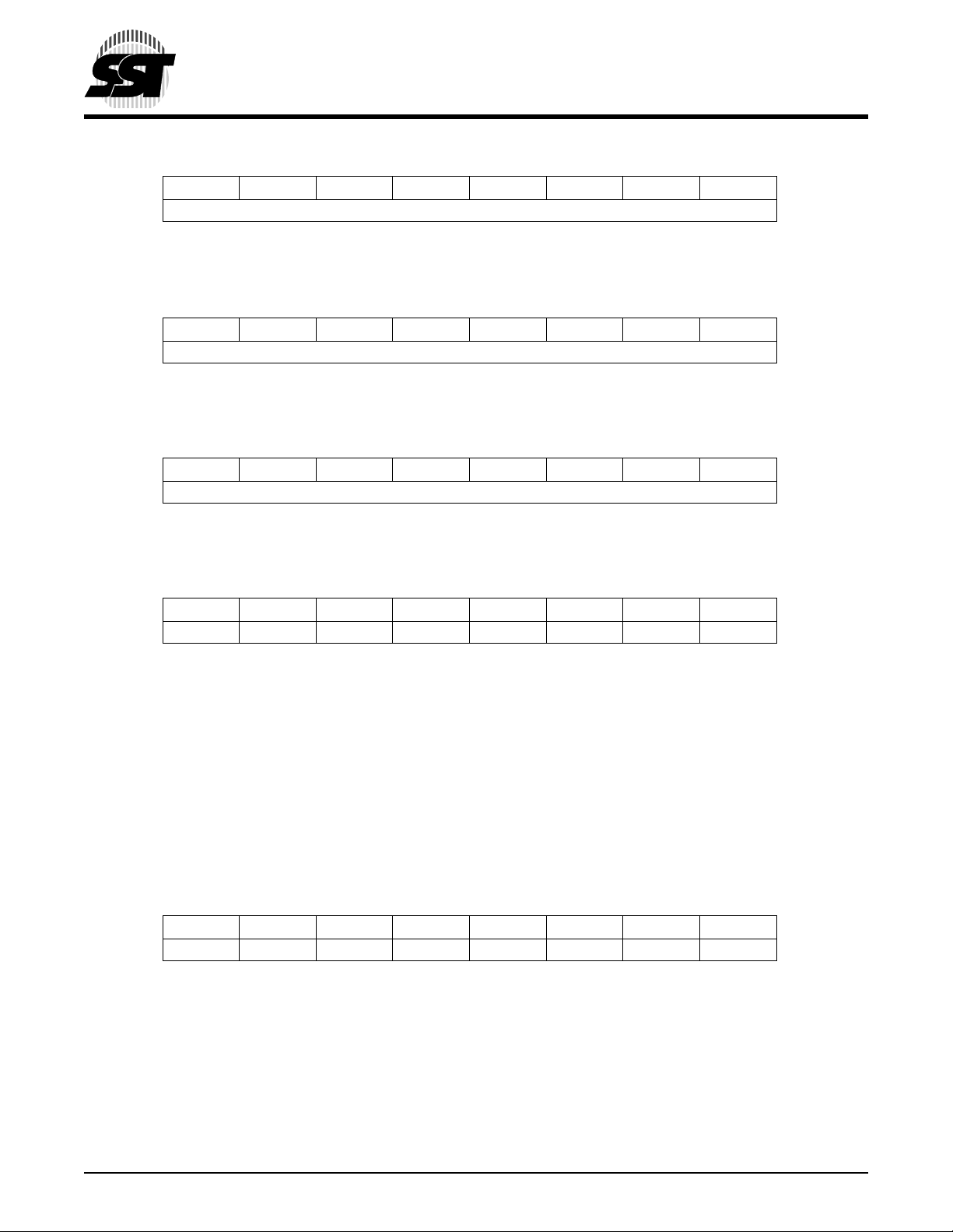

TABLE 3-6: FLASH MEMORY PROGRAMMING SFRS

Bit Address, Symbol, or Alternative Port Function

Symbol Description

SFST SuperFlash

Direct

Address

B6H SECD1 SECD2 SECD3 - - FLASH_BUSY - - xxxxx0xxb

Status

SFCF SuperFlash

B1H - IAPEN - - - - SWR BSEL x0xxxxxxb

Configuration

SFCM SuperFlash

B2H FIE FCM 00H

Command

SFDT SuperFlash

B5H SuperFlash Data Register 00H

Data

SFAL SuperFlash

B3H SuperFlash Low Order Byte Address Register - A

toA0 (SFAL) 00H

7

Address Low

SFAH SuperFlash

B4H SuperFlash High Order Byte Address Register - A

toA8 (SF AH) 00H

15

Address High

©2001 Silicon Storage Technology, Inc. S71181-03-000 9/01 384

14

RESET

ValueMSB LSB

T3-6.6 384

FlashFlex51 MCU

SST89E564 / SST89V564 / SST89E554 / SST89V554

Preliminary Specifications

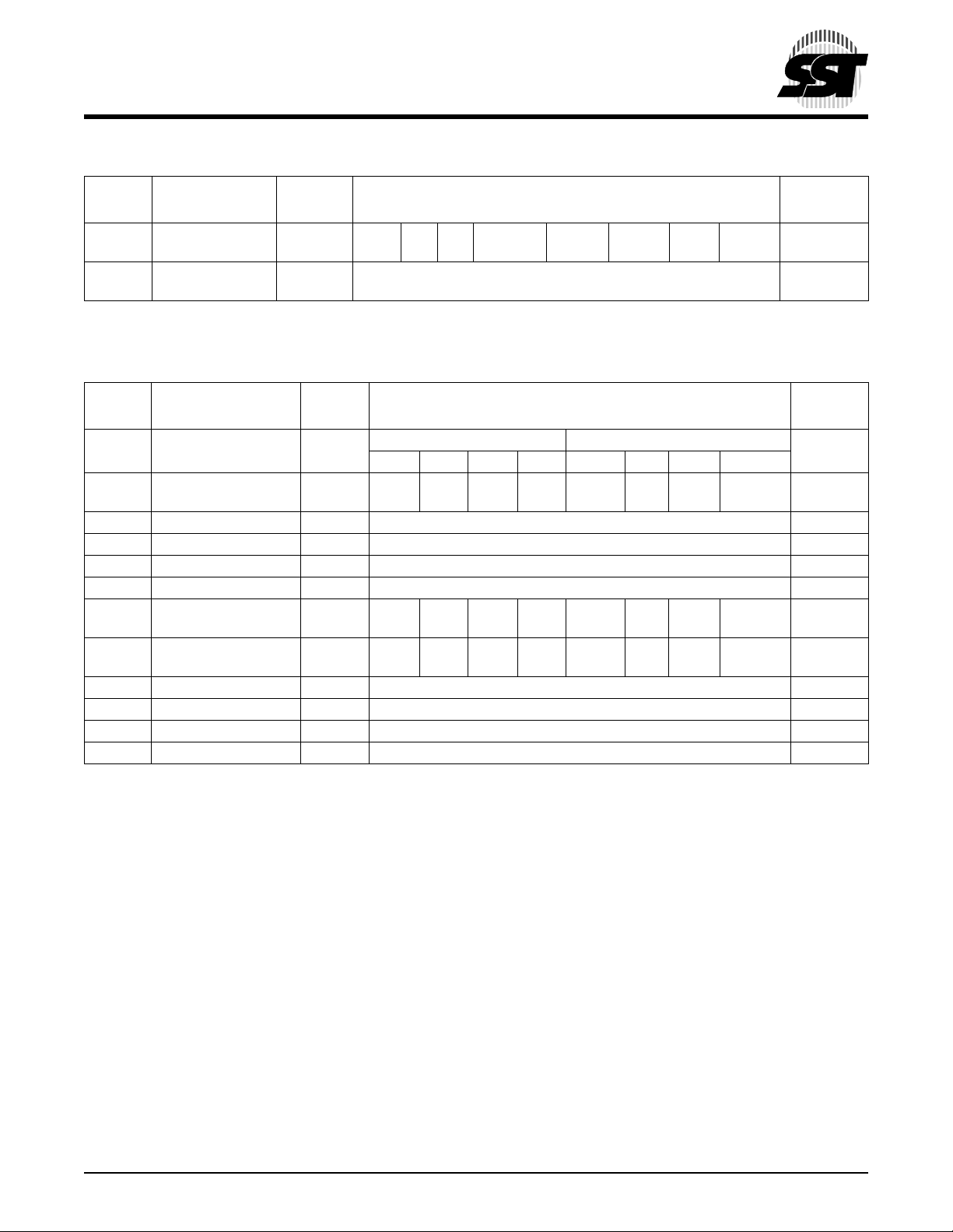

TABLE 3-7: WATCHDOG TIMER SFRS

Bit Address, Symbol, or Alternative Port Function

Symbol Description

1

WDTC

Watchdog Timer

Direct

Address

C0H - - - WDOUT WDRE WDTS WDT SWDT xxx00x00b

Control

WDTD Watchdog Timer

85H Watchdog Timer Data/Reload 00H

Data/Reload

1. Bit Addressable SFRs

TABLE 3-8: TIMER/COUNTERS SFRS

Direct

Symbol Description

TMOD Timer/Counter

Address

89H Timer 1 Timer 0 00H

Mode Control

1

TCON

Timer/Counter

88H TF1 TR1 TF0 TR0 IE1 IT1 IE0 IT0 00H

Control

TH0 Timer 0 MSB 8CH TH0[7:0] 00H

TL0 Timer 0 LSB 8AH TL0[7:0] 00H

TH1 Timer 1 MSB 8DH TH1[7:0] 00H

TL1 Timer 1 LSB 8BH TL1[7:0] 00H

1

T2CON

Timer / Counter 2

C8H TF2 EXF2 RCLK TCLK EXEN2 TR2 C/T2# CP/RL2# 00H

Control

T2MOD# Timer2

C9H---- --T2OEDCENxxxxxx00b

Mode Control

TH2 Timer 2 MSB CDH TH2[7:0] 00H

TL2 Timer 2 LSB CCH TL2[7:0] 00H

RCAP2H Timer 2 Capture MSB CBH RCAP2H[7:0] 00H

RCAP2L Timer 2 Capture LSB CAH RCAP2L[7:0] 00H

1. Bit Addressable SFRs

Bit Address, Symbol, or Alternative Port Function

GATE C/T# M1 M0 GATE C/T# M1 M0

RESET

ValueMSB LSB

RESET

ValueMSB LSB

T3-7.3 384

T3-8.3 384

©2001 Silicon Storage Technology, Inc. S71181-03-000 9/01 384

15

FlashFlex51 MCU

SST89E564 / SST89V564 / SST89E554 / SST89V554

Preliminary Specifications

TABLE 3-9: INTERFACE SFRS

Bit Address, Symbol, or Alternative Port Function

Symbol Description

Direct

Address

SBUF Serial Data Buffer 99H SBUF[7:0] Indete rminate

1

SCON

Serial Port Control 98H SM0/FE SM1 SM2 REN TB8 RB8 TI RI 00H

SADDR Slave Address A9H SADDR#[7:0] 00H

SADEN Slave Address

B9H SADEN#[7:0] 00H

Mask

SPCR SPI Control

D5H SPIE SPE DORD MSTR CPOL CPHA SPR1 SPR0 04H

Register

SPSR SPI Status

AAH SPIF WCOL 00H

Register

SPDR SPI Data Register 86H SPD7 SPD6 SPD5 SPD4 SPD3 SPD2 SPD1 SPD0 00H

1

P0

P1

P2

P3

Port 0 80H P0[7:0] FFH

1

Port 1 90H - - - - - - T2EX T2 FFH

1

Port 2 A0H P2[7:0] FFH

1

Port 3 B0H RD# WR# T1 T 0 INT1# INT0# TXD RXD FFH

1. Bit Addressable SFRs

RESET

ValueMSB LSB

T3-9.4 384

©2001 Silicon Storage Technology, Inc. S71181-03-000 9/01 384

16

FlashFlex51 MCU

SST89E564 / SST89V564 / SST89E554 / SST89V554

Preliminary Specifications

SuperFlash Status Register (SFST) (Read Only Register)

Location76543 2 10Reset Value

0B6H SECD1 SECD2 SECD3 - -

FLASH_BUSY

Symbol Function

SECD1 Security bit 1.

SECD2 Security bit 2.

SECD3 Security bit 3.

Please refer to Table 4-6 for security lock options.

FLASH_BUSYFlash operation completion polling bit.

1: Device is busy with flash operation.

0: Device has fully completed the last command.

SuperFlash Configuration Register (SFCF)

Location76543210Reset Value

0B1H - IAPEN ----

Symbol Function

IAPEN Enable IAP operation

0: IAP commands are disabled

1: IAP commands are enabled

SWR Software Reset

See “9.2 Software Reset” on page 43

BSEL Program memory block switching bit

See Figures 3-1 and 3-2.

- - xxxxx0xxb

SWR BSEL

x0xxxxxxb

SuperFlash Command Register (SFCM)

Location76543210Reset Value

0B2H FIE FCM6 FCM5 FCM4 FCM3 FCM2 FCM1 FCM0 00000000b

Symbol Function

FIE Flash Interrupt Enable.

0: INT1# is not reassigned.

1: INT1# is re-assigned to signal IAP operation completion.

External INT1# interrupts are ignored.

FCM[6:0] Flas h ope ration com man d

000_1011b Sector-Erase

000_1101b Block-Erase

000_1100b Byte-Verify

1

000_1110b Byte-Program

000_1111b Prog-SB1

000_0011b Prog-SB2

000_0101b Prog-SB3

000_1001b Prog-SC0

All other combinations are not implemented, and reserved for future use.

1. Byte-Verify has a single machine cycle latency and will not generate any INT1# interrupt regardless of FIE.

©2001 Silicon Storage Technology, Inc. S71181-03-000 9/01 384

17

FlashFlex51 MCU

SST89E564 / SST89V564 / SST89E554 / SST89V554

Preliminary Specifications

SuperFlash Data Register (SFDT)

Location76543210Reset Value

0B5H SuperFlash Data Register 00000000b

Symbol Function

SFDT Mailbox register for interfacing with flash memory block. (Data register).

SuperFlash Address Registers (SFAL)

Location76543210Reset Value

0B3H SuperFlash Low Order Byte Address Register 00000000b

Symbol Function

SFAL Mailbox register for interfacing with flash memory block. (Low order address register).

SuperFlash Address Registers (SFAH)

Location76543210Reset Value

0B4H SuperFlash High Order Byte Address Register 00000000b

Symbol Function

SFAH Mailbox register for interfacing with flash memory block. (High order address register).

Interrupt Enable (IE)

Location76543210Reset Value

A8H EA - ET2 ES ET1 EX1 ET0 EX0 00H

Symbol Function

EA Global Interrupt Enable.

0 = Disable

1 = Enable

ET2 Timer 2 Interrupt Enable.

ES Serial Interrupt Enable.

ET1 Timer 1 Interrupt Enable.

EX1 Extern al 1 Int errupt Enable.

ET0 Timer 0 Interrupt Enable.

EX0 Extern al 0 Int errupt Enable.

Interrupt Enable A (IEA)

Location76543210Reset Value

E8H----EBO---xxxx0xxxb

Symbol Function

EBO Brown-out Interrupt Enable.

1 = Enable the interrupt

0 = Disable the interrupt

©2001 Silicon Storage Technology, Inc. S71181-03-000 9/01 384

18

Loading...

Loading...