Silicon Storage Technology Inc SST34HF1681-90-4E-L1P, SST34HF1681-90-4C-L1P, SST34HF1681-70-4E-L1P, SST34HF1681-70-4C-L1P Datasheet

16 Mbit Concurrent SuperFlash + 8 Mbit SRAM ComboMemory

SST34HF1681

SST34HF16818 Mb Flash (x16) Concurrent SuperFlash ComboMemory

FEATURES:

Advance Specifications

• Flash Organization: 1M x16

• Dual-Bank Architecture for Concurrent

Read/Write Operation

– 16 Mbit: 12 Mbit + 4 Mbit

• SRAM Organization:

– 8 Mbit: 512K x16

• Single 2.7-3.3V Read and Write Operations

• Superior Reliability

– Endurance: 100,000 Cycles (typical)

– Greater than 100 years Data Retention

• Low Power Consumption:

– Active Current: 25 mA (typical)

– Standby Current: 20 µA (typical)

• Hardware Sector Protection (WP#)

– Protects 4 outer most sectors (4 KWord) in the

larger bank by holding WP# low and unprotects

by holding WP# high

• Hardware Reset Pin (RST#)

– Resets the internal state machine to reading

data array

• Sector-Erase Capability

– Uniform 1 KWord sectors

• Block-Erase Capability

– Uniform 32 KWord blocks

• Read Access Time

– Flash: 70 and 90 ns

– SRAM: 70 and 90 ns

• Latched Address and Data

• Fast Erase and Word-Program:

– Sector-Erase Time: 18 ms (typical)

– Block-Erase Time: 18 ms (typical)

– Chip-Erase Time: 70 ms (typical)

– Word-Program Time: 14 µs (typical)

– Chip Rewrite Time: 8 seconds (typical)

• Automatic Write Timing

V

– Internal

Generation

PP

• End-of-Write Detection

– Toggle Bit

– Data# Polling

– Ready/Busy# pin

• CMOS I/O Compatibility

• JEDEC Standard Command Set

• Conforms to Common Flash Memory Interface

(CFI)

• Packages Available

– 56-ball LFBGA (8mm x 10mm)

PRODUCT DESCRIPTION

The SST34HF1681 ComboMemory devices integrate a

1M x16 CMOS flash memory bank with a 512K x16 CMOS

SRAM memory bank in a Multi-Chip Package (MCP).

These devices are fabricated using SST’s proprietary, highperformance CMOS SuperFlash technology incorporating

the split-gate cell design and thick oxide tunneling injector

to attain better reliability and manufacturability compared

with alternate approaches. The SST34HF1681 devices are

ideal for applications such as cellular phones, GPSs, PDAs

and other portable electronic devices in a low power and

small form factor system.

The SST34HF1681 features dual flash memory bank

architecture allowing for concurrent operations between the

two flash memory banks and the SRAM. The devices can

read data from either bank while an Erase or Program

operation is in progress in the opposite bank. The two flash

memory banks are partitioned into 4 Mbit and 12 Mbit with

top or bottom sector protection options for storing boot

code, program code, configuration/parameter data and

user data.

©2001 Silicon Stor age Technology, Inc.

S71214-00-000 12/01 561

1

SST, the SST logo, and SuperFlash are Trademarks registered by Silicon Storage Technology, Inc. in the U.S. Patent and Trademark Office.

The SuperFlash technology provides fixed Erase and Program times, independent of the number of Erase/Program

cycles that have occurred. Therefore, the system software

or hardware does not have to be modified or de-rated as is

necessary with alternative flash technologies, whose Erase

and Program times increase with accumulated Erase/Program cycles. The SST34HF1681 devices offer a guaranteed endurance of 10,000 cycles. Data retention is rated at

greater than 100 years. With high performance Word-Program, the flash memory banks provide a typical Word-Program time of 14 µsec. The entire flash memory bank can

be erased and programmed word-by-word in typically 8

seconds for the SST34HF1681, when using interface features such as Toggle Bit or Data# Polling to indicate the

completion of Program operation. To protect against inadvertent flash write, the SST34HF1681 devices contain onchip hardware and software data protection schemes.

The flash and SRAM operate as two independent memory

banks with respective bank enable signals. The memory

bank selection is done by two bank enable signals. The

Concurrent SuperFlash, CSF, and ComboMemory are trademarks of Silicon Storage Technology, Inc.

These specifications are subject to change without notice.

16 Mbit Concurrent SuperFlash + 8 Mbit SRAM ComboMemory

SST34HF1681

Advance Specifications

SRAM bank enable signal, BES1# and BES2, selects the

SRAM bank. The flash memory bank enable signal, BEF#,

has to be used with Software Data Protection (SDP) command sequence when controlling the Erase and Program

operations in the flash memory bank. The memory banks

are superimposed in the same memory address space

where they share common address lines, data lines, WE#

and OE# which minimize power consumption and area.

Designed, manufactured, and tested for applications requiring low power and small form factor, the SST34HF1681 are

offered in both commercial and extended temperatures

and a small footprint package to meet board space constraint requirements.

Device Operation

The SST34HF1681 uses BES1#, BES2 and BEF# to control operation of either the flash or the SRAM memory

bank. When BEF# is low, the flash bank is activated for

Read, Program or Erase operation. When BES1# is low,

and BES2 is high the SRAM is activated for Read and

Write operation. BEF# and BES1# cannot be at low level,

and BES2 cannot be at high level at the same time. If all

bank enable signals are asserted, bus contention will

result and the device may suffer permanent damage.

All address, data, and control lines are shared by flash and

SRAM memory banks which minimizes power consumption and loading. The device goes into standby when BEF#

and BES1# bank enables are raised to V

(Logic High) or

IHC

when BEF# is high and BES2 is low.

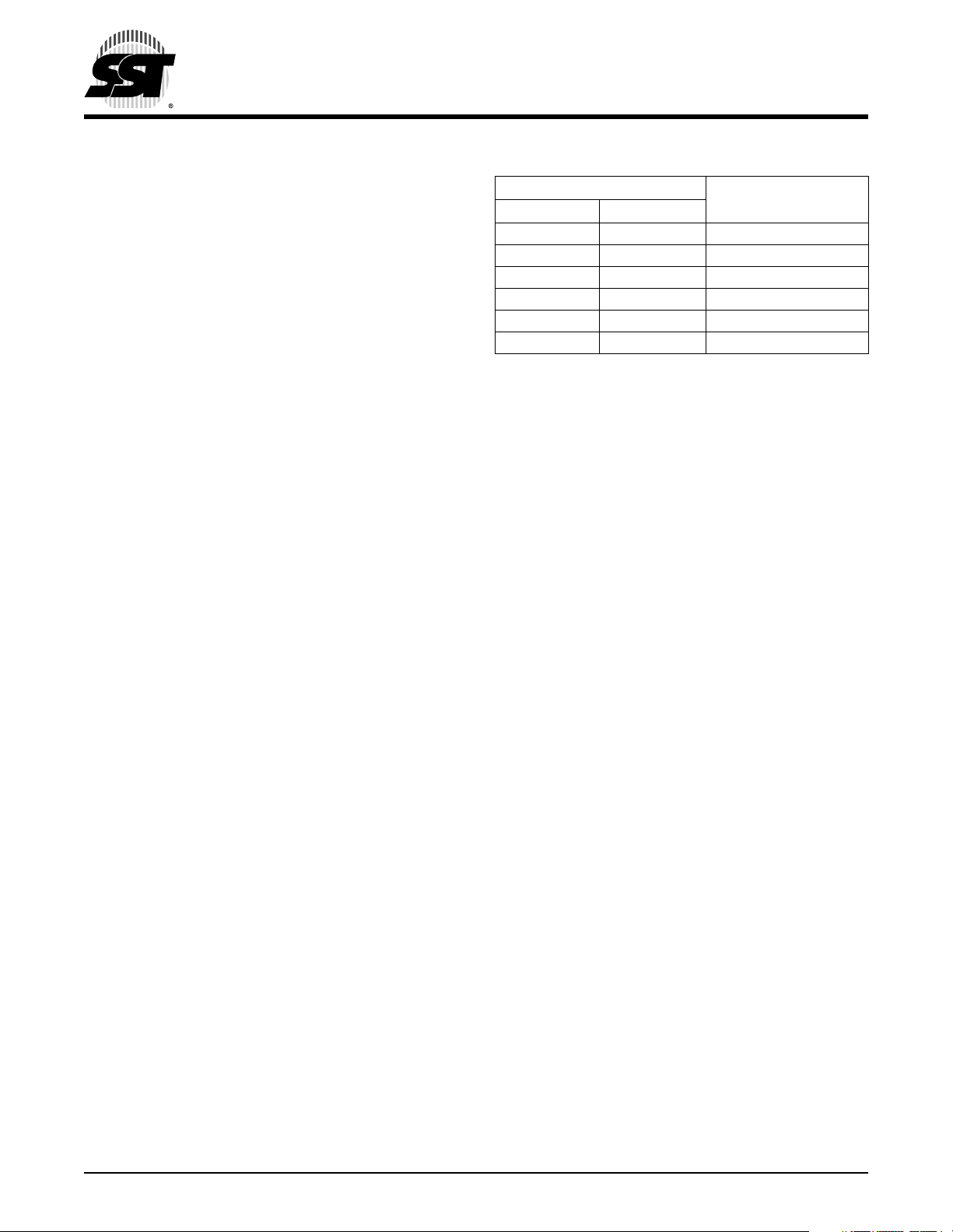

Concurrent Read/Write Operation

Dual bank architecture of SST34HF1681 devices allows

the Concurrent Read/Write operation whereby the user

can read from one bank while program or erase in the

other bank. This operation can be used when the user

needs to read system code in one bank while updating

data in the other bank. See Figure 1 for Dual-Bank Memory

Organization.

ONCURRENT READ/WRITE STATE TABLE

C

Flash

SRAMBank 1 Bank 2

Read Write No Operation

Write Read No Operation

Write No Operation Read

No Operation Write Read

Write No Operation Write

No Operation Write Write

Note: For the purposes of this table, write means to Block-, Sector,

or Chip-Erase, or Word-Program as applicable to the

appropriate bank.

Flash Read Operation

The Read operation of the SST34HF1681 is controlled by

BEF# and OE#, both have to be low for the system to

obtain data from the outputs. BEF# is used for device

selection. When BEF# is high, the chip is deselected and

only standby power is consumed. OE# is the output control

and is used to gate data from the output pins. The data bus

is in high impedance state when either BEF# or OE# is

high. Refer to the Read cycle timing diagram for further

details (Figure 6).

Flash Word-Program Operation

The SST34HF1681 are programmed on a word-by-word

basis. Before Program operations, the memory must be

erased first. The Program operation consists of three steps.

The first step is the three-byte load sequence for Software

Data Protection. The second step is to load word address

and word data. During the Word-Program operation, the

addresses are latched on the falling edge of either BEF# or

WE#, whichever occurs last. The data is latched on the rising edge of either BEF# or WE#, whichever occurs first.

The third step is the internal Program operation which is initiated after the rising edge of the fourth WE# or BEF#,

whichever occurs first. The Program operation, once initiated, will be completed typically within 10 µs. See Figures 7

and 8 for WE# and BEF# controlled Program operation timing diagrams and Figure 21 for flowcharts. During the Program operation, the only valid reads are Data# Polling and

Toggle Bit. During the internal Program operation, the host

is free to perform additional tasks. Any commands issued

during the internal Program operation are ignored.

©2001 Silicon Storage Technology, Inc. S71214-00-000 12/01 561

2

16 Mbit Concurrent SuperFlash + 8 Mbit SRAM ComboMemory

SST34HF1681

Advance Specifications

Flash Sector/Block-Erase Operation

The Sector/Block-Erase operation allows the system to

erase the device on a sector-by-sector or block-by-block

basis. The SST34HF1681 offer both Sector-Erase and

Block-Erase mode. The sector architecture is based on

uniform sector size of 1 KWord. The Block-Erase mode is

based on uniform block size of 32 KWord. The SectorErase operation is initiated by executing a six-byte command sequence with Sector-Erase command (30H) and

sector address (SA) in the last bus cycle. The Block-Erase

operation is initiated by executing a six-byte command

sequence with Block-Erase command (50H) and block

address (BA) in the last bus cycle. The sector or block

address is latched on the falling edge of the sixth WE#

pulse, while the command (30H or 50H) is latched on the

rising edge of the sixth WE# pulse. The internal Erase

operation begins after the sixth WE# pulse. See Figures 12

and 13 for timing waveforms. Any commands issued during

the Sector- or Block-Erase operation are ignored.

Flash Chip-Erase Operation

The SST34HF1681 provide a Chip-Erase operation, which

allows the user to erase all unprotected sectors/blocks to

the “1” state. This is useful when the device must be quickly

erased.

The Chip-Erase operation is initiated by executing a sixbyte command sequence with Chip-Erase command (10H)

at address 5555H in the last byte sequence. The Erase

operation begins with the rising edge of the sixth WE# or

BEF#, whichever occurs first. During the Erase operation,

the only valid read is Toggle Bits or Data# Polling. See

Table 4 for the command sequence, Figure 11 for timing

diagram, and Figure 24 for the flowchart. Any commands

issued during the Chip-Erase operation are ignored.

Flash Write Operation Status Detection

The SST34HF1681 provide one hardware and two software means to detect the completion of a Write (Program

or Erase) cycle, in order to optimize the system Write

cycle time. The hardware detection uses the Ready/

Busy# (RY/BY#) pin. The software detection includes two

status bits: Data# Polling (DQ

The End-of-Write detection mode is enabled after the rising edge of WE#, which initiates the internal Program or

Erase operation.

The actual completion of the nonvolatile write is asynchronous with the system; therefore, either a Ready/Busy# (RY/

BY#), Data# Polling (DQ

) or Toggle Bit (DQ6) read may be

7

simultaneous with the completion of the Write cycle. If this

occurs, the system may possibly get an erroneous result,

) and Toggle Bit (DQ6).

7

i.e., valid data may appear to conflict with either DQ

. In order to prevent spurious rejection, if an erroneous

DQ

6

7

or

result occurs, the software routine should include a loop to

read the accessed location an additional two (2) times. If

both reads are valid, then the device has completed the

Write cycle, otherwise the rejection is valid.

Ready/Busy# (RY/BY#)

The SST34HF1681 includes a Ready/Busy# (RY/BY#)

output signal. During any SDP initiated operation, e.g.,

Erase, Program, CFI or ID Read operation, RY/BY# is

actively pulled low, indicating a SDP controlled operation is

in Progress. The status of RY/BY# is valid after the rising

edge of fourth WE# (or CE#) pulse for Program operation.

For Sector-, Block- or Bank-Erase, the RY/BY# is valid after

the rising edge of sixth WE# or (CE#) pulse. RY/BY# is an

open drain output that allows several devices to be tied in

parallel to V

via an external pull up resistor. Ready/

DD

Busy# is in high impedance whenever OE# or CE# is high

or RST# is low. There is a 1 µs bus recovery time (T

BR

required before valid data can be read on the data bus.

New commands can be entered immediately after RY/BY#

goes high.

Flash Data# Polling (DQ7)

When the SST34HF1681 are in the internal Program operation, any attempt to read DQ

will produce the comple-

7

ment of the true data. Once the Program operation is

completed, DQ

though DQ

will produce true data. Note that even

7

may have valid data immediately following the

7

completion of an internal Write operation, the remaining

data outputs may still be invalid: valid data on the entire

data bus will appear in subsequent successive Read

cycles. During internal Erase operation, any attempt to

read DQ

tion is completed, DQ

(DQ

will produce a ‘0’. Once the internal Erase opera-

7

will produce a ‘1’. The Data# Polling

7

) is valid after the rising edge of fourth WE# (or BEF#)

7

pulse for Program operation. For Sector-, Block- or ChipErase, the Data# Polling (DQ

) is valid after the rising edge

7

of sixth WE# (or BEF#) pulse. See Figure 9 for Data# Polling (DQ

There is a 1 µs bus recovery time (T

) timing diagram and Figure 22 for a flowchart.

7

) required before

BR

valid data can be read on the data bus. New commands

can be entered immediately after DQ

becomes true data.

7

Flash Toggle Bits (DQ6)

During the internal Program or Erase operation, any consecutive attempts to read DQ

and 0s, i.e., toggling between 1 and 0. When the internal

Program or Erase operation is completed, the DQ

stop toggling. The device is then ready for the next oper-

will produce alternating 1s

6

bit will

6

)

©2001 Silicon Storage Technology, Inc. S71214-00-000 12/01 561

3

16 Mbit Concurrent SuperFlash + 8 Mbit SRAM ComboMemory

SST34HF1681

Advance Specifications

ation. The Toggle Bit (DQ6) is valid after the rising edge

of fourth WE# (or BEF#) pulse for Program operation.

For Sector-, Block- or Chip-Erase, the Toggle Bit (DQ

6

) is

valid after the rising edge of sixth WE# (or BEF#) pulse.

See Figure 10 for Toggle Bit timing diagram and Figure

22 for a flowchart. There is a 1 µs bus recovery time (T

BR

required before valid data can be read on the data bus.

New commands can be entered immediately after DQ

6

no

longer toggles.

Data Protection

The SST34HF1681 provide both hardware and software

features to protect nonvolatile data from inadvertent writes.

Hardware Data Protection

Noise/Glitch Protection: A WE# or BEF# pulse of less than

5 ns will not initiate a Write cycle.

Power Up/Down Detection: The Write operation is

V

DD

inhibited when V

Write Inhibit Mode:

is less than 1.5V.

DD

Forcing OE# low, BEF# high, or WE#

high will inhibit the Write operation. This prevents inadvertent writes during power-up or power-down.

Hardware Block Protection

The SST34HF1681 provide a hardware block protection

which protects the outermost 4 KWord in Bank 1. The block

is protected when WP# is held low. See Figure 1 for BlockProtection location.

A user can disable block protection by driving WP# high

thus allowing erase or program of data into the protected

sectors. WP# must be held high prior to issuing the write

command and remain stable until after the entire Write

operation has completed.

Hardware Reset (RST#)

The RST# pin provides a hardware method of resetting the

device to read array data. When the RST# pin is held low

for at least T

return to Read mode (see Figure 18). When no internal

Program/Erase operation is in progress, a minimum period

of T

RHR

Read can take place (see Figure 17).

The Erase operation that has been interrupted needs to be

reinitiated after the device resumes normal operation mode

to ensure data integrity. See Figures 17 and 18 for timing

diagrams.

any in-progress operation will terminate and

RP,

is required after RST# is driven high before a valid

Software Data Protection (SDP)

The SST34HF1681 provide the JEDEC standard Software

Data Protection scheme for all data alteration operations,

i.e., Program and Erase. Any Program operation requires

the inclusion of the three-byte sequence. The three-byte

)

load sequence is used to initiate the Program operation,

providing optimal protection from inadvertent Write operations, e.g., during the system power-up or power-down.

Any Erase operation requires the inclusion of six-byte

sequence. The SST34HF1681 are shipped with the Software Data Protection permanently enabled. See Table 4 for

the specific software command codes. During SDP command sequence, invalid commands will abort the device to

Read mode within T

. The contents of DQ15-DQ8 are

RC

“Don’t Care” during any SDP command sequence.

Common Flash Memory Interface (CFI)

The SST34HF1681 also contain the CFI information to

describe the characteristics of the device. In order to enter

the CFI Query mode, the system must write three-byte

sequence, same as Software ID Entry command with 98H

(CFI Query command) to address 555H in the last byte

sequence. Once the device enters the CFI Query mode, the

system can read CFI data at the addresses given in Tables

5 through 7. The system must write the CFI Exit command

to return to Read mode from the CFI Query mode.

Product Identification

The Product Identification mode identifies the device as the

SST34HF1681 and manufacturer as SST. This mode may

be accessed by software operations only. The hardware

device ID Read operation, which is typically used by programmers cannot be used on this device because of the

shared lines between flash and SRAM in the multi-chip

package. Therefore, application of high voltage to pin A

may damage this device. Users may use the software

Product Identification operation to identify the part (i.e.,

using the device ID) when using multiple manufacturers in

the same socket. For details, see Tables 3 and 4 for software operation, Figure 14 for the Software ID Entry and

Read timing diagram and Figure 23 for the ID Entry command sequence flowchart.

TABLE 1: P

Manufacturer’s ID 0000H 00BFH

Device ID

SST34HF1681 0001H 2761H

RODUCT IDENTIFICATION

ADDRESS DATA

9

T1.0 561

©2001 Silicon Storage Technology, Inc. S71214-00-000 12/01 561

4

16 Mbit Concurrent SuperFlash + 8 Mbit SRAM ComboMemory

SST34HF1681

Advance Specifications

Product Identification Mode Exit/

CFI Mode Exit

In order to return to the standard Read mode, the Software

Product Identification mode must be exited. Exit is accomplished by issuing the Software ID Exit command

sequence, which returns the device to the Read mode.

This command may also be used to reset the device to the

Read mode after any inadvertent transient condition that

apparently causes the device to behave abnormally, e.g.,

not read correctly. Please note that the Software ID Exit/

CFI Exit command is ignored during an internal Program or

Erase operation. See Table 4 for software command

codes, Figure 16 for timing waveform and Figure 23 for a

flowchart.

SRAM Operation

With BES1# low, BES2 and BEF# high, the

SST34HF1681 operates as 512K x16 CMOS SRAM,

with fully static operation requiring no external clocks or

timing strobes. The SST34HF1681 SRAM is mapped

into the first 512 KWord address space. When BES1#,

BEF# are high and BES2 is low, all memory banks are

deselected and the device enters standby. Read and

Write cycle times are equal. The control signals UBS#

and LBS# provide access to the upper data byte and

lower data byte. See Table 3 for SRAM Read and Write

data byte control modes of operation.

SRAM Read

The SRAM Read operation of the SST34HF1681 is controlled by OE# and BES1#, both have to be low with WE#

and BES2 high for the system to obtain data from the outputs. BES1# and BES2 are used for SRAM bank selection.

OE# is the output control and is used to gate data from the

output pins. The data bus is in high impedance state when

OE# is high. Refer to the Read cycle timing diagram, Figure 3, for further details.

SRAM Write

The SRAM Write operation of the SST34HF1681 is controlled by WE# and BES1#, both have to be low, BES2

have to be high for the system to write to the SRAM. During

the Word-Write operation, the addresses and data are referenced to the rising edge of either BES1#, WE#, or the

falling edge of BES2 whichever occurs first. The write time

is measured from the last falling edge of BES#1 or WE# or

the rising edge of BES2 to the first rising edge of BES1#, or

WE# or the falling edge of BES2. Refer to the Write cycle

timing diagram, Figures 4 and 5, for further details.

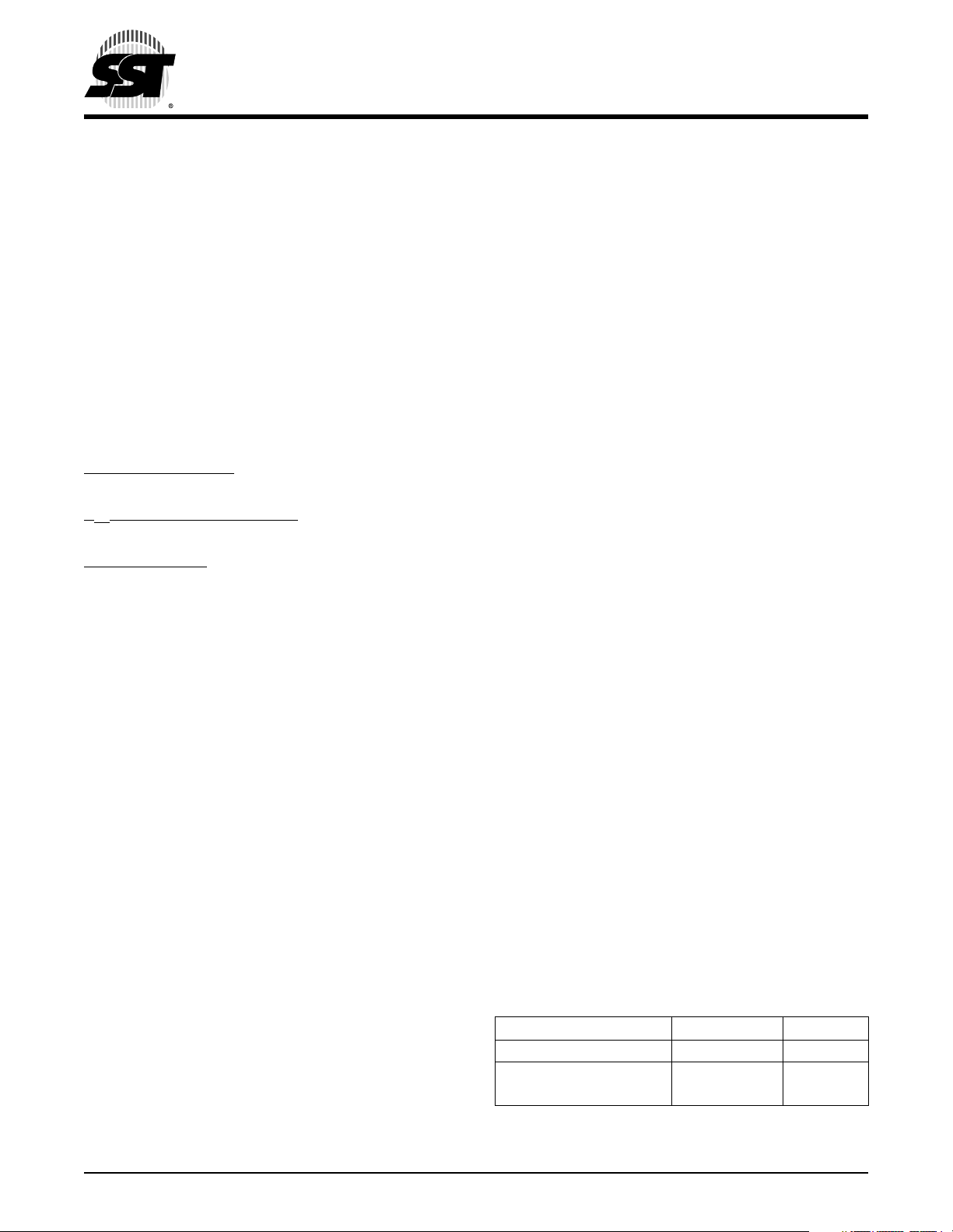

FUNCTIONAL BLOCK DIAGRAM

- A

A

MS

0

RST#

BEF#

WP#

LBS#

UBS#

WE#

OE#

BES1#

BES2

RY/BY#

AMS = Most significant address

Address

Buffers

Control

Logic

Address

Buffers

SuperFlash Memory

(Bank 1)

SuperFlash Memory

(Bank 2)

8 Mbit

SRAM

I/O Buffers

561 ILL B1.2

DQ15 - DQ

0

©2001 Silicon Storage Technology, Inc. S71214-00-000 12/01 561

5

16 Mbit Concurrent SuperFlash + 8 Mbit SRAM ComboMemory

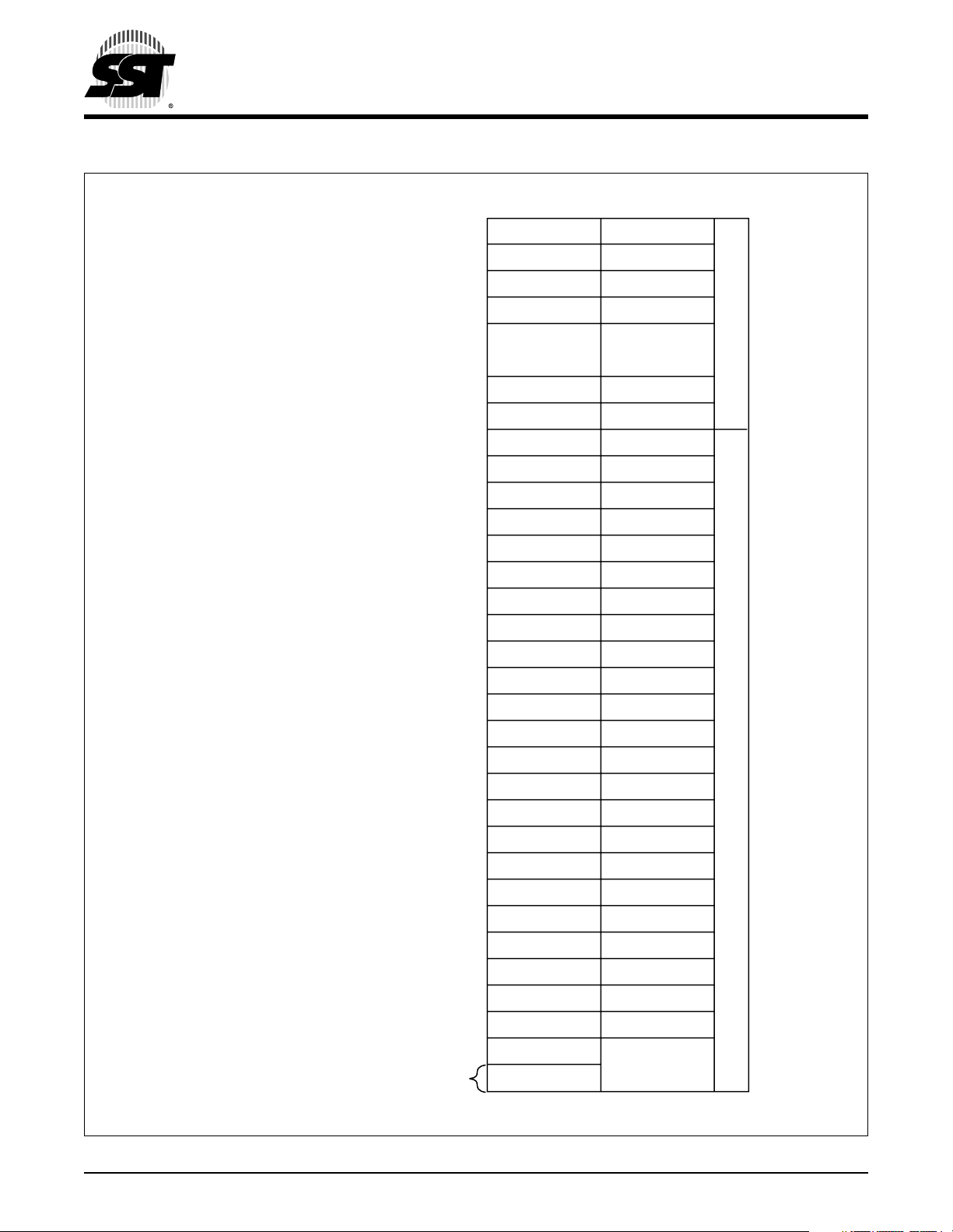

Bottom Sector Protection; 32 KWord Blocks; 1 KWord Sectors

SST34HF1681

Advance Specifications

4 KWord Sector Protection

(Four 1 KWord Sectors)

FFFFFH

F8000H

F7FFFH

F0000H

EFFFFH

E8000H

E7FFFH

E0000H

DFFFFH

D8000H

D7FFFH

D0000H

CFFFFH

C8000H

C7FFFH

C0000H

BFFFFH

B8000H

B7FFFH

B0000H

AFFFFH

A8000H

A7FFFH

A0000H

9FFFFH

98000H

97FFFH

90000H

8FFFFH

88000H

87FFFH

80000H

7FFFFH

78000H

77FFFH

70000H

6FFFFH

68000H

67FFFH

60000H

5FFFFH

58000H

57FFFH

50000H

4FFFFH

48000H

47FFFH

40000H

3FFFFH

38000H

37FFFH

30000H

2FFFFH

28000H

27FFFH

20000H

1FFFFH

18000H

17FFFH

10000H

00FFFFH

008000H

007FFFH

001000H

000FFFH

000000H

Block 31

Block 30

Block 29

Block 28

Block 27

Block 26

Block 25

Block 24

Block 23

Block 22

Block 21

Block 20

Block 19

Block 18

Block 17

Block 16

Block 15

Block 14

Block 13

Block 12

Block 11

Block 10

Block 9

Block 8

Block 7

Block 6

Block 5

Block 4

Block 3

Block 2

Block 1

Block 0

Bank 2

Bank 1

561 ILL F02.0

FIGURE 1: SST34HF1681, 1 MBIT X 16 CONCURRENT SUPERFLASH DUAL-BANK MEMORY ORGANIZATION

©2001 Silicon Storage Technology, Inc. S71214-00-000 12/01 561

6

16 Mbit Concurrent SuperFlash + 8 Mbit SRAM ComboMemory

SST34HF1681

Advance Specifications

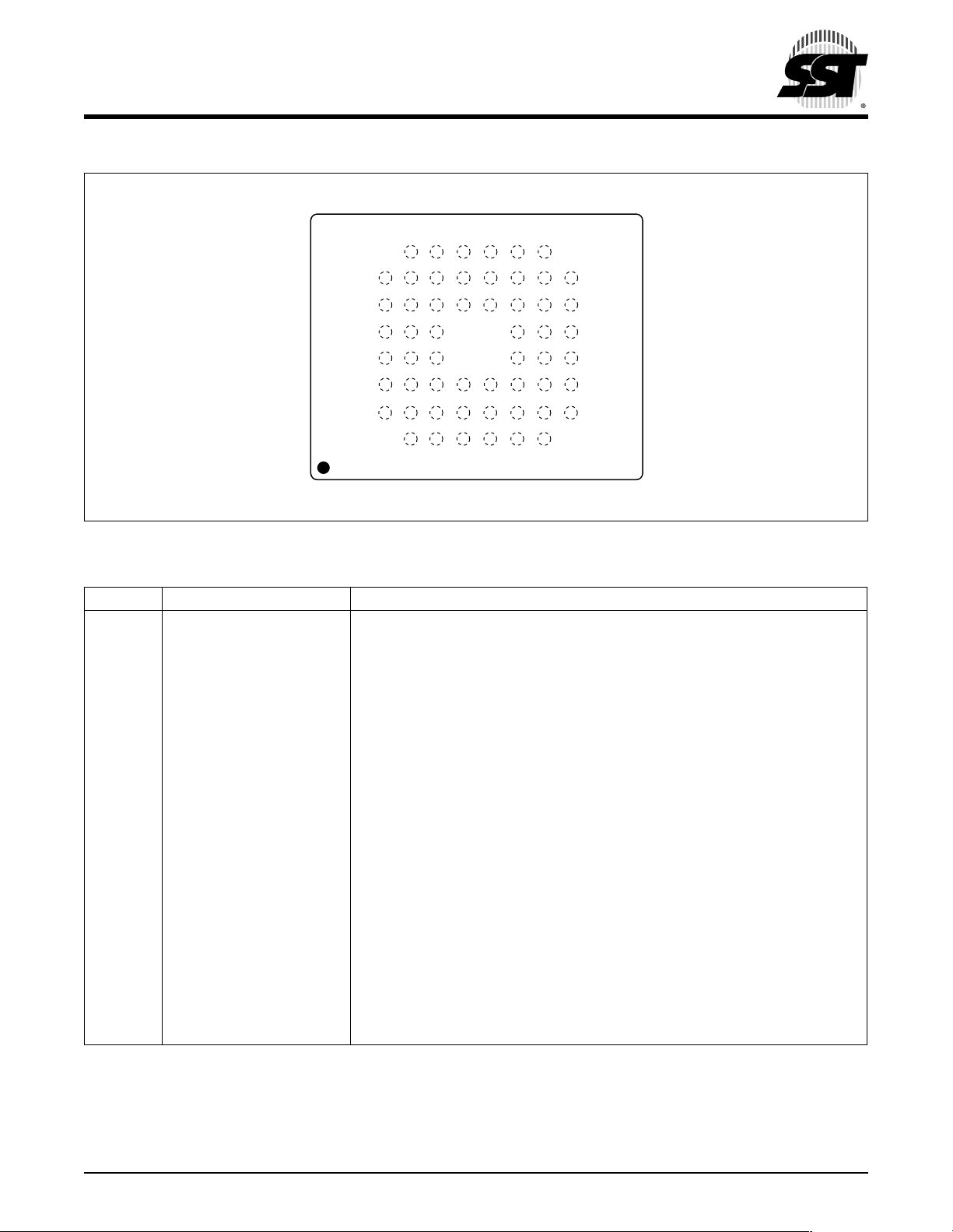

TOP VIEW (balls facing down)

8

7

6

5

4

3

2

1

A11

A8

WE#

WP#

LBS#

A7

A15

A12

A19

BES2

RST#

UBS#

A6

A3

NC

A13

A9

NC

RY/BY#

A18

A5

A2

NC

A14

A10

A17

A4

A1

A16

NC

DQ6

DQ1

V

A0

NC

V

SS

DQ7

DQ15

DQ13

DQ4

DQ3

DQ9

OE#

SS

BEF#

DQ12

V

DDS

V

DDF

DQ10

DQ0

BES1#

DQ14

DQ5

NC

DQ11

DQ2

DQ8

A B C D E F G H

SST34HF1681

561 ILL F03.0

FIGURE 2: PIN ASSIGNMENTS FOR 56-BALL LFBGA (8MM X 10MM) COMBOMEMORY PINOUT

TABLE 2: PIN DESCRIPTION

Symbol Pin Name Functions

1

A

to A

MS

DQ15-DQ0Data Inputs/Outputs To output data during Read cycles and receive input data during Write cycles.

BEF# Flash Memory Bank Enable To activate the Flash memory bank when BEF# is low

BES1# SRAM Memory Bank Enable To activate the SRAM memory bank when BES1# is low

BES2 SRAM Memory Bank Enable To activate the SRAM memory bank when BES2 is high

OE# Output Enable To gate the data output buffers

WE# Write Enable To control the Write operations

UBS# Upper Byte Control (SRAM) To enable DQ

LBS# Lower Byte Control (SRAM) To enable DQ7-DQ

WP# Write Protect To protect and unprotect sectors from Erase or Program operation

RST# Reset To Reset and return the device to Read mode

RY/BY# Ready/Busy# To output the status of a Program or Erase Operation

V

SS

V

F

DD

V

S

DD

NC No Connection Unconnected pins

1. AMS = Most Significant Address

Address Inputs To provide flash address, A19-A0.

0

To provide SRAM address, A

18-A0

Data is internally latched during a flash Erase/Program cycle. The outputs are in

tri-state when OE# is high or BES1# is high or BES2 is low and BEF# is high.

-DQ

15

8

0

RY/BY# is a open drain output, so a 10KΩ - 100KΩ pull-up resistor is required to

allow RY/BY# to transition high indicating the device is ready to read.

Ground

Power Supply (Flash) 2.7-3.3V Power Supply to Flash only

Power Supply (SRAM) 2.7-3.3V Power Supply to SRAM only

T2.1 561

©2001 Silicon Storage Technology, Inc. S71214-00-000 12/01 561

7

16 Mbit Concurrent SuperFlash + 8 Mbit SRAM ComboMemory

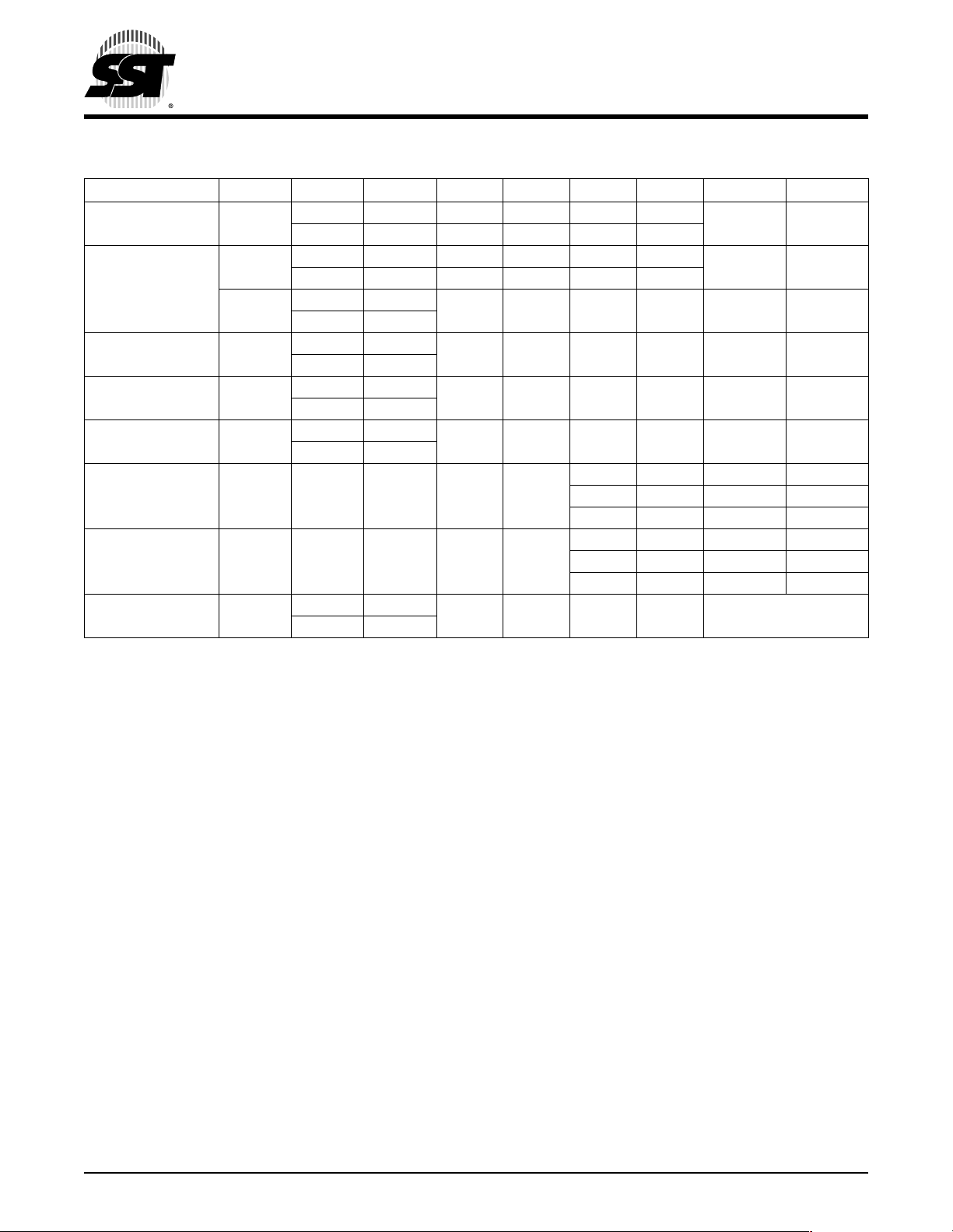

TABLE 3: OPERATIONAL MODES SELECTION

Mode BEF# BES1# BES2

Full Standby V

Output Disable V

Flash Read V

Flash Write V

Flash Erase V

IH

IH

V

IL

IL

IL

IL

SRAM Read VIH VILV

SRAM Write V

Product

Identification

1. X can be VIL or VIH, but no other value.

2. Do not apply BEF# = V

3. Software mode only

4. With A

3

= 0; SST Manufacturer’s ID = 00BFH, is read with A0=0,

19-A1

IH

V

IL

, BES1# = VIL and BES2 = VIH at the same time

IL

SST34HF1681 Device ID = 2761H, is read with A

V

IH

XV

V

IL

V

IL

V

IH

XV

V

IH

XV

VIH X V

XV

VIH XVIHV

XV

V

IL

VIH X V

XV

SST34HF1681

Advance Specifications

1

2

OE# WE# LBS# UBS# DQ

0-7

X XXXXHIGH-ZHIGH-Z

IL

V

IH

V

IH

XVIHV

IL

XVILV

IL

IL

IL

IH

V

IH

IL

XXXX

V

IH

XXVIHV

IH

V

IL

XVILV

IL

V

IH

IH

IH

V

IL

IL

V

IH

V

IH

=1

0

X X HIGH-Z HIGH-Z

IH

X X HIGH-Z HIGH-Z

XXD

XX DIND

XX X X

VIL VILD

V

IH

V

IL

IL

V

IH

V

IL

V

IL

V

IH

V

IL

V

IL

V

IH

X X Manufacturer’s ID4

OUT

OUT

HIGH-Z D

D

OUT

D

IN

HIGH-Z D

D

IN

Device ID

DQ

8-15

D

OUT

IN

D

OUT

OUT

HIGH-Z

D

IN

IN

HIGH-Z

4

T3.2 561

©2001 Silicon Storage Technology, Inc. S71214-00-000 12/01 561

8

16 Mbit Concurrent SuperFlash + 8 Mbit SRAM ComboMemory

SST34HF1681

Advance Specifications

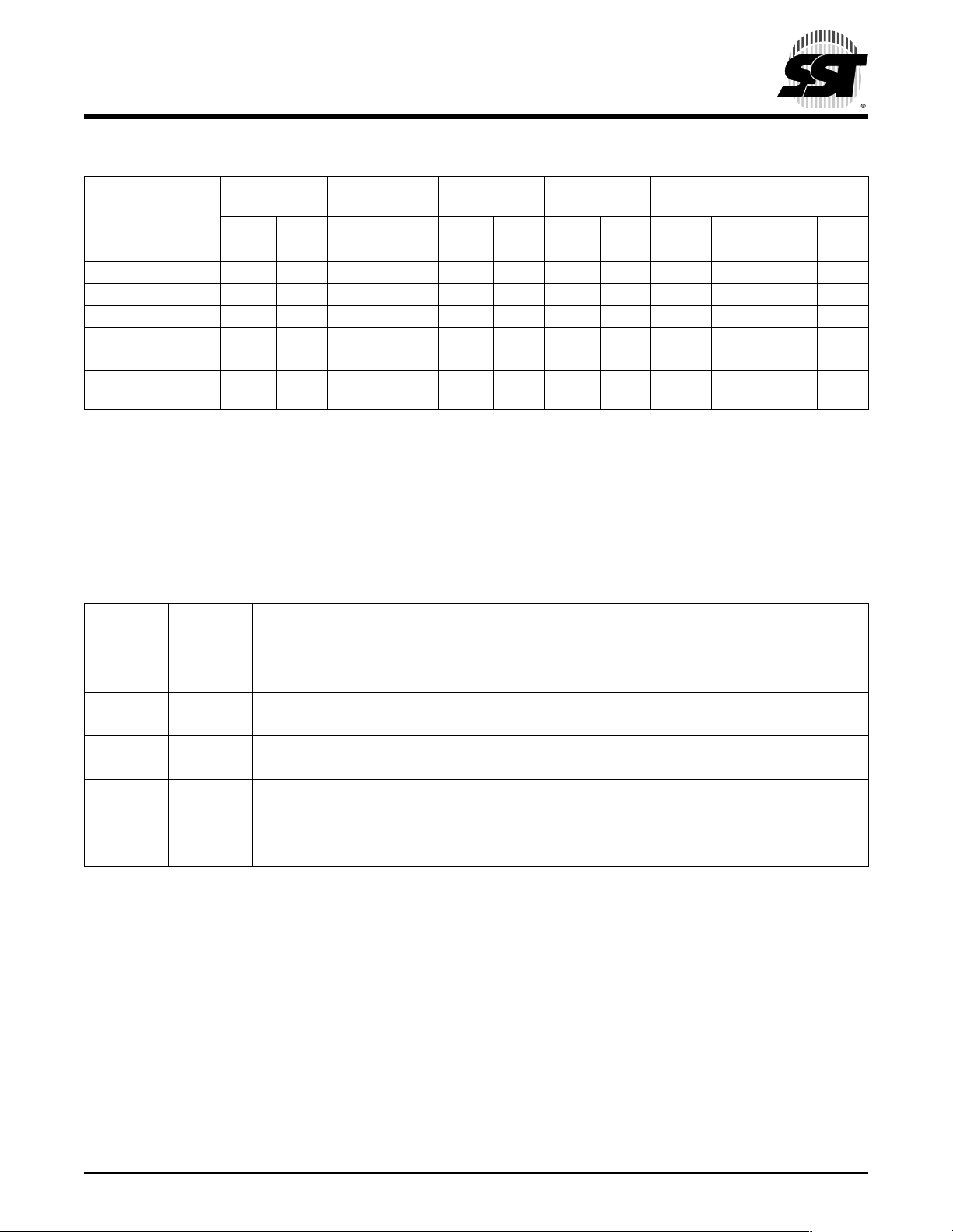

TABLE 4: SOFTWARE COMMAND SEQUENCE

Command

Sequence

Word-Program 5555H AAH 2AAAH 55H 5555H A0H WA3Data

Sector-Erase 5555H AAH 2AAAH 55H 5555H 80H 5555H AAH 2AAAH 55H SA

Block-Erase 5555H AAH 2AAAH 55H 5555H 80H 5555H AAH 2AAAH 55H BA

Chip-Erase 5555H AAH 2AAAH 55H 5555H 80H 5555H AAH 2AAAH 55H 5555H 10H

Software ID Entry55555H AAH 2AAAH 55H 5555H 90H

CFI Query Entry

5

Software ID Exit/

CFI Exit

6

1. Address format A14-A0 (Hex),Address A

2. Data format DQ

3. WA = Program Word address

4. SA

for Sector-Erase; uses A19-A11 address lines

X

, for Block-Erase; uses A19-A15 address lines

BA

X

5. The device does not remain in Software Product Identification Mode if powered down.

6. With A

= 0; SST Manufacturer’s ID = 00BFH, is read with A0=0

20-A1

1st Bus

Write Cycle

2nd Bus

Write Cycle

3rd Bus

Write Cycle

4th Bus

Write Cycle

5th Bus

Write Cycle

6th Bus

Write Cycle

Addr1Data2Addr1Data2Addr1Data2Addr1Data2Addr1Data2Addr1Data

4

X

4

X

5555H AAH 2AAAH 55H 5555H 98H

5555H AAH 2AAAH 55H 5555H F0H

can be VIL or VIH, but no other value, for the Command sequence.

-DQ8 can be VIL or VIH, but no other value, for Command sequence.

15

SST34HF1681 Device ID = 2761H, is read with A

19-A15

=1.

0

30H

50H

T4.1 561

2

TABLE 5: CFI QUERY IDENTIFICATION STRING

1

Address Data Data

10H 0051H Query Unique ASCII string “QRY”

11H 0052H

12H 0059H

13H 0001H Primary OEM command set

14H 0007H

15H 0000H Address for Primary Extended Table

16H 0000H

17H 0000H Alternate OEM command set (00H = none exists)

18H 0000H

19H 0000H Address for Alternate OEM extended Table (00H = none exits)

1AH 0000H

1. Refer to CFI publication 100 for more details.

T5.0 561

©2001 Silicon Storage Technology, Inc. S71214-00-000 12/01 561

9

Loading...

Loading...