Silicon Storage Technology Inc SST31LF021E-70-4E-WH, SST31LF021E-70-4C-WH, SST31LF021E-300-4E-WH, SST31LF021E-300-4C-WH Datasheet

2 Mbit Flash + 1 Mbit SRAM ComboMemory

FEATURES:

SST31LF021 / SST31LF021E

SST31LF021 / 021E2 Mb Flash (x8) + 1 Mb SRAM (x8) Monolithic ComboMemories

Data Sheet

• Monolithic Flash + SRAM ComboMemory

– SST31LF021/021E: 256K x8 Flash + 128K x8 SRAM

• Single 3.0-3.6V Read and Write Operations

• Concurrent Operation

– Read from or Write to SRAM while

Erase/Program Flash

• Superior Reliability

– Endurance: 100,000 Cycles (typical)

– Greater than 100 years Data Retention

• Low Power Consumption:

– Active Current: 10 mA (typical) for Flash and

20 mA (typical) for SRAM Read

– Standby Current: 10 µA (typical)

• Flash Sector-Erase Capability

– Uniform 4 KByte sectors

• Latched Address and Data for Flash

• Fast Read Access Times:

– SST31LF021 Flash: 70 ns

SRAM: 70 ns

– SST31LF021E Flash: 300 ns

SRAM: 300 ns

• Flash Fast Erase and Byte-Program:

– Sector-Erase Time: 18 ms (typical)

– Bank-Erase Time: 70 ms (typical)

– Byte-Program Time: 14 µs (typical)

– Bank Rewrite Time: 4 seconds (typical)

• Flash Automatic Erase and Program Timing

– Internal V

Generation

PP

• Flash End-of-Write Detection

– Toggle Bit

– Data# Polling

• CMOS I/O Compatibility

• JEDEC Standard Command Set

• Package Available

– 32-lead TSOP (8mm x 14mm)

PRODUCT DESCRIPTION

The SST31LF021/021E devices are a 256K x8 CMOS

flash memory bank combined with a 128K x8 or 32K x8

CMOS SRAM memory bank manufactured with SST’s

proprietary , high per f ormance SuperFlash technology. Two

pinout standards are available for these devices. The

SST31LF021 conform to JEDEC standard flash pinouts

and the SST31LF021E conforms to standard EPROM

pinouts. The SST31LF021/021E devices write (SRAM or

flash) with a 3.0-3.6V power supply. The monolithic

SST31LF021/021E devices conform to Software Data

Protect (SDP) commands for x8 EEPR OMs .

Featuring high performance Byte-Program, the flash

memory bank provides a maximum Byte-Program time of

20 µsec. The entire flash memory bank can be erased and

programmed byte-by-byte in typically 4 seconds, when

using interface features such as Toggle Bit or Data# Polling to indicate the completion of Program operation. To

protect against inadvertent flash write, the SST31LF021/

021E devices have on-chip hardware and Software Data

Protection schemes. Designed, manufactured, and tested

for a wide spectrum of applications, the SST31LF021/

021E devices are offered with a guaranteed endurance of

10,000 cycles. Data retention is rated at greater than 100

years.

The SST31LF021/021E operate as two independent memory banks with respective bank enable signals. The SRAM

and flash memor y banks are superi mposed in the same

memory ad dress spa ce. Both memor y b anks share common address lines, data lines, WE# and OE#. The memory

bank selection is done by memory bank enable signals.

The SRAM bank e nable signal, BES# sel ects the SRAM

bank and the flash memory bank enable signal, BEF#

selects the flash mem ory bank. The W E# signa l has to be

used with Software Data Protection (SDP) command

sequence when controlling the Eras e an d P r ogram ope rations in the flash memory bank. The SDP command

sequence protects the data stored in the flash memory

bank from accidental alteration.

The SST31LF021/021E provide the added functionality of

being able to simultaneously read from or write to the

SRAM bank while erasing or programming in the flash

memory ban k. The SRAM memo ry bank can be read or

written while the flash memory bank performs SectorErase, Bank-Erase, or Byte-Program concurrently . All flash

memory Era se and Program operatio ns will automatic ally

latch the input ad dr ess a nd dat a s i gn als and c om pl ete th e

operation in background without further input stimulus

©2001 Silicon Storage Technology, Inc.

S71137-03-000 10/01 392

1

The SST logo and SuperFlash are registered trademarks of Silicon Storage Technology, Inc.

ComboMemory are trademarks of Silicon Storage Technology, Inc.

These specifications are subject to change without notice.

2 Mbit Flash + 1 Mbit SRAM ComboMemory

SST31LF021 / SST31LF021E

Data Sheet

requirement. On ce the internall y controlled Erase or Program cycle in the fla sh bank has c ommenced , the SRAM

bank can be accessed for Read or Write.

The SST31LF021/021E devices are suited for applications

that use both nonvolatile flash memory and volatile SRAM

memory to store code or data. For all s yst em applications,

the SST31LF021/0 21E devices significantly improve performance and reliability , while lowering power consumption,

when compared with multiple chip solutions. The

SST31LF021/021E inherently use less energy during

Erase and Program than alternative flash technologies.

When programming a flash device, the total energy consumed is a function of the applied voltage, current, and

time of application. Since for any given voltage range, the

SuperFlash techn ology uses less current to program and

has a shor ter Erase time, the total energy consumed during any Erase or Program operation is less than alternative

flash technologies. The monolithic ComboMemory eliminates redundant functions when using two separate memories of similar architecture; therefore, reducing the total

power co nsumpt ion.

The SuperFlash te ch nology provides fixed Erase and P r ogram times, independent o f th e numbe r of Erase/ Pro gram

cycles that have occurred. Therefore the system software

or hardware does not have to be modified or de-rated as is

necessary with al ternativ e flas h techno logies , whos e Erase

and Program times i ncrease with accumul ated Erase/P rogram cycles .

The SST31LF02 1/021E devices also i mprove flexibility by

using a single package an d a common set of signals to

perform functions previously requiring two separate

device s. To meet high dens ity, surface moun t requiremen ts,

the SST31LF021/021E devices are offered in 32-lead

TSOP packages. See Figure 1 for the pinouts.

Device Operation

The ComboMemory uses BES# and BEF# to control operation of either the SRA M or the flash memor y bank. Bus

contention is eliminated as the monolithi c device will not

recognize both bank enables as being simultaneously

active. If both bank enables are asser ted (i.e., BEF# and

BES# are both low), the BEF# will dominate while the

BES# is ignored and the appropriate operation will be executed in the flash memory bank. SST does not recommend

that both bank enables be simultaneously asserted. All

other address, data, and control lines are shared; which

minimizes power consump tion and a rea. The device goes

into standby when both bank enables are raised to V

IHC.

SRAM Operation

With BES# low and BEF# high, the SST31LF021/021E

operate as a 128K x8 or 32 K x8 CMO S SRAM, with fully

static operation requiring no external clocks or timing

strobes. The SRAM is mapped into the first 128 KByte

address space of the device. Read and Write cycle times

are equal.

SRAM Read

The SRAM Read operati on o f the SST3 1LF 021 /021 E are

controlled by OE# and BES#, both have to be low with

WE# high, for the system to obtain data from the outputs.

BES# is used for SRAM bank selection. When BES# and

BEF# are high, both memory banks are deselected. OE#

is the output control and is used to gate data from the output pins. The data bus is in high impedance state when

OE# is high. See Figure 2 for the Read cycle timing diagram.

SRAM Write

The SRAM Write operation of th e SST31LF021/021E ar e

controlled by WE# and BES#, both have to be low for the

system to write to the SRAM. BES# is used for SRAM bank

selection. During the Byte-Write operation , the addresses

and data are referenced to the rising edge of either BES#

or WE#, whichever occurs first. The Write time is measured

from the last falling edge to the first rising edge of BES# and

WE#. See Figure 3 for the Write cycle timing diagram.

Flash Operation

With BEF# active, the SST31LF021/021E operate as a

256K x8 flash mem ory. The flash memory bank is read

using the common address lines, data lines, WE# and

OE#. Erase and Program operations are initiated with the

JEDEC standard SDP command sequences. Address and

data are latched during the SDP commands and internally

timed Erase and Pr ogr am oper atio ns.

Flash Read

The Read operation of the SST31LF021/021E devices are

controlled by BEF# an d OE#, both have to be low, with

WE# high, for the system to obtain data fr om the outputs.

BEF# is used for flash memory bank selection. When

BEF# and BES# are high, both bank s are des electe d and

only standby power is consumed. OE# is the output control

and is used to gate data from the output pins. The data bus

is in high impedance state when OE# is high. See Figure 4

for the Read cycle timing diagram.

©2001 Silicon Storage Technology, Inc. S71137-03-000 10/01 392

2

2 Mbit Flash + 1 Mbit SRAM ComboMemory

SST31LF021 / SST31LF021E

Data Sheet

Flash Erase/Program Operation

SDP command s are used to init iate the flash me mory bank

Program and Erase operation s of the S ST31LF0 21/021E .

SDP commands are loaded to the flash memory bank

using standard microprocess or write sequences. A command is loaded by asserting WE# low while keeping BEF#

low and OE# high. The a ddress is latched on the falling

edge of WE# or BEF#, wh ichever occurs last. The dat a is

latched on the rising edge of WE# or BEF#, whichever

occurs first.

Flash Byte-Program Operation

The flash memory bank of the SST31LF021/021E devices

are programmed on a byte-by-byte basis. Before the Program operations, the memory must be erased first. The

Program operation consists of three steps. The first step is

the three-byte load sequence for Software Data Protection.

The second st ep is to load byte address and byte data.

During the Byte-Program operation, the addresses are

latched on the falling edge of ei ther B EF# o r W E#, whichever occurs last. The data i s latched on the r ising edge of

either BEF# or WE#, whic hever occurs first. T he th ir d step

is the internal Program operation which is initiated after the

rising edge of the four th WE# or BEF#, whichever occurs

first. The Program operation, once initiated, will be completed, within 20 µs. See Figures 5 and 6 for WE# and

BEF# controlled Pr ogram operation timing di agrams and

Figure 16 f or flow charts. During th e Prog ram op era tion, t he

only valid Flash Read operations are Data# Polling and

Toggle Bit. During the internal Program operation, the host

is free to perform additional tasks. Any SDP commands

loaded during the internal Program operation will be

ignored.

Flash Sector-Erase Operation

The Sector-Erase operation allows the system to erase the

flash memory bank on a sector-by-sector basis. The sector

architecture is based on uniform sector size of 4 KByte.

The Sector-Erase op eration is in itiated by executing a sixbyte command load sequence for Software Data Protection with Sector-Erase command (30H) and sector address

(SA) in the last bus cy cle. The ad dress lines A

used to determ ine the sector addr es s. The s ector ad dr ess

is latched on the falling edge of the six th WE # pu ls e, whil e

the command (30H) is latched on the rising edge of the

sixth WE# pulse. The internal Erase operation begins after

the sixth WE# pul se . The End-o f-Er a se can be det ermined

using either Dat a# Polling or Toggle Bit methods. See Figure 9 for timing waveforms. Any SDP commands loaded

during the Sector-Erase operation will be ignored.

17-A12

will be

Flash Bank-Erase Operation

The SST31LF021/021E flash memory bank provides a

Bank-Erase operation, which allows the user to erase the

entire flash memory bank array to the ‘1’ s state . This is useful when the entire bank must be quic kly erased. The BankErase operation is initiated by ex ecuting a six-byte Softw are

Data Protection command sequence with Bank-Erase command (10H) with address 5555H in the last byte sequence.

The internal Erase operation begins with the rising edge of

the sixth WE# or BEF# pulse, whichever occurs first. During

the internal Erase operation, the only valid Flash Read operations are Toggle Bit and Data# Polling. See Table 4 for the

command sequence, Figure 10 for timing diagram, and Figure 19 for the flowchart. Any SDP commands loaded during

the Bank-Erase operation will be ignored.

Flash Write Operation Status Detection

The SST31LF021/021E flash memory bank provides two

software means to dete ct the complet ion of a flas h memory

bank Write (Program or Erase) cycle, in order to optimize

the system Write cycle time. The software detection

includes two status bits: Data# Polling (DQ

). The End-of-Wr ite detection mode is enabled after

(DQ

6

) and T oggle Bit

7

the rising edge of WE#, which initiates the internal Program

or Erase operation. The actu al completio n of the nonvolatile write is asynchronous with the system; therefore, either

a Data# Polling or Toggle Bit Rea d may be simultaneous

with the completi on of the Write cy cle. If this occurs, the

system may possibly get an erroneous result, i.e., valid

data may appear to conflict with either DQ

or DQ6. In

7

order to prevent spuriou s rejection, if an erroneous resul t

occurs, the software r outine shou ld includ e a loop t o read

the accessed locat ion an additional two (2) times. If both

reads are valid, then t he device has completed th e Write

cycle, otherwise the rejection is valid.

Flash Data# Polling (DQ7)

When the SST31LF021/021E flash memory bank is in the

internal Program operation, any attempt to read DQ

produce the com plement of the tr ue data. Once the P rogram operation is compl eted, DQ

Note that even though DQ

7

will produce tr ue data.

7

may have valid data immediately following the compl etion of an internal W rite operation, the remaini ng data outputs m ay still be invalid: valid

data on the entire data bus will a pp ear i n s ubs e que nt s uccessive Read cycles after an interval of 1 µs. During internal Erase operatio n, any attem pt to read DQ

will produce

7

a ‘0’. Once the internal Erase operation is completed, DQ

will produce a ‘1’. The Data# Polling is valid after the rising

edge of the fourth WE# (or BEF#) pulse for Program operation. For Sector or Bank-Eras e, the Data# Polling is valid

will

7

7

©2001 Silicon Storage Technology, Inc. S71137-03-000 10/01 392

3

2 Mbit Flash + 1 Mbit SRAM ComboMemory

SST31LF021 / SST31LF021E

Data Sheet

after the rising e dge of t he sixth WE# (or BE F#) puls e. See

Figure 7 for Data# Polling timing diagram and Figure 17 for

a flowchart.

Flash Toggle Bit (DQ6)

During the inter nal Program or Erase ope ration, any consecutive attempts to read DQ

will produce alter nating 0s

6

and 1s, i.e., toggling between 0 and 1. W hen the internal

Program or Erase operation is com plete d, t he tog gling wi ll

stop. The flash memor y bank is then ready for the next

operation. The T oggle Bit is valid after the rising edge of the

fourth WE# (or BE#) pulse for Program operation. For Sector or Bank-Erase, the Toggle Bit is valid after the rising

edge of the sixth WE# (or BEF#) pulse. See Figur e 8 for

Toggle Bit timing diagram and Figure 17 for a flowchart.

Flash Memory Data Protection

The SST31LF021/021E flash memory bank provides both

hardware and software features to protec t nonvolatile data

from inadvertent writes.

Flash Hardware Data Protection

Noise/Glitch Protection: A WE# or BEF# pulse of less than

5 ns will not initiate a Write cycle.

Power Up/Down Detection: The Write operation is

V

DD

inhibited when is less than 1.5V.

Write Inhibi t Mode: Forcing OE# low, BEF# high, or WE#

high will inhibit the Flash Write operation. This prevents

inadvertent writes during power-up or power-down.

Flash Software Data Protection (SDP)

The SST31LF021/021E provide the JEDEC approved

Software Data Protection scheme for all flash memory

bank data alteration operations, i.e., Program and Erase.

Any Program operation requires the inclusion of a series of

three-byte sequence. The three-byte load sequence is

used to initiate the Program operation, providing optimal

protection from inadver tent Write operations, e.g., during

the system power-up or power-down. Any Erase operation

requires the inclusion of six-byte load sequence. The

SST31LF021/021E devices are shipped with the Software

Data Protection permanently enabled. See Table 4 for the

specific software command codes. During SDP command

sequence, invalid SDP comma nds wil l abor t the device t o

the Read mode, within T

RC.

Concurrent Read and Write Operations

The SST31LF021/021E provide the unique benefit of

being able to read from o r write to SRAM, while si multaneously erasing or pr ogramming the flash. Th e device will

ignore all SDP commands when an Erase or Program

operation is in progress. This allows data alteration code to

be executed from SRAM, while alteri ng the data in flash.

The following table lists all valid states. SST does not recommend that both bank enables, BEF# and BES#, be

simultaneously asserted.

ONCURRENT READ/WRITE STATE TABLE

C

Flash SRAM

Program/Erase Read

Program/Erase Write

Note that Product Identification commands use SDP;

therefore, these commands will also be ignored while an

Erase or Program operation is in progress.

Product Identification

The Product Id entification mode ide ntifies the devices as

either SST31LF 021 or SST31LF021E and the manufacturer as SST . This mode may be accessed by hardware or

software operations. The ha rdware device ID R ead ope ration is typica lly used b y a prog rammer to identi fy the corre ct

algorithm for the SST 31LF0 21/02 1E fl ash m emor y bank s.

Users may wish to use the sof tware Product Id entificatio n

operation to identify the part (i.e., using the device ID) when

using multiple manufacturers in the same socket. For

details, see Table 3 for hardware operation or Table 4 for

software operation, Figure 11 for the software ID entry and

read timing diagram and F igure 18 for the ID entry co mmand sequence flowchart.

TABLE 1: PRODUCT IDENTIFICATION

Address Data

Manufacture r’s ID 0000H BFH

Device ID

SST31LF021 0001H 18H

SST31LF021E 0001H 19H

T1.4 392

Product Identification Mode Exit/Reset

In order to return to the standard Read mode, the Software

Product Identification mode must be exited. Exiting is

accomplished by issuing the Exit ID command sequence,

which returns the device to the Read operation. Please

note that the software reset command is ignored during an

©2001 Silicon Storage Technology, Inc. S71137-03-000 10/01 392

4

2 Mbit Flash + 1 Mbit SRAM ComboMemory

SST31LF021 / SST31LF021E

Data Sheet

internal Pr ogram or Erase op eration. See Table 4 for soft-

ware command cod es, Figur e 12 for timin g waveform and

Figure 18 for a flowchart.

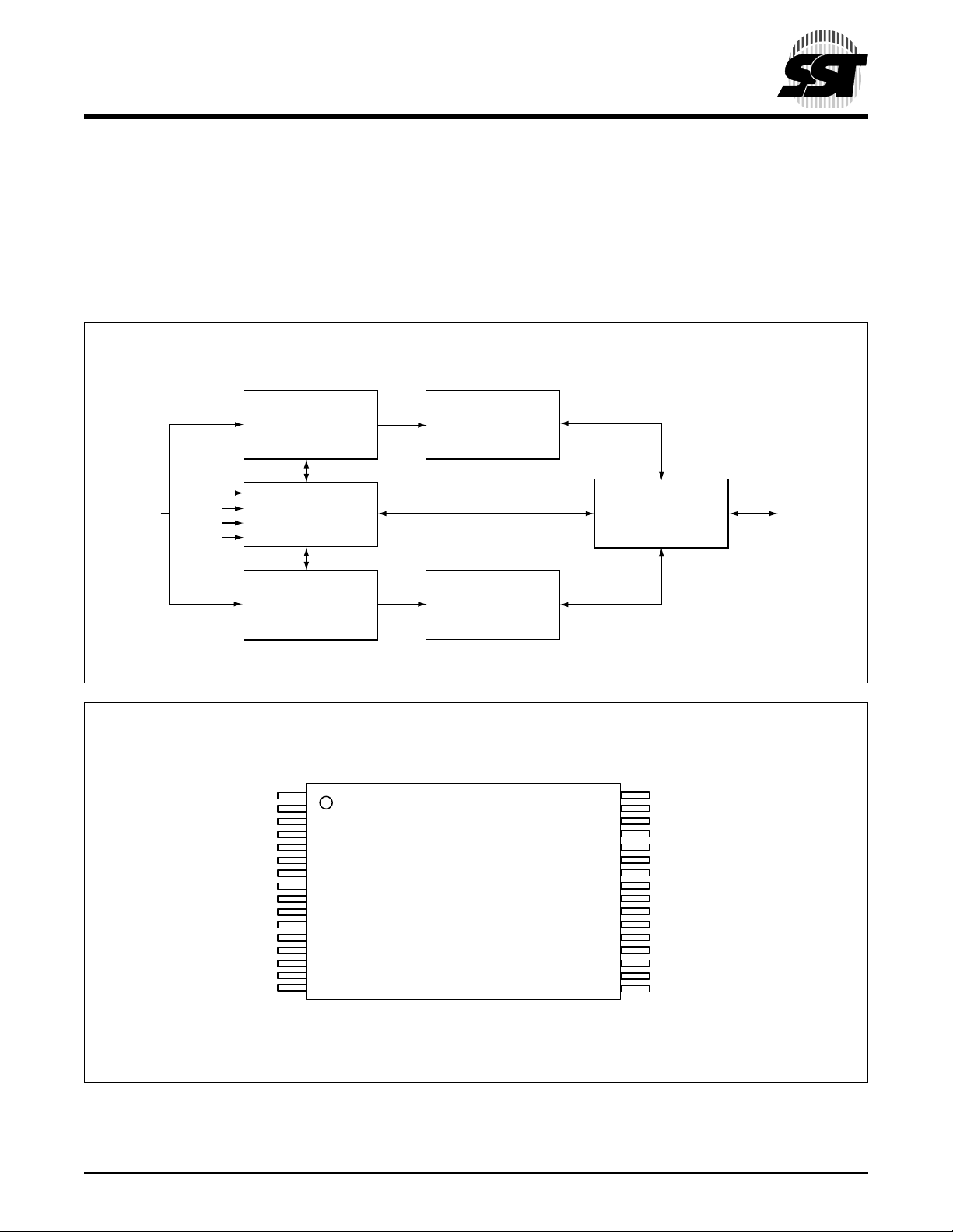

FUNCTIONAL BLOCK DIAGRAM

Address Buffers

BES#

AMS - A

BEF#

0

OE#

Control Logic

WE#

Address Buffers

& Latches

Design Considerations

SST recommends a high frequency 0.1 µF ceramic capacitor to be plac ed as close as possible between V

, e.g., less than 1 cm away from the VDD pin of the

V

SS

device. Additionally, a low frequency 4.7 µF electrolytic

capacitor from V

the V

SRAM

SuperFlash

Memory

DD

pin.

to VSS should be placed within 1 cm of

DD

I/O Buffers

DQ7 - DQ

DD

and

0

392 ILL B1.2

Note: AMS = Most Significant Address

SST31LF021E SST31LF021 SST31LF021 SST31LF021E

A11

A13

A14

A17

BES#

V

DD

WE#

A16

A15

A12

A11

A13

A14

A17

WE#

V

DD

BES#

A16

A15

A12

A9

A8

A7

A6

A5

A4

A9

A8

A7

A6

A5

A4

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

Standard Pinout

T op Vie w

Die Up

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

392 ILL F01.3

OE#

A10

BEF#

DQ7

DQ6

DQ5

DQ4

DQ3

V

SS

DQ2

DQ1

DQ0

A0

A1

A2

A3

OE#

A10

BEF#

DQ7

DQ6

DQ5

DQ4

DQ3

V

SS

DQ2

DQ1

DQ0

A0

A1

A2

A3

FIGURE 1: P

©2001 Silicon Storage Technology, Inc. S71137-03-000 10/01 392

IN ASSIGNMENTS FOR 32-LEAD TSOP (8MM X 14MM)

5

2 Mbit Flash + 1 Mbit SRAM ComboMemory

SST31LF021 / SST31LF021E

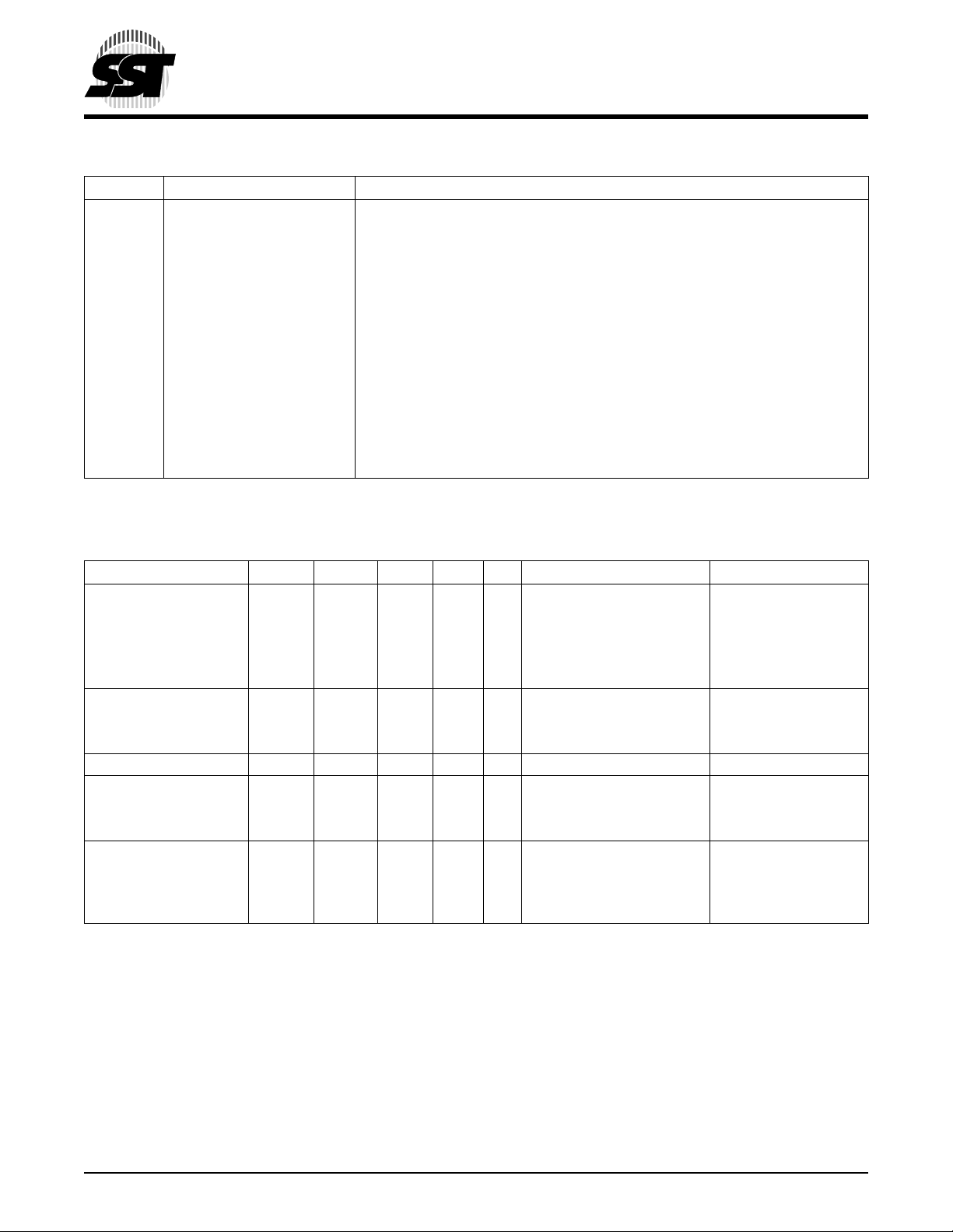

TABLE 2: PIN DESCRIPTION

Symbol Pin Name Functions

1

-A

A

MS

DQ

-DQ0Data Input/Output To output data during Read cycles and receive input data during Write cycles.

7

BES# SRAM Memory Bank Enable T o ac tivate the SRAM memory bank when BES# is low.

BEF# Flash Memory Bank Enable To activate the Flash memory bank when BEF# is low.

OE# Output Enable To gate the data output buffers.

WE# Write Enable To control the Write operations.

V

DD

V

SS

1. AMS = Most significant address

Address Inputs To provide memory addresses.

0

During flash Sector-Erase, A

Data is internal ly latched during a flash Erase/P rogram cycle.

The outputs are in tri-state when OE# or BES# and BEF# are high.

Power Supply 3.0-3.6V Power Supply

Ground

address lines will select the sector.

17-A12

to provide flash address

A

17-A0

to provide SST31LF021/021E SRAM

A

16-A0

addresses

Data Sheet

T2.3 392

TABLE 3: OPERATION MODES SELECTION

Mode BES# BEF# OE# WE# A9DQ Address

Flash

Read X

Program X V

Erase X V

SRAM

Read V

Write V

Standby V

Flash Write Inhibit X X V

Product Identification

Hardware Mode X V

Software Mode X V

1. X can be VIL or VIH, but no other value.

2. Device ID 18H for SST31LF021, 19H for SST31LF021E.

1

IL

IL

IHC

XXXVIHXHigh Z / D

XV

V

IL

IL

IL

V

IH

V

IH

V

IHC

IH

IL

IL

V

V

V

V

XVILAIND

V

IL

IH

IH

IL

AIND

IH

V

IL

V

IL

V

IH

OUT

AIND

IN

X X Sector address,

AIND

OUT

IN

XXXHigh Z X

IL

XXXHigh Z / D

V

IL

V

IL

X X High Z / D

V

VHManufacturer’s ID (BFH)

IH

Device ID

V

AINID Code See Table 4

IH

OUT

OUT

OUT

2

A

IN

A

IN

XXH for Bank-Erase

A

IN

A

IN

X

X

X

A17-A1=VIL, A0=V

A17-A1=VIL, A0=V

IL

IH

T3.4 392

©2001 Silicon Storage Technology, Inc. S71137-03-000 10/01 392

6

2 Mbit Flash + 1 Mbit SRAM ComboMemory

SST31LF021 / SST31LF021E

Data Sheet

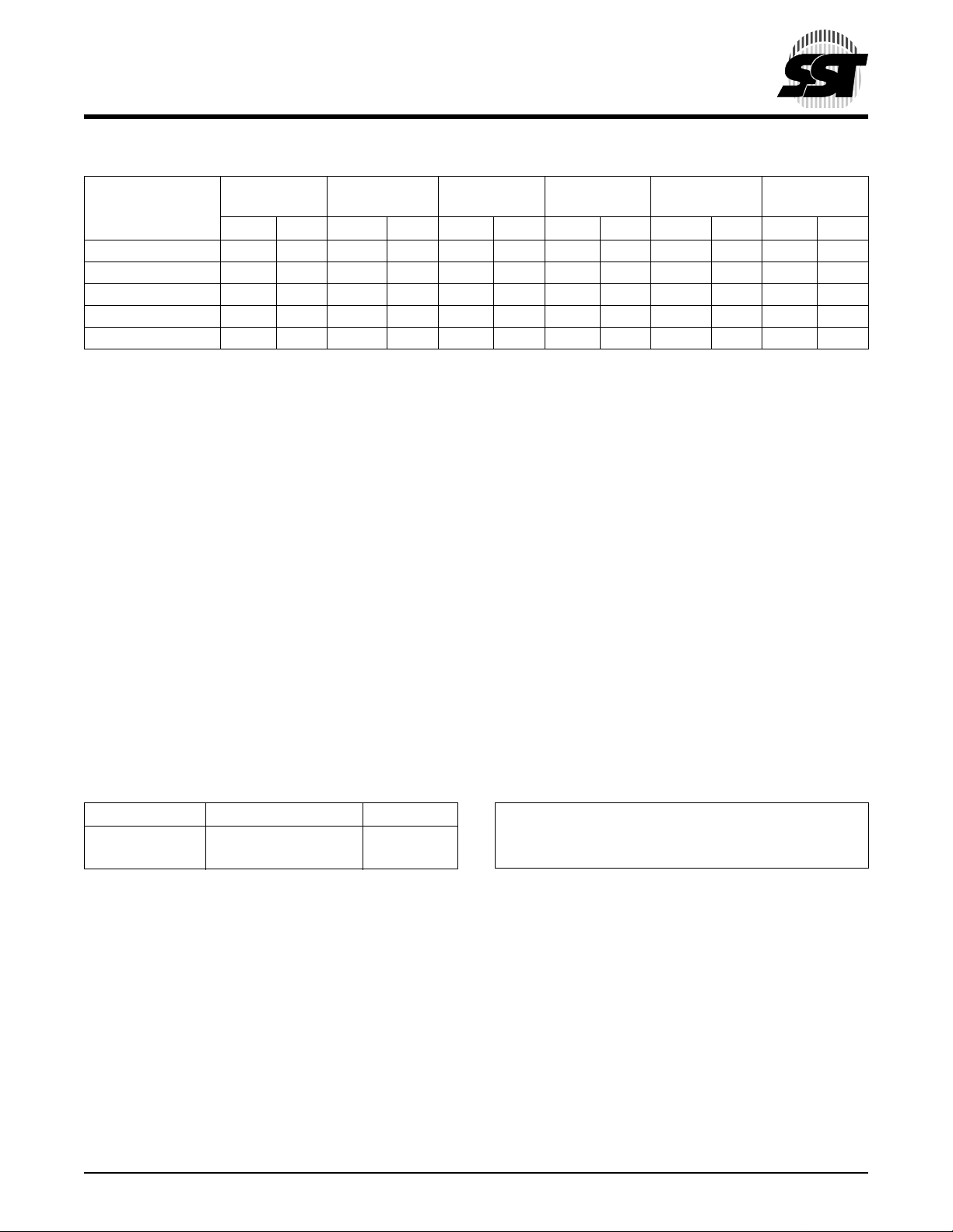

TABLE 4: SOFTWARE COMMAND SEQUENCE

Command

Sequence

Byte-Program 5555H AAH 2AAAH 55H 5555H A0H BA

Sector-Erase 5555H AAH 2AAAH 55H 5555H 80H 5555H AAH 2AAAH 55H SA

Bank-Erase 5555H AAH 2AAAH 55H 5555H 80H 5555H AAH 2AAAH 55H 5555H 10H

Software ID Entry

4,5

Software ID Exit 5555H AAH 2AAAH 55H 5555H F0H

1. Address format A14-A0 (Hex),Address A

2. BA = Program Byte address

3. SA

for Sector-Erase; uses A17-A12 address lines

X

4. The device does not remain in Software Product ID mode if powered down.

5. With A

= 0; SS T Manufacturer’s ID = BFH, is read with A0 = 0,

17-A1

Absolute Maximum Stress Ratings (Applied conditions greater than those listed under “Absolute Maximum

Stress Ratings” may cause pe r manent dama ge to the device. This is a stres s rating only and funct ional operatio n

of the device at these conditions or conditions greater tha n those defined in the ope rational sections of this data

sheet is not implied. Exposure to absolute maximum stress rating conditions may affect device reliability.)

1st Bus

Write Cycle

2nd Bus

Write Cycle

3rd Bus

Write Cycle

4th Bus

Write Cycle

5th Bus

Write Cycle

6th Bus

Write Cycle

Addr1Data Addr1Data Addr1Data Addr1Data Addr1Data Addr1Data

2

Data

3

X

5555H AAH 2AAAH 55H 5555H 90H

and A17 can be VIL or VIH, but no other value, for the Command sequence.

15, A16,

SST31LF021 Device ID = 18H, is read with A

SST31LF021E Device ID = 19H, is read with A

= 1,

0

0

= 1

30H

T4.4 392

Operating Temperature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -20°C to +85°C

Storage Temperature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -65°C to +150°C

D. C. Voltage on Any Pin to Ground Potential . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .-0.5V to V

Transient Voltage (<20 ns) on Any Pin to Ground Potential . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .-1.0V to V

DD

DD

+0.5V

+1.0V

Package Power Dissipation Capability (Ta = 25°C) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1.0W

Surface Mount Lead Soldering Temperature (3 Seconds). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 240°C

1

Output Short Circ uit Curr ent

1. Outputs shorted for no more than one second. No more than one output shorted at a time.

OPERATING RANGE: SST31LF021/021E

Range Ambient Temp V

Commercial 0°C to +70°C 3.0-3.6V

Extended -20°C to +85°C 3.0-3.6V

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50 mA

AC CONDITIONS OF TEST

DD

Input Rise/Fall Time . . . . . . . . . . . . . . . 5 ns

Output Load . . . . . . . . . . . . . . . . . . . . . CL = 30 pF

See Figures 14 and 15

©2001 Silicon Storage Technology, Inc. S71137-03-000 10/01 392

7

2 Mbit Flash + 1 Mbit SRAM ComboMemory

SST31LF021 / SST31LF021E

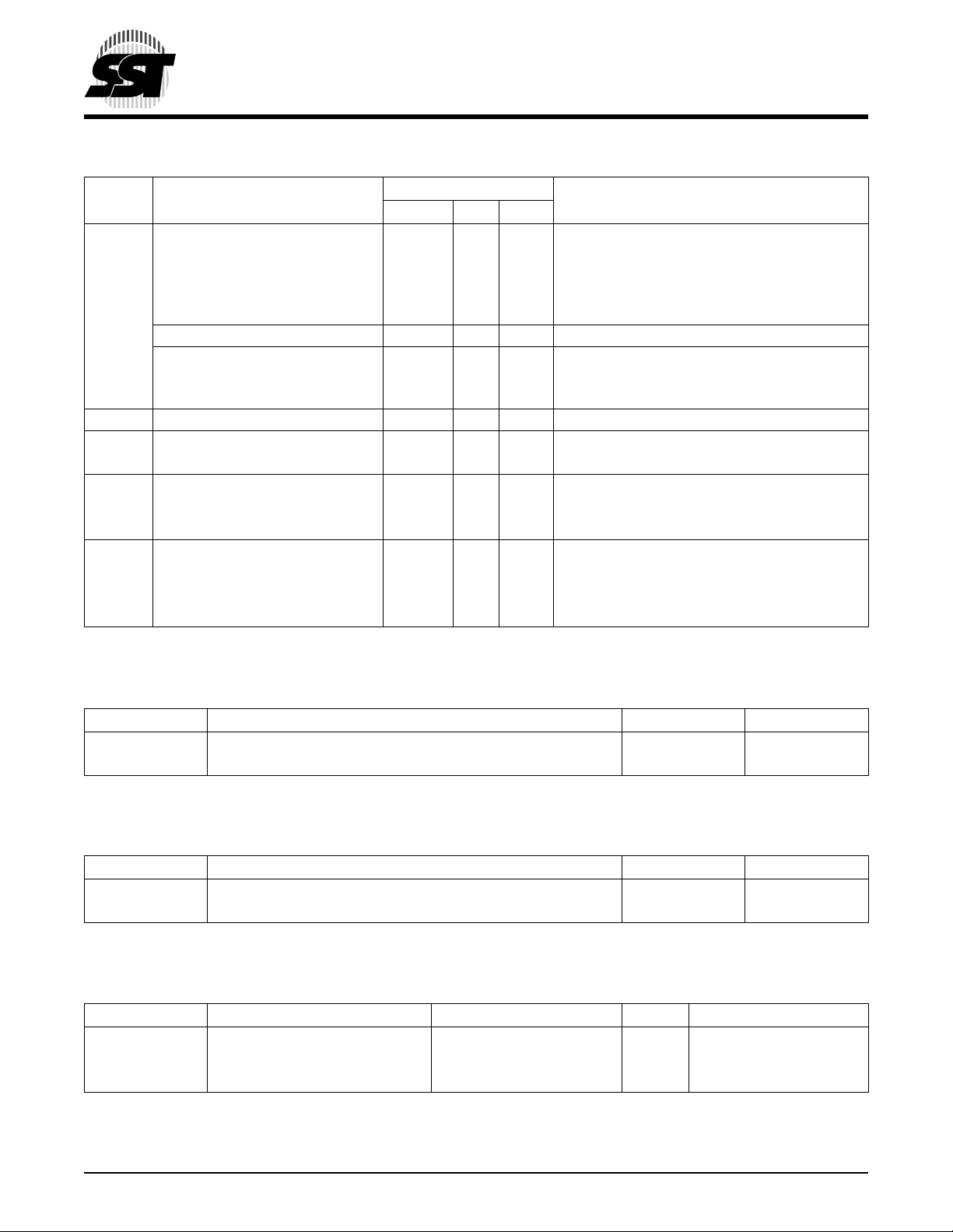

TABLE 5: DC OPERATING CHARACTERISTICS (VDD = 3.0-3.6V)

Limits

Symbol Parameter

I

DD

Power Supply Current Address input VIL/VIH, at f=1/TRC Min,

Read

Flash 12 mA

SRAM 40 mA BEF#=VIH, BES#=V

Concurrent Operation 55 mA BEF#=VIH, BES#=V

Write

Flash (Program) 15 mA

SRAM 40 mA BEF#=VIH, BES#=V

1

I

SB

I

LI

I

LO

V

IL

V

IH

V

IHC

V

OL

V

OH

V

H

I

H

1. Specification applies to commercial temperature devices only. This parameter may be higher for extended devices.

Standby VDD Current 30 µA BEF#=BES#=V

Input Leakage Current 1 µA VIN=GND to VDD, VDD=VDD Max

Output Leakage Current 1 µA V

Input Low Voltage 0.4 V VDD=VDD Min

Input High Voltage 0.7V

DD

Input High Voltage (CMOS) VDD-0.3 V VDD=VDD Max

Output Low Voltage 0.2 V IOL=100 µA, VDD=VDD Min

Output Hi gh Voltage VDD-0.2 V IOH=-100 µA, VDD=VDD Min

Supervoltage for A9 pin 11.4 12.6 V BEF#=OE#=VIL, WE#=V

Supervoltage Current for A9 pin 200 µA BEF#=OE#=VIL, WE#=V

Test ConditionsMin Max Units

DD=VDD

Max, all DQs open

, WE#=V

IL

V

OE#=V

BEF#=VIL, BES#=V

OE#=VIH, WE#=V

BEF#=VIL, BES#=V

=GND to VDD, VDD=VDD Max

OUT

VVDD=VDD Max

IH

IH

IL

IL

IL

IH

IL

, VDD=VDD Max

IHC

IH

IH, A9=VH

Data Sheet

Max

T5.3 392

TABLE 6: RECOMMENDED SYSTEM POWER-UP TIMINGS

Symbol Parameter Minimum Units

T

T

1

PU-READ

PU-WRITE

1

1. This parameter is measured only for initial qualification and after a design or process change that could affect this parameter.

Power-up to Read Operation 100 µs

Power-up to Write Operation 100 µs

TABLE 7: CAPACITANCE (Ta = 25°C, f=1 Mhz, other pins open)

Parameter Description Test Condition Maximum

1

C

I/O

1

C

IN

1. This parameter is measured only for initial qualification and after a design or process change that could affect this parameter.

I/O Pin Capacitance V

= 0V 12 pF

I/O

Input Capacitance VIN = 0V 6 pF

TABLE 8: RELIABILITY CHARACTERISTICS

Symbol Parameter Minimum Specification Units Test Method

1

N

END

1

T

DR

1

I

LTH

1. This parameter is measured only for initial qualification and after a design or process change that could affect this parameter.

Endurance 10,000 Cycles JEDEC Standard A117

Data Retention 100 Years JEDEC Standard A103

Latch Up 100 + I

DD

mA JEDEC Standard 78

T6.1 392

T7.0 392

T8.1 392

©2001 Silicon Storage Technology, Inc. S71137-03-000 10/01 392

8

Loading...

Loading...