Page 1

Si4704/05/06/07/1X/2X /3X/4X FM TRANSMITTER/

AN332

AM/FM/SW/LW/WB R

ECEIVER PROGRAMMING GUIDE

1. Introduction

1.1. Scope

This document provides an overview of the programming requirements for the Si4704/05/06/1x/2x/3x/4x FM

transmitter/AM/FM/SW/LW/WB receiver. The hardware control interface and software commands are detailed

along with several examples of the required steps to configure the device for various modes of operation.

2. Overview

This family of products is programmed using commands and responses. To perform an action, the system

controller writes a command byte and associated arguments, causing the device to execute the given command.

The device will, in turn, provide a response depending on the type of command that was sent. "4. Commands and

Responses" on page 5 and "5. Commands and Properties" on page 6 describe the procedures for using

commands and responses and provide complete lists of commands, properties, and responses.

The device has a slave control interface that allows the system controller to send commands to and receive

responses from the device using one of three serial protocols (or bus modes): 2-wire mode (I

compatible), 3-wire mode, or SPI mode. "6. Control Interface" on page 168 describes the control interface in detail.

"7. Powerup" on page 176 describes options for the sequencing of VDD and VIO power supplies, selection of the

desired bus mode, provision of the reference clock, RCLK, and sending of the POWER_UP command.

"8. Powerdown" on page 182 describes sending the POWER_DOWN command and removing VDD and VIO

power supplies as necessary.

2

C and SMBUS

"9. Digital Audio Interface" on page 183 describes the digital audio format supported and how to operate the device

in digital mode.

"10. Timing" on page 186 describes the CTS (Clear to Send) timing indicating when the command has been

accepted and in most cases completed execution, and the STC (Seek/Tune Complete) timing indicating when the

Seek/Tune commands have completed execution.

"11. FM Transmitter" on page 191 describes the audio dynamic range control, limiter, pre-emphasis,

recommendations for maximizing audio volume for the FM transmitter.

"12. Programming Examples" on page 195 provides flowcharts and step-by-step procedures for programming the

device.

Confidential Rev. 0.2 2/08 Copyright © 2008 by Silicon Laboratories AN332

Silicon Laboratories Confidential. Information contained herein is covered under non-disclosure agreement (NDA).

Page 2

AN332

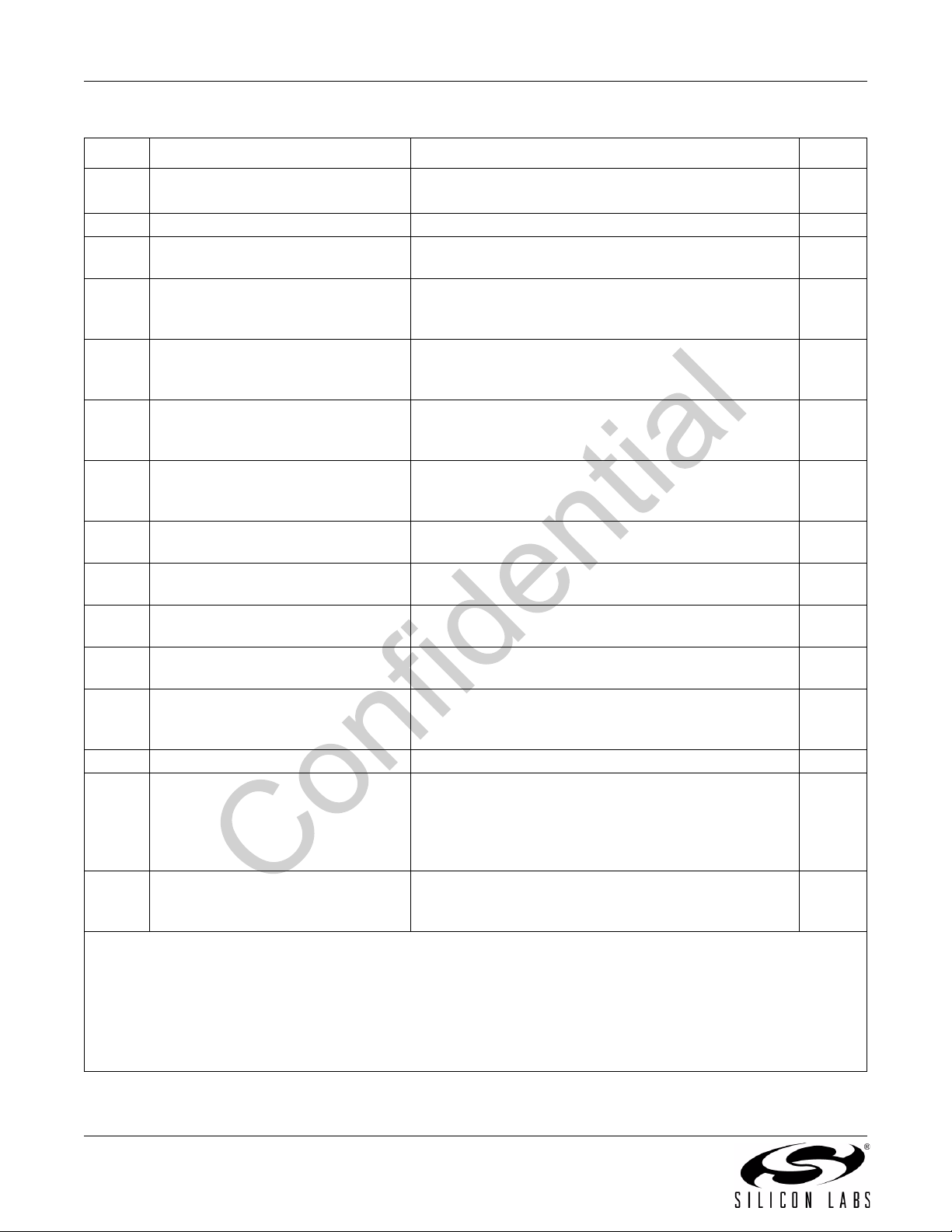

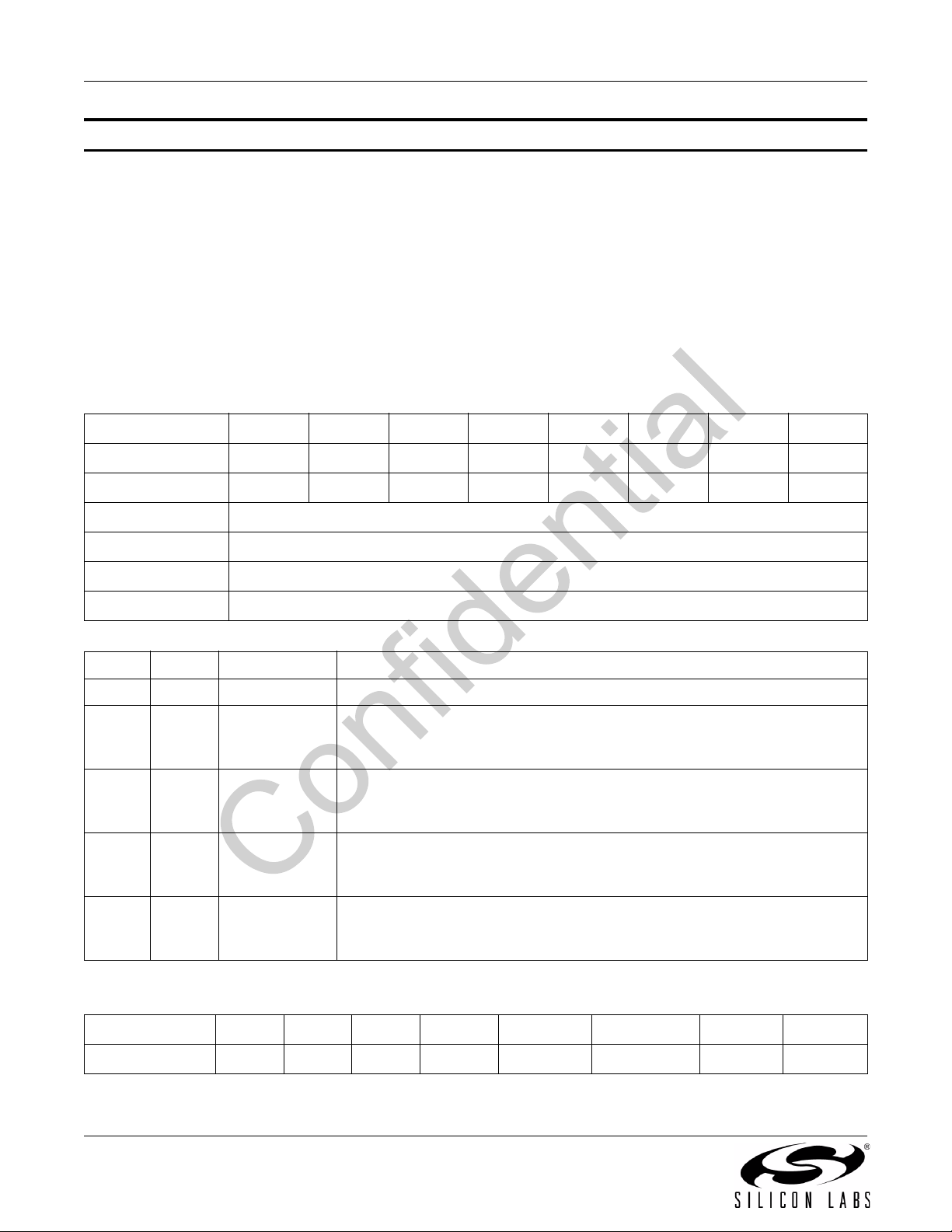

Table 1. Product Family Function

Part Number General Description

Si4700 FM Receiver

Si4701 FM Receiver with RDS

Si4702 FM Receiver

Si4703 FM Receiver with RDS

Si4704 FM Receiver

Si4705 FM Receiver with RDS

Si4706 High Performance RDS Receiver

Si4707 WB Receiver with SAME

Si4710 FM Transmitter

Si4711 FM Transmitter with RDS

Si4712 FM Transmitter with RPS

Si4713 FM Transmitter with RDS & RPS

Si4720 FM Transceiver

Si4721 FM Transceiver with RDS

Si4730 AM/FM Receiver

Si4731 AM/FM Receiver with RDS

Si4734 AM/SW/LW/FM Receiver

Si4735 AM/SW/LW/FM Receiver with RDS

Si4736 AM/FM/WB Receiver

Si4737 AM/FM/WB Receiver with RDS

Si4738 FM/WB Receiver

Si4739 FM/WB Receiver with RDS

Si4740 AM/FM Receiver

Si4741 AM/FM Receiver with RDS

Si4749 High-Performance RDS Receiver

RDS

FM Receiver

FM Transmitter

333

3333

3 333

3 3333

33 333

33 3 3 333

AM Receiver

3

33

3

33

33

33 33

3333

33

33 3 3

333

333 3 3

33 3

33 33 3

33

333 3

33 3

33 3 3

WB Receiver

SW/LW Receiver

33

RPS

SAME

Digital Input

Digital Output

Package Size (mm)

AEC-Q100 Qualified

High Performance RDS

33

Embedded FM antenna

4x4

4x4

3x3

3x3

3x3

3x3

3x3

3x3

3x3

3x3

3x3

3x3

3x3

3x3

3x3

3x3

3x3

3x3

3x3

3x3

3x3

3x3

4x4

4x4

4x4

2 Confidential Rev. 0.2

Page 3

AN332

TABLE OF CONTENTS

1. Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1

1.1. Scope . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1

2. Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1

3. Terminology . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4

4. Commands and Responses . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

5. Commands and Properties . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6

5.1. Commands and Properties for the FM/RDS Transmitter

(Si4710/11/12/13/20/21) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

5.2. Commands and Properties for the FM/RDS Receiver

(Si4704/05/06/2x/3x/4x) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .52

5.3. Commands and Properties for the AM/SW/LW Receiver

(Si4730/31/34/35/36/37/40/41) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

5.4. Commands and Properties for the WB Receiver (Si4707/36/37/38/39) . . . . . . . . . 136

6. Control Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .168

6.1. 2-Wire Control Interface Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .168

6.2. 3-Wire Control Interface Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .171

6.3. SPI Control Interface Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 174

7. Powerup . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .176

7.1. Powerup from Device Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 177

7.2. Powerup from a Component Patch . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .178

8. Powerdown . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .182

9. Digital Audio Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .183

10. Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .186

11. FM Transmitter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.1. Audio Dynamic Range Control for FM Transmitter . . . . . . . . . . . . . . . . . . . . . . . . 191

11.2. Audio Pre-emphasis for FM Transmitter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .192

11.3. Audio Limiter for FM Transmitter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 193

11.4. Maximizing Audio Volume for FM Transmitter . . . . . . . . . . . . . . . . . . . . . . . . . . .193

12. Programming Examples . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 195

12.1. Programming Example for the FM/RDS Transmitter . . . . . . . . . . . . . . . . . . . . . .195

12.2. Programming Example for the FM/RDS Receiver . . . . . . . . . . . . . . . . . . . . . . . .213

12.3. Programming Example for the AM/SW/LW Receiver . . . . . . . . . . . . . . . . . . . . . . 235

12.4. Programming Example for the WB/SAME Receiver . . . . . . . . . . . . . . . . . . . . . . . 246

Document Change List . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .254

Contact Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .256

. .191

Confidential Rev. 0.2 3

Page 4

AN332

3. Terminology

SEN—Serial enable pin, active low; used as device select in 3-wire and SPI operation and address selection in

2-wire operation.

SDIO—Serial data in/data out pin.

SCLK—Serial clock pin.

RST or RSTb—Reset pin, active low

RCLK—External reference clock

GPO—General purpose output

CTS—Clear to send

STC—Seek/Tune Complete

NVM—Non-volatile internal device memory

Device—Refers to the FM Transmitter/AM/FM/SW/LW/WB Receiver

System Controller—Refers to the system microcontroller

CMD—Command byte

COMMANDn—Command register (16-bit) in 3-Wire mode (n = 1 to 4)

ARGn—Argument byte (n = 1 to 7)

STATUS—Status byte

RESPn—Response byte (n = 1 to 15)

RESPONSEn—Response register (16-bit) in 3-Wire mode (n = 1 to 8)

4 Confidential Rev. 0.2

Page 5

AN332

4. Commands and Responses

Commands control actions, such as power up, power down, or tune to a frequency, and are one byte in size.

Arguments are specific to a given command and are used to modify the command. For example, after the

TX_TUNE_FREQ command, arguments are required to set the tune frequency. Arguments are one byte in size,

and each command may require up to seven arguments. Responses provide the system controller status

information and are returned after a command and its associated arguments are issued. All commands return a

one byte status indicating interrupt state and clear-to-send the next command. Commands may return up to 15

additional response bytes. A complete list of commands is available in “5. Commands and Properties”.

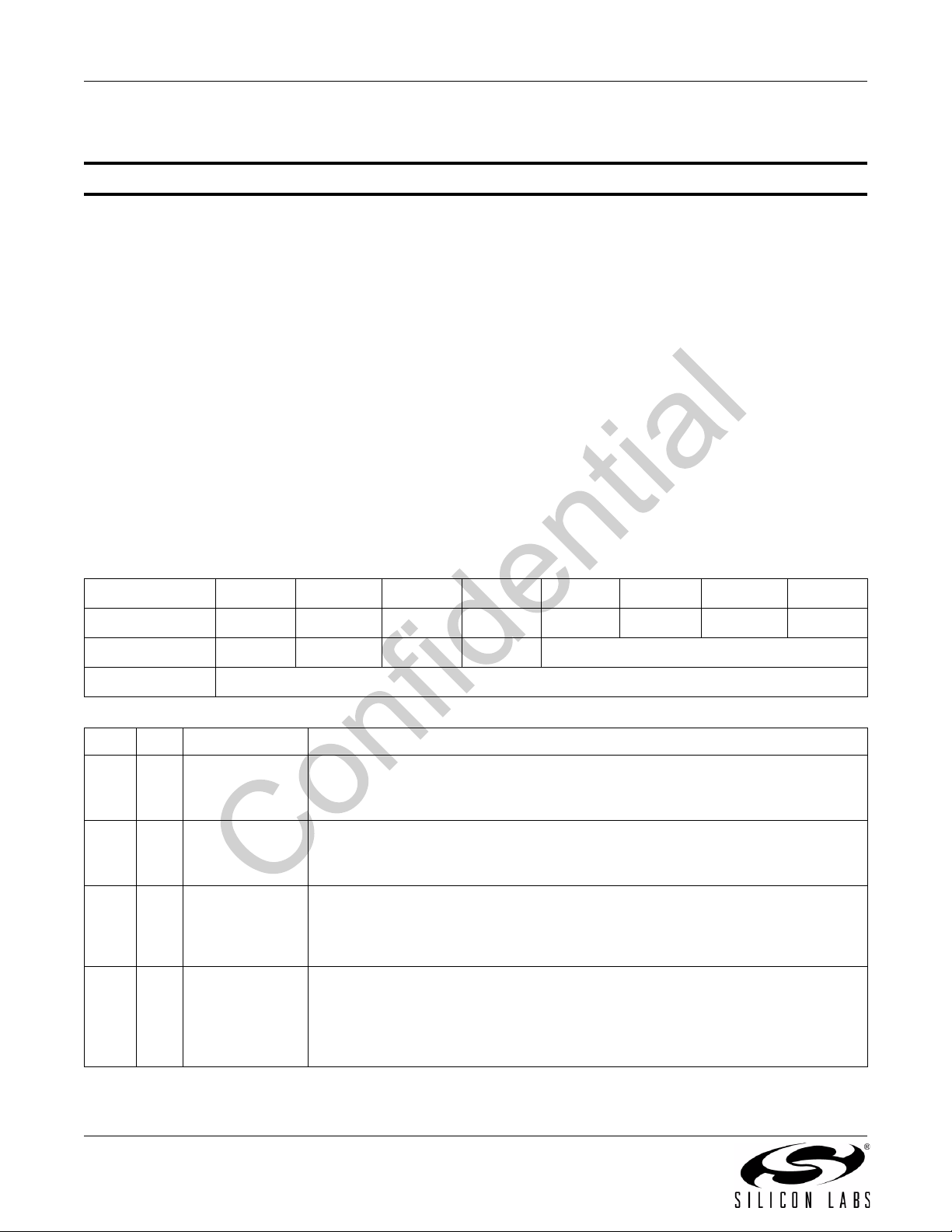

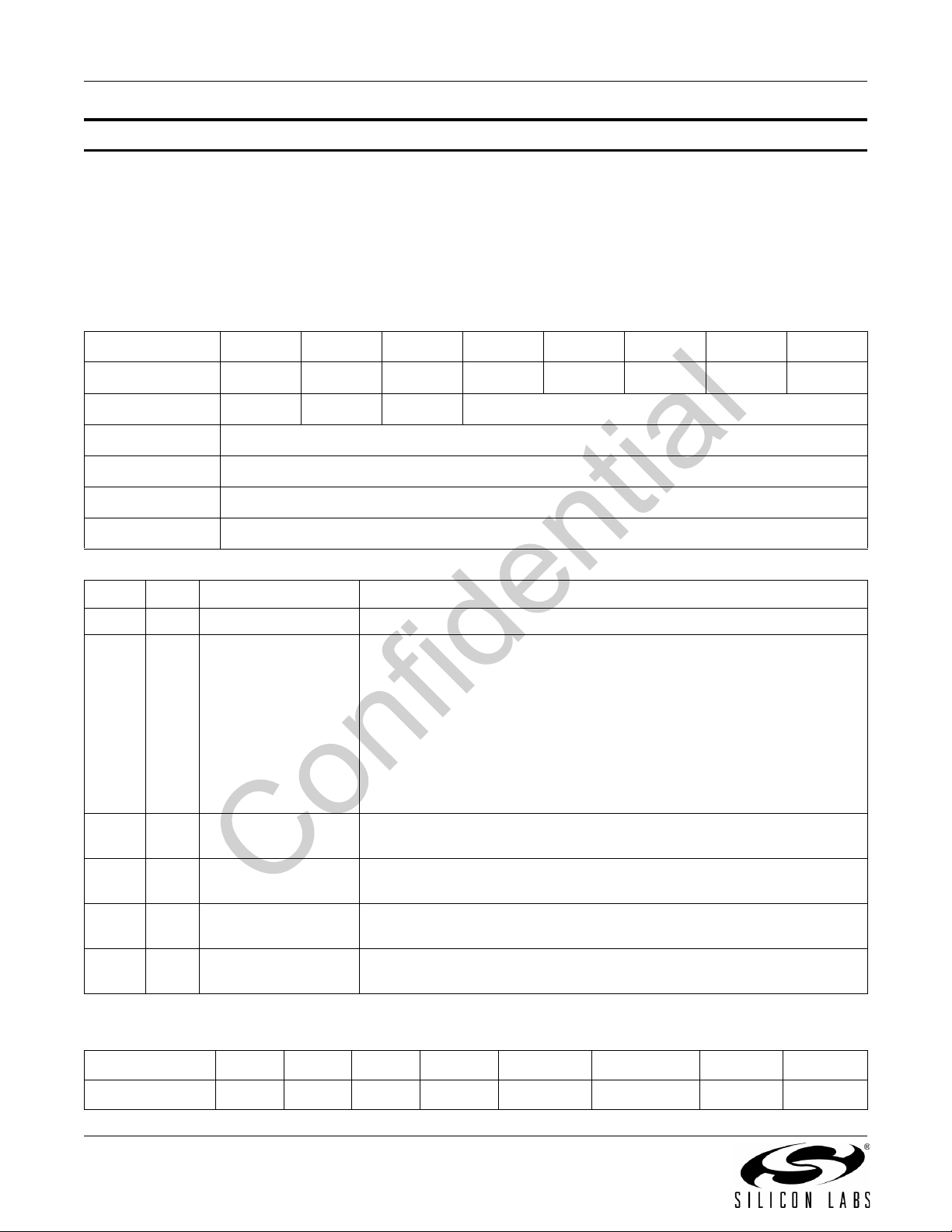

Table 2 shows an example of tuning to a frequency using the TX_TUNE_FREQ command. This command requires

that a command and three arguments be sent and returns one status byte. The table is broken into three columns.

The first column lists the action taking place: command (CMD), argument (ARG), status (STATUS), or response

(RESP). The second column lists the data byte or bytes in hexadecimal that are being sent or received. An arrow

preceding the data indicates data being sent from the device to the system controller. The third column describes

the action.

Table 2. Using the TX_TUNE_FREQ Command

Action Data Description

CMD 0x30 TX_TUNE_FREQ

ARG1 0x00

ARG2 0x27 Set Station to 101.1 MHz

ARG3 0x7E (0x277E = 10110 with 10 kHz step size)

STATUS

→0x80 Reply Status. Clear-to-send high.

Properties are special command arguments used to modify the default device operation and are generally

configured immediately after power-up. Examples of properties are TX _PREEMPHASIS and REFCLK_FREQ. A

complete list of properties is available in “5. Commands and Properties”.

Table 3 shows an example of setting the REFCLK frequency using the REFCLK_FREQ property by sending the

SET_PROPERTY command and five argument bytes. ARG1 of the SET_PROPERTY command is always 0x00.

ARG2 and ARG3 are used to select the property number, PROP (0x0201 in this example), and ARG4 and ARG5

are used to set the property value, PROPD (0x8000 or 32768 Hz in the example).

Table 3. Using the SET_PROPERTY Command

Action Data Description

CMD 0x12 SET_PROPERTY

ARG1 0x00

ARG2 (PROP) 0x02 REFCLK_FREQ

ARG3 (PROP) 0x01

ARG4 (PROPD) 0x80 32768 Hz

ARG5 (PROPD) 0x00

STATUS

The implementation of the command and response procedures in the system controller differs for each of the three

bus modes. Section "6. Control Interface" on page 168 details the required bit transactions on the control bus for

each of the bus modes.

→0x80 Reply Status. Clear-to-send high.

Confidential Rev. 0.2 5

Page 6

AN332

5. Commands and Properties

There are four different components for these product families:

1. FM Transmitter component

2. FM Receiver component

3. AM/SW/LW component

4. WB component

The following four subsections list all the commands and properties used by each of the component.

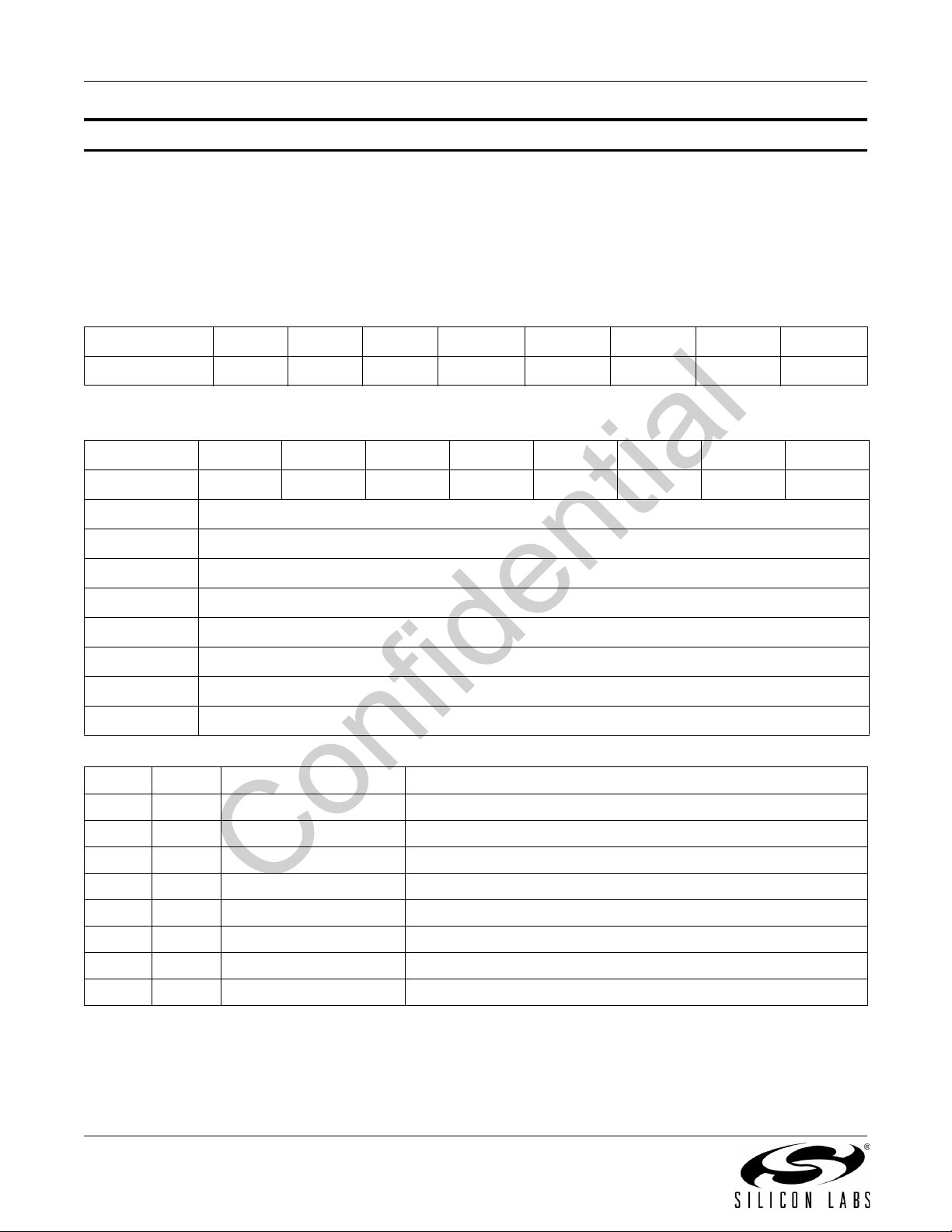

5.1. Commands and Properties for the FM/RDS Transmitter (Si4710/11/12/13/20/21)

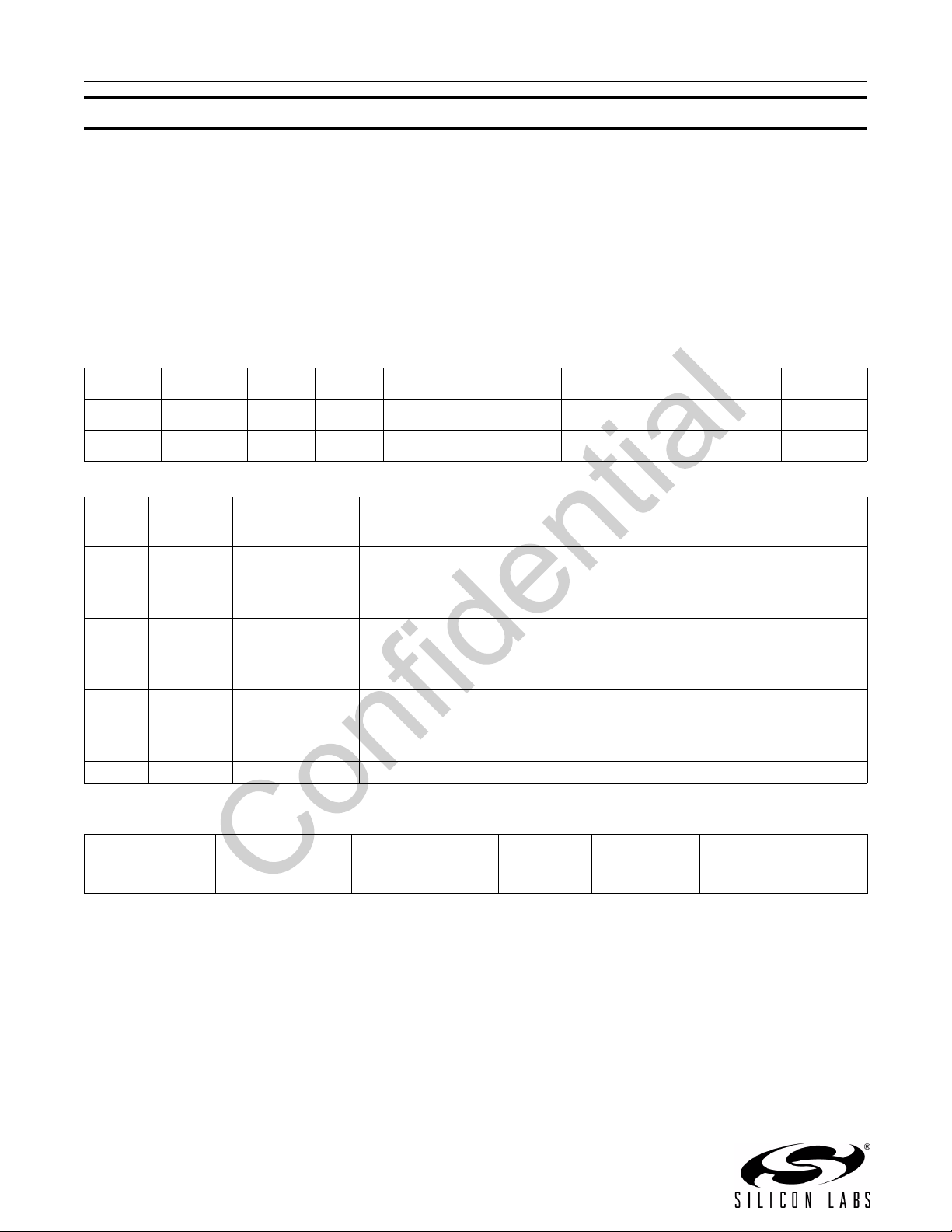

The following two tables are the summary of the commands and properties for the FM/RDS Transmitter component

applicable to Si4710/11/12/13/20/21.

Table 4. FM/RDS Transmitter Command Summary

Cmd Name Description

0x01 POWER_UP

0x10 GET_REV Returns revision information on the device.

0x11 POWER_DOWN Power down device.

0x12 SET_PROPERTY Sets the value of a property.

0x13 GET_PROPERTY Retrieves a property’s value.

0x14 GET_INT_STATUS Read interrupt status bits.

0x15 PATCH_ARGS Reserved command used for patch file downloads.

0x16 PATCH_DATA Reserved command used for patch file downloads.

0x30 TX_TUNE_FREQ Tunes to given transmit frequency.

0x31 TX_TUNE_POWER Sets the output power level and tunes the antenna capacitor.

0x32 TX_TUNE_MEASURE

0x33 TX_TUNE_STATUS

0x34 TX_ASQ_STATUS Queries the TX status and input audio signal metrics.

0x35 TX_RDS_BUFF

0x36 TX_RDS_PS

0x80 GPIO_CTL

0x81 GPIO_SET

1

1

2

2

Power up device and mode selection. Modes include FM transmit

and analog/digital audio interface configuration.

Si4712/13/20/21 Only. Measure the received noise level at the

specified frequency.

Queries the status of a previously sent TX Tune Freq, TX Tune

Power, or TX Tune Measure command.

Si4711/13/21 Only. Queries the status of the RDS Group Buffer

and loads new data into buffer.

Si4711/13/21 Only. Set up default PS strings.

Configures GPO1, 2, and 3 as output or Hi-Z.

Sets GPO1, 2, and 3 output level (low or high).

Notes:

RDS feature (command TX_RDS_BUFF, TX_RDS_PS and RDS properties 0x2103, 0x2C00 through

1.

2C07) is supported in FMTX component 2.0 or higher.

2. GPIO feature (command GPIO_CTL and GPIO_SET) is fully supported in FMTX component 3.0 or higher.

It is partially supported (GPO3 only) in FMTX component 2.0.

6 Confidential Rev. 0.2

Page 7

AN332

Table 5. FM Transmitter Property Summary

Prop Name Description Default

0x0001 GPO_IEN Enables interrupt sources. 0x0000

0x0101 DIGITAL_INPUT _FORMAT

0x0103 DIGITAL_INPUT _SAMPLE_RATE

0x0201 REFCLK_FREQ

0x0202 REFCLK_PRESCALE Sets the prescaler value for the reference clock. 0x0001

0x2100 TX_COMPONENT_ENABLE

0x2101 TX_AUDIO_DEVIATION

0x2102 TX_PILOT_DEVIATION

0x2103 TX_RDS_DEVIATION

0x2104 TX_LINE_INPUT_LEVEL

0x2105 TX_LINE_INPUT_MUTE

0x2106 TX_PREEMPHASIS

0x2107 TX_PILOT_FREQUENCY

0x2200 TX_ACOMP_ENABLE

0x2201 TX_ACOMP_THRESHOLD

0x2202 TX_ACOMP_ATTACK_TIME

0x2203 TX_ACOMP_RELEASE_TIME

Notes:

1. Digital Audio Input feature (property DIGITAL_INPUT_FORMAT and DIGITAL_INPUT_SAMPLE_RATE) is

supported in FMTX component 2.0 or higher.

2. RDS feature (command TX_RDS_BUFF, TX_RDS_PS and RDS properties 0x2103, 0x2C00 through

2C07) is supported in FMTX component 2.0 or higher.

3. Limiter feature (LIMITEN bit in TX_ACOMP_ENABLE and property TX_LIMITER_RELEASE_TIME) is

supported in FMTX component 2.0 or higher.

1

Configures the digital input format. 0x0000

Configures the digital input sample rate in 1 Hz steps.

1

Default is 0.

0x0000

Sets frequency of the reference clock in Hz. The range

is 31130 to 34406 Hz, or 0 to disable the AFC. Default is

0x8000

32768 Hz.

Enable transmit multiplex signal components.

Default has pilot and L-R enabled.

Configures audio frequency deviation level. Units are in

10 Hz increments. Default is 6825 (68.25 kHz).

Configures pilot tone frequency deviation level. Units

are in 10 Hz increments. Default is 675 (6.75 kHz)

2

Si4711/13/21 Only. Configures the RDS/RBDS frequency deviation level. Units are in 10 Hz increments.

0x0003

0x1AA9

0x02A3

0x00C8

Default is 2 kHz.

Configures maximum analog line input level to the

LIN/RIN pins to reach the maximum deviation level

programmed into the audio deviation property TX

Audio Deviation. Default is 636 mV

PK

.

Sets line input mute. L and R inputs may be independently muted. Default is not muted.

Configures pre-emphasis time constant.

Default is 0 (75 µS).

Configures the frequency of the stereo pilot. Default is

19000 Hz.

0x327C

0x0000

0x0000

0x4A38

Enables audio dynamic range control and limiter.

3

Default is 2 (limiter is enabled, audio dynamic range

0x0002

control is disabled).

Sets the threshold level for audio dynamic range control.

0xFFD8

Default is –40 dB.

Sets the attack time for audio dynamic range control.

Default is 0 (0.5 ms).

Sets the release time for audio dynamic range control.

Default is 4 (1000 ms).

0x0000

0x0004

Confidential Rev. 0.2 7

Page 8

AN332

Table 5. FM Transmitter Property Summary (Continued)

Prop Name Description Default

0x2204 TX_ACOMP_GAIN

0x2205 TX_LIMITER_RELEASE_TIME

0x2300 TX_ASQ_INTERRUPT_SOURCE

0x2301 TX_ASQ_LEVEL_LOW

0x2302 TX_ASQ_DURATION_LOW

0x2303 TX_ASQ_LEVEL_HIGH

0x2304 TX_ASQ_DURATION_HIGH

0x2C00 TX_RDS_INTERRUPT_SOURCE

0x2C01 TX_RDS_PI

0x2C02 TX_RDS_PS_MIX

0x2C03 TX_RDS_PS_MISC

2

2

2

0x2C04 TX_RDS_PS_REPEAT_COUNT

0x2C05 TX_RDS_PS_MESSAGE_COUNT

0x2C06 TX_RDS_PS_AF

0x2C07 TX_RDS_FIFO_SIZE

Notes:

2

2

1. Digital Audio Input feature (property DIGITAL_INPUT_FORMAT and DIGITAL_INPUT_SAMPLE_RATE) is

supported in FMTX component 2.0 or higher.

2. RDS feature (command TX_RDS_BUFF, TX_RDS_PS and RDS properties 0x2103, 0x2C00 through

2C07) is supported in FMTX component 2.0 or higher.

3. Limiter feature (LIMITEN bit in TX_ACOMP_ENABLE and property TX_LIMITER_RELEASE_TIME) is

supported in FMTX component 2.0 or higher.

Sets the gain for audio dynamic range control.

Default is 15 dB.

3

Sets the limiter release time. Default is 102 (5.01 ms) 0x0066

Configures measurements related to signal quality

metrics. Default is none selected.

Configures low audio input level detection threshold.

This threshold can be used to detect silence on the

incoming audio.

Configures the duration which the input audio level

must be below the low threshold in order to detect a

low audio condition.

Configures high audio input level detection threshold.

This threshold can be used to detect activity on the

incoming audio.

Configures the duration which the input audio level

must be above the high threshold in order to detect a

high audio condition.

Si4711/13/21 Only. Configure RDS interrupt sources.

2

Default is none selected.

Si4711/13/21 Only. Sets transmit RDS program identifier.

Si4711/13/21 Only. Configures mix of RDS PS Group

with RDS Group Buffer.

Si4711/13/21 Only. Miscellaneous bits to transmit

along with RDS_PS Groups.

Si4711/13/21 Only. Number of times to repeat trans-

2

mission of a PS message before transmitting the next

PS message.

2

Si4711/13/21 Only. Number of PS messages in use. 0x0001

Si4711/13/21 Only. RDS Program Service Alternate

Frequency. This provides the ability to inform the

receiver of a single alternate frequency using AF

Method A coding and is transmitted along with the

RDS_PS Groups.

Si4711/13/21 Only. Number of blocks reserved for the

FIFO. Note that the value written must be one larger

than the desired FIFO size.

0x000F

0x0000

0x0000

0x0000

0x0000

0x0000

0x0000

0x40A7

0x0003

0x1008

0x0003

0xE0E0

0x0000

8 Confidential Rev. 0.2

Page 9

AN332

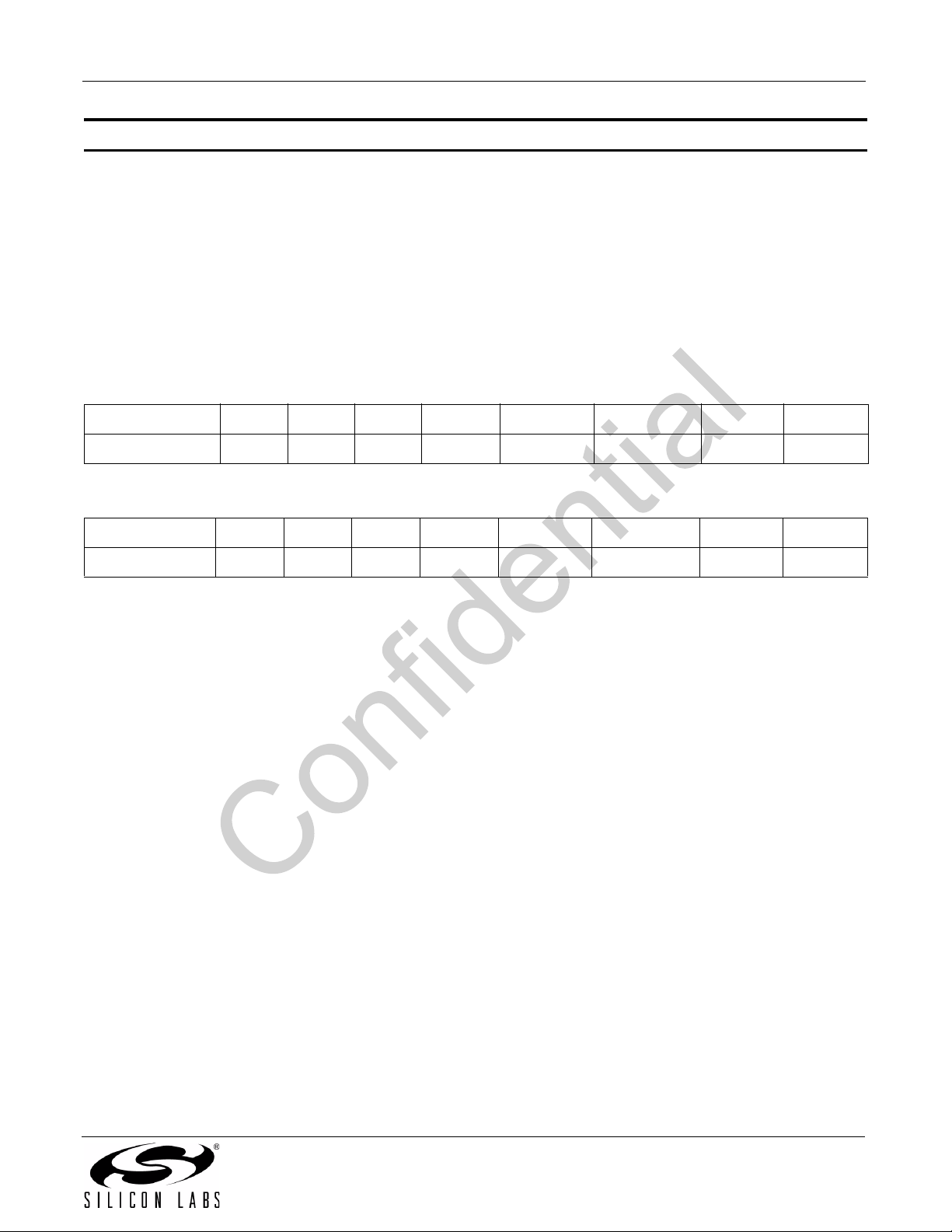

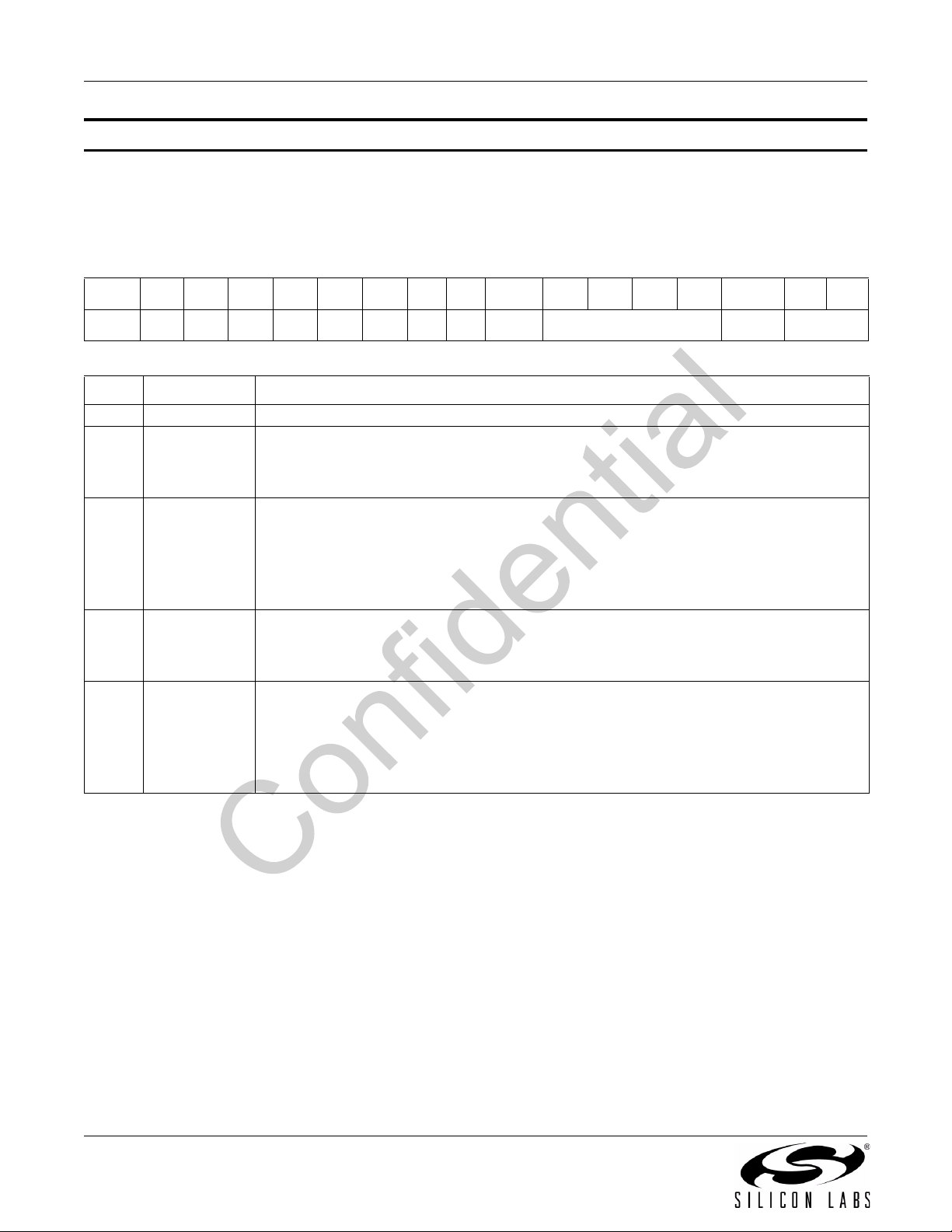

Table 6. Status Response

BitD7D6D5D4D3D2D1D0

STATUS CTS ERR X X X RDSINT ASQINT STCINT

Bit Name Function

Clear to Send.

7CTS

6ERR

5:3 Reserved Values may vary.

2 RDSINT

1 ASQINT

0STCINT

0 = Wait before sending next command.

1 = Clear to send next command.

Error.

0=No error

1 = Error

RDS Interrupt.

0 = RDS interrupt has not been triggered.

1 = RDS interrupt has been triggered.

Signal Quality Interrupt.

0 = Signal quality measurement has not been triggered.

1 = Signal quality measurement has been triggered.

Seek/Tune Complete Interrupt.

0 = Tune complete has not been triggered.

1 = Tune complete has been triggered.

Confidential Rev. 0.2 9

Page 10

AN332

5.1.1. Commands and Properties for the FM/RDS Transmitter

Command 0x01. POWER_UP

Initiates the boot process to move the device from powerdown to powerup mode. The boot can occur from internal

device memory or a system controller downloaded patch. To confirm that the patch is compatible with the internal

device library revision, the library revision should be confirmed by issuing the POWER_UP command with

Function = 15 (query library ID). The device will return the response, including the library revision, and then moves

into powerdown mode. The device can then be placed in powerup mode by issuing the POWER_UP command

with Function = 2 (transmit) and the patch may be applied. Only the STATUS byte will be returned in the response

stream in transmit mode. The POWER_UP command configures the state of DIN (pin 13), DFS (pin 14), and RIN

(pin 15) and LIN (pin 16) for analog or digital audio modes and GPO2/INT (pin 18) for interrupt operation. The

command configures GPO2/INT interrupts (GPO2OEN) and CTS interrupts (CTSIEN). If both are enabled,

GPO2/INT is driven high during normal operation and low for a minimum of 1 µs during the interrupt. The CTSIEN

bit is duplicated in the GPO_IEN property. The command is complete when the CTS bit (and optional interrupt) is

set.

Note: To change function (e.g., FM TX to FM RX), issue the POWER_DOWN command to stop the current function; then,

issue POWER_UP to start the new function.

Command Arguments: Two

Response Bytes: None (FUNC = 2), Seven (FUNC = 15)

Command

Bit D7D6D5D4D3D2D1D0

CMD

ARG1

ARG2

ARG Bit Name Function

1 7 CTSIEN

1 6 GPO2OEN

15 PATCH

1 4 XOSCEN

00000001

CTSIEN GPO2OEN PATCH XOSCEN FUNC[3:0]

OPMODE[7:0]

CTS Interrupt Enable.

0 = CTS interrupt disabled.

1 = CTS interrupt enabled.

GPO2 Output Enable.

0 = GPO2 output disabled, (Hi-Z).

1 = GPO2 output enabled.

Patch Enable.

0 = Boot normally

1 = Copy non-volatile memory to RAM, but do not boot. After CTS has been set,

RAM may be patched

Crystal Oscillator Enable.

0 = Use external RCLK (crystal oscillator disabled).

1 = Use crystal oscillator (RCLK and GPO3/DCLK with external 32.768 kHz crys-

tal and OPMODE=00000101).

See Si47xx Data Sheet Application Schematic for external BOM details.

10 Confidential Rev. 0.2

Page 11

AN332

Function.

1 3:0 FUNC[3:0]

2 7:0 OPMODE[7:0]

Response (to FUNC = 2, TX)

Bit D7D6D5 D4 D3 D2 D1 D0

STATUS CTS ERR X X X RDSINT ASQINT STCINT

Response (to FUNC = 15, Query Library ID)

Bit D7 D6 D5 D4 D3 D2 D1 D0

STATUS CTS ERR X X X RDSINT ASQINT STCINT

RESP1 PN[7:0]

0–1, 3–14 = Reserved.

2 = Transmit.

15 = Query Library ID.

Application Setting

01010000 = Analog audio inputs (LIN/RIN)

00001111 = Digital audio inputs (DIN/DFS/DCLK)

RESP2 FWMAJOR[7:0]

RESP3 FWMINOR[7:0]

RESP4 RESERVED[7:0]

RESP5 RESERVED[7:0]

RESP6 CHIPREV[7:0]

RESP7 LIBRARYID[7:0]

RESP Bit Name Function

1 7:0 PN[7:0] Final 2 digits of part number.

2 7:0 FWMAJOR[7:0] Firmware Major Revision.

3 7:0 FWMINOR[7:0] Firmware Minor Revision.

4 7:0 RESERVED[7:0] Reserved, various values.

5 7:0 RESERVED[7:0] Reserved, various values.

6 7:0 CHIPREV[7:0] Chip Revision.

7 7:0 LIBRARYID[7:0] Library Revision.

Confidential Rev. 0.2 11

Page 12

AN332

Command 0x10. GET_REV

Returns the part number, chip revision, firmware revision, patch revision and component revision numbers. The

command is complete when the CTS bit (and optional interrupt) is set. This command may only be sent when in

powerup mode.

Command arguments: None

Response bytes: Eight

Command

Bit D7D6D5 D4 D3 D2 D1 D0

CMD

000 1 0 0 0 0

Response

Bit D7D6D5D4D3D2D1D0

STATUS

RESP1

RESP2

RESP3

RESP4

RESP5

RESP6

RESP7

RESP8

CTS ERR X X X RDSINT ASQINT STCINT

PN[7:0]

FWMAJOR[7:0]

FWMINOR[7:0]

PATCH

PATCH

H

L

[7:0]

[7:0]

CMPMAJOR[7:0]

CMPMINOR[7:0]

CHIPREV[7:0]

RESP Bit Name Function

1 7:0 PN[7:0] Final 2 digits of Part Number

2 7:0 FWMAJOR[7:0] Firmware Major Revision

3 7:0 FWMINOR[7:0] Firmware Minor Revision

4 7:0 PATCH

5 7:0 PATCH

[7:0] Patch ID High Byte

H

[7:0] Patch ID Low Byte

L

6 7:0 CMPMAJOR[7:0] Component Major Revision

7 7:0 CMPMINOR[7:0] Component Minor Revision

8 7:0 CHIPREV[7:0] Chip Revision

12 Confidential Rev. 0.2

Page 13

AN332

Command 0x11. POWER_DOWN

Moves the device from powerup to powerdown mode. The CTS bit (and optional interrupt) is set when it is safe to

send the next command. This command may only be sent when in powerup mode. Note that only the POWER_UP

command is accepted in powerdown mode. If the system controller writes a command other than POWER_UP

when in powerdown mode, the device does not respond. The device will only respond when a POWER_UP

command is written.

Note: In FMTX component 1.0 and 2.0, a reset is required when the system controller writes a command other than

POWER_UP when in powerdown mode.

Command arguments: None

Response bytes: None

Command

Bit D7 D6 D5 D4 D3 D2 D1 D0

CMD

Response

Bit D7D6D5 D4 D3 D2 D1 D0

STATUS CTS ERR X X X RDSINT ASQINT STCINT

000 1 0 0 0 1

Confidential Rev. 0.2 13

Page 14

AN332

Command 0x12. SET_PROPERTY

Sets a property shown in Table 5, “FM Transmitter Property Summary,” on page 7. The CTS bit (and optional

interrupt) is set when it is safe to send the next command. This command may only be sent when in powerup

mode.

See Figure 18, “CTS and SET_PROPERTY Command Complete tCOMP Timing Model,” on page 187 and

Table 41, “Command Timing Parameters for the FM Transmitter,” on page 188.

Note: The use of GPO2 as an interrupt pin and/or the use of GPO3 as DCLK digital clock input will override this GPIO_CTL

function for GPO2 and/or GPO3.

Command Arguments: Five

Response bytes: None

Command

Bit D7D6D5D4D3D2D1D0

CMD

ARG1

ARG2

ARG3

ARG4

ARG5

00010010

00000000

PROP

PROP

PROPD

PROPD

[7:0]

H

[7:0]

L

H

L

[7:0]

[7:0]

ARG Bit Name Function

1 7:0 Reserved Always write to 0.

Property High Byte.

2 7:0 PROP

H

[7:0]

This byte in combination with PROP

is used to specify the property to

L

modify. See Section "5.1.2. FM/RDS Transmitter Properties" on page 29.

Property Low Byte.

3 7:0 PROP

[7:0]

L

This byte in combination with PROP

is used to specify the property to

H

modify. See Section "5.1.2. FM/RDS Transmitter Properties" on page 29.

Property Value High Byte.

4 7:0 PROPD

H

[7:0]

This byte in combination with PROPV

is used to set the property value.

L

See Section "5.1.2. FM/RDS Transmitter Properties" on page 29.

Property Value Low Byte.

5 7:0 PROPD

L

[7:0]

This byte in combination with PROPV

is used to set the property value.

H

See Section "5.1.2. FM/RDS Transmitter Properties" on page 29.

Response

Bit D7D6D5 D4 D3 D2 D1 D0

STATUS CTS ERR X X X RDSINT ASQINT STCINT

14 Confidential Rev. 0.2

Page 15

AN332

Command 0x13. GET_PROPERTY

Gets a property shown in Table 5, “FM Transmitter Property Summary,” on page 7. The CTS bit (and optional

interrupt) is set when it is safe to send the next command. This command may only be sent when in powerup

mode.

Command arguments: Three

Response bytes: Three

Command

Bit D7D6D5D4D3D2D1D0

CMD

ARG1

ARG2

ARG3

00010011

00000000

PROP

PROP

H

L

[7:0]

[7:0]

ARG Bit Name Function

1 7:0 Reserved Always write to 0.

27:0 PROP

37:0 PROP

H

L

[7:0]

[7:0]

Property Get High Byte.

This byte in combination with PROP

Property Get Low Byte.

This byte in combination with PROP

is used to specify the property to get.

L

is used to specify the property to get.

H

Response

BitD7D6D5D4D3D2D1D0

STATUS

RESP1

RESP2

RESP3

CTS ERR X X X RDSINT ASQINT STCINT

XXXXXXXX

PROPD

PROPD

[7:0]

H

[7:0]

L

RESP Bit Name Function

1 7:0 Reserved Reserved, various values.

Property Value High Byte.

27:0PROPD

H

[7:0]

This byte in combination with PROPV

will represent the requested prop-

L

erty value.

Property Value High Byte.

37:0PROPD

[7:0]

L

This byte in combination with PROPV

will represent the requested prop-

H

erty value.

Confidential Rev. 0.2 15

Page 16

AN332

Command 0x14. GET_INT_STATUS

Updates bits 6:0 of the status byte. This command should be called after any command that sets the STCINT,

ASQINT, or RDSINT bits. When polling this command should be periodically called to monitor the STATUS byte,

and when using interrupts, this command should be called after the interrupt is set to update the STATUS byte. The

command is complete when the CTS bit (and optional interrupt) is set. This command may only be sent when in

powerup mode.

Command arguments: None

Response bytes: One

Command

Bit D7D6D5D4D3D2D1D0

CMD

Response

BitD7D6D5D4D3D2D1D0

STATUS

CTS ERR X X X RDSINT ASQINT STCINT

00010100

16 Confidential Rev. 0.2

Page 17

AN332

Command 0x30. TX_TUNE_FREQ

Sets the state of the RF carrier and sets the tuning frequency between 76 and 108 MHz in 10 kHz units and steps

of 50 kHz. For example 76.05 MHz = 7605 is valid because it follows the 50 kHz step requirement but

76.01 MHz = 7601 is not valid. The CTS bit (and optional interrupt) is set when it is safe to send the next

command. The ERR bit (and optional interrupt) is set if an invalid argument is sent. Note that only a single interrupt

occurs if both the CTS and ERR bits are set. The optional STC interrupt is set when the command completes. The

STCINT bit is set only after the GET_INT_STATUS command is called. This command may only be sent when in

powerup mode. The command clears the STC bit if it is already set. See Figure 17, “CTS and STC Timing Model,”

on page 187 and Table 41, “Command Timing Parameters for the FM Transmitter,” on page 188.

Command arguments: Three

Response bytes: None

Command

Bit D7D6D5D4D3D2D1D0

CMD

ARG1

ARG2

ARG3

00110000

00000000

FREQ

FREQ

H

L

[7:0]

[7:0]

ARG Bit Name Function

1 7:0 Reserved Always write to 0.

Tune Frequency High Byte.

27:0FREQ

H

[7:0]

This byte in combination with FREQ

10 kHz. The valid range is from 7600 to 10800 (76–108 MHz). The frequency

selects the tune frequency in units of

L

must be a multiple of 50 kHz.

Tune Frequency Low Byte.

37:0FREQ

[7:0]

L

This byte in combination with FREQ

10 kHz. The valid range is from 7600 to 10800 (76–108 MHz). The frequency

selects the tune frequency in units of

H

must be a multiple of 50 kHz.

Response

Bit D7D6D5 D4 D3 D2 D1 D0

STATUS CTS ERR X X X RDSINT ASQINT STCINT

Confidential Rev. 0.2 17

Page 18

AN332

Command 0x31. TX_TUNE_POWER

Sets the RF voltage level between 88 dBµV and 115 dBµV in 1 dB units. Power may be set as high as 120 dBµV;

however, voltage accuracy is not guaranteed. A value of 0x00 indicates off. The command also sets the antenna

tuning capacitance. A value of 0 indicates autotuning, and a value of 1–191 indicates a manual override. The CTS

bit (and optional interrupt) is set when it is safe to send the next command. The ERR bit (and optional interrupt) is

set if an invalid argument is sent. Note that only a single interrupt occurs if both the CTS and ERR bits are set. The

optional STC interrupt is set when the command completes. The STCINT bit is set only after the

GET_INT_STATUS command is called. This command may only be sent when in powerup mode. The command

clears the STC bit if it is already set. See Figure 17, “CTS and STC Timing Model,” on page 187 and Table 41,

“Command Timing Parameters for the FM Transmitter,” on page 188.

Command arguments: Four

Response bytes: None

Command

Bit D7D6D5D4D3D2D1D0

CMD

ARG1

ARG2

ARG3

ARG4

ARG Bit Name Function

1 7:0 Reserved Always write to 0.

2 7:0 Reserved Always write to 0.

3 7:0 RFdBµV[7:0]

4 7:0 ANTCAP[7:0]

Response

00110001

00000000

00000000

RFdBµV[7:0]

ANTCAP[7:0]

Tune Power Byte.

Sets the tune power in dBµV in 1 dB steps. The valid range is from 88–

115 dBµV. Power may be set as high as 120 dBµV; however, voltage accuracy is not guaranteed.

Antenna Tuning Capacitor.

This selects the value of the antenna tuning capacitor manually, or automatically if set to zero. The valid range is 0 to 191, which results in a tuning

capacitance of 0.25 pF x ANTCAP.

Bit D7D6D5 D4 D3 D2 D1 D0

STATUS CTS ERR X X X RDSINT ASQINT STCINT

18 Confidential Rev. 0.2

Page 19

AN332

Command 0x32. TX_TUNE_MEASURE (Si4712/13/20/21 Only)

Enters receive mode (disables transmitter output power) and measures the received noise level (RNL) in units of

dBµV on the selected frequency. The command sets the tuning frequency between 76 and 108 MHz in 10 kHz

units and steps of 50 kHz. For example 76.05 MHz = 7605 is valid because it follows the 50 kHz step requirement

but 76.01 MHz = 7601 is not valid. The command also sets the antenna tuning capacitance. A value of 0 indicates

autotuning, and a value of 1–191 indicates a manual override. The CTS bit (and optional interrupt) is set when it is

safe to send the next command. The ERR bit (and optional interrupt) is set if an invalid argument is sent. Note that

only a single interrupt occurs if both the CTS and ERR bits are set. The optional STC interrupt is set when the

command completes. The STCINT bit is set only after the GET_INT_STATUS command is called. This command

may only be sent when in powerup mode. The command clears the STC bit if it is already set. See Figure 17, “CTS

and STC Timing Model,” on page 187 and Table 41, “Command Timing Parameters for the FM Transmitter,” on

page 188.

Command arguments: Three

Response bytes: None

Command

Bit D7D6D5D4D3D2D1D0

CMD

ARG1

ARG2

ARG3

ARG4

00110010

00000000

FREQ

FREQ

H

L

[7:0]

[7:0]

ANTCAP[7:0]

ARG Bit Name Function

1 7:0 Reserved Always write to 0.

Tune Frequency High Byte.

27:0 FREQ

H

[7:0]

This byte in combination with FREQ

10 kHz. In FM mode the valid range is from 7600 to 10800 (76–108 MHz).

selects the tune frequency in units of

L

The frequency must be a multiple of 50 kHz.

Tune Frequency Low Byte.

37:0 FREQ

L

[7:0]

This byte in combination with FREQ

10 kHz. In FM mode the valid range is from 7600 to 10800 (76–108 MHz).

selects the tune frequency in units of

H

The frequency must be a multiple of 50 kHz.

Antenna Tuning Capacitor.

4 7:0 ANTCAP[7:0]

This selects the value of the antenna tuning capacitor manually, or automatic if set to zero. The valid range is 0–191.

Response

Bit D7D6D5 D4 D3 D2 D1 D0

STATUS CTS ERR X X X RDSINT ASQINT STCINT

Confidential Rev. 0.2 19

Page 20

AN332

Command 0x33. TX_TUNE_STATUS

Returns the status of the TX_TUNE_FREQ, TX_TUNE_MEASURE, or TX_TUNE_POWER commands. The

command returns the current frequency, output voltage in dBµV (if applicable), the antenna tuning capacitance

value (0–191) and the received noise level (if applicable). The command clears the STCINT interrupt bit when

INTACK bit of ARG1 is set. The CTS bit (and optional interrupt) is set when it is safe to send the next command.

This command may only be sent when in powerup mode.

Command arguments: One

Response bytes: Seven

Command

Bit D7D6D5D4D3D2D1D0

CMD

ARG1

ARG Bit Name Function

1 7:1 Reserved Always write to 0.

10 INTACK

Response

BitD7D6D5D4D3D2D1D0

STATUS

RESP1

RESP2

RESP3

RESP4

RESP5

CTS ERR X X X RDSINT ASQINT STCINT

00110011

0000000INTACK

Seek/Tune Interrupt Clear.

If set this bit clears the seek/tune complete interrupt status indicator.

XXXXXXXX

READFREQ

READFREQ

XXXXXXXX

READRFdBµV[7:0]

H

L

[7:0]

[7:0]

RESP6

RESP7

20 Confidential Rev. 0.2

READANTCAP[7:0]

RNL[7:0]

Page 21

RESP Bit Name Function

1 7:0 Reserved Returns various data.

Read Frequency High Byte.

2 7:0 READFREQ

H

[7:0]

This byte in combination with READFREQ

tuned.

37:0READFREQ

L

[7:0]

Read Frequency Low Byte.

This byte in combination with READFREQ

4 7:0 Reserved Returns various data.

5 7:0 READRFdBµV[7:0]

6 7:0 READANTCAP [7:0]

Read Power.

Returns the transmit output voltage setting.

Read Antenna Tuning Capacitor.

This byte will contain the current antenna tuning capacitor value.

Read Received Noise Level (Si4712/13 Only).

This byte will contain the receive level as the response to a TX Tune Mea-

7 7:0 RNL[7:0]

sure command. The returned value will be the last RNL measurement (or

0 if no measurement has been performed) for the TX Tune Freq and TX

Tune Power commands.

AN332

returns frequency being

L

returns frequency being tuned.

H

Confidential Rev. 0.2 21

Page 22

AN332

Command 0x34. TX_ASQ_STATUS

Returns status information about the audio signal quality and current FM transmit frequency. This command can be

used to check if the input audio stream is below a low threshold as reported by the IALL bit, or above a high

threshold as reported by the IALH bit. The thresholds can be configured to detect a silence condition or an activity

condition which can then be used by the host to take an appropriate action such as turning off the carrier in the

case of prolonged silence. The thresholds are set using the TX_ASQ_LEVEL_LOW and TX_ASQ_LEVEL_HIGH

properties. The audio must be above or below the threshold for greater than the amount of time specified in the

TX_ASQ_DURATION_LOW and TX_ASQ_DURATION_HIGH properties for the status to be detected. Additionally

the command can be used to determine if an overmodulation condition has occurred or the limiter has engaged, as

reported by the OVERMOD bit, in which case the host could reduce the audio level to the part. If any of the

OVERMOD, IALH, or IALL bits are set, the ASQINT bit will also be set. The ASQINT bit can be routed to a

hardware interrupt via the GPO_IEN property.

Clearing the IALH or IALL interrupts will result in the TX_ASQ_DURATION_LOW or TX_ASQ_DURATION_HIGH

counters being rearmed, respectively, to start another detection interval measurement. The command clears the

ASQINT interrupt bit and OVERMOD, IALH, and IALL bits when the INTACK bit of ARG1 is set. The CTS bit (and

optional interrupt) is set when it is safe to send the next command. This command may only be sent when in

powerup mode.

Note that the TX_ASQ_DURATION_LOW and TX_ASQ_DURATION_HIGH counters start and the

TX_ASQ_STATUS command will only return valid data after a call to TX_TUNE_FREQ, TX_TUNE_POWER, or

TX_TUNE_MEASURE.

Command arguments: One

Response bytes: Four

Command

Bit D7D6D5D4D3D2D1D0

CMD

ARG1

ARG Bit Name Function

10 INTACK

00110100

0000000INTACK

Interrupt Acknowledge.

0 = Interrupt status preserved.

1 = Clears ASQINT, OVERMOD, IALDH, and IALDL.

22 Confidential Rev. 0.2

Page 23

AN332

Response

Bit D7D6D5D4D3 D2 D1 D0

STATUS

RESP1

RESP2

RESP3

RESP4

RESP Bit Name Function

1 2 OVERMOD

11 IALH

10 IALL

27:0 Reserved Returns various values.

CTS ERR X X X RDSINT ASQINT STCINT

X X X X X OVERMOD IALH IALL

XXXXX X X X

XXXXX X X X

INLEVEL[7:0]

Overmodulation Detection.

0 = Output signal is below requested modulation level.

1 = Output signal is above requested modulation level.

Input Audio Level Threshold Detect High.

0 = Input audio level high threshold not exceeded.

1 = Input audio level high threshold exceeded.

Input Audio Level Threshold Detect Low.

0 = Input audio level low threshold not exceeded.

1 = Input audio level low threshold exceeded.

37:0 Reserved Returns various values.

Input Audio Level.

4 7:0 INLEVEL[7:0]

The current audio input level measured in dBfs (2s complement notation).

Confidential Rev. 0.2 23

Page 24

AN332

Command 0x35. TX_RDS_BUFF (Si4711/13/21 Only)

Loads or clears the RDS group buffer FIFO or circular buffer and returns the FIFO status. The buffer can be

allocated between the circular buffer and FIFO with the TX_RDS_FIFO_SIZE property. A common use case for the

circular buffer is to broadcast group 2A radio text, and a common use case for the FIFO is to broadcast group 4A

real time clock. The command clears the INTACK interrupt bit when the INTACK bit of ARG1 is set. The CTS bit

(and optional interrupt) is set when it is safe to send the next command. This command may only be sent when in

powerup mode.

Note: TX_RDS_BUFF is supported in FMTX component 2.0 or higher.

Command arguments: Seven

Response bytes: Five

Command

Bit D7D6D5D4D3D2D1D0

CMD

ARG1

ARG2

ARG3

ARG4

ARG5

ARG6

ARG7

00110101

FIFO 0 0 0 0 LDBUFF MTBUFF INTACK

H

L

H

L

H

L

[7:0]

[7:0]

[7:0]

[7:0]

[7:0]

[7:0]

RDSB

RDSB

RDSC

RDSC

RDSD

RDSD

ARG Bit Name Function

Operate on FIFO.

1 7 FIFO

If set, the command operates on the FIFO buffer. If cleared, the command

operates on the circular buffer.

1 6:3 Reserved Always write to 0.

Load RDS Group Buffer.

12 LDBUFF

If set, loads the RDS group buffer with RDSB, RDSC, and RDSD. Block A

data is generated from the RDS_TX_PI property when the buffer is transmitted.

11 MTBUFF

10 INTACK

27:0 RDSB

37:0 RDSB

[7:0]

H

[7:0]

L

Empty RDS Group Buffer.

If set, empties the RDS group buffer.

Clear RDS Group buffer interrupt.

If set this bit clears the RDS group buffer interrupt indicator.

RDS Block B High Byte.

This byte in combination with RDSB

sets the RDS block B data.

L

RDS Block B Low Byte.

This byte in combination with RDSB

sets the RDS block B data.

H

24 Confidential Rev. 0.2

Page 25

ARG Bit Name Function

AN332

4 7:0 RDSC

5 7:0 RDSC

6 7:0 RDSD

7 7:0 RDSD

[7:0]

H

[7:0]

L

[7:0]

H

[7:0]

L

RDS Block C High Byte.

This byte in combination with RDSC

RDS Block C Low Byte.

This byte in combination with RDSC

RDS Block D High Byte.

This byte in combination with RDSD

RDS Block D Low Byte.

This byte in combination with RDSD

sets the RDS block C data.

L

sets the RDS block C data.

H

sets the RDS block D data.

L

sets the RDS block D data.

H

Response

Bit D7 D6 D5 D4 D3 D2 D1 D0

STATUS

RESP1

RESP2

RESP3

RESP4

RESP5

CTS ERR X X X RDSINT ASQINT STCINT

X X X RDSPSXMIT CBUFXMIT FIFOXMIT CBUFWRAP FIFOMT

CBAVAIL[7:0]

CBUSED[7:0]

FIFOAVAIL[7:0]

FIFOUSED[7:0]

RESP Bit Name Function

1 7:5 Reserved Values may vary.

1 4 RDSPSXMIT Interrupt source: RDS PS Group has been transmitted.

1 3 CBUFXMIT Interrupt source: RDS Group has been transmitted from the FIFO buffer.

1 2 FIFOXMIT Interrupt source: RDS Group has been transmitted from the circular buffer.

1 1 CBUFWRAP Interrupt source: RDS Group Circular Buffer has wrapped.

1 0 FIFOMT Interrupt source: RDS Group FIFO Buffer is empty.

2 7:0 CBAVAIL[7:0] Returns the number of available Circular Buffer blocks.

3 7:0 CBUSED[7:0] Returns the number of used Circular Buffer blocks.

4 7:0 FIFOAVAIL[7:0] Returns the number of available FIFO blocks.

5 7:0 FIFOUSED[7:0] Returns the number of used FIFO blocks.

Confidential Rev. 0.2 25

Page 26

AN332

Command 0x36. TX_RDS_PS (Si4711/13/21 Only)

Loads or clears the program service buffer. The CTS bit (and optional interrupt) is set when it is safe to send the

next command. This command may only be sent when in powerup mode.

Note: TX_RDS_PS is supported in FMTX component 2.0 or higher.

Command arguments: Five

Response bytes: None

Command

Bit D7D6D5D4D3D2D1D0

CMD

ARG1

ARG2

ARG3

ARG4

ARG5

ARG Bit Name Function

1 7:5 Reserved Always write to 0.

1 4:0 PSID[4:0]

2 7:0 PSCHAR0[7:0]

3 7:0 PSCHAR1[7:0]

4 7:0 PSCHAR2[7:0]

5 7:0 PSCHAR3[7:0]

00110110

0 0 0 PSID[4:0]

PSCHAR0 [7:0]

PSCHAR1 [7:0]

PSCHAR2 [7:0]

PSCHAR3 [7:0]

Selects which PS data to load (0–23)

0 = First 4 characters of PS0.

1 = Last 4 characters of PS0.

2 = First 4 characters of PS1.

3 = Last 4 characters of PS1.

.

.

.

22 = First 4 characters of PS11.

23 = Last 4 characters of PS11.

RDS PSID CHAR0.

First character of selected PSID.

RDS PSID CHAR1.

Second character of selected PSID.

RDS PSID CHAR2.

Third character of selected PSID.

RDS PSID CHAR3.

Fourth character of selected PSID.

Response

Bit D7D6D5 D4 D3 D2 D1 D0

STATUS CTS ERR X X X RDSINT ASQINT STCINT

26 Confidential Rev. 0.2

Page 27

AN332

Command 0x80. GPIO_CTL

Enables output for GPO1, 2, and 3. GPO1, 2, and 3 can be configured for output (Hi-Z or active drive) by setting

the GPO1OEN, GPO2OEN, and GPO3OEN bit. The state (high or low) of GPO1, 2, and 3 is set with the

GPIO_SET command. To avoid excessive current consumption due to oscillation, GPO pins should not be left in a

high impedance state. The CTS bit (and optional interrupt) is set when it is safe to send the next command. This

command may only be sent when in powerup mode. The default is all GPO pins set for high impedance.

Notes:

1. GPIO_CTL is fully supported in FMTX component 3.0 or higher. Only bit GPO3OEN is supported in FMTX comp 2.0.

2. The use of GPO2 as an interrupt pin and/or the use of GPO3 as DCLK digital clock input will override this GPIO_CTL

function for GPO2 and/or GPO3 respectively.

Command arguments: One

Response bytes: None

Command

BitD7D6D5D4D3D2D1D0

CMD 10000000

ARG1 0 0 0 0 GPO3OEN GPO2OEN GPO1OEN 0

ARG Bit Name Function

1 7:4 Reserved Always write 0.

GPO3 Output Enable.

1 3 GPO3OEN

1 2 GPO2OEN

1 1 GPO1OEN

1 0 Reserved Always write 0.

Response

Bit D7D6D5 D4 D3 D2 D1 D0

STATUS CTS ERR X X X RDSINT ASQINT STCINT

0 = Output Disabled (Hi-Z) (default).

1 = Output Enabled.

GPO2 Output Enable.

0 = Output Disabled (Hi-Z) (default).

1 = Output Enabled.

GPO1 Output Enable.

0 = Output Disabled (Hi-Z) (default).

1 = Output Enabled.

Confidential Rev. 0.2 27

Page 28

AN332

Command 0x81. GPIO_SET

Sets the output level (high or low) for GPO1, 2, and 3. GPO1, 2, and 3 can be configured for output by setting the

GPO1OEN, GPO2OEN, and GPO3OEN bit in the GPIO_CTL command. To avoid excessive current consumption

due to oscillation, GPO pins should not be left in a high impedance state. The CTS bit (and optional interrupt) is set

when it is safe to send the next command. This property may only be set or read when in powerup mode. The

default is all GPO pins set for high impedance.

Note: GPIO_SET is fully-supported in FMTX comp 3.0 or higher. Only bit GPO3LEVEL is supported in FMTX comp 2.0.

Command arguments: One

Response bytes: None

Command

Bit D7 D6D5D4 D3 D2 D1 D0

CMD 10000001

ARG1 0 0 0 0 GPO3LEVEL GPO2LEVEL GPO1LEVEL 0

ARG Bit Name Function

1 7:4 Reserved Always write 0.

GPO3 Output Level.

1 3 GPO3LEVEL

0 = Output low (default).

1 = Output high.

GPO3 Output Level.

1 2 GPO2LEVEL

1 1 GPO1LEVEL

1 0 Reserved Always write 0.

Response

Bit D7D6D5 D4 D3 D2 D1 D0

STATUS CTS ERR X X X RDSINT ASQINT STCINT

0 = Output low (default).

1 = Output high.

GPO3 Output Level.

0 = Output low (default).

1 = Output high.

28 Confidential Rev. 0.2

Page 29

AN332

5.1.2. FM/RDS Transmitter Properties

Property 0x0001. GPO_IEN

Configures the sources for the GPO2/INT interrupt pin. Valid sources are the lower 8 bits of the STATUS byte,

including CTS, ERR, RDSINT, ASQINT, and STCINT bits. The corresponding bit is set before the interrupt occurs.

The CTS bit (and optional interrupt) is set when it is safe to send the next command. The CTS interrupt enable

(CTSIEN) can be set with this property and the POWER_UP command. The state of the CTSIEN bit set during the

POWER_UP command can be read by reading the this property and modified by writing this property. This

property may only be set or read when in powerup mode. The default is no interrupts enabled.

Default: 0x0000

D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

Bit

Name

Bit Name Function

15:11 Reserved Always write to 0.

10 RDSREP

9ASQREP

8 STCREP

7CTSIEN

6 ERRIEN

5:3 Reserved Always write to 0.

2 RDSIEN

1 ASQIEN

0STCIEN

00000

RDS Interrupt Repeat. (Si4711/13/21 Only)

0 = No interrupt generated when RDSINT is already set (default).

1 = Interrupt generated even if RDSINT is already set.

ASQ Interrupt Repeat.

0 = No interrupt generated when ASQREP is already set (default).

1 = Interrupt generated even if ASQREP is already set.

STC Interrupt Repeat.

0 = No interrupt generated when STCREP is already set (default).

1 = Interrupt generated even if STCREP is already set.

CTS Interrupt Enable.

0 = No interrupt generated when CTS is set (default).

1 = Interrupt generated when CTS is set.

After PowerUp, this bit will reflect the CTSIEN bit in ARG1 of PowerUp Command.

ERR Interrupt Enable.

0 = No interrupt generated when ERR is set (default).

1 = Interrupt generated when ERR is set.

RDS Interrupt Enable (Si4711/13/21 Only).

0 = No interrupt generated when RDSINT is set (default).

1 = Interrupt generated when RDSINT is set.

Audio Signal Quality Interrupt Enable.

0 = No interrupt generated when ASQINT is set (default).

1 = Interrupt generated when ASQINT is set.

Seek/Tune Complete Interrupt Enable.

0 = No interrupt generated when STCINT is set (default).

1 = Interrupt generated when STCINT is set.

RDSREP ASQREP STCREP CTSIEN ERRIEN

000

RDSIEN ASQIEN STCIEN

Confidential Rev. 0.2 29

Page 30

AN332

Property 0x0101. DIGITAL_INPUT_FORMAT

Configures the digital input format. The CTS bit (and optional interrupt) is set when it is safe to send the next

command. This property may only be set or read when in powerup mode.

Note: DIGITAL_INPUT_FORMAT is supported in FMTX component 2.0 or higher.

Default: 0x0000

Bit D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

Name 00000000IFALL IMODE[3:0] IMONOISIZE[1:0]

Bit Name Function

15:8 Reserved Always write to 0.

DCLK Falling Edge.

7IFALL

6:3 IMODE[3:0]

0 = Sample on DCLK rising edge (default).

1 = Sample on DCLK falling edge.

Digital Mode.

2

0000 = I

0110 = Left-justified mode.

1100 = MSB at 1

1000 = MSB at 2

S Mode (default).

st

DCLK rising edge after DFS Pulse.

nd

DCLK rising edge after DFS Pulse.

2IMONO

1:0 ISIZE[1:0]

Mono Audio Mode.

0 = Stereo audio mode (default).

1 = Mono audio mode.

Digital Audio Sample Precision.

00 = 16 bits (default)

01 = 20 bits

10 = 24 bits

11 = 8 bits

30 Confidential Rev. 0.2

Page 31

AN332

Property 0x0103. DIGITAL_INPUT_SAMPLE_RATE

Configures the digital input sample rate in 1 Hz units. The input sample rate must be set to 0 before removing the

DCLK input or reducing the DCLK frequency below 2 MHz. If this guideline is not followed, a device reset will be

required. The CTS bit (and optional interrupt) is set when it is safe to send the next command. This property may

only be set or read when in powerup mode.

Note: DIGITAL_INPUT_SAMPLE_RATE is supported in FMTX component 2.0 or higher.

Default: 0x0000

Units: 1 Hz

Step: 1 Hz

Range: 0, 32000-48000

BitD15D14D13D12D11D10D9D8D7D6D5D4D3D2D1D0

Name DISR[15:0]

Bit Name Function

Digital Input Sample Rate.

15:0 DISR

0 = Disabled. Required before removing DCLK or reducing DCLK frequency below

2 MHz. The range is 32000–48000 Hz.

Confidential Rev. 0.2 31

Page 32

AN332

Property 0x0201. REFCLK_FREQ

Sets the frequency of the REFCLK from the output of the prescaler. (Figure 1 shows the relation between RCLK

and REFCLK.) The REFCLK range is 31130 to 34406 Hz (32768 ±5% Hz) in 1 Hz steps, or 0 (to disable AFC). For

example, an RCLK of 13 MHz would require a prescaler value of 400 to divide it to 32500 Hz REFCLK. The

reference clock frequency property would then need to be set to 32500 Hz. RCLK frequencies between 31130 Hz

and 40 MHz are supported, however, there are gaps in frequency coverage for prescaler values ranging from 1 to

10, or frequencies up to 311300 Hz. Table 7 summarizes these RCLK gaps.

PIN 9

RCLK REFCLK

Prescaler

Divide by

31.130 kHz –

40 MHz

1-4095

Figure 1. REFCLK Prescaler

Table 7. RCLK Gaps

Prescaler RCLK Low (Hz) RCLK High (Hz)

1 31130 34406

2 62260 68812

3 93390 103218

4 124520 137624

5 155650 172030

6 186780 206436

7 217910 240842

8 249040 275248

9 280170 309654

31.130 kHz –

34.406 kHz

10 311300 344060

The RCLK must be valid 10 ns before and 10 ns after sending the TX_TUNE_MEASURE, TX_TUNE_FREQ, or

TX_TUNE_POWER commands. In addition, the RCLK must be valid at all times when the carrier is enabled for

proper AFC operation. The RCLK may be removed or reconfigured at other times. The CTS bit (and optional

interrupt) is set when it is safe to send the next command. This property may only be set or read when in powerup

mode. The default is 32768 Hz.

Default: 0x8000 (32768)

Units: 1 Hz

Step: 1 Hz

Range: 31130–34406

32 Confidential Rev. 0.2

Page 33

AN332

Bit D15D14D13D12D11D10D9D8D7D6D5D4D3D2D1D0

Name

Bit Name Function

Frequency of Reference Clock in Hz.

15:0 REFCLKF[15:0]

Property 0x0202. REFCLK_PRESCALE

Sets the number used by the prescaler to divide the external RCLK down to the internal REFCLK. The range may

be between 1 and 4095 in 1 unit steps. For example, an RCLK of 13 MHz would require a prescaler value of 400 to

divide it to 32500 Hz. The reference clock frequency property would then need to be set to 32500 Hz. The RCLK

must be valid 10 ns before and 10 ns after sending the TX_TUNE_MEASURE, TX_TUNE_FREQ, or

TX_TUNE_POWER commands. In addition, the RCLK must be valid at all times when the carrier is enabled for

proper AFC operation. The RCLK may be removed or reconfigured at other times. The CTS bit (and optional

interrupt) is set when it is safe to send the next command. This property may only be set or read when in powerup

mode. The default is 1.

Default: 0x0001

Step: 1

Range: 1–4095

The allowed REFCLK frequency range is between 31130 and 34406 Hz (32768

±5%), or 0 (to disable AFC).

REFCLKF[15:0]

BitD15D14D13D12D11D10D9D8D7D6D5D4D3D2D1D0

Name

Bit Name Function

15:12 Reserved Always write to 0.

11:0 R EFCLKP[ 11 : 0]

0000 RCLKP[11:0]

Prescaler for Reference Clock.

Integer number used to divide the RCLK frequency down to REFCLK frequency.

The allowed REFCLK frequency range is between 31130 and 34406 Hz (32768

±5%), or 0 (to disable AFC).

Confidential Rev. 0.2 33

Page 34

AN332

Property 0x2100. TX_COMPONENT_ENABLE

Individually enables the stereo pilot, left minus right stereo and RDS components. The CTS bit (and optional

interrupt) is set when it is safe to send the next command. This property may only be set or read when in powerup

mode. The default is stereo pilot and left minus right stereo components enabled.

Default: 0x0003

Bit D15D14D13D12D11D10D9D8D7D6D5D4D3D2D1 D0

Name

Bit Name Function

15:3 Reserved Always write 0.

2RDS

1LMR

0PILOT

Property 0x2101. TX_AUDIO_DEVIATION

Sets the transmit audio deviation from 0 to 90 kHz in 10 Hz units. The sum of the audio deviation, pilot deviation

and RDS deviation should not exceed regulatory requirements, typically 75 kHz. The CTS bit (and optional

interrupt) is set when it is safe to send the next command. This property may only be set or read when in powerup

mode. The default is 6825, or 68.25 kHz.

0000000000000RDSLMRPILOT

RDS Enable (Si4711/13/21 Only).

0 = Disables RDS (default).

1 = Enables RDS to be transmitted.

Left Minus Right.

0 = Disables Left Minus Right.

1 = Enables Left minus Right (Stereo) to be transmitted (default).

Pilot Tone.

0 = Disables Pilot.

1 = Enables the Pilot tone to be transmitted (default).

Default: 0x1AA9 (6825)

Units: 10 Hz

Step: 10 Hz

Range: 0–9000

Bit D15D14D13D12D11D10D9D8D7D6D5D4D3D2D1D0

Name

Bit Name Function

Transmit Audio Frequency Deviation.

15:0 TXADEV[15:0]

34 Confidential Rev. 0.2

Audio frequency deviation is programmable from 0 Hz to 90 kHz in 10 Hz units.

Default is 6825 (68.25 kHz). Note that the total deviation of the audio, pilot, and

RDS must be less than 75 kHz to meet regulatory requirements.

TXADEV[15:0]

Page 35

AN332

Property 0x2102. TX_PILOT_DEVIATION

Sets the transmit pilot deviation from 0 to 90 kHz in 10 Hz units. The sum of the audio deviation, pilot deviation and

RDS deviation should not exceed regulatory requirements, typically 75 kHz. The CTS bit (and optional interrupt) is

set when it is safe to send the next command. This property may only be set or read when in powerup mode. The

default is 675, or 6.75 kHz.

Default: 0x02A3 (675)

Units: 10 Hz

Step: 10 Hz

Range: 0–9000

Bit D15D14D13D12D11D10D9D8D7D6D5D4D3D2D1D0

Name

Bit Name Function

Transmit Pilot Frequency Deviation.

15:0 TXPDEV[15:0]

Property 0x2103. TX_RDS_DEVIATION (Si4711/13/21 Only)

Sets the RDS deviation from 0 to 7.5 kHz in 10 Hz units. The sum of the audio deviation, pilot deviation and RDS

deviation should not exceed regulatory requirements, typically 75 kHz. The CTS bit (and optional interrupt) is set

when it is safe to send the next command. This property may only be set or read when in powerup mode. The

default is 200, or 2 kHz.

Default: 0x00C8 (200)

Units: 10 Hz

Step: 10 Hz

Range: 0–9000

Pilot tone frequency deviation is programmable from 0 Hz to 90 kHz in 10 Hz units.

Default is 675 (6.75 kHz). Note that the total deviation of the audio, pilot, and RDS

must be less than 75 kHz to meet regulatory requirements.

TXPDEV[15:0]

Bit D15D14D13D12D11D10D9D8D7D6D5D4D3D2D1D0

Name

Bit Name Function

Transmit RDS Frequency Deviation.

15:0 TXRDEV[15:0]

RDS frequency deviation is programmable from 0 Hz to 90 kHz in 10 Hz units.

Default is 200 (2 kHz). Note that the total deviation of the audio, pilot, and RDS

must be less than 75 kHz to meet regulatory requirements.

Confidential Rev. 0.2 35

TXRDEV[15:0]

Page 36

AN332

Property 0x2104. TX_LINE_INPUT_LEVEL

Sets the input resistance and maximum audio input level for the LIN/RIN pins. An application providing a 150 mV

PK

input to the device on RIN/LIN would set Line Attenuation = 00, resulting in a maximum permissible input level of

190 mV

the TX audio deviation level set by the TX_AUDIO_DEVIATION property. An application providing a 1 V

the device on RIN/LIN would set Line Attenuation = 11, resulting in a maximum permissible input level of 636 mV

on LIN/RIN and an input resistance of 396 kΩ. The Line Level would be set to 150 mV to correspond to

PK

input to

PK

PK

on LIN/RIN and an input resistance of 60 kΩ. An external series resistor on LIN and RIN inputs of 40 kΩ would

create a resistive voltage divider that would keep the maximum line level on RIN/LIN below 636 mV

Level would be set to 636 mV

to correspond to the TX audio deviation level set by the TX_AUDIO_DEVIATION

PK

. The Line

PK

property. The CTS bit (and optional interrupt) is set when it is safe to send the next command. This property may

only be set or read when in powerup mode. The default input level and peak line level is 636 mV

impedance of 60 k

Ω.

with an input

PK

Default: 0x327C

Bit D15D14D13D12D11D10D9D8D7D6D5D4D3D2D1D0

Name

0 0 LIATTEN[1:0] 0 0 LILEVEL[9:0]

Bit Name Function

15:14 Reserved Always write to 0.

Line Attenuation.

00 = Max input level = 190 mVPK; input resistance = 396 kΩ

13:12 LIATTEN[1:0]

01 = Max input level = 301 mVPK; input resistance = 100 kΩ

10 = Max input level = 416 mVPK; input resistance = 74 kΩ

11 = Max input level = 636 mVPK; input resistance = 60 kΩ (default)

11:10 Reserved Always write to 0.

Line Level.

9:0 LILEVEL[9:0]

Maximum line amplitude level on the LIN/RIN pins in mVPK. The default is 0x27C or

636 mV

PK

.

36 Confidential Rev. 0.2

Page 37

AN332

Property 0x2105. TX_LINE_INPUT_MUTE

Selectively mutes the left and right audio inputs. The CTS bit (and optional interrupt) is set when it is safe to send

the next command. This property may only be set or read when in powerup mode.

Default: 0x0000

Bit D15D14D13D12D11D10D9D8D7D6D5D4D3D2 D1 D0

Name

Bit Name Function

15:2 Reserved Always write to 0.

1LIMUTE

0RIMUTE

Property 0x2106. TX_PREEMPHASIS

Sets the transmit pre-emphasis to 50 µs, 75 µs or off. The CTS bit (and optional interrupt) is set when it is safe to

send the next command. This property may only be set or read when in powerup mode. The default is 75 µs.

Default: 0x0000

Bit D15D14D13D12D11D10D9D8D7D6D5D4D3D2D1D0

Name

0 0 0 0 0 0 00000000LIMUTERIMUTE

Mutes L Line Input.

0 = No mute (default)

1=Mute

Mutes R Line Input.

0 = No mute (default)

1=Mute

00000000000000FMPE[1:0]

Bit Name Function

15:2 Reserved Always write to 0.

FM Pre-Emphasis.

00 = 75 µs. Used in USA (default)

1:0 FMPE[1:0]

01 = 50 µs. Used in Europe, Australia, Japan

10 = Disabled

11 = Reserve d

Confidential Rev. 0.2 37

Page 38

AN332

Property 0x2107. TX_PILOT_FREQUENCY

This property is used to set the frequency of the stereo pilot in 1 Hz steps. The stereo pilot is nominally set to

19 kHz for stereo operation, however the pilot can be set to any frequency from 0 Hz to 19 kHz to support the

generation of an audible test tone. The pilot tone is enabled by setting the PILOT bit (D0) of the

TX_COMPONENT_ENABLE property. When using the stereo pilot as an audible test generator it is recommended

that the RDS bit (D2) be disabled. The CTS bit (and optional interrupt) is set when it is safe to send the next

command. This property may only be set or read when in powerup mode.

Default: 0x4A38 (19000)

Units: 1 Hz

Step: 1 Hz

Range: 0–19000

Bit D15D14D13D12D11D10D9D8D7D6D5D4D3D2D1D0

Name

Bit Name Function

Stereo Pilot Frequency

15:0 FREQ

Property 0x2200. TX_ACOMP_ENABLE

Selectively enables the audio dynamic range control and limiter. The CTS bit (and optional interrupt) is set when it

is safe to send the next command. This property may only be set or read when in powerup mode. The default is

limiter enabled and audio dynamic range control disabled.

Note: LIMITEN bit is supported in FMTX component 2.0 or higher. Reset this bit to 0 in FMTX component 1.0.

Default: 0x0002

Bit D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

Name

00000000000000LIMITENACEN

Sets the frequency of the stereo pilot in 1 Hz steps.

Range 0 Hz–19000 Hz (default is 0x4A38 or 19 kHz).

FREQ[15:0]

Bit Name Function

15:2 Reserved Always write to 0.

Audio Limiter.

1 LIMITEN

0ACEN

38 Confidential Rev. 0.2

0=Disable

1 = Enable (default)

Transmit Audio Dynamic Range Control Enable.

0 = Audio dynamic range control disabled (default)

1 = Audio dynamic range control enabled

Page 39

AN332

Property 0x2201. TX_ACOMP_THRESHOLD

Sets the threshold for audio dynamic range control from 0 dBFS to –40 dBFS in 1 dB units in 2's complement

notation. For example, a setting of –40 dB would be 65536 – 40 = 65496 = 0xFFD8. The threshold is the level

below which the device applies the gain set by the TX_ACOMP_GAIN property, and above which the device

applies the compression defined by (gain + threshold) / threshold. The CTS bit (and optional interrupt) is set when

it is safe to send the next command. This property may only be set or read when in powerup mode. The default is

0xFFD8, or –40 dBFS.

Default: 0xFFD8 (–40)

Units: 1 dB

Step: 1 dB

Range: –40 to 0

Bit D15D14D13D12D11D10D9D8D7D6D5D4D3D2D1D0

Name

Bit Name Function

Transmit Audio Dynamic Range Control Threshold.

15:0 THRESHOLD[15:0]

Range is from –40 to 0 dBFS in 1 dB steps (0xFFD8–0x0).

Default is 0xFFD8 (–40 dBFS).

THRESHOLD[15:0]

Confidential Rev. 0.2 39

Page 40

AN332

Property 0x2202. TX_ACOMP_ATTACK_TIME

Sets the time required for the device to respond to audio level transitions from below the threshold in the gain

region to above the threshold in the compression region. The CTS bit (and optional interrupt) is set when it is safe

to send the next command. This property may only be set or read when in powerup mode. The default is 0.5 ms, or

0.

Default: 0x0000

Range: 0–9

Bit D15D14D13D12D11D10D9D8D7D6D5D4D3D2D1D0

Name

Bit Name Function

15:4 Reserved Always write to 0.

3:0 ATTACK[3:0]

000000000000 ATTACK[3:0]

Transmit Audio Dynamic Range Control Attack Time.

0 = 0.5 ms (default)

1 = 1.0 ms

2 = 1.5 ms

3 = 2.0 ms

4 = 2.5 ms

5 = 3.0 ms

6 = 3.5 ms

7 = 4.0 ms

8 = 4.5 ms

9 = 5.0 ms

40 Confidential Rev. 0.2

Page 41

AN332

Property 0x2203. TX_ACOMP_RELEASE_TIME

Sets the time required for the device to respond to audio level transitions from above the threshold in the

compression region to below the threshold in the gain region. The CTS bit (and optional interrupt) is set when it is

safe to send the next command. This property may only be set or read when in powerup mode. The default is

1000 ms, or 4.

Default: 0x0004

Range: 0–4

Bit D15D14D13D12D11D10D9D8D7D6D5D4D3D2D1D0

Name

Bit Name Function

15:3 Reserved Always write to 0.

2:0 RELEASE[2:0]

Property 0x2204. TX_ACOMP_GAIN

Sets the gain for audio dynamic range control from 0 to 20 dB in 1 dB units. For example, a setting of 15 dB would

be 15 = 0xF. The gain is applied to the audio below the threshold set by the TX_ACOMP_THRESHOLD property.

The CTS bit (and optional interrupt) is set when it is safe to send the next command. This property may only be set

or read when in powerup mode. The default is 15 dB or 0xF.

Default: 0x000F (15)

Units: 1 dB

0000000000000RELEASE[2:0]

Transmit Audio Dynamic Range Control Release Time.

0 = 100 ms

1 = 200 ms

2 = 350 ms

3 = 525 ms

4 = 1000 ms (default)

Step: 1 dB

Range: 0–20

Bit D15D14D13D12D11D10D9D8D7D6D5D4D3D2D1D0

Name

Bit Name Function

15:6 Reserved Always write to 0.

Transmit Audio Dynamic Range Control Gain.

5:0 GAIN[5:0]

Range is from 0 to 20 dB in 1 dB steps.

Default is 15.

Confidential Rev. 0.2 41

GAIN[5:0]

Page 42

AN332

Property 0x2205. TX_LIMITER_RELEASE_TIME

Sets the time required for the device to respond to audio level transitions from above the limiter threshold to below

the limiter threshold. The CTS bit (and optional interrupt) is set when it is safe to send the next command. This

property may only be set or read when in powerup mode. The default is 5.01 ms, or 102.

Note: TX_LIMITER_RELEASE_TIME is supported in FMTX component 2.0 or higher.

Default 0x0066 (102)

Step: 1

Range: 5–2000

Bit D15D14D13D12D11D10D9D8D7D6D5D4D3D2D1D0

Name

Bit Name Function

Sets the limiter release time.

5 = 102.39 ms

6 = 85.33 ms

7 = 73.14 ms

8 = 63.99 ms

10 = 51.19 ms

13 = 39.38 ms

17 = 30.11 ms

25 = 20.47 ms

51 = 10.03 ms

15:0 LMITERTC[15:0]

57 = 8.97 ms

64 = 7.99 ms

73 = 7.01 ms

85 = 6.02 ms

102 = 5.01 ms (default)

127 = 4.02 ms

170 = 3.00 ms

255 = 2.00 ms

510 = 1.00 ms

1000 = 0.50 ms

2000 = 0.25 ms

LIMITERTC[15:0]

42 Confidential Rev. 0.2

Page 43

AN332

Property 0x2300. TX_ASQ_INTERRUPT_SELECT

This property is used to enable which Audio Signal Quality (ASQ) measurements are returned by the

TX_ASQ_STATUS command. Overmodulation of the FM output signal due to excessive input signal level is

reported via the OVERMOD bit, which is enabled by setting the OVERMODIEN bit. A high or low input audio

condition is reported via the IALH and IALL bits which are enabled by the IALHIEN and IALLIEN bits. The CTS bit

(and optional interrupt) is set when it is safe to send the next command. This property may only be set or read

when in powerup mode.

Default: 0x0000

Bit D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

Name

Bit Name Function

15:3 Reserved Always write to 0.

0 0 0 0 0 0 0000000OVERMODIENIALHIENIALLIEN

Overmodulation Detection Enable.

2 OVERMODIEN

1 IALHIEN

0 IALLIEN

0 = OVERMOD detect disabled (default).

1 = OVERMOD detect enabled.

Input Audio Level Detection High Threshold Enable.

0 = IALH detect disabled (default).

1 = IALH detect enabled.

Input Audio Level Detection Low Threshold Enable.

0 = IALL detect disabled (default).

1 = IALL detect enabled.

Confidential Rev. 0.2 43

Page 44

AN332

Property 0x2301. TX_ASQ_LEVEL_LOW

This property sets the low audio level threshold relative to 0 dBFS in 1 dB increments, which is used to trigger the

IALL bit. This threshold can be set to detect a silence condition in the input audio allowing the host to take an

appropriate action such as disabling the RF carrier or powering down the chip. The CTS bit (and optional interrupt)

is set when it is safe to send the next command. This property may only be set or read when in powerup mode. The

default is 0x0000 and the range is 0 to –70.

Default: 0x0000

Units: 1 dB

Step: 1 dB

Range: –70 to 0

Bit D15 D14 D13D12 D11 D10D9D8D7D6D5D4D3D2D1D0

Name

Bit Name Function

15:8 Reserved Always write to 0.

7:0 IALLTH[7:0]

Property 0x2302. TX_ASQ_DURATION_LOW

This property is used to determine the duration (in 1 ms increments) that the input signal must be below the

TX_ASQ_LEVEL_LOW threshold in order for an IALL condition to be generated. The range is 0 ms to 65535 ms,

and the default is 0 ms. Note that the TX_ASQ_DURATION_LOW and TX_ASQ_DURATION_HIGH counters start

and the TX_ASQ_STATUS command will only return valid data after a call to TX_TUNE_FREQ,

TX_TUNE_POWER, or TX_TUNE_MEASURE. The CTS bit (and optional interrupt) is set when it is safe to send

the next command. This property may only be set or read when in powerup mode.

Default: 0x0000

Units: 1 ms

Step: 1 ms

00000000 IALLTH[7:0]

Input Audio Level Low Threshold

Threshold which input audio level must be below in order to detect a low audio condition.

Specified in units of dBFS in 1 dB steps (–70 .. 0). Default is 0.

Range: 0–65535

Bit D15 D14D13 D12 D11 D10D9D8D7D6D5D4D3D2D1D0

Name

Bit Name Function

Input Audio Level Duration Low.

15:0 IALLDUR[15:0]

44 Confidential Rev. 0.2

Required duration the input audio level must fall below IALLTH to trigger an IALL interrupt. Specified in 1mS increments (0–65535 ms). Default is 0.

IALLDUR[15:0]

Page 45

AN332

Property 0x2303. TX_ASQ_LEVEL_HIGH

This property sets the high audio level threshold relative to 0 dBFS in 1 dB increments, which is used to trigger the

IALH bit. This threshold can be set to detect an activity condition in the input audio allowing the host to take an

appropriate action such as enabling the RF carrier after an extended silent period. The CTS bit (and optional

interrupt) is set when it is safe to send the next command. This property may only be set or read when in powerup

mode. The default is 0x0000 and the range is 0 to –70.

Default: 0x0000