Page 1

AN0918.0: MCU Series 0 to EFM32JGxx/

PGxx Compatibility and Migration Guide

This porting guide is targeted at migrating an existing design from

MCU Series

0 to EFM32JGxx/PGxx or Wireless SoC Series 1.

Both hardware and software migration needs to be considered.

The core and peripherals of EFM32JGxx/PGxx or Wireless SoC Series 1 devices are

based on the existing MCU Series 0 with better performance and lower current consumption.

This document will describe which aspects are enhanced in the peripherals common

between MCU Series 0, EFM32JGxx/PGxx, and Wireless SoC Series 1. Details for all

of the new peripherals of EFM32JGxx/PGxx and Wireless SoC Series 1 can be found

in the reference manual, and it is recommended to review the available example code

for assistance and recommendations.

All peripherals in the MCU Series 0, EFM32JGxx/PGxx, and Wireless SoC Series 1

devices are described in general terms. Not all modules are present in all devices, and

the feature set for each device might vary. Such differences, including pinout, are covered in the device-specific data sheets.

KEY POINTS

• EFM32JGxx/PGxx and Wireless SoC

Series 1 have commonalities and

enhancements from

peripherals.

• Software and hardware migration must

both be considered when porting from an

MCU Series 0 device to EFM32JGxx/

PGxx or Wireless SoC Series 1 device.

• The EFM32JGxx/PGxx and Wireless SoC

Series 1 devices are software compatible

with the existing MCU Series 0 devices, so

only minor changes are required for

common peripherals.

• Refer to the example code for specific

recommendations and assistance.

MCU Series 0

silabs.com | Building a more connected world. Rev. 1.03

Page 2

AN0918.0: MCU Series 0 to EFM32JGxx/PGxx Compatibility and Migration Guide

1. Device Compatibility

This application note supports multiple device families, and some functionality is different depending on the device.

MCU Series 0 consists of:

• EFM32 Gecko (EFM32G)

• EFM32 Giant Gecko (EFM32GG)

• EFM32 Wonder Gecko (EFM32WG)

• EFM32 Leopard Gecko (EFM32LG)

• EFM32 Tiny Gecko (EFM32TG)

• EFM32 Zero Gecko (EFM32ZG)

• EFM32 Happy Gecko (EFM32HG)

Wireless MCU Series 0 consists of:

• EZR32 Wonder Gecko (EZR32WG)

• EZR32 Leopard Gecko (EZR32LG)

• EZR32 Happy Gecko (EZR32HG)

MCU Series 1 consists of:

• EFM32 Jade Gecko (EFM32JG1/EFM32JG12) (Collectively referred to in this document as EFM32JGxx)

• EFM32 Pearl Gecko (EFM32PG1/EFM32PG12) (Collectively referred to in this document as EFM32PGxx)

Device Compatibility

Wireless SoC Series 1 consists of:

• EFR32 Blue Gecko (EFR32BG1/EFR32BG12/EFR32BG13)

• EFR32 Flex Gecko (EFR32FG1/EFR32FG12/EFR32FG13)

• EFR32 Mighty Gecko (EFR32MG1/EFR32MG12/EFR32MG13)

silabs.com | Building a more connected world. Rev. 1.03 | 2

Page 3

AN0918.0: MCU Series 0 to EFM32JGxx/PGxx Compatibility and Migration Guide

Compatibility Overview

2. Compatibility Overview

Four factors must be considered when porting a design from MCU Series 0 to EFM32JGxx/PGxx or Wireless SoC Series 1: pin compatibility, hardware compatibility, software compatibility, and peripheral compatibility.

2.1 Pins and Hardware

EFM32JGxx/PGxx and Wireless SoC Series 1 devices are not footprint compatible with MCU Series 0 devices.

More information on footprint and hardware compatibility between MCU Series 0, EFM32JGxx/PGxx, and Wireless SoC Series 1 can

be found in 6. Hardware Migration.

2.2 Software and Peripherals

Software compatibility between MCU Series 0 is maintained using emlib and emdrv, which are software libraries built upon the CMSIS

(Cortex Microcontroller Software Interface Standard) layer defined by ARM. These devices are not binary compatible, meaning code

compiled for an MCU Series 0 should not work after being downloaded to an EFM32JGxx/PGxx. However, if the software is written

using the emlib or emdrv modules, then the application code should not need to change in most cases when recompiling for the new

EFM32JGxx/PGxx target.

Note: There are some small exceptions to full software compatibility across MCU Series 0 and EFM32JGxx/PGxx. For example, wakeup pins and GPIO drive strength are implemented slightly differently on these parts, so the emlib functions have changed slightly to

accommodate these differences. Wherever possible, these details have been abstracted away by the emlib and emdrv modules. See

5.1 Peripheral Support Library (emlib) and energyAware Drivers (emdrv) for more information on compatibility between MCU Series 0

and EFM32JGxx/PGxx. Consult the [Gecko SDK Suite] under [Documentation] in Simplicity Studio for more information on the emlib

and emdrv modules.

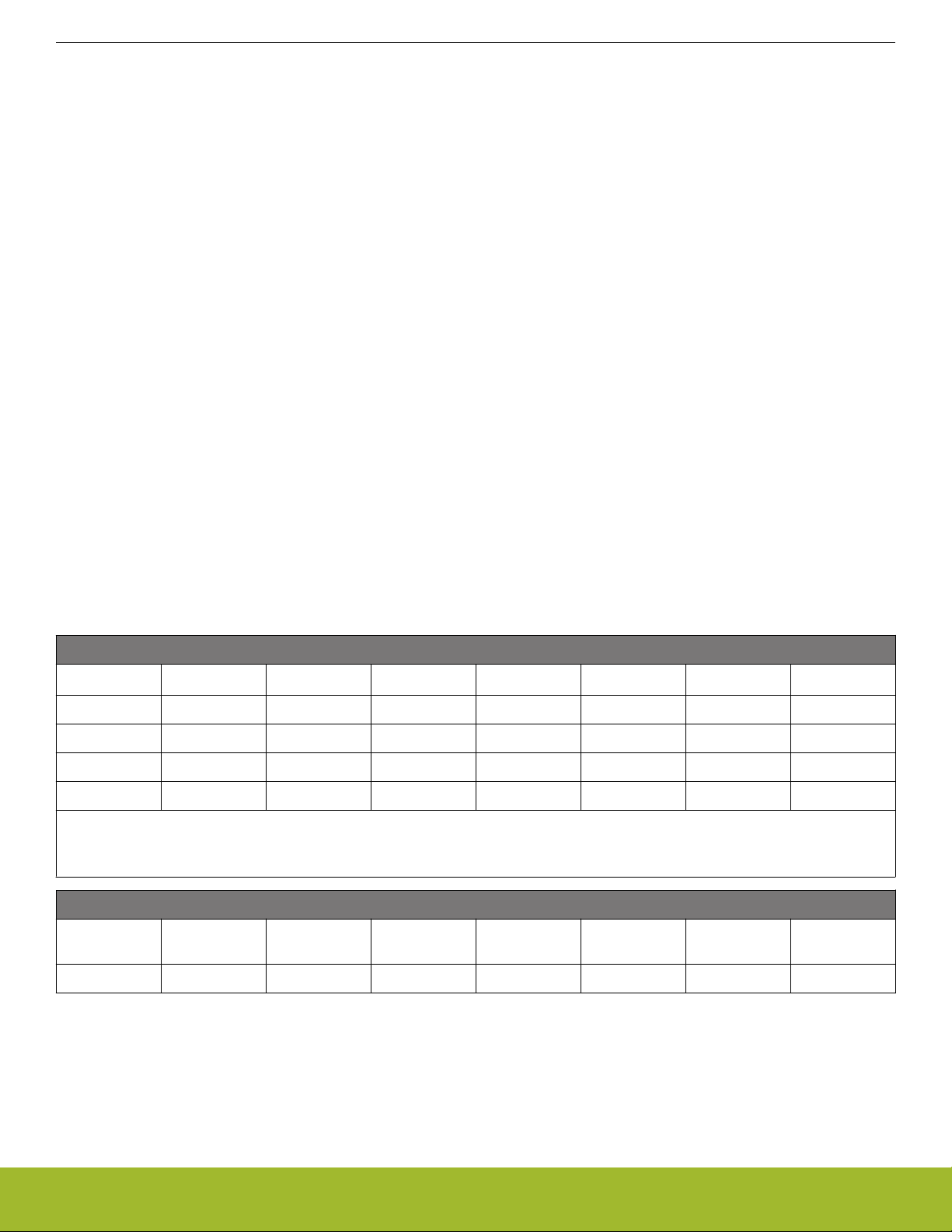

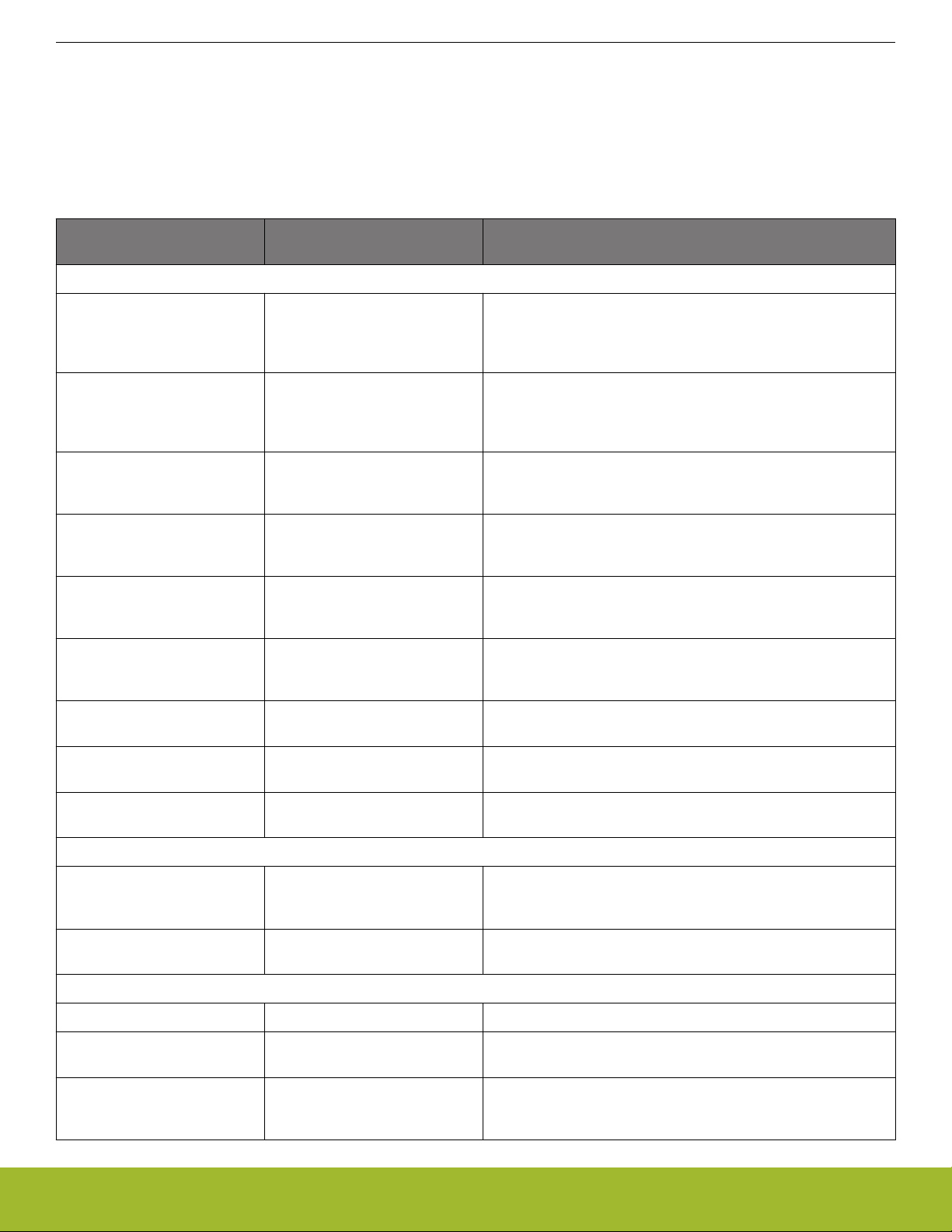

The emlib and emdrv modules provide abstraction layers that make peripheral initialization and usage simple and easy. Version 5.1.2

or above of the emlib and emdrv modules support the following peripherals across MCU Series 0 and EFM32JGxx/PGxx:

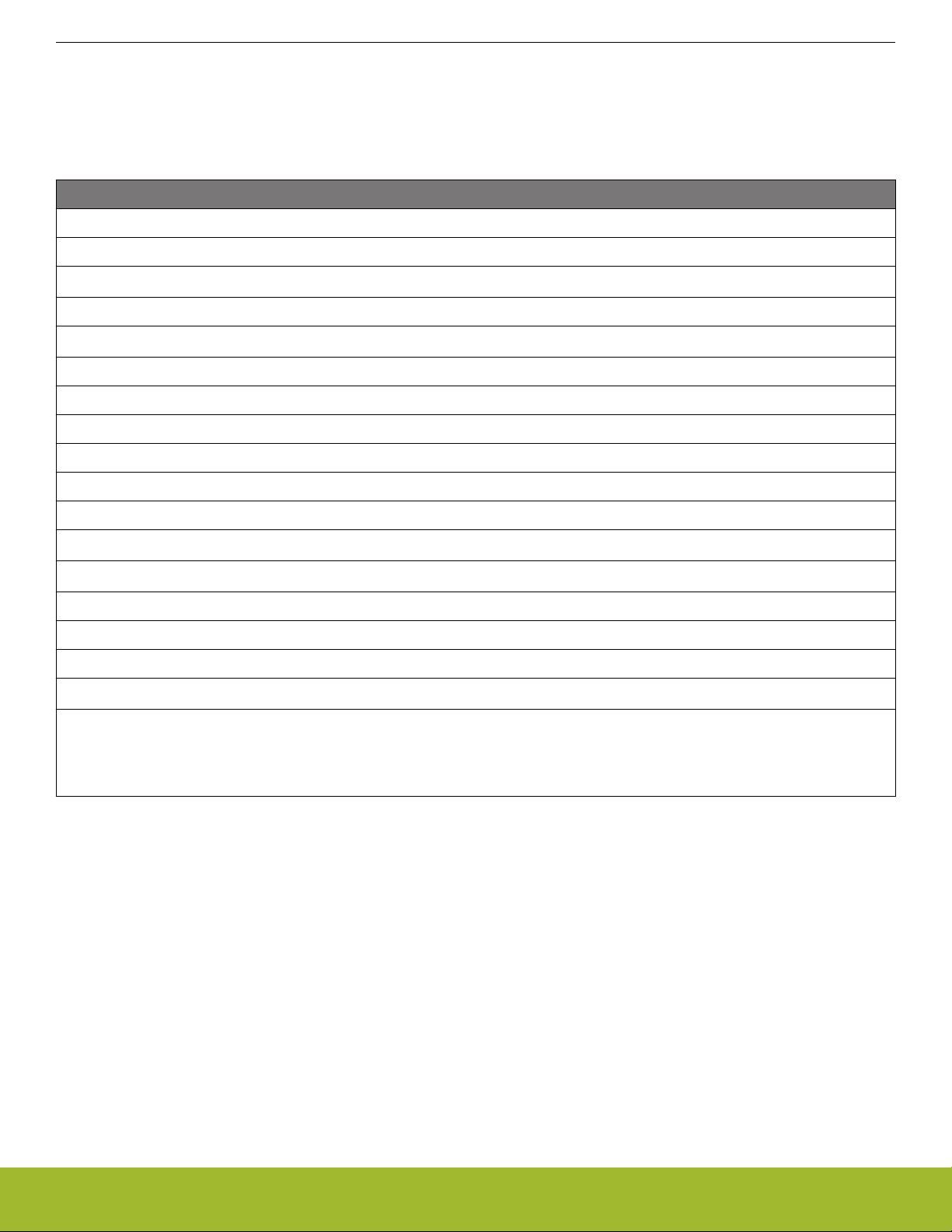

Table 2.1. The emlib and emdrv Support for MCU Series 0 and EFM32JGxx/PGxx

Peripherals Supported by emlib

ACMP ADC

AES

1

BURTC CMU CORE CRYOTIMER

CRYPTO

1

CSEN DAC DBG DMA EBI EMU GPCRC GPIO

I2C IDAC INT LCD LDMA LESENSE LETIMER LEUART

MPU MSC OPAMP PCNT PRS RMU RTC RTCC

SYSTEM TIMER USART VCMP VDAC WDOG — —

Note:

1.

For AES and CRYPTO, use the mbedTLS library.

The emdrv Modules

DMADRV EZRADIODRV GPIOINTERR-

NVM RTCDRV SLEEP SPIDRV TEMPDRV

PUT

UARTDRV USTIMER — — — — — —

silabs.com | Building a more connected world. Rev. 1.03 | 3

Page 4

AN0918.0: MCU Series 0 to EFM32JGxx/PGxx Compatibility and Migration Guide

Compatibility Overview

Since the emlib and emdrv modules are common across MCU Series 0 and EFM32JGxx/PGxx, the look and feel of the software development experience

struct software and use peripherals on the EFM32JGxx/PGxx products. In addition, existing MCU Series 0 designs can be quickly ported to new products to take advantage of new capabilities available on the EFM32JGxx/PGxx by utilizing the common code base between the families.

For systems that have software written without the use of emdrv, there are two methods to migrate a design from MCU Series 0 to

EFM32JGxx/PGxx:

1. Elevate the code to the level of emdrv to take advantage of the hardware abstraction provided by this layer.

2. Use the information in this document to migrate the code to the peripherals featured on the EFM32JGxx/PGxx products.

More information on software migration can be found in 5. Software Migration, and more information on the peripheral commonalities

and differences can be found in 4. Peripherals Common Between MCU Series 0, EFM32JGxx/PGxx, and Wireless SoC Series 1.

Wireless SoC Series 1 devices are configurable through the Silicon Labs software stacks, which are a layer on top of the emdrv modules. Systems migrating from MCU Series 0 to a Wireless SoC Series 1 platform should use the tools available in Simplicity Studio to

migrate their code.

is familiar. In other words, developers experienced with the MCU Series 0 products will already know how to con-

silabs.com | Building a more connected world. Rev. 1.03 | 4

Page 5

AN0918.0: MCU Series 0 to EFM32JGxx/PGxx Compatibility and Migration Guide

3. System Overview

3.1 Core and Memory

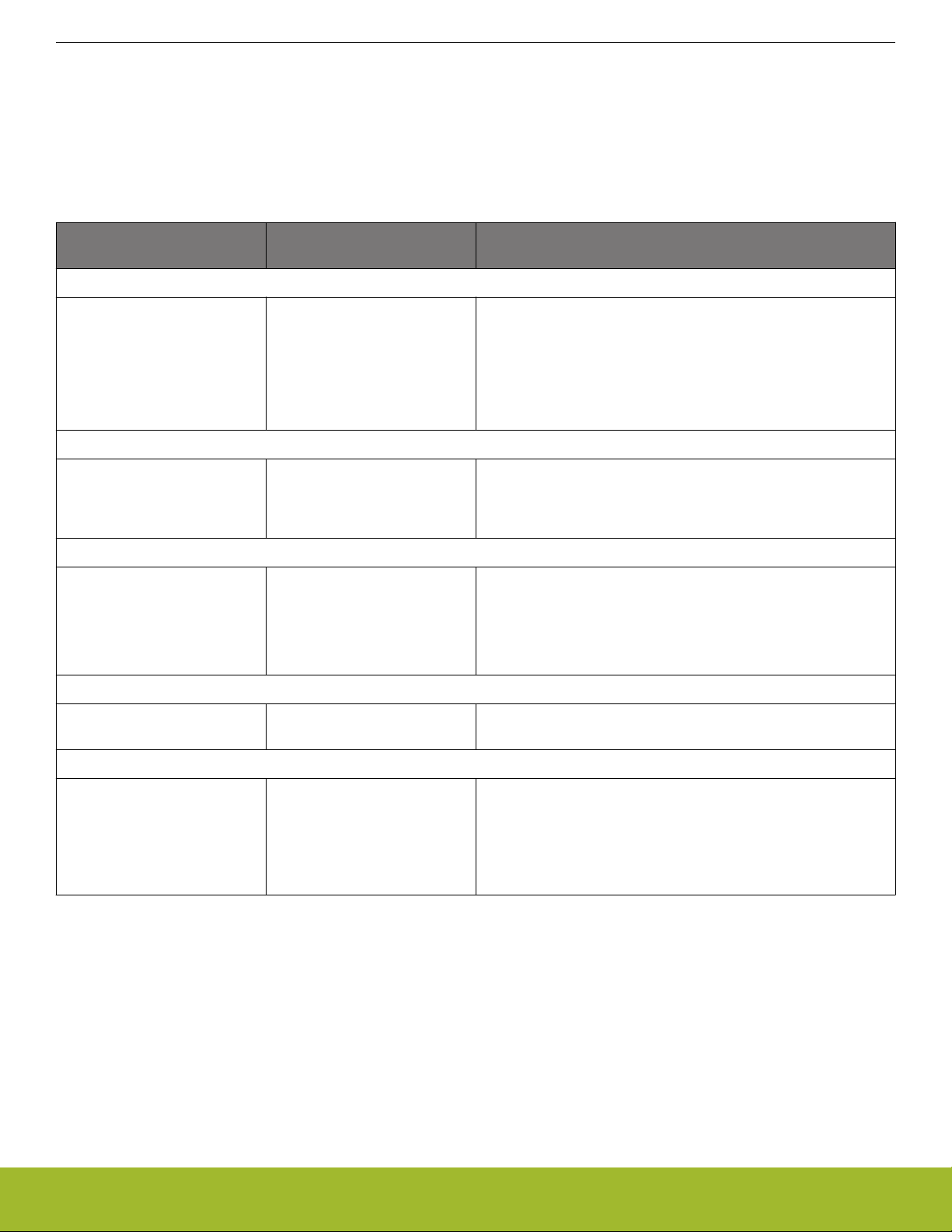

This section compares the core and memory of MCU Series 0 with EFM32JGxx/PGxx and Wireless SoC Series 1.

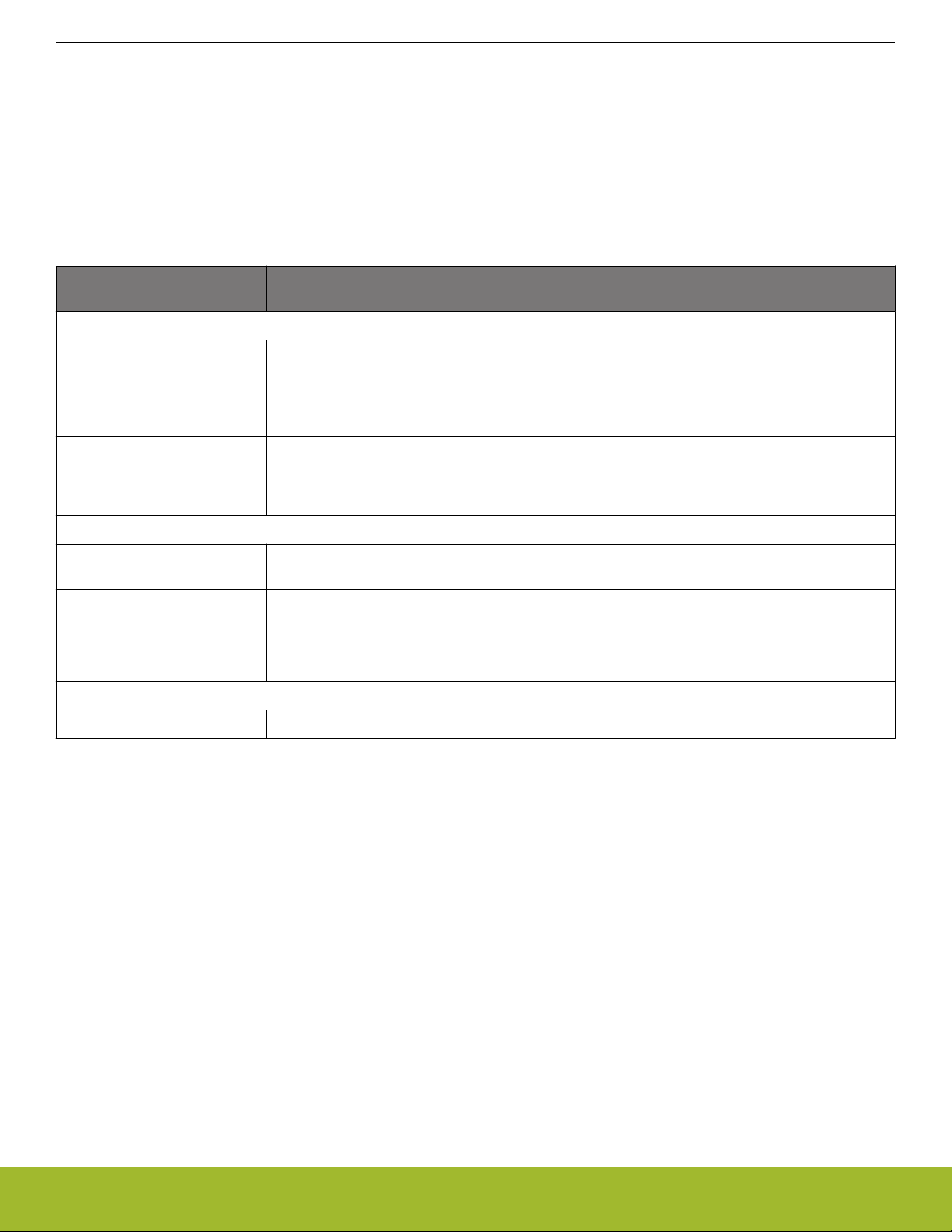

Table 3.1. Core and Memory

System Overview

MCU Series 0 EFM32JGxx/PGxx and Wire-

less SoC Series 1

Core

ARM Cortex M0+, M3 and M4

with FPU

Debug Interface

The 2-pin serial-wire debug

(SWD) interface.

DMA Controller (DMA)

ARM µDMA Controller Linked DMA Controller (LDMA) LDMA is completely a new design, it is more flexible and higher

EFM32JGxx:

ARM Cortex M3

EFM32PGxx and Wireless SoC

Series 1:

ARM Cortex M4 with FPU

The 2-pin serial-wire debug

(SWD) interface or a 4-pin Joint

Test Action Group (JTAG) interface.

Notes

—

Debug interface (SWD, JTAG, and ETM) for each device might

vary, such differences are covered in the device-specific data

sheets.

performance.

Number of DMA channels for each device might vary, such differences are covered in the device-specific data sheets. The dmadrv

module can also be used to assist with family differences.

Flash Program Memory

4 - 1024 KB 128 - 1024 KB Flash program memory for each device might vary, such differen-

ces are covered in the device-specific data sheets.

RAM Memory

2 - 128 KB EFM32JGxx/PGxx:

32 - 256 KB

Wireless SoC Series 1

16 - 256 KB

:

RAM memory for each device might vary, such differences are

covered in the device-specific data sheets.

silabs.com | Building a more connected world. Rev. 1.03 | 5

Page 6

3.2 Peripherals in MCU Series 0 only

AN0918.0: MCU Series 0 to EFM32JGxx/PGxx Compatibility and Migration Guide

System Overview

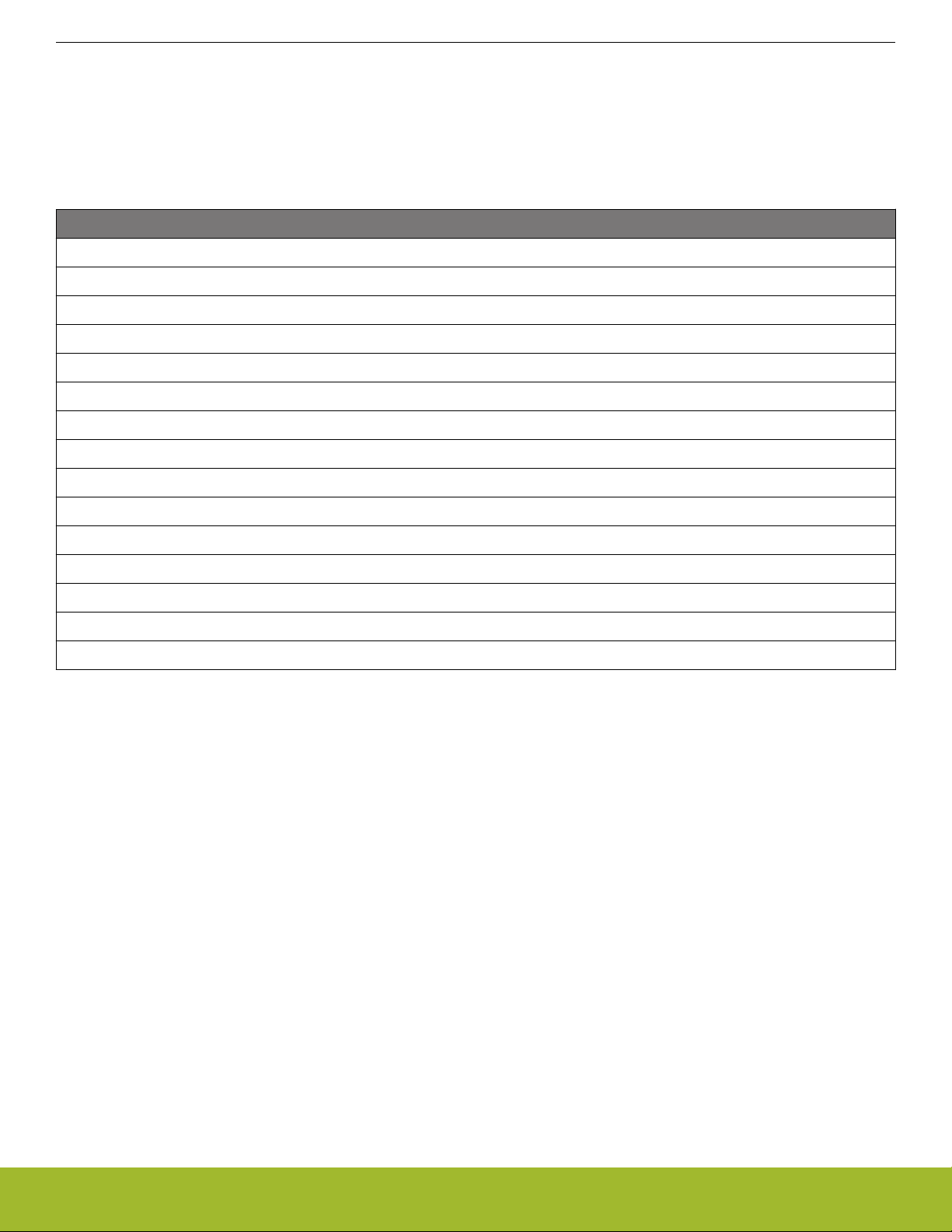

This section descibes the peripherals of MCU Series 0 that are not available in

EFM32JGxx/PGxx and Wireless SoC Series 1.

Refer to 5.1 Peripheral Support Library (emlib) and energyAware Drivers (emdrv) and 6.4 Peripherals Only on MCU Series 0 on how to

migrate these MCU Series 0 peripherals to EFM32JGxx/PGxx or Wireless SoC Series 1.

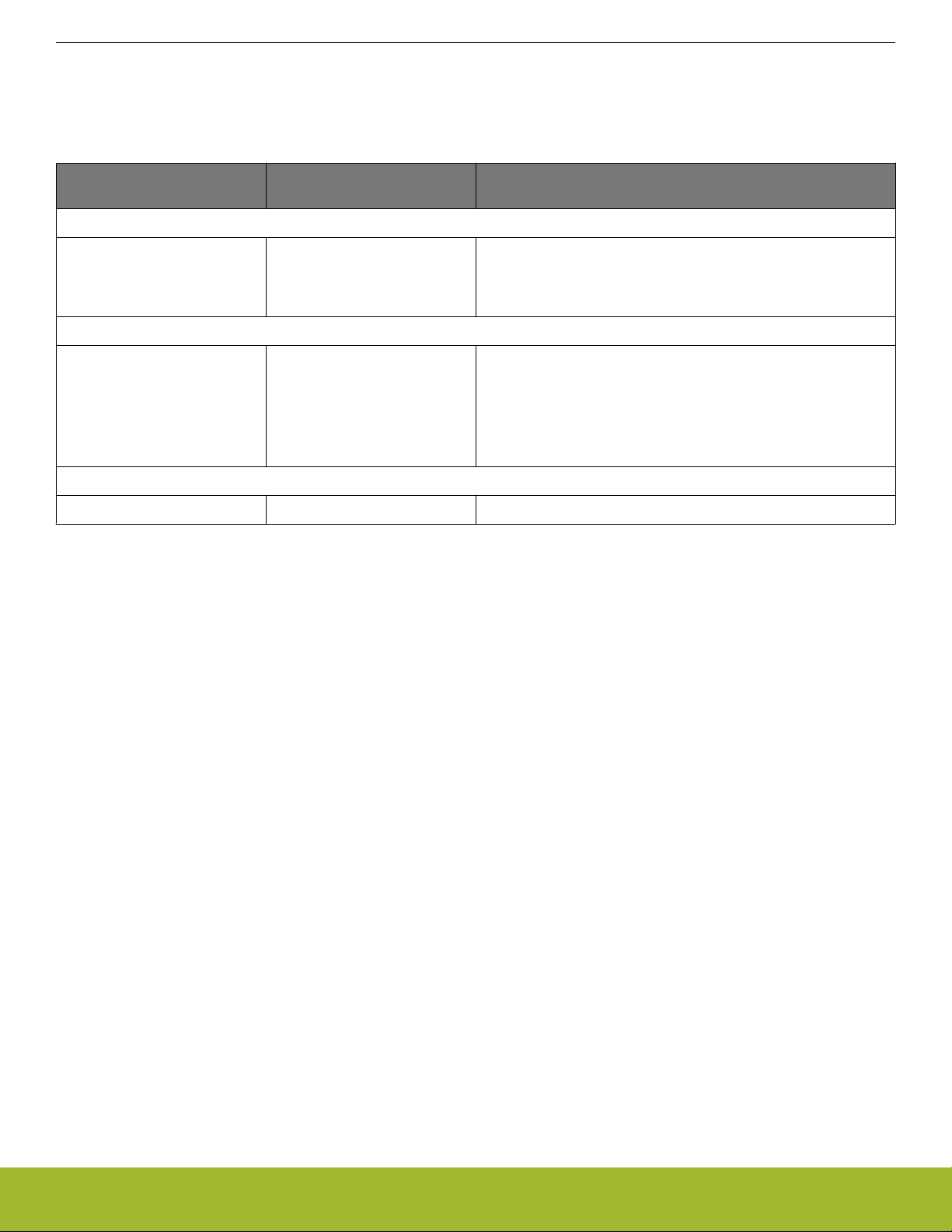

Table 3.2. Peripherals in MCU Series 0 only

MCU Series 0

Analog Interfaces

LCD Controller (LCD)

Energy Management

Voltage Comparator (VCMP)

Back-up Power Domain

I/O Ports

External Bus Interface (EBI)

Security

Advanced Encryption Standard Accelerator (AES)

Serial Interfaces

UART

USB

Timers and Triggers

Backup Real Time Counter (BURTC)

Real Time Counter (RTC)

silabs.com | Building a more connected world. Rev. 1.03 | 6

Page 7

AN0918.0: MCU Series 0 to EFM32JGxx/PGxx Compatibility and Migration Guide

3.3 New Peripherals in EFM32JGxx/PGxx and Wireless SoC Series 1

System Overview

This section

describes the new peripherals that are available in EFM32JGxx/PGxx and Wireless SoC Series 1. The RF portions of

Wireless SoC Series 1 are not included in this comparison.

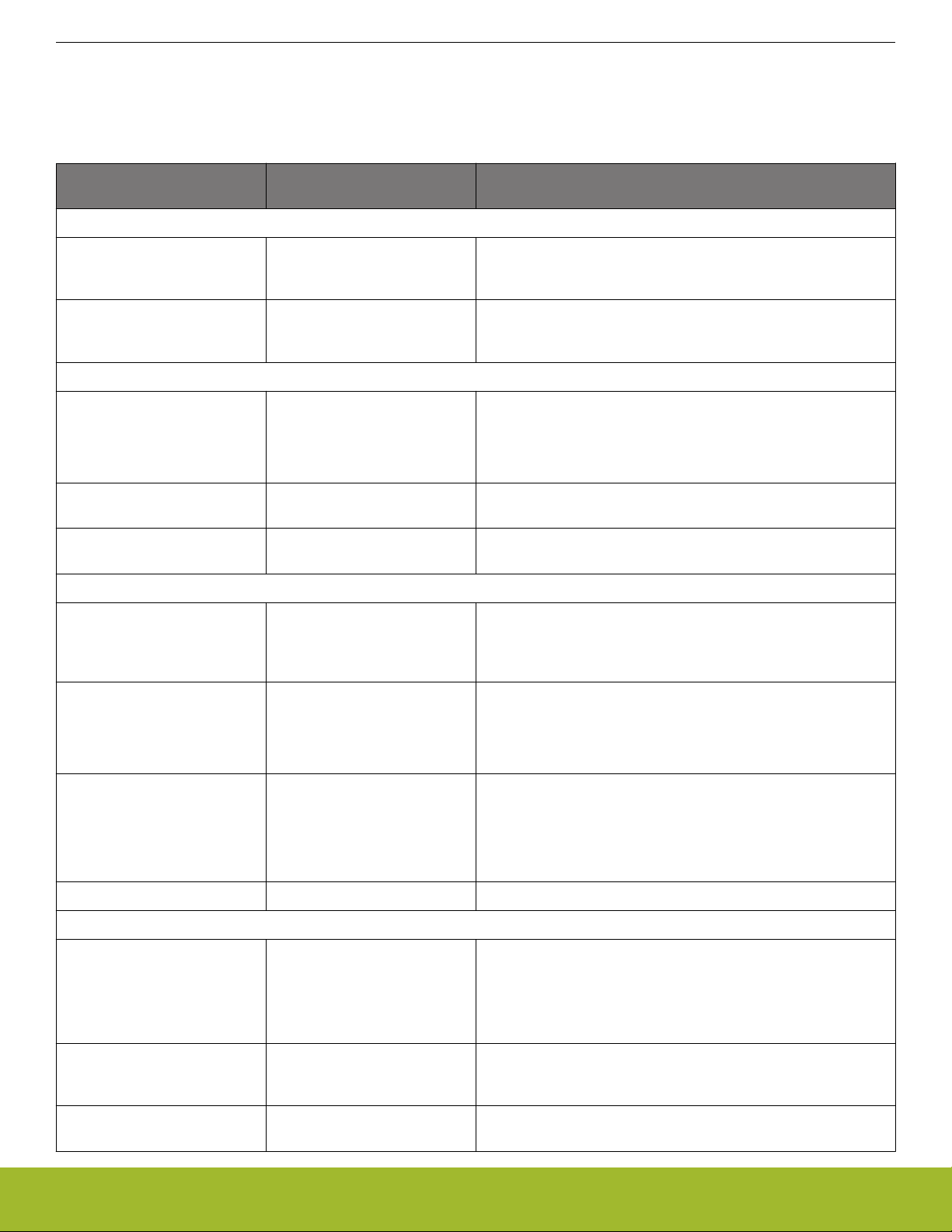

Table 3.3. New Peripherals in EFM32JGxx/PGxx and Wireless SoC Series 1

EFM32JGxx/PGxx and Wireless SoC Series 1

Analog Interfaces

Analog Port (APORT)

Capacitive Sense Module (CSEN)

1

Clock Management

High Frequency RC Oscillator (HFRCO) with Digital Phase-Locked Loop (DPLL)

Energy Management

DC-DC Converter

Voltage/Temp Monitor

Security

Crypto Accelerator (CRYPTO)

General Purpose Cyclic Redundancy Check (GPCRC)

Security Management Unit (SMU)

True Random Number Generator (TRNG)

1

1

2

Timers and Triggers

Ultra Low Energy Timer/Counter (CRYOTIMER)

Real Time Counter and Calendar (RTCC)

32 bit General Purpose Timer (WTIMER)

1

Note:

1.

Peripherals are only available on

EFM32JG1x/PG1x and EFR32xG12/xG13 devices.

2. Peripherals are only available on EFM32JG1x/PG1x devices.

silabs.com | Building a more connected world. Rev. 1.03 | 7

Page 8

AN0918.0: MCU Series 0 to EFM32JGxx/PGxx Compatibility and Migration Guide

Peripherals Common Between MCU Series 0, EFM32JGxx/PGxx, and Wireless SoC Series 1

4. Peripherals Common Between MCU Series 0, EFM32JGxx/PGxx, and Wireless SoC Series 1

4.1 Core and Memory

4.1.1 Debug (DBG)

The major changes are JTAG support and AAP lock.

Table 4.1. DBG

MCU Series 0 EFM32JGxx/PGxx and Wire-

less SoC Series 1

Enhancements

Hardware Debug support

through a 2-pin serial-wire debug (SWD) interface.

Debug Lock only. Debug Lock (DLW in lockbits

New Features

— The system bus can be stalled

— The CRCREQ command

Limitations

— — —

Hardware debug support

through a 2-pin serial-wire debug (SWD) interface or a 4-pin

Joint Test Action Group (JTAG)

interface.

page) and AAP Lock (ALW in

lockbits page).

by AAP_CTRL register.

(AAP_CRCCMD register) initiates a CRC calculation on a

given Flash Page.

Notes

The debug pins can be enabled and disabled through

GPIO_ROUTE_PEN.

If enabling the JTAG pins, the part must be power cycled to enable a SWD debug session.

The AAP_CMD register is locked by AAP Lock and this process is

irreversible. The user can no longer access the AAP_CMD register to issue a mass erase to the FLASH in order to gain entry to

the system via the debugger.

Use the SYSBUSSTALL bit in AAP_CTRL register.

The CRC is only available on the Main, User Data, and Lock Bit

pages.

It is highly recommended that the system bus is stalled before any

CRCREQ commands are issued.

silabs.com | Building a more connected world. Rev. 1.03 | 8

Page 9

AN0918.0: MCU Series 0 to EFM32JGxx/PGxx Compatibility and Migration Guide

Peripherals Common Between MCU Series 0, EFM32JGxx/PGxx, and Wireless SoC Series 1

4.1.2 Memory and Bus System

The major changes are the RAM segments and single-cycle bit access for peripherals.

Table 4.2. Memory and Bus System

MCU Series 0 EFM32JGxx/PGxx and Wire-

Notes

less SoC Series 1

Enhancements

Single RAM segment. The SRAM memory is split into

different AHB slaves, each having an individual bus connec-

This enables simultaneous access to different RAM segments,

e.g. if the core is accessing one RAM segment, the DMA can access another RAM segment without any bus contention.

tion.

New Features

— Peripheral Bit Set and Clear –

Dedicate inline function in em_bus.h.

single cycle bit set and clear to

peripherals' registers.

__STATIC_INLINE void BUS_RegBitWrite(volatile

uint32_t* const addr, uint32_t bit, uint32_t val)

Peripherals that do not support Bit Set and Bit Clear are EMU,

RMU, CRYOTIMER and TRNG0.

Limitations

— — —

silabs.com | Building a more connected world. Rev. 1.03 | 9

Page 10

AN0918.0: MCU Series 0 to EFM32JGxx/PGxx Compatibility and Migration Guide

Peripherals Common Between MCU Series 0, EFM32JGxx/PGxx, and Wireless SoC Series 1

4.1.3 Memory System Controller (MSC)

The major change is the addition of a dedicated page for the bootloader and AAP lock.

Table 4.3. MSC

MCU Series 0 EFM32JGxx/PGxx and Wire-

Notes

less SoC Series 1

Enhancements

Configure MSC_TIMEBASE

register for falsh erase and write

opeations.

Bus fault only on access to unmapped code and system

Timing configuration is not re-

—

quired for flash erase and write

operations.

Bus fault on different scenarios. The different bus fault responses are enabled by fields in

MSC_CTRL register.

space.

New Features on All EFM32JGxx/PGxx and Wireless SoC Series 1 Devices

Bootloader is placed on Main

Page.

Bootloader can be placed on

dedicated page at address

The system is configured to boot from bootloader at address

0x0FE10000 automatically after system reset.

0x0FE10000 (10 KB or 32 KB).

User can bypass the bootloader by clear bit 1 in Config Lock

Word 0 (CLW0) in word 122 of lockbit (LB) page.

— An additional atomic Read-clear

operation for IFC register.

— Authentication Access Port

It can be enabled by setting IFCREADCLEAR in the MSC_CTRL

register.

Word 124 of lockbit (LB) page is the AAP lock word (ALW).

(AAP) lock bits for AAP lock.

New Features Only on EFM32JG1x/PG1x and EFR32xG12/xG13 Devices

— The SWITCHINGBANK comm-

This command is only available on devices with dual-bank flash.

nad (MSC_CMD) initiates a

bank swithcing to swap between

two flash instances.

This feature can be disabled by Config Lock Word 1 (CLW1) in

word 123 of lockbit (LB) page.

— Low voltage flash read when

scaling down supply voltage to

reduce current consumption.

The system clock frequency and flash wait states should be pro-

grammed accordingly since it takes a longer time to read from

flash with a lower voltage supply.

Flash write/erase is not supported in low voltage mode.

— Bootloader software reads and

writes enable.

Reading and writing of bootloader area may be enabled with the

MSC_BOOTLOADERCTRL register.

The BOOTLOADERCTRL register is write-once, so after writing

the register, a reset of the system is required in order to change

permissions again.

— Advance cache control. Through MSC_CACHECONFIG0 and MSC_RAMCTRL registers.

Limitations

Flash wait states:

•

HFCLK > 16 MHz 1WS

•

HFCLK > 32 MHz 2WS

Flash wait states:

•

HFCLK > 26 MHz 1WS

Flash wait states (MODE field in MSC_READCTRL register) at

voltage scaling level 0 on EFM32JG1x/PG1x and EFR32xG12/

xG13 devices:

• 7 MHz < HFCLK <= 14 MHz 1WS

• 14 MHz < HFCLK <= 21 MHz 2WS

No Flash Startup time on transitions from EM2/3 to EM0

Flash Startup time on transitions

from EM2/3 to EM0 depends on

The related parameters are stored in MSC_STARTUP register.

the current operating conditions.

Minimum 20000 erase cycles

endurance.

Minimum 10000 erase cycles

endurance.

—

silabs.com | Building a more connected world. Rev. 1.03 | 10

Page 11

AN0918.0: MCU Series 0 to EFM32JGxx/PGxx Compatibility and Migration Guide

Peripherals Common Between MCU Series 0, EFM32JGxx/PGxx, and Wireless SoC Series 1

4.2 Clock Management

4.2.1 Clock Management Unit (CMU)

The major changes are the new HFXO automatic start features and Digital Phased-Locked Loop (DPLL).

Table 4.4. CMU

MCU Series 0 EFM32JGxx/PGxx and Wireless

Notes

SoC Series 1

Enhancements on All EFM32JGxx/PGxx and Wireless SoC Series 1 Devices

1.2 MHz – 28 MHz HFRCO

(1.2, 6.6, 11, 14, 21 and 28

MHz), HFRCO is 14 MHz after

reset.

1.2 MHz – 28 MHz AUXHFRCO

(1.2, 6.6, 11, 14, 21 and 28

MHz), AUXHFRCO is 14 MHz

after reset.

LFRCO and LFXO ready interrupt are available in EM0 - EM1

energy modes.

Startup time setup for LFXO

and HFXO.

1 MHz – 38 MHz HFRCO (1, 2, 4,

7, 13, 16, 19, 26, 32 and 38

MHz), HFRCO is 19 MHz after

reset.

1 MHz – 38 MHz AUXHFRCO (1,

2, 4, 7, 13, 16, 19, 26, 32 and 38

MHz), AUXHFRCO is 19 MHz after reset.

LFRCO and LFXO ready interrupt

are available in EM0 - EM2 energy modes.

Startup time setup for LFRCO,

LFXO, and HFXO.

Additional FINETUNING and FINETUNINGEN fields in

MSC_HFRCOCTRL register for HFRCO frequency tuning.

Additional FINETUNING and FINETUNINGEN fields in

MSC_AUXHFRCOCTRL register for AUXHFRCO frequency tuning.

The LFRCORDY and LFXORDY fields are in CMU_IEN register.

The HFXO has a second time-out counter which can be used to

achieve deterministic startup time based on timing from the

LFXO, ULFRCO, or LFRCO.

Only TUNING field in

CMU_LFRCOCTRL register.

More fields in

CMU_LFRCOCTRL register to

—

configure LFRCO.

— More settings for HFXO startup

with on-chip tunable capacitance.

Add CMU_HFXOCTRL, CMU_HFXOSTARTUPCTRL,

CMU_HFXOSTEADYSTATECTRL and CMU_HFXOTIMEOUTCTRL registers.

— More settings for LFXO startup

Add CMU_LFXOCTRL register.

with on-chip tunable capacitance.

— Clock output to PRS. Selected by a PRS consumer as CMUCLKOUT0 or CMUCLK-

OUT1.

— Calibration input from PRS. Selected by PRSUPSEL and PRSDOWNSEL fields in

CMU_CALCTRL register.

Enhancements Only on EFM32JG1x/PG1x and EFR32xG12/xG13 Devices

The Watchdog (WDOG) can be

clocked by LFRCO, LFXO, and

ULFRCO.

The SYSTICK can be clocked

by HFCORECLK.

The Watchdog (WDOG) can be

clocked by HFCORECLK,

LFRCO, LFXO, and ULFRCO.

The SYSTICK can be clocked by

HFCORECLK or LFBCLK.

—

The LFBCLK can be HFCLKLE, LFXO, LFRCO, or ULFRCO.

New Features on All EFM32JGxx/PGxx and Wireless SoC Series 1 Devices

— Add LFECLK for RTCC. LFECLK is available down to EM4H.

— Add HFEXPCLK for HFCLK out-

Prescaled version of HFCLK to CMU_OUT0 or CMU_OUT1.

put.

— Add HFBUSCLK without prescal-

er, separate it from HFCOR-

The LE, CRYPTOn, GPIO, PRS, LDMA and GPCRC are clocked

by HFBUSCLK if enable.

ECLK.

silabs.com | Building a more connected world. Rev. 1.03 | 11

Page 12

AN0918.0: MCU Series 0 to EFM32JGxx/PGxx Compatibility and Migration Guide

Peripherals Common Between MCU Series 0, EFM32JGxx/PGxx, and Wireless SoC Series 1

MCU Series 0 EFM32JGxx/PGxx and Wireless

Notes

SoC Series 1

— AUXHFRCO can clock ADC in

Selected by ADC0CLKSEL field in CMU_ADCCTRL register.

EM2/3.

— Automatic HFXO Start. The enabling of the HFXO and its selection as HFCLK source

can be performed automatically by hardware.

New Features Only on EFM32JG1x/PG1x and EFR32xG12/xG13 Devices

— New clock sources, HFRCODIV2

and CLKIN0, for HFCLK.

— The Digital Phase-Locked Loop

The HFROCDIV2 is HFRCO divided by 2 and CLKIN0 is the external clock source from the dedicate CLKIN0 pin.

The reference clock source can be HFXO, LFXO, or CLKIN0.

(DPLL) generates a digitally controlled oscillator (DCO), which is

HFRCO, as a ratio of a reference

The DPLL is disabled automatically when entering EM2, EM3,

EM4H or EM4S.

clock source.

Limitations

HFXO range is 4 – 48 MHz. HFXO range is 38 – 40 MHz. —

HFCORECLKLE > 24 or 32

MHz

•

Set HFLE if available

Set HFCORECLKLEDIV to

•

HFBUSCLKLE > 32 MHz

• Set WSHFLE

• Set HFCLKLEPRESC to DIV4

The WSHFLE is in CMU_CTRL register and HFCLKLEPRESC is

in CMU_HFPRESC register.

DIV4

HFXTAL_P and HFXTAL_N

pins can use as GPIO.

HFXTAL_P and HFXTAL_N pins

cannot use as GPIO.

— LFACLK cannot select

HFBUSCLKLE as clock source.

—

The LESENSE and LETIMER are clocked by LFACLK.

silabs.com | Building a more connected world. Rev. 1.03 | 12

Page 13

AN0918.0: MCU Series 0 to EFM32JGxx/PGxx Compatibility and Migration Guide

Peripherals Common Between MCU Series 0, EFM32JGxx/PGxx, and Wireless SoC Series 1

4.3 Energy Management

4.3.1 Energy Management Unit (EMU)

The major changes are new EM4 energy modes (EM4H and EM4S) and the new DC-DC converter module.

Table 4.5. EMU

MCU Series 0 EFM32JGxx/PGxx and Wireless

Notes

SoC Series 1

Enhancements on All EFM32JGxx/PGxx and Wireless SoC Series 1 Devices

No way to know the system

wakes up from EM2 and EM3.

Single EM4 energy mode. EM4 splits in EM4H (Hibernate)

Interrupt to indicate system

wakes up from EM2 and EM3.

and EM4S (Shutoff) energy

EM23WAKEUP in EMU_IF register will be set when the system

wakes from EM2 and EM3.

Set EM4STATE in EMU_EM4CTRL register to enter EM4H

when entering EM4.

modes.

In EM4H, the regulator will be on in reduced mode allowing for

RTCC. Otherwise, when entering in EM4, the regulator will be

disabled allowing for lowest power mode, Shutoff state (EM4S).

When RAM block is powered

down, it cannot be powered up

again without reset.

Selected RAM block is powered

down in EM2/3 with full access in

EM0.

The RAM block 0 (128 kB) will always be powered on for proper

system functionality.

The stack must be located in retained memory.

Enhancements Only on EFM32JG1x/PG1x and EFR32xG12/xG13 Devices

The Brown-Out Detector (BOD)

cannot be disabled.

The Brown-Out Detector (BOD)

can be disabled in EM2 to mini-

Set EM2BODDIS in EMU_CTRL register to disable BOD when

entering EM2.

mize current.

New Features on All EFM32JGxx/PGxx and Wireless SoC Series 1 Devices

No DC-DC converter module. With a DC-DC converter module

to power internal circuits and it

requires an external inductor and

The DC-DC converter allows up to two external hookup configu-

rations with additional options giving flexible power architecture

selection.

capacitor.

Use Voltage Supply Comparator (VCMP) to monitor the sup-

Use Voltage Monitor (VMON) to

monitor different voltage sources.

Trigger points for interrupts are preloaded but may be reconfig-

ured.

ply voltage.

ADC temperature sensor only. EMU temperature sensor is al-

ways running (except in EM4

Temperature measurement is taken every 250ms with the 8-bit

result stored in EMU_TEMP register.

Shutoff) and is independent from

ADC temperature sensor.

The high and low temperature trigger points for interrupt are con-

figurable.

New Features Only on EFM32JG1x/PG1x and EFR32xG12/xG13 Devices

— Prevent DVDD BOD from caus-

ing a reset.

— Separate voltage scaling controls

are available for the different energy modes.

•

EM01 Voltage Scaling

• EM23 Voltage Scaling

Set DVDDBODDIS in EMU_PWRCTRL register to enable this

feature.

Voltage scaling allows for a tradeoff between power and per-

formance, the user can scale voltages between Voltage Scale

Level 2 (1.2 V) and Voltage Scale Level 0 (1.0 V).

The software should follow certain sequences for supply voltage

scaling up and down.

• EM4H Voltage Scaling

— Peripherals that are available in

EM2 Deep Sleep or EM3 Stop

The EMU_EM23PERNORETAINCTRL register can be used to

setup unused peripherals for powering down prior to EM23 entry.

can optionally be powered down

during EM2 or EM3.

silabs.com | Building a more connected world. Rev. 1.03 | 13

Page 14

AN0918.0: MCU Series 0 to EFM32JGxx/PGxx Compatibility and Migration Guide

Peripherals Common Between MCU Series 0, EFM32JGxx/PGxx, and Wireless SoC Series 1

MCU Series 0 EFM32JGxx/PGxx and Wireless

Notes

SoC Series 1

Limitations

— — —

4.3.2 Reset Management Unit (RMU)

The major change is configurable reset levels for Watchdog, Lockup, Pin, and System reset requests.

Table 4.6. RMU

MCU Series 0 EFM32JGxx/PGxx and Wire-

Notes

less SoC Series 1

Enhancements

RESETn pin reset can only be

hard reset.

RESETn pin reset can be configured to be either hard or soft

The soft reset can be configured to be either DISABLED, LIMITED, EXTENDED or FULL.

reset.

Hard resets will reset the entire chip (= soft reset configured as

FULL).

To configure RESETn pin reset as a hard reset, clear the PINRESETSOFT bit in CLW0 in the Lock bit page.

New Features

Watchdog, Lockup, Pin and

System reset request are non

configurable.

Limitations

Brown-out Detection (BOD) on

Regulated domain, Unregulated

domain, Analog Power Domain

0 (AVDD0) and Analog Power

Domain 1 (AVDD1).

Watchdog, Lockup, Pin (RESETn) and System reset request are sources for soft reset.

Brown-out Detection (BOD) on

Analog Unregulated Power Domain (AVDD), Digital Unregulated Power Domain (DVDD) and

Regulated Digital Domain (DECOUPLE).

The reset level (DISABLED, LIMITED, EXTENDED or FULL) for

soft reset sources is configured in the xxxRMODE bitfields in

RMU_CTRL register.

—

silabs.com | Building a more connected world. Rev. 1.03 | 14

Page 15

Peripherals Common Between MCU Series 0, EFM32JGxx/PGxx, and Wireless SoC Series 1

4.4 Serial Interfaces

4.4.1 Inter-Integrated Circuit Interface (I2C)

There are no major changes for the I2C module.

AN0918.0: MCU Series 0 to EFM32JGxx/PGxx Compatibility and Migration Guide

Table 4.7. I2C

MCU Series 0 EFM32JGxx/PGxx and Wire-

Notes

less SoC Series 1

Enhancements

Separate single buffer for transmit and receive.

Separate 2-level FIFO for transmit and receive.

Access through I2Cn_TXDOUBLE and I2Cn_RXDOUBLE registers.

New Features

— — —

Limitations

— — —

4.4.2 Low Energy Universal Asynchronous Receiver/Transmitter (LEUART)

There are no major changes for the LEUART module.

Table 4.8. LEUART

MCU Series 0 EFM32JGxx/PGxx and Wire-

Notes

less SoC Series 1

Enhancements

— — —

New Features

— — —

Limitations

— — —

silabs.com | Building a more connected world. Rev. 1.03 | 15

Page 16

AN0918.0: MCU Series 0 to EFM32JGxx/PGxx Compatibility and Migration Guide

Peripherals Common Between MCU Series 0, EFM32JGxx/PGxx, and Wireless SoC Series 1

4.4.3 Universal Synchronous Asynchronous Receiver/Transmitter (USART)

The major changes are hardware flow control and the addition of a 8-bit timer.

Table 4.9. USART

MCU Series 0 EFM32JGxx/PGxx and Wire-

Notes

less SoC Series 1

Enhancements

The baud rate divider is 13-bit

integral part and a 2-bit fractional part.

Extend baud rate divider to 20bit value, with a 15-bit integral

part and a 5-bit fractional part.

Better accuracy on baud rate generation.

PRS RX input only. PRS RX and PRS CLK inputs. The USART can be configured to receive data and clock directly

from PRS channels.

The PRS channels are selected by RXPRSSEL and CLKPRSSEL

in USARTn_INPUT register.

New Features

— Automatic Baud Rate Detection. Setting AUTOBAUDEN in USARTn_CLKDIV register uses the

first frame received to automatically set the baud rate provided

that it contains 0x55 (IrDA uses 0x00).

— Hardware Flow Control with de-

This function is configured by USARTn_CTRLX register.

bug halt.

— New 8-bit Timer to create timing

for a variety of uses.

It can be used for different purposes such as RX timeout, break

detection, response timeout, and RX enable delay.

Limitations

— — —

silabs.com | Building a more connected world. Rev. 1.03 | 16

Page 17

AN0918.0: MCU Series 0 to EFM32JGxx/PGxx Compatibility and Migration Guide

Peripherals Common Between MCU Series 0, EFM32JGxx/PGxx, and Wireless SoC Series 1

4.5 I/O Ports

4.5.1 General Purpose Input/Output (GPIO)

The major change is the addition of configurable over voltage tolerance inputs.

Table 4.10. GPIO

MCU Series 0 EFM32JGxx/PGxx and Wire-

Notes

less SoC Series 1

Enhancements

Use DOUTSET and DOUTCLR

registers to set and clear GPIO

Remove DOUTSET &

DOUTCLR registers.

Use Peripheral Bit Set and Clear to set and clear GPIO pins.

pins.

New Features

— Input disable. The pin inputs can be disabled on a port-by-port basis. The input

of pins configured using the normal or alternate MODEn settings

can be disabled by setting DINDIS or DINDISALT in

GPIO_Px_CTRL register.

— Slewrate setting. The slewrate can be applied to pins on a port-by-port basis. The

actual slewrate applied to the selected pins is configured in the

SLEWRATE and SLEWRATEALT fields in GPIO_Px_CTRL register.

— Over voltage tolerance is availa-

ble for most pins.

The over voltage tolerance applied to the selected pins is configured in the GPIO_Px_OVTDIS register (Default over voltage is

enabled for each pin supporting that feature).

Disabling the over voltage tolerance for a pin will provide less distortion on that pin, which is useful when the pin is used as analog

input.

— Level interrupt for EM4 wakeup. GPIO can generate a level interrupt using the input of any EM4

wake-up pin on the device.

Limitations

Drive strength – 0.1, 1, 6 and 20

mA.

All pins with the same pin number (n) are grouped together to

trigger one interrupt flag or to

form one PRS producer output.

Drive strength – 1 mA and 10

mA.

All pins within a group of four

(0-3, 4-7, 8-11, 12-15) from all

ports are grouped together to

trigger one interrupt flag index

or to form one PRS producer

output.

—

It is more flexible to configure GPIO interrupt source or PRS producer output while maintaining compatibility with

MCU Series 0

Add GPIO_EXTIPINSELL and GPIO_EXTIPINSELH registers.

.

silabs.com | Building a more connected world. Rev. 1.03 | 17

Page 18

AN0918.0: MCU Series 0 to EFM32JGxx/PGxx Compatibility and Migration Guide

Peripherals Common Between MCU Series 0, EFM32JGxx/PGxx, and Wireless SoC Series 1

4.6 Timers and Triggers

4.6.1 Timer/Counter (TIMER)

The major change is dedicate TIMER now has 4 compare/capture channels, can be used for RGBW LED control.

Table 4.11. TIMER

MCU Series 0 EFM32JGxx/PGxx and Wire-

Notes

less SoC Series 1

Enhancements

3 Compare/Capture channels. 3 or 4 Compare/Capture chan-

nels.

The 4 Compare/Capture channels are only available on TIMER1

and WTIMER1.

New Features Only on EFM32JG1x/PG1x and EFR32xG12/xG13 Devices

— The new 32 bit general purpose

timer WTIMER.

The TIMER and WTIMER peripherals are identical except for the

timer width.

Limitations

— — —

4.6.2 Low Energy Timer (LETIMER)

The major change is to replace RTC trigger with PRS.

Table 4.12. LETIMER

MCU Series 0 EFM32JGxx/PGxx and Wire-

Notes

less SoC Series 1

Enhancements

— — —

New Features

LETIMER can be started by a

RTC event or started, stopped,

and cleared by software.

LETIMER can be started, stopped, and cleared by PRS or

software.

The PRS mode and input are configured by LETIMERn_PRSSEL

register.

Limitations

— — —

silabs.com | Building a more connected world. Rev. 1.03 | 18

Page 19

Peripherals Common Between MCU Series 0, EFM32JGxx/PGxx, and Wireless SoC Series 1

4.6.3 Peripheral Reflex System (PRS)

The major change is that PRS can trigger the core and DMA.

AN0918.0: MCU Series 0 to EFM32JGxx/PGxx Compatibility and Migration Guide

Table 4.13. PRS

MCU Series 0 EFM32JGxx/PGxx and Wire-

Notes

less SoC Series 1

Enhancements

— Optional channel output invert. Set INV bit in PRS_CHx_CTRL register to invert channel output.

— Pulse stretch for domains run-

ning at different frequency.

Set STRETCH bit in PRS_CHx_CTRL register to stretch channel

output.

Stretches channel output to ensure that the target clock domain

detects it.

— Read back PRS channel value. Access through PRS_PEEK register.

PRS channels 0-3 can output to

GPIO with one common location

field.

All PRS channels can output to

GPIO with independent location

field.

This function is configured by PRS_ROUTELOCn registers.

New Features

— PRS channel can use as PRS

source.

— The PRS can be used to send

events to the core.

Use PRSL or PRSH of SOURCESEL field in PRS_CHx_CTRL

register to select PRS channel as PRS input source.

This is very useful in combination with the Wait For Event (WFE)

instruction.

This function is configured by PRS_CTRL register.

— Up to two independent DMA re-

quests can be generated by the

This function is configured by PRS_DMAREQ0 and PRS_DMAREQ1 registers

PRS.

The PRS signals triggering the DMA requests are selected with

the SOURCESEL (= 0x1 for PRS) and SIGNAL (= 0x0 for

PRSREQ0 or = 0x1 for PRSREQ1) fields in the LDMA_CHx_REQSEL register.

— Configurable PRS Logic (AND

and OR).

Each PRS channel has three logic functions that can be used by

themselves or in combination.

The selected PRS source can be AND'ed with the next PRS channel output, OR'ed with the previous PRS channel output and inverted.

Limitations

— — —

silabs.com | Building a more connected world. Rev. 1.03 | 19

Page 20

AN0918.0: MCU Series 0 to EFM32JGxx/PGxx Compatibility and Migration Guide

Peripherals Common Between MCU Series 0, EFM32JGxx/PGxx, and Wireless SoC Series 1

4.6.4 Pulse Counter (PCNT)

The major change is new support for the quadrature decoder in oversampling mode.

Table 4.14. PCNT

MCU Series 0 EFM32JGxx/PGxx and Wire-

Notes

less SoC Series 1

Enhancements

Fix filter length in oversample

mode.

PCNTn_CNT reset through

RSTEN.

Programmable filter length in

oversample mode.

PCNTn_CNT reset through

RSTEN or CNTRSTEN.

This is configured by FILTEN field in PCNTn_OVSCFG register.

CNTRSTEN in PCNTn_CTRL register works in a similar manner

as RSTEN, but only resetting the counter, PCNTn_CNT.

New Features

Externally clocked quadrature

decoder mode only.

Externally clocked quadrature

decoder 1X mode and Over-

Flutter is removed when setting FLUTTERRM field in

PCNTn_OVSCFG register.

sampling quadrature decoder

1X, 2X and 4X modes with flutter removal.

— Cascading PCNT through PRS. Possible to form a 32-bit pulse counter.

Limitations

— — —

4.6.5 Watchdog Timer (WDOG)

The major change is the Watchdog timeout can either generate a reset or an interrupt.

Table 4.15. WDOG

MCU Series 0 EFM32JGxx/PGxx and Wire-

less SoC Series 1

Enhancements

WDOG reset cannot be disa-

Option to disable WDOG reset. Set WDOGRSTDIS in WDOG_CTRL register to disable watchdog

bled.

New Features

— Configurable warning interrupt

at a percentage of timeout period.

— Configurable window interrupt at

a percentage of timeout period.

— PRS as a watchdog clear,

source is selected by

WDOG_PCH0_PRSCTRL register.

— Trigger an interrupt when a

WDOG clear happens before a

PRS event has been detected.

Limitations

Notes

timeout reset, option to trigger timeout interrupt instead.

Use WARNSEL field in WDOG_CTRL register, the percentage

are 25%, 50%, or 75%.

Use WINSEL field in WDOG_CTRL register, the percentage are

12.5%, 25%, 37.5%, 50%, 62.5%, 75%, or 87.5%.

Use CLRSRC bit in WDOG_CTRL register to select software or

PRS to clear the watchdog counter.

Use WDOG_PCH0_PRSCTRL and WDOG_PCH1_PRSCTRL

registers to select PRS channels.

— — —

silabs.com | Building a more connected world. Rev. 1.03 | 20

Page 21

Peripherals Common Between MCU Series 0, EFM32JGxx/PGxx, and Wireless SoC Series 1

4.6.6 Low Energy Sensor Interface (LESENSE)

AN0918.0: MCU Series 0 to EFM32JGxx/PGxx Compatibility and Migration Guide

The major

changes are ADC support and sensor evaluation. The LESENSE is only available on EFM32JG1x/PG1x and EFR32xG12/

xG13 devices.

Table 4.16. LESENSE

MCU Series 0 EFM32JG1x/PG1x and

EFR32xG12/xG13

Enhancements

Uses the analog comparators,

ACMP, for measurement of sensor signals.

Sensor evaluation can be based

on either ACMP outputs, or

threshold comparison.

Uses the analog comparators,

ACMP, or the ADC for measurement of sensor signals.

Sensor evaluation can be based

on either ACMP outputs, threshold comparison, sliding window,

or step detection.

LESENSE decoder, which is a

configurable state machine with

up to 16 states.

LESENSE decoder, which is a

configurable state machine with

up to 32 states.

New Features

— The decoder has a PRS output

named DECCMP.

Notes

—

In sliding window mode, the sensor data is compared against the

upper and lower limits of a window range.

Step detection is used to detect steps in the sensor data com-

pared to sensor data from the previous measurement.

—

This output can be used to indicate which state, or subset for

states, the decoder is currently in.

Limitations

Maximum four inputs for LESENSE decoder.

Maximum four inputs for LESENSE decoder.

—

silabs.com | Building a more connected world. Rev. 1.03 | 21

Page 22

AN0918.0: MCU Series 0 to EFM32JGxx/PGxx Compatibility and Migration Guide

Peripherals Common Between MCU Series 0, EFM32JGxx/PGxx, and Wireless SoC Series 1

4.7 Analog Interfaces

4.7.1 Analog Comparator (ACMP)

The major changes are the new APORT, and the external I/O can use as a reference voltage.

Table 4.17. ACMP

MCU Series 0 EFM32JGxx/PGxx and Wire-

Notes

less SoC Series 1

Enhancements

FULLBIAS and HALFBIAS

fields in ACMPn_CTRL register.

Symmetric hysteresis only. Symmetric and asymmetric hys-

No HALFBIAS field in

ACMPn_CTRL register.

teresis.

The HALFBIAS field is merged with BIASPROG field (increase to

6-bit value) in ACMPn_CTRL register.

Hysteresis is configured through the HYST field in ACMPn_HYS-

TERESIS0 and ACMPn_HYSTERESIS1 registers. The hysteresis

value can be positive or negative.

Selectable internal voltage for

negative input only.

Selectable internal voltage for

both positive and negative in-

Internal voltages are VDD, 1.25 V, 2.5 V and VDAC channel out-

put.

puts.

Scaler for VDD. Voltage dividers for VDD, 1.25

Voltage dividers in the ACMPn_HYSTERESIS0/1 registers.

V and 2.5 V.

4 resistance values for the internal capactive sense resistor.

8 resistance values for the internal capactive sense resistor.

—

New Features

— Up to 48 I/O (through APORT)

can be used as a dividable ref-

Not all selectable I/O are available on a given device, refer to the

device data sheet for details.

erence voltage.

— Selected level of accuracy. Configured by ACCURACY field in ACMPn_CTRL register, de-

fault is low accuracy mode to consume less current.

Voltage monitor function in

VCMP.

Limitations

The warm-up time is

HFPERCLK dependent and

should be >= 10us.

Dedicated capacitive sense

mode with up to 16 inputs.

Up to 8 external I/O for both

positive and negative input terminals.

The ACMP can be used to monitor supply voltages.

The warm-up time is self-timed

and will complete within 5µs.

Dedicated capacitive sense

mode with up to 80 inputs.

Up to 144 or 160 external I/O

(through APORT) for both positive and negative input terminals.

The voltage source (including AVDD, VREGVDD, IOVDD0 and

IOVDD1) can be selected by PWRSEL field in ACMPn_CTRL reg-

ister.

—

The capacitive sense mode inputs are configured through

APORT.

Add ACMPn_APORTREQ and ACMPn_APORTCONFLICT regis-

ters.

Not all selectable I/O are available on a given device, refer to the

device data sheet for details.

silabs.com | Building a more connected world. Rev. 1.03 | 22

Page 23

AN0918.0: MCU Series 0 to EFM32JGxx/PGxx Compatibility and Migration Guide

Peripherals Common Between MCU Series 0, EFM32JGxx/PGxx, and Wireless SoC Series 1

4.7.2 Analog to Digital Converter (ADC)

The major changes are FIFO and APORT support, and the ADC can run in EM2/3 energy mode.

Table 4.18. ADC

MCU Series 0 EFM32JGxx/PGxx and Wire-

Notes

less SoC Series 1

Enhancements

Separate single buffer for single

and scan conversion.

The ADC can run in EM0 - EM1

energy modes.

Separate FIFO for single and

scan conversion.

The ADC can run in EM0 - EM3

energy modes.

Four deep 32-bit FIFO to store conversion data along with chan-

nel ID and option to overwrite old data when full.

ADC must in asynchronous mode with AUXHFRCO as clock

source to run in EM2/3.

The ADC can wake the system from EM2/3 to EM0 on enabled in-

terrupts and it can also work with the DMA so that the system

does not have to be woken up to consume data.

New Features on All EFM32JGxx/PGxx and Wireless SoC Series 1 Devices

— Programmable watermark to

generate interrupt.

The DVL field of the ADCn_SINGLECTRLX/SCANTRLX controls

the FIFO watermark crossing which sets the SINGLEDV/SCANDV

bit in ADCn_STATUS high and is cleared when the data is read

and watermark falls below the DVL threshold.

— Window Compare Function. The ADC supports window compare function on both latest single

and scan sample.

The compare thresholds, ADGT and ADLT, are defined in the

ADCn_CMPTHR register.

— Programmable full scale (peak-

to-peak) voltage (VFS) with se-

Advanced VFS configuration is enabled by setting the REF field in

ADCn_SINGLECTRL or ADCn_SCANCTRL register to CONF.

lectable reference sources.

— The ADC can be used as ran-

dom number generator.

This is done simply by choosing the REF in the ADCn_SIN-

GLECTRL as CONF and by setting the VREFSEL in the

ADCn_SINGLECTRLX as VENTROPY.

— Externally controllable conver-

sion start time using PRS in

TIMED mode.

In TIMED mode, a long PRS pulse is expected to trigger the ADC

and its negative edge directly finishes input sampling and starts

the approximation phase, giving precise sampling frequency man-

agement.

New Features Only on EFM32JG1x/PG1x and EFR32xG12/xG13 Devices

— Reference should be kept warm

is programmable.

By default the scan mode reference is kept warm (CHCONREF-

WARMIDLE field in the ADCn_CTRL register). The user can also

choose to keep the single channel mode reference warm or to

keep the last used reference warm.

— Programmable delay between

repetitive conversions.

The REPDELAY field in the ADCn_SINGLECTRLX and

ADCn_SCANCTRLX registers can be used to set the delay be-

tween two repeated conversions in single channel and scan mode

respectively.

— Scan conversions can be trig-

—

gered using LESENSE.

— Programmable ADC behavior in

debug mode.

If DBGHALT field in the ADCn_CTRL register is set to 1, then in

debug mode ADC completes the current conversions and then

halts. This means that all conversion triggers that were received

before the debug halt occurred will be serviced before the ADC

halts.

silabs.com | Building a more connected world. Rev. 1.03 | 23

Page 24

AN0918.0: MCU Series 0 to EFM32JGxx/PGxx Compatibility and Migration Guide

Peripherals Common Between MCU Series 0, EFM32JGxx/PGxx, and Wireless SoC Series 1

MCU Series 0 EFM32JGxx/PGxx and Wire-

less SoC Series 1

Limitations

ADC_CLK from 32 kHz to 13

MHz.

ADC_CLK from 32 kHz to 16

MHz.

Up to 8 external input channels. Up to 144 external input chan-

nels (through APROT).

Up to 8 configurable samples in

scan sequence.

Gain calibration is available in

all voltage references except

Up to 32 configurable samples

in scan sequence.

Gain calibration is not available

in VDD and external references.

unbuffered 2xVDD.

4.7.3 Current Digital to Analog Converter (IDAC)

The major change is support for the APORT.

Table 4.19. IDAC

MCU Series 0 EFM32JGxx/PGxx and Wire-

less SoC Series 1

Notes

—

Add ADCn_APORTREQ and ADCn_APORTCONFLICT registers.

Not all selectable I/O are available on a given device, refer to the

device data sheet for details.

—

Use software to implement gain calibration on VDD and external

references.

Notes

Enhancements

TUNNING field is in IDAC_CAL

register.

DUTYCYCLEEN bit in

IDAC_DUTYCONFIG register.

TUNNING field is in

IDAC_CURPROG register.

No DUTYCYCLEEN bit in

IDAC_DUTYCONFIG register.

New Features

— Selects the power source for the

IDAC.

— Delays EM2 entry until IDAC-

OUT is stable.

— Status to indicate the IDAC is

active and output is stable.

— Interrupt for IDAC status and

APORT bus conflict.

Limitations

IDAC can output current either

to IDAC0_OUT pin, or to the

currently selected ADC channel.

IDAC can output current either

to IDAC0_OUT pin, or APORT

pins.

The IDAC_CAL register is removed.

Duty cycle enable or disable is not available in EM0/1.

Use PWRSEL bit in IDAC_CTRL register to select AVDD or

IOVDD as IDAC power source.

Set EM2DELAY bit in IDAC_CTRL register.

Add IDAC_STATUS register.

When the IDAC is enabled and warmed up, the CURSTABLE bit

in IDAC_STATUS will indicate that the IDAC is active and output

is stable.

Add IDAC_IEN, IDAC_IF, IDAC_IFS and IDAC_IFC registers.

The IDAC can generate two types of interrupts, CURSTABLE and

APORTCONFLICT, located in IDAC_IF register.

Add IDAC_APORTREQ and IDAC_APORTCONFLICT registers.

Not all selectable I/O are available on a given device, refer to the

device data sheet for details.

IDAC0_OUT is only available on

EFR32xG12/xG13 devices

silabs.com | Building a more connected world. Rev. 1.03 | 24

EFM32JG1x/PG1x and

.

Page 25

Peripherals Common Between MCU Series 0, EFM32JGxx/PGxx, and Wireless SoC Series 1

4.7.4 Operational Amplifier (OPAMP)

AN0918.0: MCU Series 0 to EFM32JGxx/PGxx Compatibility and Migration Guide

The major

changes are APORT and OPAMP timing support. The OPAMP is only available on EFM32JG1x/PG1x and EFR32xG12/

xG13 devices.

MCU Series 0 EFM32JG1x/PG1x and

EFR32xG12/xG13

Enhancements

The external pins for POSSEL

and NEGSEL mux are fixed.

The external pins for POSSEL

and NEGSEL mux can be fixed

or from APORT.

The opamp has two outputs, the

main output and an alternative

output network.

The opamp has three outputs,

the main output, an alternative

output network, and an APORT

output.

Alternative output with lower

Programmable drive strength. It is configured by DRIVESTRENGTH field in

drive strength.

Table 4.20. OPAMP

Notes

The OPAn_P pin is for positive input and OPAn_N pin is for nega-

tive input.

Not all selectable I/O are available on a given device, refer to the

device data sheet for details.

The OPAn_OUT pin is for main output and OPAn_OUTALT pin is

for alternative output.

Add VDACn_OPAx_APORTREQ and VDACn_OPAx_APORT-

CONFLICT registers.

Not all selectable I/O are available on a given device, refer to the

device data sheet for details.

VDACn_OPAx_CTRL register.

The outputs of the opamps can

be routed to the ADC.

The outputs of the opamps can

be routed to the ADC and

—

ACMP.

Opamp can be enabled with

software.

Opamp can be enabled either

with software or PRS.

The default source is software, setting PRSEN to 1 in

VDACn_OPAx_CTRL register enables PRS mode.

New Features

— Programmable startup delay. It is configured by STARTDLY field in VDACn_OPAx_TIMER reg-

ister.

— Programmable warmup time. It depends on the selected drive strength. It is configured by

WARMUPTIME field in VDACn_OPAx_TIMER register.

— Programmable settle time. It depends on the load at OPAMP output and selected drive

strength. It is configured by SETTLETIME field in

VDACn_OPAx_TIMER register.

— Preconfigured resistor ladder

with 3X gain.

The 3x gain resistor ladder is enabled by setting GAIN3X in

VDACn_OPAx_MUX register. By default all opamps are config-

ured in 3x gain mode.

— Unity gain bandwidth and

opamp output scaling.

Unity gain bandwidth of an opamp can be scaled by setting the

INCBW bit in VDACn_OPAx_CTRL register.

Opamp output drive strength is scaled by one half when the OUT-

SCALE bit in VDACn_OPAx_CTRL register is set.

— Interrupt generation for opamp

operation.

Interrupt flags for the opamp output is settled externally at the

load, protocol error when the opamp is triggered, and APORT bus

conflict occurs.

— Asynchronous PRS output. One of two asynchronous PRS outputs (opamp warmup and out-

put valid status) can be enabled for each opamp by setting

PRSOUTMODE in VDACn_OPAx_CTRL register.

Limitations

silabs.com | Building a more connected world. Rev. 1.03 | 25

Page 26

AN0918.0: MCU Series 0 to EFM32JGxx/PGxx Compatibility and Migration Guide

Peripherals Common Between MCU Series 0, EFM32JGxx/PGxx, and Wireless SoC Series 1

MCU Series 0 EFM32JG1x/PG1x and

Notes

EFR32xG12/xG13

Two of the opamps are part of

the DAC, while the others are

standalone.

Two of the opamps are part of

the VDAC, while the others are

standalone.

Since OPA0 and OPA1 are part of the VDAC, special considera-

tions need to be taken when both VDAC channel 0/channel 1 and

OPA0/OPA1 are used.

4.7.5 Digital to Analog Converter (VDAC)

The major

changes are APORT and VDAC timing support. The VDAC is only available on EFM32JG1x/PG1x and EFR32xG12/xG13

devices.

Table 4.21. VDAC

MCU Series 0 EFM32JG1x/PG1x and

Notes

EFR32xG12/xG13

Enhancements

Each DAC channel has two outputs, the main output

(DACn_OUTx) and an alternative output (DACn_OUTxALT).

Each VDAC channel has three

outputs, the main output

(VDACn_OUTx), an alternative

output (VDACn_OUTxALT), and

an APORT output.

Add VDACn_OPAx_APORTREQ and VDACn_OPAx_APORT-

CONFLICT registers.

Not all selectable I/O are available on a given device, refer to the

device data sheet for details.

The drive strength is fixed. Programmable drive strength. It is configured by DRIVESTRENGTH field in

VDACn_OPAx_CTRL register.

Three internal voltage references are available.

Five internal and one external

voltage (VDAC0_EXT) referen-

The new internal references are 1.25 V and 2.5 V low noise

bandgap references.

ces are available.

The DAC supports three conversion modes.

Conversion is triggered either

by software, PRS, or LESENSE.

The DAC supports two conversion modes.

Conversion is triggered either

by software, PRS, refresh timer,

The Sample/Hold mode is removed.

The PRS pulse can be from a synchronous or asynchronous PRS

producer.

or LESENSE.

New Features

— Programmable warmup time. It depends on the selected drive strength. It is configured by

WARMUPTIME field in VDACn_OPAx_TIMER register.

— Asynchronous clocking mode. Uses internal 12 MHz VDAC oscillator to generate DAC_CLK to

allow VDAC operation in EM2/3.

— New Interrupt flags for VDAC

operation.

These are channel buffer level (CHxBL), channel overflow

(CHxOF), and EM23ERR interrupt flags.

Limitations

— — —

silabs.com | Building a more connected world. Rev. 1.03 | 26

Page 27

AN0918.0: MCU Series 0 to EFM32JGxx/PGxx Compatibility and Migration Guide

Software Migration

5. Software Migration

The EFM32JGxx/PGxx and Wireless SoC Series 1 devices are software compatible with the existing MCU Series 0 devices, so only

minor changes are required for peripherals that are common to MCU Series 0, EFM32JGxx/PGxx, and Wireless SoC Series 1 (especially when enhancements and new features are not used).

silabs.com | Building a more connected world. Rev. 1.03 | 27

Page 28

AN0918.0: MCU Series 0 to EFM32JGxx/PGxx Compatibility and Migration Guide

5.1 Peripheral Support Library (emlib) and energyAware Drivers (emdrv)

Software Migration

The Peripheral

Support Library (emlib) abstracts the differences between MCU Series 0 and EFM32JGxx/PGxx through the API, so

software migration becomes transparent to the firmware author.

The emlib modules are found under the Simplicity Studio installation path. The default location on Windows is:

C:\SiliconLabs\SimplicityStudio\v4\developer\sdks\gecko_sdk_suite\v1.0\platform\emlib

The energyAware Drivers Library (emdrv) is optimized for speed and power consumption while maintaining API compatibility between

different product families.

It is highly recommended to develop peripherals' software with emdrv since it can maintain 100% software compatibility across MCU

Series 0 and EFM32JGxx/PGxx.

The available peripherals' emdrv modules are found under the Simplicity Studio installation path. The default location on Windows is:

C:\SiliconLabs\SimplicityStudio\v4\developer\sdks\gecko_sdk_suite\v1.0\platform\emdrv

Wireless SoC Series 1 devices are configurable through the Silicon Labs software stacks, which are a layer on top of the emdrv modules. Systems migrating from MCU Series 0 to a Wireless SoC Series 1 platform should use the tools available in Simplicity Studio to

migrate their code.

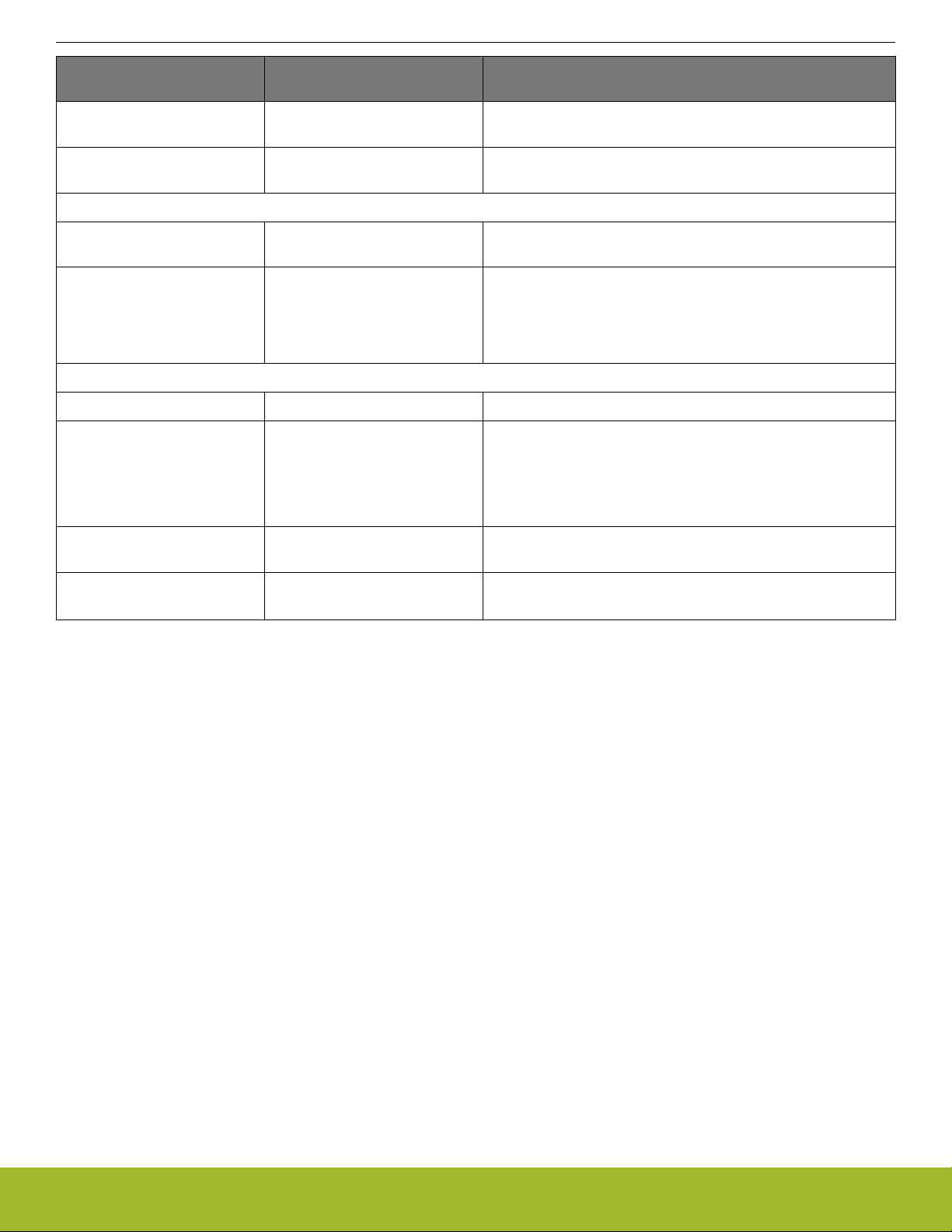

Table 5.1. Software Migration Checklist

Items Support on emlib & emdrv Notes

DCDC power configurations in

EFM32JGxx/PGxx.

emlib:

Call below function after power up to initialize the DCDC (if availa-

ble) power configuration.

New API for DCDC configura-

tion in em_emu.c.

bool EMU_DCDCInit(const EMU_DCDCInit_TypeDef *dcdcI-

nit)

HFXO startup initialization in

emlib:

MCU Series 0 and EFM32JGxx/

PGxx.

Common API for HFXO startup

in em_cmu.c.

LFXO startup initialization in

emlib:

MCU Series 0 and EFM32JGxx/

PGxx.

Common API for LFXO startup

in em_cmu.c.

Use HFRCO as HFCLK. emlib:

Common API in em_cmu.c to

setup HFRCO frequency band.

Flash startup timing in

— Use default timing or initialize the time to power up Flash on tran-

EFM32JGxx/PGxx.

Call below function to configure HFXO to ensure safe startup for

the given crystal.

void CMU_HFXOInit(const CMU_HFXOInit_TypeDef *hfxoI-

nit)

Call below function to optimize startup time and power consump-

tion for a given low frequency crystal.

void CMU_LFXOInit(const CMU_LFXOInit_TypeDef *lfxoI-

nit)

Call below function to change HFRCO frequency band.

void CMU_HFRCOBandSet(CMU_HFRCOFreq_TypeDef setFreq)

Calibrate HFRCO of

EFM32JGxx/PGxx

at startup to match with

MCU Series 0 HFRCO frequency band.

Otherwise manual adjustment for HFRCO frequency dependent

parameters are required.

sitions from EM2/3 to EM0.

silabs.com | Building a more connected world. Rev. 1.03 | 28

Page 29

AN0918.0: MCU Series 0 to EFM32JGxx/PGxx Compatibility and Migration Guide

Items Support on emlib & emdrv Notes

Software Migration

Pin enable and location for digital peripherals.

APORT for analog peripherals

in EFM32JGxx/PGxx.

emlib:

The new ROUTEPEN and

ROUTELOC definitions of digital

peripherals can be found in corresponding emlib header files.

emlib:

The new APORT definitions of

analog peripherals can be found

in corresponding emlib header

files.

At least two registers (ROUTEPEN and ROUTELOCn) are used

for pin enable and location in

EFM32JGxx/PGxx

peripherals (only

one ROUTE register in MCU Series 0).

Independent location field for each pin allows pins in peripheral of

EFM32JGxx/PGxx configure to different locations.

Example for EFM32JGxx/PGxx:

USART0->ROUTEPEN = USART_ROUTEPEN_RXPEN | USART_ROUTEP

EN_TXPEN;

USART0->ROUTELOC0 = ( USART0->ROUTELOC0 & ~( _USART_RO

UTELOC0_TXLOC_MASK | _USART_ROUTELOC0_RXLOC_MASK ) ) |

( USART_ROUTELOC0_TXLOC_LOC0 << _USART_ROUTELOC0_TXLOC

_SHIFT ) | ( USART_ROUTELOC0_RXLOC_LOC0 << _USART_ROUT

ELOC0_RXLOC_SHIFT );

Example for MCU Series 0:

USART0->ROUTE = USART_ROUTE_RXPEN | USART_ROUTE_TXPEN

| USART_ROUTE_LOCATION_LOC0;

To route signals between analog peripherals and GPIOs.

Example to use APORT BUS1X channel 6 for ADC input in

EFM32JGxx/PGxx:

ADC_InitSingle_TypeDef singleInit = ADC_INITSINGLE_DEF

AULT;

singleInit.posSel = adcPosSelAPORT1XCH6;

Example to use analog channel 1 for ADC input in

ADC_InitSingle_TypeDef singleInit = ADC_INITSINGLE_DEF

AULT;

singleInit.input = adcSingleInputCh1;

MCU Series 0:

APORT conflict between analog peripherals can be detected by

XXX_APORTCONFLICT registers or APORTCONFLICT interrupt.

GPIO emlib:

Different GPIO grouping (0-3, 4-7, 8-11, 12-15) in EFM32JGxx/

PGxx to trigger interrupt or to form PRS producer output.

Common API for GPIO configu-

ration in em_gpio.c.

Pins with the same pin number within a group can now be used

as interrupt trigger sources or PRS producer outputs.

emdrv:

For example below, PC6 (interrupt source 6) and PF6 (interrupt

gpiointerrupt

source 4) in group 4-7 can both configure as interrupt sources

without conflict.

GPIO_PinModeSet(gpioPortC, 6, gpioModeInputPull, 1);

GPIO_ExtIntConfig(gpioPortC, 6, 6, false, true, true);

GPIO_PinModeSet(gpioPortF, 6, gpioModeInputPull, 1);

GPIO_ExtIntConfig(gpioPortF, 6, 4, false, true, true);

Bootloader — The preprogrammed bootloader (if available) moves from Main

page to Bootloader page in

EFM32JGxx/PGxx.

DAC & VDAC emlib:

Except

VDAC_PrescaleCalc(…), the function prototypes of

em_dac.c are compatible with em_vdac.c (DAC_XXX(…) to

New source file em_vdac.c for

VDAC_XXX(…)).

VDAC.

silabs.com | Building a more connected world. Rev. 1.03 | 29

Page 30

AN0918.0: MCU Series 0 to EFM32JGxx/PGxx Compatibility and Migration Guide

Items Support on emlib & emdrv Notes

Software Migration

VCMP & VMON emlib:

New APIs for VMON in

em_emu.c.

AES & CRYPTO emlib:

New source file em_crypto.c for

CRYPTO.

RTC & RTCC emlib:

New source file em_rtcc.c for

RTCC.

The VCMP function in MCU Series 0 is now handled by Voltage

Monitor (VMON) in EFM32JGxx/PGxx.

void EMU_VmonInit(const EMU_VmonInit_TypeDef *vmonI-

nit)

void EMU_VmonHystInit(const EMU_VmonHystInit_TypeDef

*vmonInit)

void EMU_VmonEnable(EMU_VmonChannel_TypeDef channel,

bool enable)

bool EMU_VmonChannelStatusGet(EMU_VmonChannel_TypeDef

channel)

The AES function in MCU Series 0 is now handled by Crypto Ac-

celerator (CRYPTO) in

EFM32JGxx/PGxx.

The AES and new cryptographic operations in EFM32JGxx/PGxx

are handled by mbedTLS library.

The mbedTLS library is found under the Simplicity Studio installa-

tion path. The default location on Windows is:

C:\SiliconLabs\SimplicityStudio\v4\developer\sdks\geck

o_sdk_suite\v1.0\util\third_party\mbedtls

APIs in em_rtcc.c are not compatible with em_rtc.c.

The rtcdrv provides common RTC APIs for MCU Series 0 and

EFM32JGxx/PGxx.

emdrv:

The rtcdrv now handles both

RTC and RTCC.

µDMA & LDMA emlib:

APIs in em_ldma.c are not compatible with em_dma.c (for µDMA

in MCU Series 0).

New source file em_ldma.c for

LDMA.

emdrv:

The dmadrv provides common DMA APIs for MCU Series 0 and

EFM32JGxx/PGxx

.

The dmadrv now handles both

µDMA and LDMA.

5.2 Migration Examples

The examples of this section describe the usage of emlib and emdrv to migrate software from MCU Series 0 to EFM32JGxx/PGxx

.

Almost 100% of the code can be reused during migration and just minor modifications need to be made for code running on the new

platform.

The hardware differences between platforms will be handled by the peripherals' initialization functions of emlib, it just needs to change

the parameters in the function calls or peripherals' initialization structures to fit for the selected device.

Usually nothing needs to be changed when migrating the portion of emdrv, keeps all function calls the same and just modifies the IDE

settings for the target device.

silabs.com | Building a more connected world. Rev. 1.03 | 30

Page 31

AN0918.0: MCU Series 0 to EFM32JGxx/PGxx Compatibility and Migration Guide

5.2.1 Migration Example for RTC and ADC

This example configures the RTC to trigger ADC conversion and toggle LED every 500ms.

Source code that runs on EFM32GG STK (EFM32GG_STK3700).

#include <stdio.h>

#include "em_device.h"

#include "em_adc.h"

#include "em_chip.h"

#include "em_emu.h"

#include "em_gpio.h"

#include "em_cmu.h"

#include "rtcdriver.h"

/* STK specific LED port and pin */

#define LED_PORT gpioPortE

#define LED_PIN 2

uint32_t i;

uint32_t sample;

RTCDRV_TimerID_t id;

/**************************************************************************//**

* @brief RTC Callback used to toggle LED and ADC measurement

*****************************************************************************/

void rtcCallback( RTCDRV_TimerID_t id, void *user )

{

/* Start ADC and get result */

ADC_Start(ADC0, adcStartSingle);

while (ADC0->STATUS & ADC_STATUS_SINGLEACT)

;

sample = ADC_DataSingleGet(ADC0);

/* Toggle LED */

i++;

if (i & 0x01)

{

GPIO_PinOutSet(LED_PORT, LED_PIN);

}

else

{

GPIO_PinOutClear(LED_PORT, LED_PIN);

}

}

Software Migration

/**************************************************************************//**

* @brief Initialize ADC for single conversion

*****************************************************************************/

void setupAdc(void)

{

ADC_Init_TypeDef init = ADC_INIT_DEFAULT;

ADC_InitSingle_TypeDef singleInit = ADC_INITSINGLE_DEFAULT;

/* Init common settings for both single and scan conversion */

init.timebase = ADC_TimebaseCalc(0);

init.prescale = ADC_PrescaleCalc(10000000, 0);

ADC_Init(ADC0, &init);

/* Init for single conversion */

singleInit.reference = adcRefVDD;

singleInit.input = adcSingleInpCh1;

ADC_InitSingle(ADC0, &singleInit);

}

/**************************************************************************//**

* @brief Main function

*****************************************************************************/

int main(void)

{

/* Chip errata */

CHIP_Init();

silabs.com | Building a more connected world. Rev. 1.03 | 31

Page 32

AN0918.0: MCU Series 0 to EFM32JGxx/PGxx Compatibility and Migration Guide

/* Setup GPIO and ADC. */

CMU_ClockEnable(cmuClock_GPIO, true);

GPIO_PinModeSet(LED_PORT, LED_PIN, gpioModePushPull, 0);

CMU_ClockEnable(cmuClock_ADC0, true);

setupAdc();

/* Initialize RTC driver. */

RTCDRV_Init();

RTCDRV_AllocateTimer( &id );

RTCDRV_StartTimer( id, rtcdrvTimerTypePeriodic, 500, rtcCallback, NULL );

while (1)

{

/* Wait in EM1 */

EMU_EnterEM1();

}

}

To migrate this example from EFM32GG STK to EFM32PG STK, following changes are made.

Table 5.2. Changes for RTC and ADC example migration

EFM32GG STK EFM32PG STK Notes

Software Migration

No need to setup power configuration.

Need to setup power configuration at startup if device has DC-

Call EMU_DCDCInit(&dcdcInit); to initialize the power configura-

tion.

DC converter.

Use RTC for ADC Trigger and

LED toggle.

Use DOUTSET and DOUTCLR

registers to set and clear LED

pin.

Use RTCC for ADC trigger and

LED toggle.

No DOUTSET and DOUTCLR

registers to set and clear GPIO

pins, use Peripheral Bit Set and

The rtcdrv is used in this example so the migration from RTC to

RTCC is transparent.

The

GPIO_PinOutSet() and GPIO_PinOutClear() inline func-

tions in em_gpio.h will handle it so the migration is transparent.

Clear to set and clear LED pins.

LED on pin PE2. LED on pin PF4. Change #define statements for LED port (LED_PORT) and pin

(LED_PIN) in GPIO_PinOutSet(), GPIO_PinOutClear() and

GPIO_PinModeSet().

ADC input channel on PD1. PD1 is not available in

EFM32PG STK

, use APORT to

Add below parameters to ADC single conversion initialization

structure, the APORT definitions are included in em_adc.h.

configure PC6 as ADC input.

singleInit.posSel = adcPosSelAPORT1XCH6;

Modified source code that runs on EFM32PG STK (SLSTK3401A_EFM32PG).

#include <stdio.h>

#include "em_device.h"

#include "em_adc.h"

#include "em_chip.h"

#include "em_emu.h"

#include "em_gpio.h"

#include "em_cmu.h"

#include "rtcdriver.h"

/* STK specific LED port and pin */

#define LED_PORT gpioPortF

#define LED_PIN 4

uint32_t i;

uint32_t sample;

RTCDRV_TimerID_t id;

/**************************************************************************//**

* @brief RTC Callback used to toggle LED and ADC measurement

*****************************************************************************/

void rtcCallback( RTCDRV_TimerID_t id, void *user )

silabs.com | Building a more connected world. Rev. 1.03 | 32

Page 33

AN0918.0: MCU Series 0 to EFM32JGxx/PGxx Compatibility and Migration Guide

{

/* Start ADC and get result */

ADC_Start(ADC0, adcStartSingle);

while (ADC0->STATUS & ADC_STATUS_SINGLEACT)

;

sample = ADC_DataSingleGet(ADC0);

/* Toggle LED */

i++;

if (i & 0x01)

{

GPIO_PinOutSet(LED_PORT, LED_PIN);

}

else

{

GPIO_PinOutClear(LED_PORT, LED_PIN);

}

}

/**************************************************************************//**

* @brief Initialize ADC for single conversion

*****************************************************************************/

void setupAdc(void)

{

ADC_Init_TypeDef init = ADC_INIT_DEFAULT;

ADC_InitSingle_TypeDef singleInit = ADC_INITSINGLE_DEFAULT;

Software Migration

/* Init common settings for both single and scan conversion */

init.timebase = ADC_TimebaseCalc(0);

init.prescale = ADC_PrescaleCalc(10000000, 0);

ADC_Init(ADC0, &init);

/* Init for single conversion */

singleInit.reference = adcRefVDD;

singleInit.posSel = adcPosSelAPORT1XCH6;

ADC_InitSingle(ADC0, &singleInit);

}

/**************************************************************************//**

* @brief Main function

*****************************************************************************/

int main(void)

{

EMU_DCDCInit_TypeDef dcdcInit = EMU_DCDCINIT_DEFAULT;

/* Chip errata */

CHIP_Init();

/* Init DCDC regulator with specific parameters */

EMU_DCDCInit(&dcdcInit);

/* Setup GPIO and ADC. */

CMU_ClockEnable(cmuClock_GPIO, true);

GPIO_PinModeSet(LED_PORT, LED_PIN, gpioModePushPull, 0);

CMU_ClockEnable(cmuClock_ADC0, true);

setupAdc();

/* Initialize RTC driver. */

RTCDRV_Init();

RTCDRV_AllocateTimer( &id );

RTCDRV_StartTimer( id, rtcdrvTimerTypePeriodic, 500, rtcCallback, NULL );

while (1)

{

/* Wait in EM1 */

EMU_EnterEM1();

}

}

silabs.com | Building a more connected world. Rev. 1.03 | 33

Page 34

AN0918.0: MCU Series 0 to EFM32JGxx/PGxx Compatibility and Migration Guide

5.2.2 Migration Example for USART and DMA

This example configures the DMA to transmit data through USART.

Source code that runs on EFM32GG STK (EFM32GG_STK3700).

#include <stdio.h>

#include "em_chip.h"

#include "em_cmu.h"

#include "em_emu.h"

#include "dmadrv.h"

#include "retargetserial.h"

/* STK specific retarget serial output */

#define DMA_USART_SIGNAL dmadrvPeripheralSignal_USART1_TXBL

unsigned int channel;

uint8_t str[] = "Hello DMA !\n";

/**************************************************************************//**

* @brief Main function

*****************************************************************************/

int main( void )

{

CMU_HFXOInit_TypeDef hfxoInit = CMU_HFXOINIT_DEFAULT;

Software Migration

/* Chip errata */

CHIP_Init();

/* Init HFXO with specific parameters */

CMU_HFXOInit(&hfxoInit);

/* Switch HFCLK to HFXO and disable HFRCO */

CMU_ClockSelectSet(cmuClock_HF, cmuSelect_HFXO);

CMU_OscillatorEnable(cmuOsc_HFRCO, false, false);

/* Initialize USART. */

RETARGET_SerialInit();

/* Initialize DMA driver. */

DMADRV_Init();

/* Request a DMA channel. */

DMADRV_AllocateChannel( &channel, NULL );

/* Start the DMA transfer. */

DMADRV_MemoryPeripheral( channel,

DMA_USART_SIGNAL,

(void*)&(RETARGET_UART->TXDATA),

str,

true,

sizeof( str ),

dmadrvDataSize1,

NULL,

NULL );

while (1)

{

;

}

}

To migrate this example from EFM32GG STK to EFM32PG STK

silabs.com | Building a more connected world. Rev. 1.03 | 34

, following changes are made.

Page 35

AN0918.0: MCU Series 0 to EFM32JGxx/PGxx Compatibility and Migration Guide

Table 5.3. Changes for USART and DMA example migration

EFM32GG STK EFM32PG STK Notes

Software Migration

No need to setup power configuration.

Need to setup power configuration at startup if device has DC-

Call EMU_DCDCInit(&dcdcInit);

tion.

DC converter.

Use µDMA for USART transmit.

Use LDMA for USART transmit. The dmadrv is used in this example so the migration from µDMA

to LDMA is transparent.

Use USART1 as retarget serial

output.

Use USART0 as retarget serial

output.

Change #define statement for USART (DMA_USART_SIGNAL)

with DMA in DMADRV_MemoryPeripheral().

Modified source code that runs on EFM32PG STK (SLSTK3401A_EFM32PG).

#include <stdio.h>

#include "em_chip.h"

#include "em_cmu.h"

#include "em_emu.h"

#include "dmadrv.h"

#include "retargetserial.h"

/* STK specific retarget serial output */

#define DMA_USART_SIGNAL dmadrvPeripheralSignal_USART0_TXBL

unsigned int channel;

uint8_t str[] = "Hello DMA !\n";

/**************************************************************************//**

* @brief Main function

*****************************************************************************/

int main( void )

{

EMU_DCDCInit_TypeDef dcdcInit = EMU_DCDCINIT_DEFAULT;

CMU_HFXOInit_TypeDef hfxoInit = CMU_HFXOINIT_DEFAULT;

to initialize the power configura-

/* Chip errata */

CHIP_Init();

/* Init DCDC regulator and HFXO with specific parameters */

EMU_DCDCInit(&dcdcInit);

CMU_HFXOInit(&hfxoInit);

/* Switch HFCLK to HFXO and disable HFRCO */

CMU_ClockSelectSet(cmuClock_HF, cmuSelect_HFXO);

CMU_OscillatorEnable(cmuOsc_HFRCO, false, false);

/* Initialize USART. */

RETARGET_SerialInit();

/* Initialize DMA driver. */

DMADRV_Init();

/* Request a DMA channel. */

DMADRV_AllocateChannel( &channel, NULL );

/* Start the DMA transfer. */

DMADRV_MemoryPeripheral( channel,

DMA_USART_SIGNAL,

(void*)&(RETARGET_UART->TXDATA),

str,

true,

sizeof( str ),

dmadrvDataSize1,

NULL,

NULL );

while (1)

silabs.com | Building a more connected world. Rev. 1.03 | 35

Page 36

{

;

}

}

AN0918.0: MCU Series 0 to EFM32JGxx/PGxx Compatibility and Migration Guide

Software Migration

silabs.com | Building a more connected world. Rev. 1.03 | 36

Page 37

AN0918.0: MCU Series 0 to EFM32JGxx/PGxx Compatibility and Migration Guide

Hardware Migration

6. Hardware Migration

6.1 Pin Compatibility