Si4133-BT

查询Si4112供应商

Si4133

Si4123/22/13/12

D

UAL-BAND

F

W

OR

IRELESS COMMUNICATIONS

RF S

YNTHESIZER WITH INTEGRATED

Features

!

Dual-Band RF Synthesizers

RF1: 900 MHz to 1.8 GHz

"

RF2: 750 MHz to 1.5 GHz

"

!

IF Synthesizer

IF: 62.5 MHz to 1000 MHz

"

!

Integrated VCOs, Loop Filters,

Varactors, and Resonators

!

Minimal (2) External

Components Required

!

Low Phase Noise

!

Programmable Power Down Modes

!

1 µA Standby Current

!

18 mA Typical Supply Current

!

2.7 V to 3.6 V Operation

!

Packages: 24-Pin TSSOP, 28-Lead

MLP

Applications

!

Dual-Band Communications

!

Digital Cellular Telephones

GSM, DCS1800, PCS1900

!

Digital Cordless Phones

!

Analog Cordless Phones

!

Wireless LAN and WAN

Description

The Si4133 is a mo nolith ic in tegrate d circui t that per forms bo th IF an d dualband RF synthesis for wireless communications applications. The Si4133

includes three VCOs, loop filters, reference and VCO dividers, and phase

detectors. Divider and power-down settings are programmable through a

three-wire serial interface.

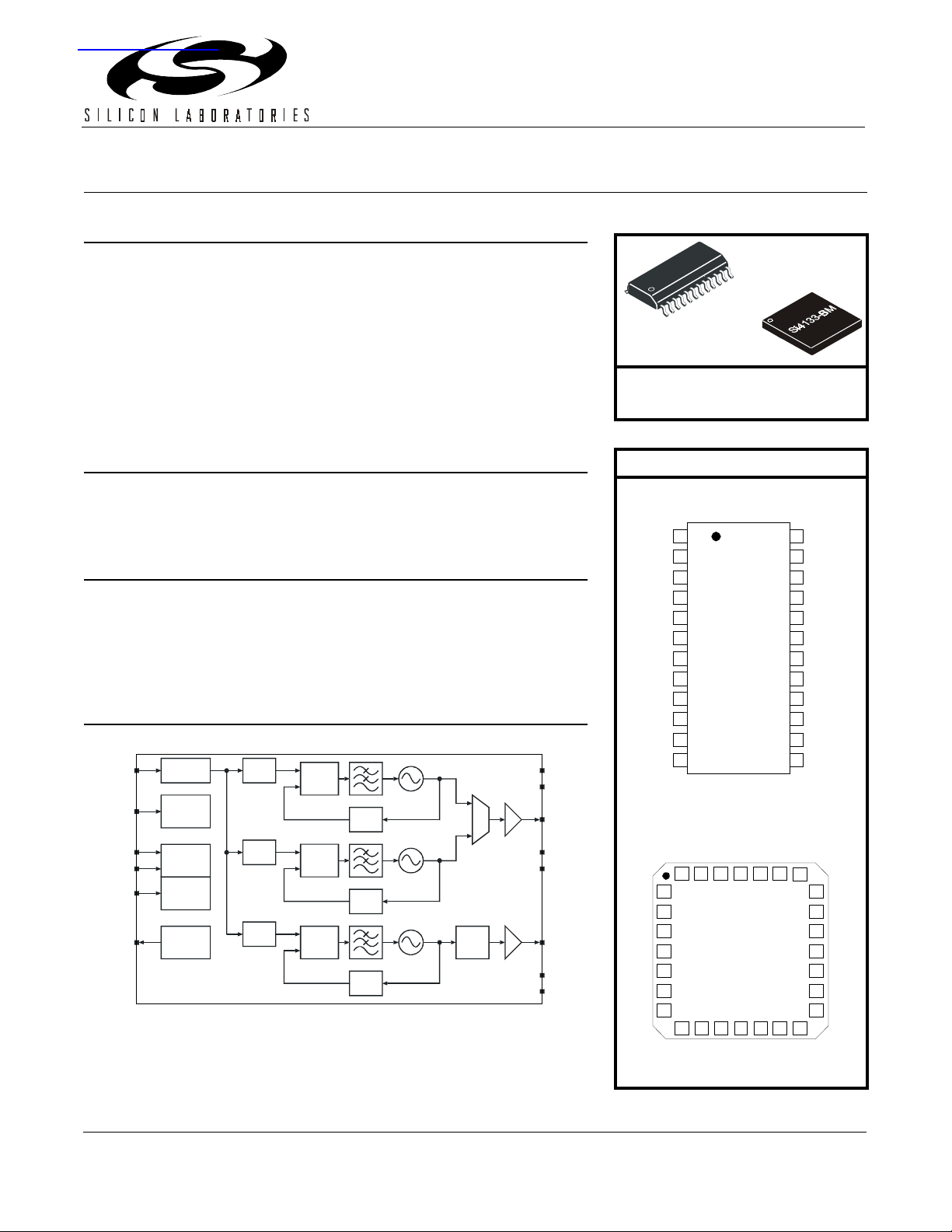

Functional Block Diagram

XIN

PWDNB

Reference

Am plifier

Power

Down

Control

÷

R

Phase

Detector

RF1

÷

N

RFLA

RFLB

RFOUT

VCOS

Si4133-BT

Ordering Information:

See page 31.

Pin Assignments

Si4133-BT

SCLK

SDATA

GNDR

RFLD

RFLC

GNDR

RFLB

RFLA

GNDR

GNDR

RFOUT

VDDR

124

223

322

421

520

619

718

817

916

10 15

11 14

12 13

Si4133-BM

SENB

VDDI

IFOUT

GNDI

IFLB

IFLA

GNDD

VDDD

GNDD

XIN

PWDNB

AUXOUT

Rev. 1.1 3/01 Copyright © 2001 by Silicon Laboratories Si4133-DS11

SDATA

SCLK

SENB

AUXOUT IFD I V

Serial

Inte r f ace

22-bit

Data

Register

Test

Mux

÷

R

÷

Phase

Detector

R

Phase

Detector

RF2

÷

N

IF

÷

N

RFLC

RFLD

IFO UT

IFL A

IFL B

VDDI

SCLK

SDATA

GNDR

28 27 26 25 24 23

1

GNDR

2

RFLD

3

RFLC

4

GNDR GNDD

5

RFLB

6

RFLA

7

GNDR

8 9 10 11 12 13 14

VDDR SENB

GNDR

GNDR

RFOUT

AUXOUT

Patents pending

This information applies to a product under development. Its characteristics and specifications are subject to change without notice.

IFOUT

GNDI

22

21

GNDI

20

IFLB

19

IFLA

18

17

VDDD

16

GNDD

15

XIN

GNDD

PWDNB

Si4133

2 Rev. 1.1

Si4133

T

ABLE OF

C

ONTENTS

Section Page

Electrical Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Serial Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Setting the VCO Center Frequencies . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Extended Frequency Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Self-Tuning Algorithm . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Output Frequencies . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

PLL Loop Dynamics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

RF and IF Outputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Reference Frequency Amplifier . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Power Down Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Auxiliary Output (AUXOUT) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Pin Descriptions: Si4133-BT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Pin Descriptions: Si4133-BM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Ordering Guide . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Si4133 Derivative Devices . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Package Outline: Si4133-BT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Package Outline: Si4133-BM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Contact Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Rev. 1.1 3

Si4133

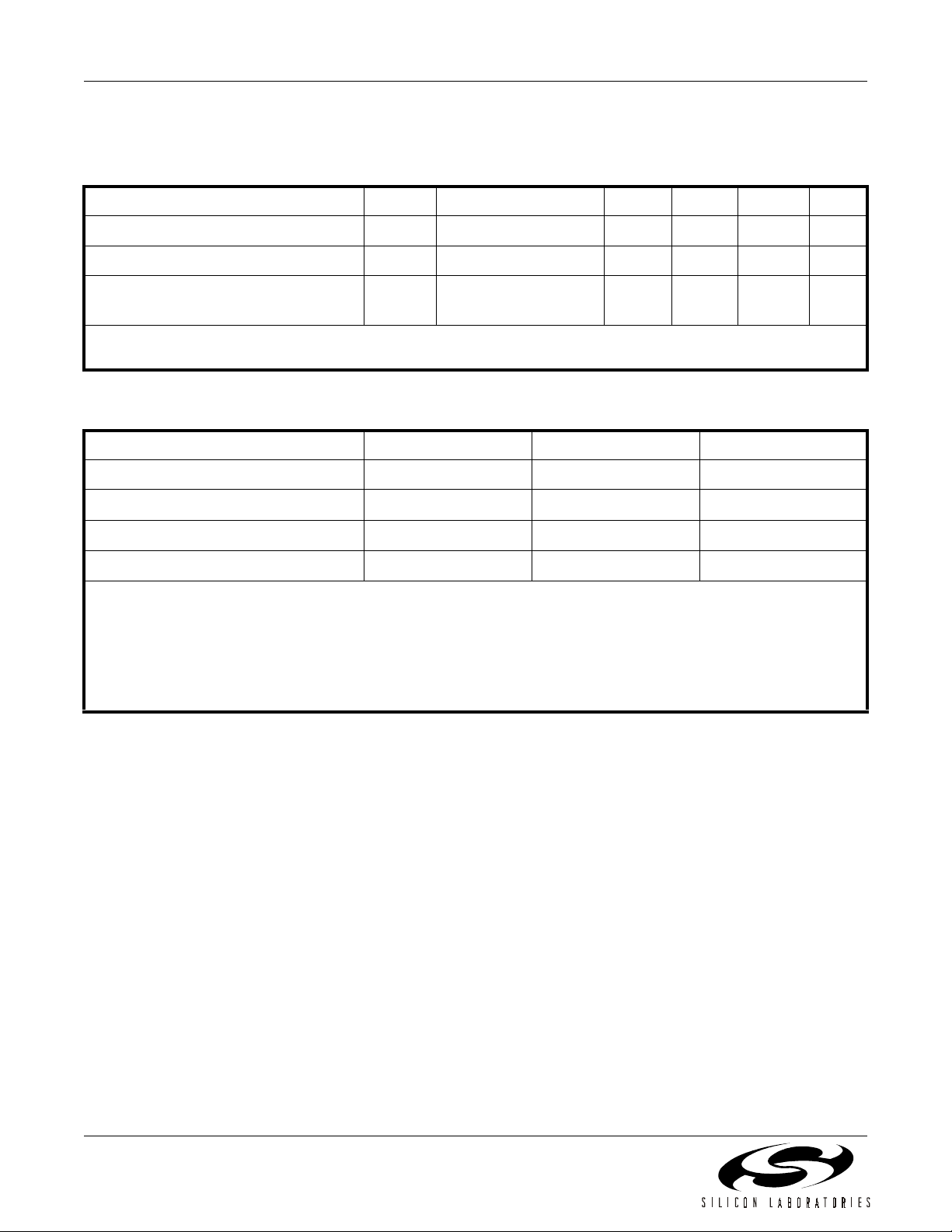

Electrical Specifications

Table 1. Recommended Operating Conditions

Parameter Symbol Test Condition Min Typ Max Unit

Ambient Temperature T

Supply Voltage V

Supply Voltages Difference V

Note: All minimum and maximum specifications are guaranteed and apply across the recommended operating conditions.

Typical values apply at nominal supply voltages and an operating temperature of 25°C unless otherwise stated.

Table 2. Absolute Maximum Ratings

1,2

DD

A

(V

(V

DDR

DDI

– V

– V

∆

DDD

DDD

),

)

–40 25 85 °C

2.7 3.0 3.6 V

–0.3 — 0.3 V

Parameter Symbol Value Unit

DC Supply Voltage V

Input Current

Input Voltage

3

3

Storage Temperature Range T

Notes:

1. Permanent device damage may occur if the above Absolute Maximum Ratings are exceeded. Functional operation

should be restricted to the conditions as specified in the operational sections of this data sheet. Exposure to absolute

maximum rating conditions for extended periods may affect device reliability.

2. This device is a high performan ce RF integrated circ uit with an ESD rating of < 2 kV. Handling and assembly of

this device should only be done at ESD-protected workstations.

3. For signals SCLK, SDATA, SENB, PWDNB and XIN.

I

V

DD

IN

IN

STG

–0.5 to 4.0 V

±10 mA

–0.3 to VDD+0.3 V

–55 to 150

o

C

4 Rev. 1.1

Si4133

Table 3. DC Characteristics

(VDD = 2.7 to 3.6 V, TA = –40 to 85°C)

Parameter Symbol Test Condition Min Typ Max Unit

Total Supply Current

RF1 Mode Supply Current

RF2 Mode Supply Current

IF Mode Supply Current

1

1

1

1

Standby Current PWDNB = 0 — 1 — µA

High Level Input Voltage

Low Level Input Voltage

High Level Input Current

Low Level Input Current

High Level Output Voltage

Low Level Output Voltage

Notes:

1. RF1 = 1.6 GHz, RF2 = 1.1 GHz, IFOUT = 550 MHz, LPWR = 0

2. For signals SCLK, SDATA, SENB, and PWDNB.

3. For signal AUXOUT.

2

2

2

2

3

3

V

IH

V

IL

I

IH

I

IL

V

OH

V

OL

RF1 and IF operating — 18 27 mA

—1016mA

—916mA

—813mA

V

V

V

=

IH

= 3.6 V

DD

V

IL

=

DD

3.6 V,

=

0 V,

3.6 V

0.7 V

DD

— — 0.3 V

–10 — 10 µA

–10 — 10 µA

——V

DD

IOH = –500 µA VDD–0.4 — — V

IOH = 500 µA — — 0.4 V

V

Rev. 1.1 5

Si4133

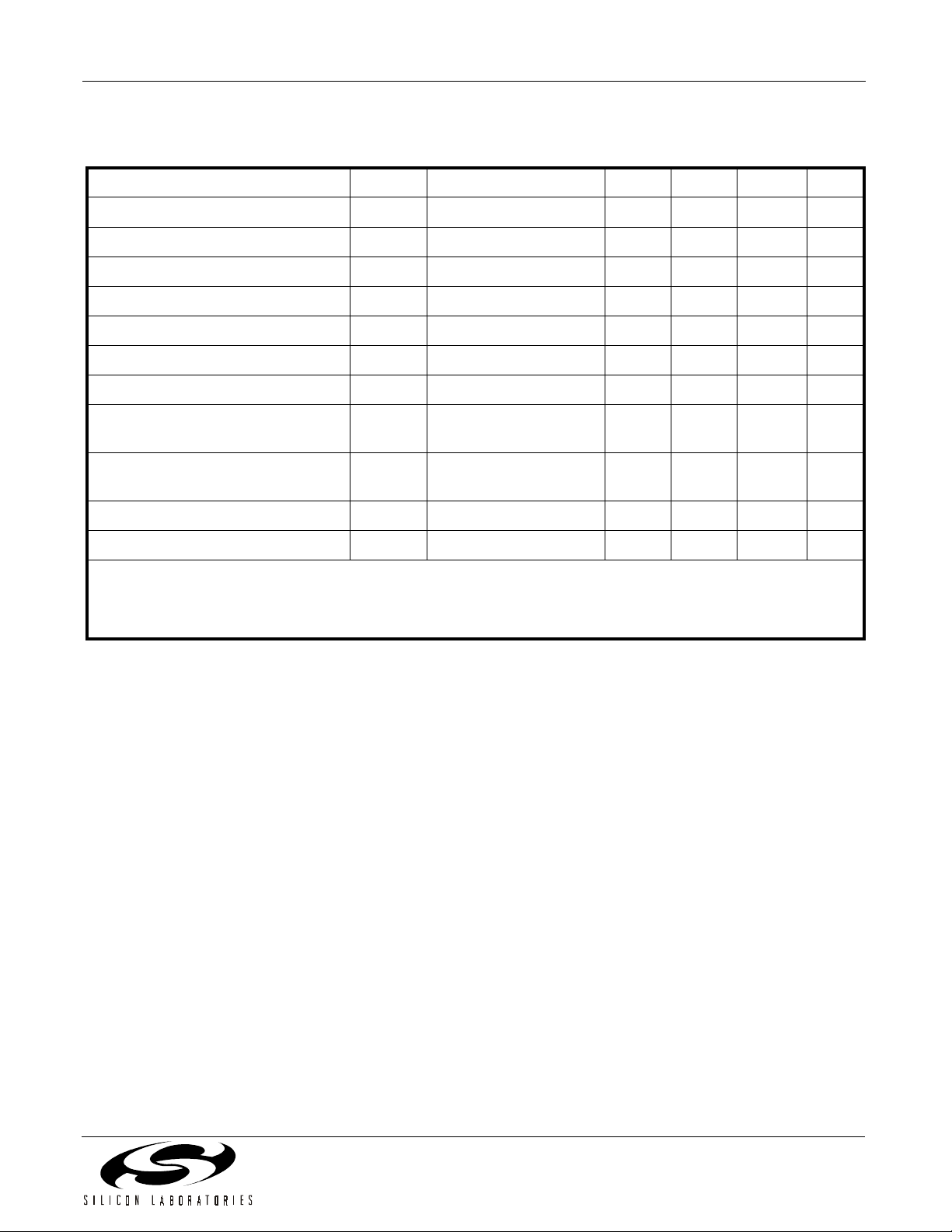

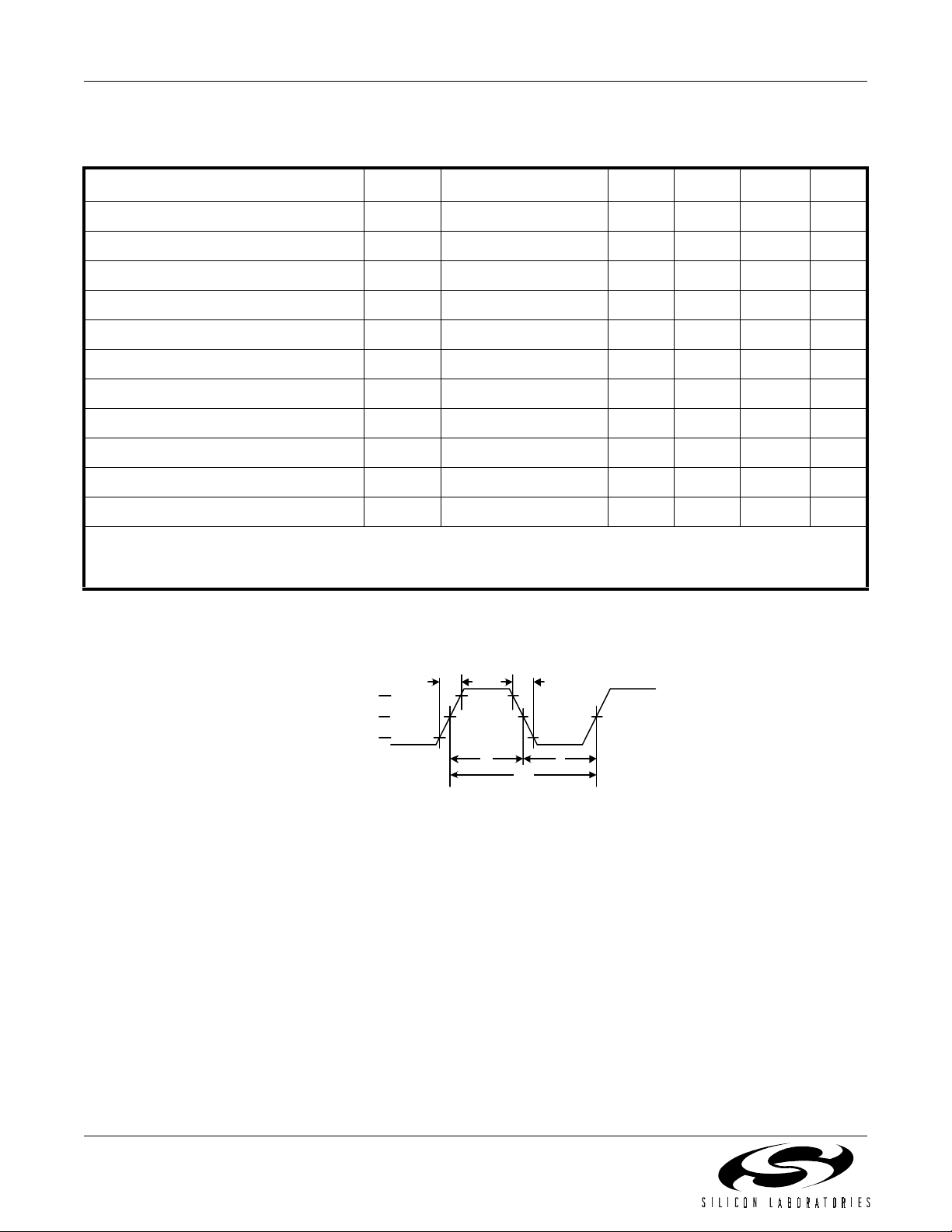

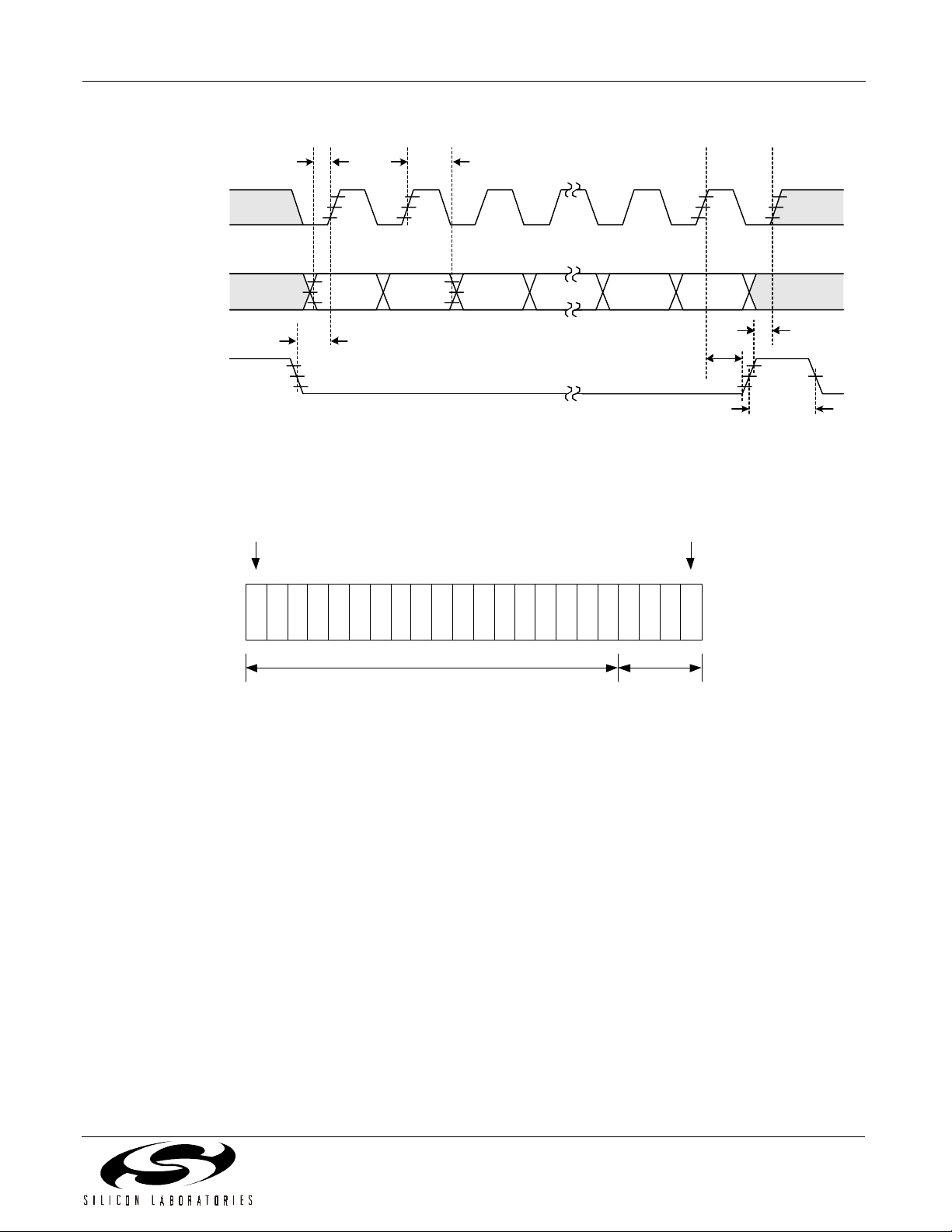

Table 4. Serial Interface Ti ming

(VDD = 2.7 to 3.6 V, TA = –40 to 85°C)

Parameter

1

SCLK Cycle Time t

SCLK Rise Time t

SCLK Fall Time t

SCLK High Time t

SCLK Low Time t

SDATA Setup Time to SCLK↑

SDATA Hold Time from SCLK↑

SENB↓ to SCLK↑ Delay Time

SCLK↑ to SENB↑ Delay Time

SENB↑ to SCLK↑ Delay Time

2

2

2

2

2

SENB Pulse Width t

Symbol Test Condition Min Typ Max Unit

Figure 1 40 — — ns

Figure 1 — — 50 ns

Figure 1 — — 50 ns

Figure 1 10 — — ns

Figure 1 10 — — ns

Figure 2 5 — — n s

Figure 2 0 — — n s

Figure 2 10 — — ns

Figure 2 12 — — ns

Figure 2 12 — — ns

Figure 2 10 — — ns

t

t

t

t

clk

t

su

hold

en1

en2

en3

w

r

f

h

l

Notes:

1. All timing is referenced to the 50% level of the waveforms unless otherwise noted.

2. Timing is not referenced to 50% level of the waveform. See Figure 2.

SCLK

80%

50%

20%

t

r

t

f

t

h

t

l

t

clk

Figure 1. SCLK Timing Diagram

6 Rev. 1.1

Si4133

SCLK

SDATA

SENB

First bit

cloc ked in

t

su

D17 D16 D15 A1 A0

t

en1

t

hold

Figure 2. Serial Interface Timing Diagram

Last bit

cloc ked in

t

en3

t

en2

t

w

D17D16D15D14D13D12D11D10D9D8D7D6D5D4D3D2D1D0A3A2A1A

data

field

address

field

Figure 3. Serial Word Format

0

Rev. 1.1 7

Si4133

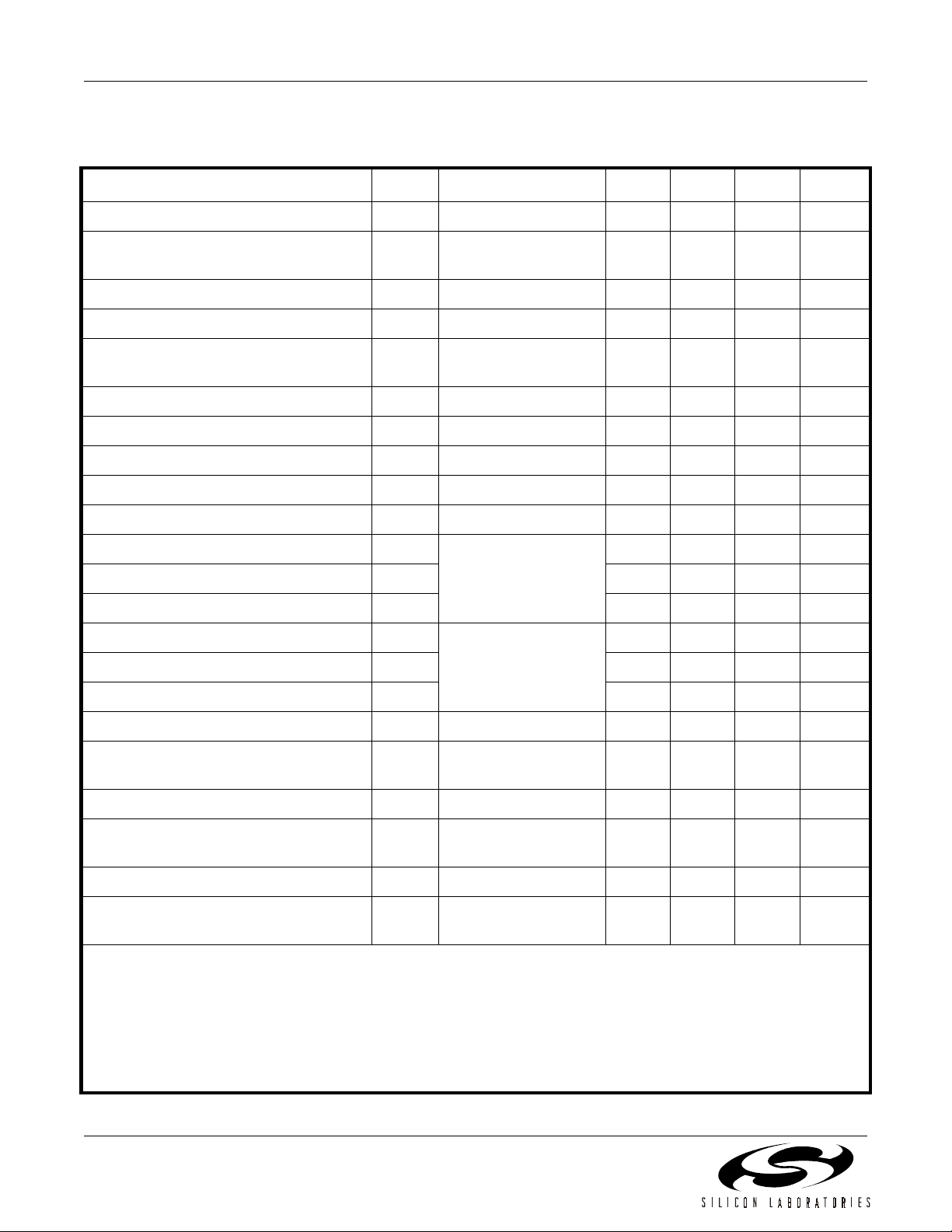

Table 5. RF and IF Synthesizer Characteristics

(VDD = 2.7 to 3.6 V, TA = –40 to 85°C)

Parameter

1

XIN Input Frequency f

Reference Amplifier Sensitivity V

Symbol Test Condition Min Typ Max Unit

REF

REF

2—26MHz

0.5 — VDD

V

P-P

+0.3 V

Phase Detector Update Frequency f

RF1 VCO Center Frequency Range f

RF1 VCO Tuning Range

2

φ

CEN

f

= f

/R 0.010 — 1.0 MHz

REF

φ

Extended frequency

947 — 1720 MHz

1850 — 2050 MHz

operation

RF2 VCO Center Frequency Range f

RF Tuning Range from f

CEN

IF VCO Center Frequency Range f

CEN

CEN

Note: L

±10% –5 — 5 %

EXT

789 — 1429 MHz

526 — 952 MHz

IFOUT Tuning Range with IFDIV 62.5 — 1000 MHz

IFOUT Tuning Range from f

CEN

Note: L

±10% –5 — 5 %

EXT

RF1 VCO Pushing Open loop — 500 — kHz/V

RF2 VCO Pushing — 400 — kHz/V

IF VCO Pushing — 300 — kHz/V

RF1 VCO Pulling VSWR = 2:1, all

RF2 VCO Pulling — 300 — kHz

phases, open loop

— 900 — MHz

IF VCO Pulling — 100 — kHz

RF1 Phase Noise 1 MHz offset — –132 — dBc/Hz

RF1 Integrated Phase Error 10 Hz to 100 kHz — 0.9 — degrees

rms

RF2 Phase Noise 1 MHz offset — –134 — dBc/Hz

RF2 Integrated Phase Error 10 Hz to 100 kHz — 0.7 — degrees

rms

IF Phase Noise 100 kHz offset — –117 — dBc/Hz

IF Integrated Phase Error 100 Hz to 100 kHz — 0.4 — degrees

rms

Notes:

= 200 kHz, RF1 = 1.6 GHz, RF2 = 1.2 GHz, IFOUT = 550 MHz, LPWR = 0, for all parameters unless otherwise noted.

1. f

φ

2. Extended frequency operation only. V

RFLB pins. See Application Note 41 for more details on the Si4133 extended frequency operation.

3. From power up request (PWDNB↑ or SENB↑ during a write of 1 to bits PDIB and PDRB in Register 2) to RF and IF

synthesizers ready (settled to within 0.1 ppm frequency error).

4. From power down request (PWDNB↓, or SENB↑ during a write of 0 to bits PDIB and PDRB in Register 2) to supply

current equal to I

PWDN

.

≥ 3.0 V, MLP only, VCO Tuning Range fixed by directly shorting the RFLA and

DD

8 Rev. 1.1

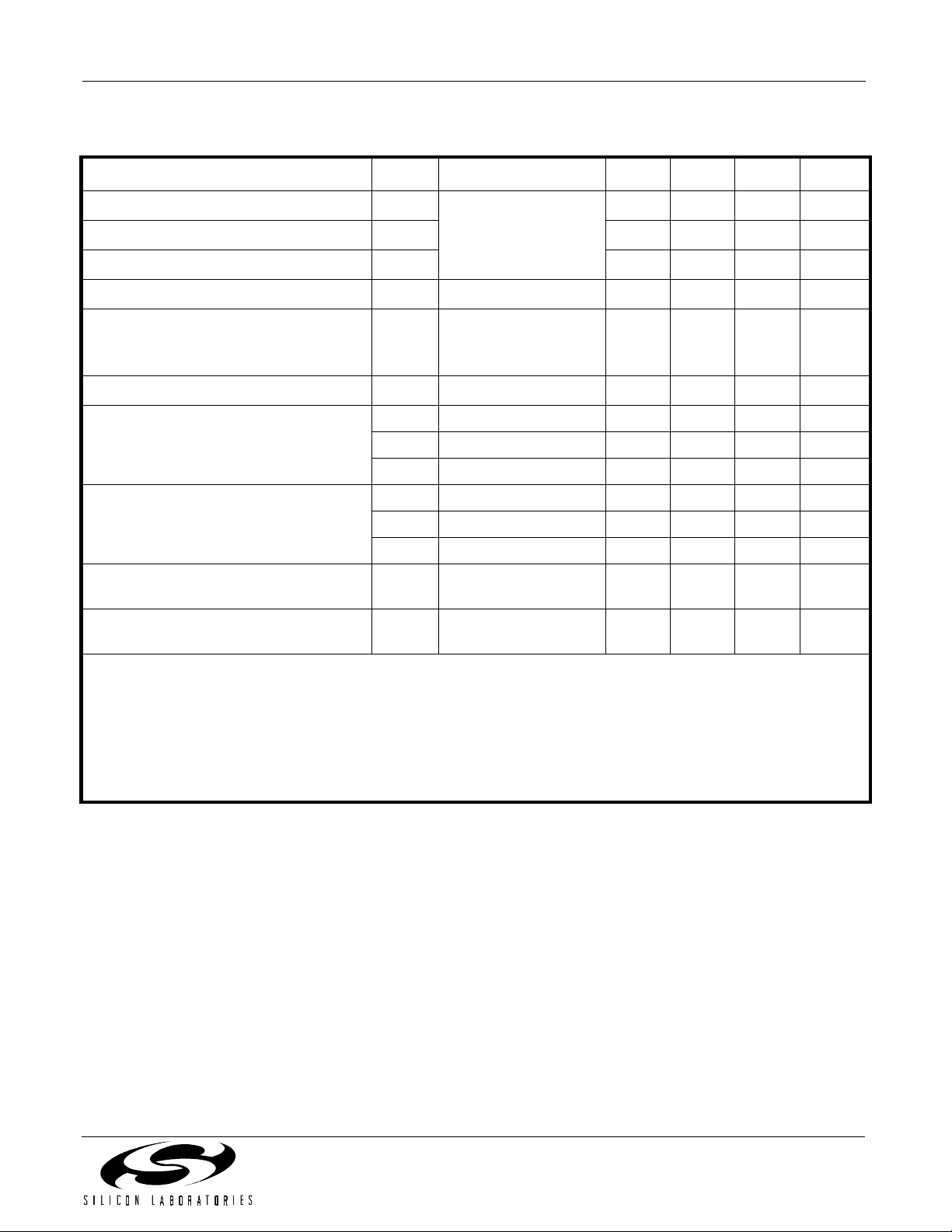

Table 5. RF and IF Synthesizer Characteristics (Continued)

(VDD = 2.7 to 3.6 V, TA = –40 to 85°C)

Si4133

Parameter

1

Symbol Test Condition Min Typ Max Unit

RF1 Harmonic Suppression Second Harmonic — –26 –20 dBc

RF2 Harmonic Suppression — –26 –20 dBc

IF Harmonic Suppression — –26 –20 dBc

RFOUT Power Level Z

RFOUT Power Level

2

ZL = 50 Ω, RF1 active,

= 50 Ω –8 –3 1 dBm

L

–14 –7 1 dBm

Extended frequency

operation

IFOUT Power Level Z

= 50 Ω –8 –4 0 dBm

L

RF1 Output Reference Spurs Offset = 200 kHz — –65 — dBc

Offset = 400 kHz — –71 — dBc

Offset = 600 kHz — –75 — dBc

RF2 Output Reference Spurs Offset = 200 kHz — –65 — dBc

Offset = 400 kHz — –71 — dBc

Offset = 600 kHz — –75 — dBc

Power Up Request to Synthesizer

3

Ready

Time

t

pup

Figures 4, 5 — 40/f

50/f

φ

φ

Power Down Request to Synthesizer

4

Off

Time

Notes:

1. f

= 200 kHz, RF1 = 1.6 GHz, RF2 = 1.2 GHz, IFOUT = 550 MHz, LPWR = 0, for all parameters unless otherwise noted.

φ

2. Extended frequency operation only. V

RFLB pins. See Application Note 41 for more details on the Si4133 extended frequency operation.

3. From power up request (PWDNB↑ or SENB↑ during a write of 1 to bits PDIB and PDRB in Register 2) to RF and IF

synthesizers ready (settled to within 0.1 ppm frequency error).

4. From power down request (PWDNB↓, or SENB↑ during a write of 0 to bits PDIB and PDRB in Register 2) to supply

current equal to I

PWDN

.

t

pdn

≥ 3.0 V, MLP only, VCO Tuning Range fixed by directly shorting the RFLA and

DD

Figures 4, 5 — — 100 ns

Rev. 1.1 9

Si4133

RF and IF synthes iz er s settled to

w ithi n 0.1 ppm frequency error.

t

pup

I

PWD N

I

T

SENB

SDATA

PDIB = 1

PDRB = 1

PDIB = 0

PDRB = 0

Figure 4. Software Power Management

Timing Diagram

RF and IF synthes ize r s settled to

w ithi n 0.1 ppm frequency error.

t

pdn

I

PWD N

I

T

t

pup

t

pdn

PWDNB

Figure 5. Hardware Power Management

Timing Diagram

10 Rev. 1.1

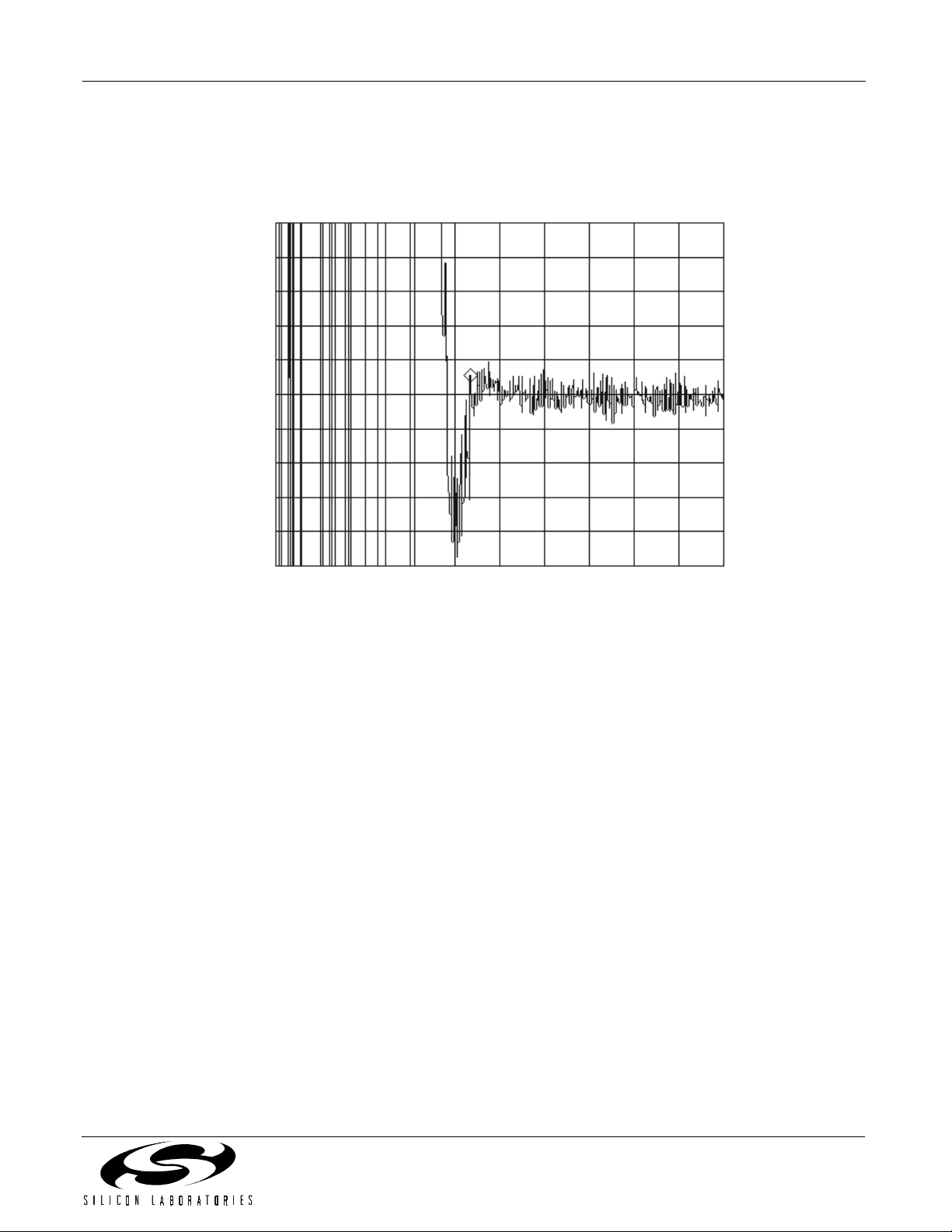

TRACE A: Ch1 FM Main Time

A Marker 174.04471

1.424

kHz

Real

160

Hz

/div

us

Si4133

711.00 Hz

176

Hz

Start: 0 s

Stop: 399.6003996 us

Figure 6. Typical Transient Response RF1 at 1.6 GHz

with 200 kHz Phase Detector Update Frequency

Rev. 1.1 11

Loading...

Loading...