Si3036

FCC/JATE MC’97 S

ILICON

DAA

Features

Complete DAA includes the following:

!

AC’97 2.1 Compliant

!

Primary or Secondary Codec

!

Phone Line Interface Compliant

with FCC Part 68 and JATE

!

86 dB Dynamic Range TX/RX

Paths

!

3.3 or 5 V Power Supply

!

3000 V Isolation

!

Integrated Ring Detector

!

Wake-Up on Ring

!

Caller ID Support

!

Integrated Analog Front End

!

2- to 4-Wire Hybrid

!

Low-Power Standby Mode

!

Low Profile SOIC Packages

!

Patented ISOcap™ Technology

Applications

!

Software Modems

!

Audio/Telephony Sub-Systems

!

Audio/Modem Riser Cards (AMR)

!

Mobile Daughter Cards (MDC)

!

Mini-PCI Cards

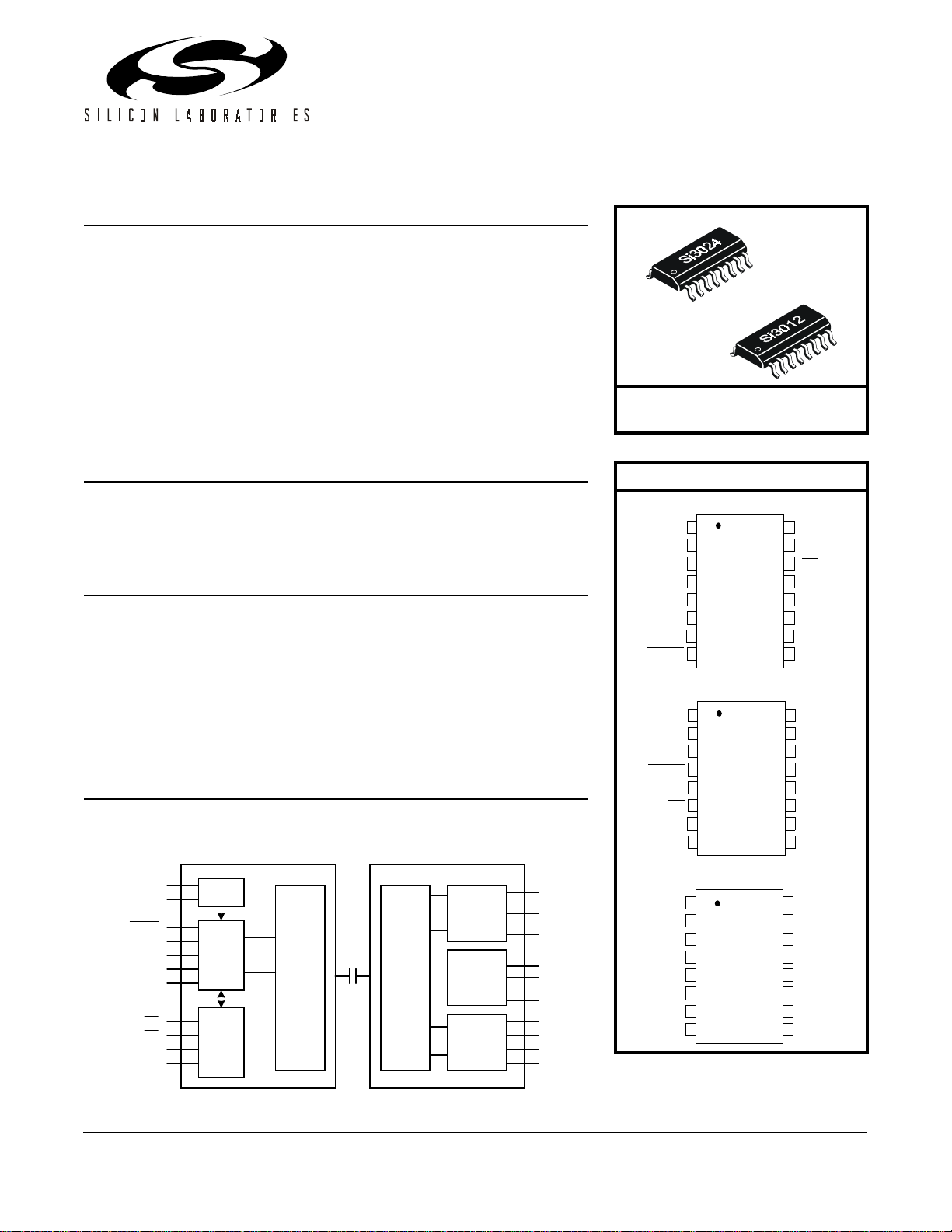

Description

The Si3036 is an integrated direct access arrangement (DAA) chipset that

provides a digital, pr ogrammable interface to a telephone line. Availabl e

in two 16-pin small outline packages (AC’97 interface on Si3024 and

phone-line interface on Si3012), the chipset eliminates the need for an

analog front end (AFE), an isolation transformer, relays, opto-isolators,

and a 2- to 4-wire hybrid. The Si3036 dramatically reduces the number of

discrete components and cost required to achieve compliance with FCC

Part 68 and JATE. The Si3024 complies with the AC’97 2.1 specification.

Functional Block Diagram

Si3024 Si3012

Ordering Information

See page 50.

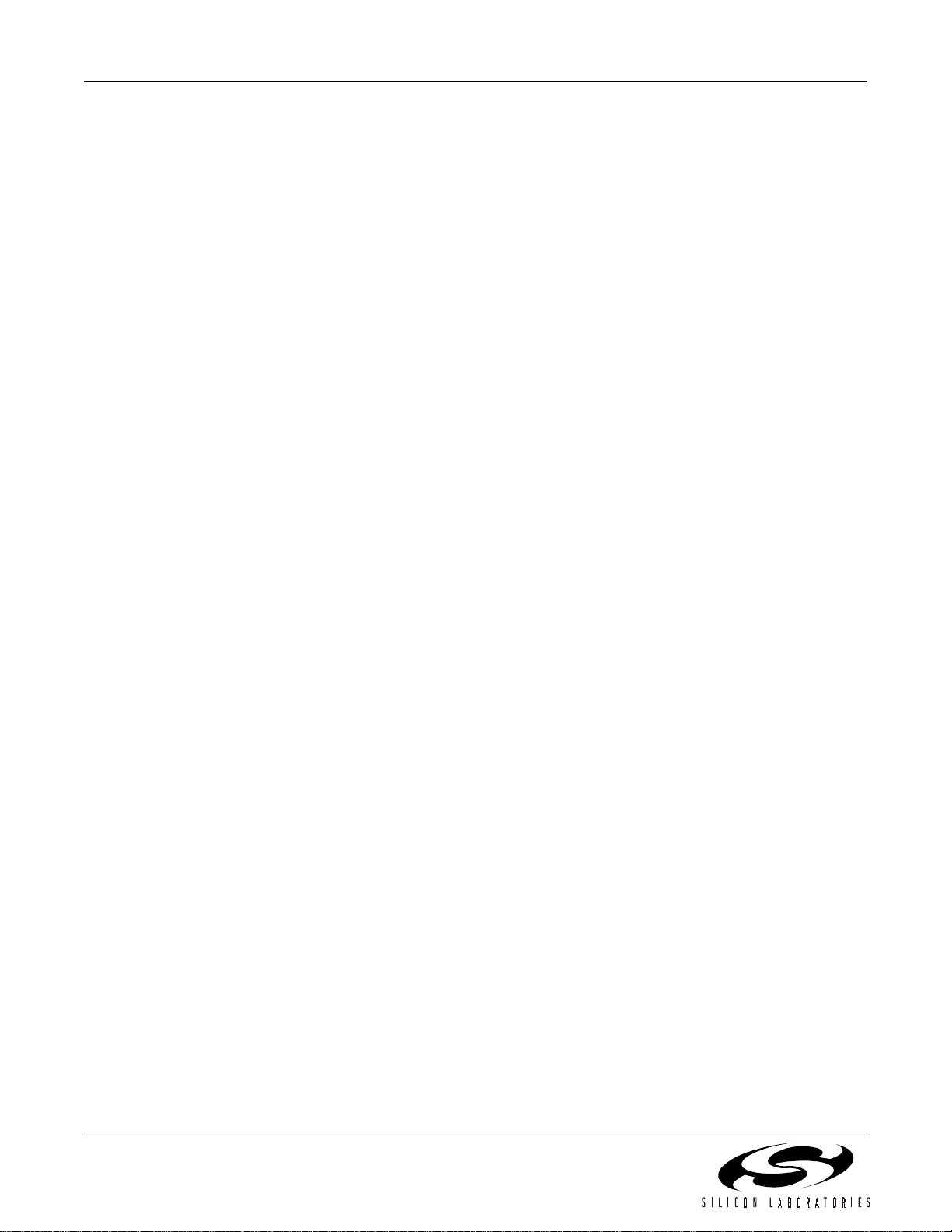

Pin Assignments

Si3024 (SOIC)

MCLK/XIN

XOUT

BIT_CLK

SDATA_IN

SDATA_OUT

SYNC

RESET

SDATA_IN

SDATA_OUT

SYNC

RESET

AOUT

1

2

3

4

V

D

5

6

7

8

Si3024 (TSSOP)

1

2

3

4

5

6

ID0

7

C1A

8

GND

16

15

14

13

12

11

10

16

15

14

13

12

11

10

9

9

GPIO_A

GPIO_B

ID1

V

A

GND

C1A

ID0

AOUT

V

D

BIT_CLK

XOUT

MCLK/XIN

GPIO_A

GPIO_B

ID1

V

A

XOUT

MCL K /X IN

RESET

BIT_CLK

SYNC

SDATA_IN

SDATA_OUT

IDO

ID1

GPIO_A

GPIO_B

Clock

AC'97

Digital

Interfa ce

Control

Interfa ce

Isolation

Interfa ce

Isolation

Interfa ce

Hybrid

DC

Termination

Ring Detect

Off-Hook

Out

TX

In

RX

HYBD

VREG2

VREG

DCT

REXT

IGND

RNG1

RNG2

QB

QE

Si3012 (SOIC or TSSOP)

TSTA

TSTB

IGND

RNG1

RNG2

C1B

QB

QE

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

TX

NC

RX

REXT

DCT

HYBD

VREG2

VREG

US Patent # 5,870,046

US Patent # 6,061,009

Other Patents Pending

Rev. 1.2 12/00 Copyright © 2000 by Silicon Laboratories Si3036-DS12

Si3036

2 Rev. 1.2

Si3036

T

ABLE OF

C

ONTENTS

Section Page

Electrical Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

Typical Application Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Si3036 Schematic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Bill of Materials . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Analog Output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

AC-Link . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

JATE Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Isolation Barrier . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Off-Hook . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Ring Detect . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Wake-Up on Ring . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Pulse Dialing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

On-Hook Line Monitor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Caller ID . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Loop Current Monitor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Analog Output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Gain Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Filter Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

In-Circuit Testing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Lightning Test . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Safety and Isolation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Digital Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Si3024 as Secondary Device . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Si3024 as Primary MC’97 Codec . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Si3024 Connection to the Digital AC’97 controller . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Clocking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Resetting Si3036 Chipset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

AC-Link Digital Serial Interface Protocol . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Codec Register Access . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

AC-Link Low Power Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Appendix—UL1950 3rd Edition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Pin Descriptions: Si3024 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Pin Descriptions: Si3012 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Ordering Guide . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

SOIC Outline . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

TSSOP Outline . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Contact Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

Rev. 1.2 3

Si3036

Electrical Specifications

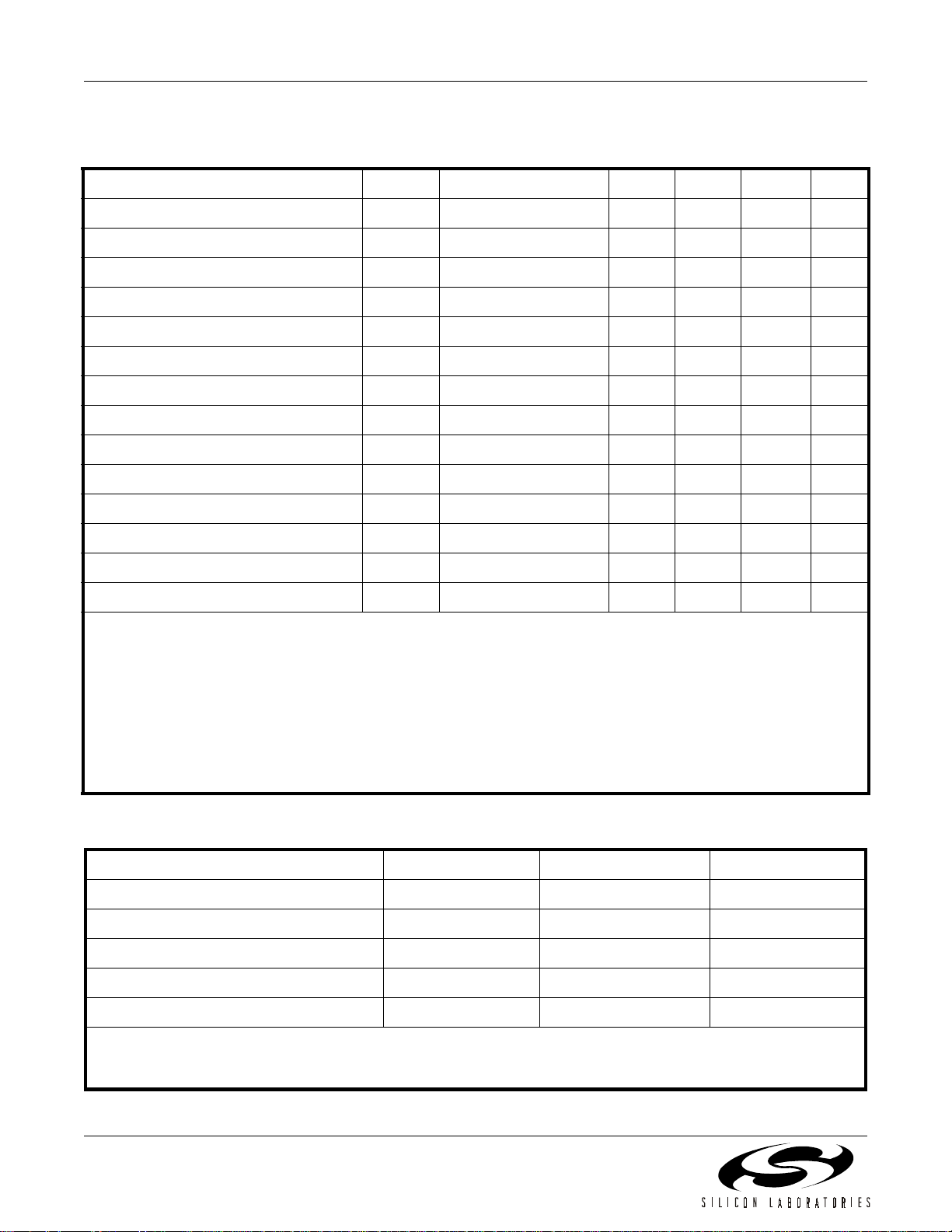

Table 1: Recommended Operating Conditions

Parameter

Ambient Temperature

1

3

Si3024 Supply Voltage, Analog V

Si3024 Supply Voltage, Digital

Si3024 Supply Voltage, Digital

Notes:

1.

The Si3036 specifications are guaranteed when the typical application circuit (including component tolerances) of

Figure 19 and any Si3024 and Si3012 are used.

2. All minimum and maximum specifications are guaranteed and apply across the recommended operating conditions.

Typical values apply at nominal supply voltages and an operating temperature of 25°C unless otherwise stated.

3.

The temperature specifications are guaranteed when using the typical application circuit on a 4 sq. in. minimum FR4

PCB. For other materials and smaller form factors, heat dissipation factors may apply. Contact Silicon Laboratories for

more details.

4.

The digital supply, V

operating from 3.3 V. 3.3 V operation applies to both the AC’97 Digital Interface and the digital signals RESET

and ID1

.

4

4

can operate from either 3.3 V or 5.0 V. The Si3024 supports interface to 3.3V logic when

D,

Symbol Test Condition

T

A

A

V

D

V

D

K-Grade 0 25 70 °C

VA = 5 V 4.75 5.0 5.25 V

VA = Charge Pump 3.0 3.3 3.6 V

Min

2

Typ

Max

2

Unit

4.75 5.0 5.25 V

, ID0,

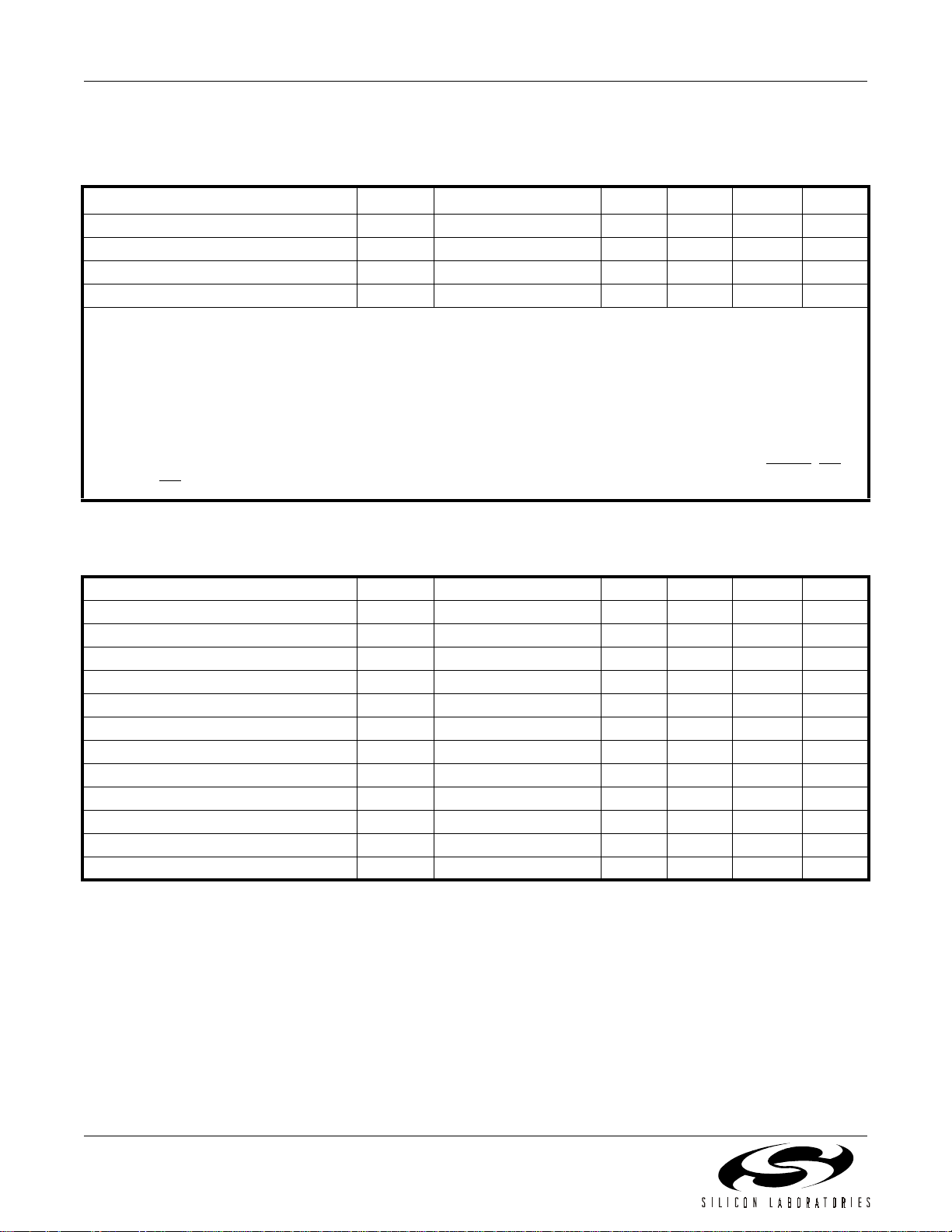

Table 2: Loop Characteristics

(VD = 3.0 to 3.6 V, VA = Charge Pump, TA = 0 to 70°C, See Figure 1)

Parameter Symbol Test Condition Min Typ Max Unit

DC Termination Voltage V

DC Termination Voltage V

DC Ring Current I

DC Ring Current I

AC Termination Impedance Z

Operating Loop Current I

TR

TR

RDC

RDC

ACT

LP

Loop Current Sense Bits LCS LCS = Fh 180 155 — mA

Ring Detect Voltage V

Ring Frequency F

On-hook Leakage Current I

RD

R

LK

Ringer Equivalence Number REN w/ Caller ID — 1.0 1.67

Ringer Equivalence Number REN w/o Caller ID — 0.2 —

IL = 20 mA — — 7.7 V

IL = 105 mA 12 — — V

w/ Caller ID — — 1 mA

w/o Caller ID — — 20 µA

—600— Ω

20 — 120 mA

13 18 26 V

RMS

15 — 68 Hz

VTR = –48 V — — 1 µA

4 Rev. 1.2

TIP

+

Si3012 V

TR

600

10 µF

Si3036

Ω

I

L

RING

Note: The remainder of the circuit is identical to the one shown in Figure 19 on page 15.

–

Figure 1. Test Circuit for Loop Characteristics

Table 3: DC Characteristics, V

(VA = 4.75 to 5.25 V, VD = 4.75 to 5.25 V, TA = 0°C to 70°C)

Parameter Symbol Test Condition Min Typ Max Unit

High Level Input Voltage V

Low Level Input Voltage V

High Level Output Voltage V

Low Level Output Voltage V

Input Leakage Current I

Power Supply Current, Analog I

Power Supply Current, Digital I

Total Supply Current, Sleep Mode I

= + 5 V

D

A

IH

IL

OH

OL

L

A

D

+ I

3.5 — — V

——0.8V

IO = –2 mA 2.4 — — V

IO = 2 mA — — 0.4 V

–10 — 10 µA

VA pin — 0.1 2 mA

VD pin — 14 17 mA

D

——1.5mA

Table 4: DC Characteristics, VD = + 3.3 V

(VD = 3.0 to 3.6 V, VA = Charge Pump, TA = 0 to 70°C)

Parameter Symbol Test Condition Min Typ Max Unit

High Level Input Voltage V

Low Level Input Voltage V

High Level Output Voltage V

Low Level Output Voltage V

Input Leakage Current I

Power Supply Current, Digital I

Total Supply Current, Sleep Mode I

A

IH

IL

OH

OL

L

D

+ I

IO = –2 mA 2.4 — — V

IO = 2 mA — — 0.35 V

VD pin — 12 14.5 mA

D

Rev. 1.2 5

2.4 — — V

——0.8V

–10 — 10 µA

—1.53.0mA

Si3036

Table 5: AC Characteristics

(VD = 3.0 to 5.25 V, VA = Charge Pump, TA = 0 to 70°C)

Parameter Symbol Test Condition Min Typ Max Unit

Freq Response, Transmit

Transmit Full Scale Level

Freq Response, Receive

Receive Full Scale Level

Dynamic Range

Dynamic Range

4

5

Total Harmonic Distortion

1

2

(0 dB gain) V

1

2,3

(0 dB gain) V

6

F

RT

TX

F

RR

RX

Low –3 dB corner — 16 — Hz

—0.98—V

PEAK

Low –3 dB corner — 16 — Hz

—0.98—V

PEAK

DR VIN = 1 kHz, –3 dBFS 80 86 — dB

DR VIN = 1 kHz, –3 dBFS — 84 — dB

THD VIN = 1 kHz, –3 dBFS — –84 — dB

Dynamic Range (call progress AOUT) DR

THD (call progress AOUT) THD

AO

AO

AOUT Full Scale Level — 0.75V

VIN = 1 kHz 60 — — dB

VIN = 1 kHz — 1.0 — %

—V

A

PP

AOUT Output Impedance — 10 — kΩ

Mute Level (call progress AOUT) –90 — — dBFS

Dynamic Range (Caller ID mode) DR

2

Caller ID Full Scale Level (0 dB gain)

Notes:

1. These characteristics are determined by external components. See Figure 19 on page 15.

2. Parameter measured at TIP and RING of Figure 19 on page 15.

3.

Receive Full Scale Level will produce –0.9 dBFS at SDATA_IN.

4. DR = 3 dB + 20log (RMS signal/RMS noise). Applies to both transmit and receive paths. Measurement bandwidth is

300 to 3400 Hz. Sample rate = 9.6 kHz, loop current = 40 mA.

5. DR = 3 dB + 20log (RMS signal/RMS noise). Applies to both tran smit and rece ive path s. Mea surem ent band widt h is 15

to 3400 Hz. Sample rate = 9.6 kHz, loop current = 40mA.

6.

THD = 20log (RMS distortion/RMS signal). This applies to both the transmit and receive paths.

Sample rate = 9.6 kHz, loop current = 40 mA.

V

CID

VIN = 1 kHz, –13 dBFS — 60 — dB

CID

—0.8—V

PEAK

Table 6: Absolute Maximum Ratings

Parameter Symbol Value Unit

DC Supply Voltage V

Input Current, Si3024 Digital Input Pins I

Digital Input Voltage V

Operating Temperature Range T

Storage Temperature Range T

Note: Permanent device damage may occur if the above Absolute Maximum Ratings are exceeded. Functional operation

should be restricted to the conditions as specified in the operational sections of this data sheet. Exposure to absolute

maximum rating conditions for extended periods may affect device reliability.

6 Rev. 1.2

D

IND

STG

, V

IN

A

A

–0.5 to 6.0 V

± 10 mA

–0.3 to (VD + 0.3) V

–40 to 100 °C

–65 to 150 °C

Si3036

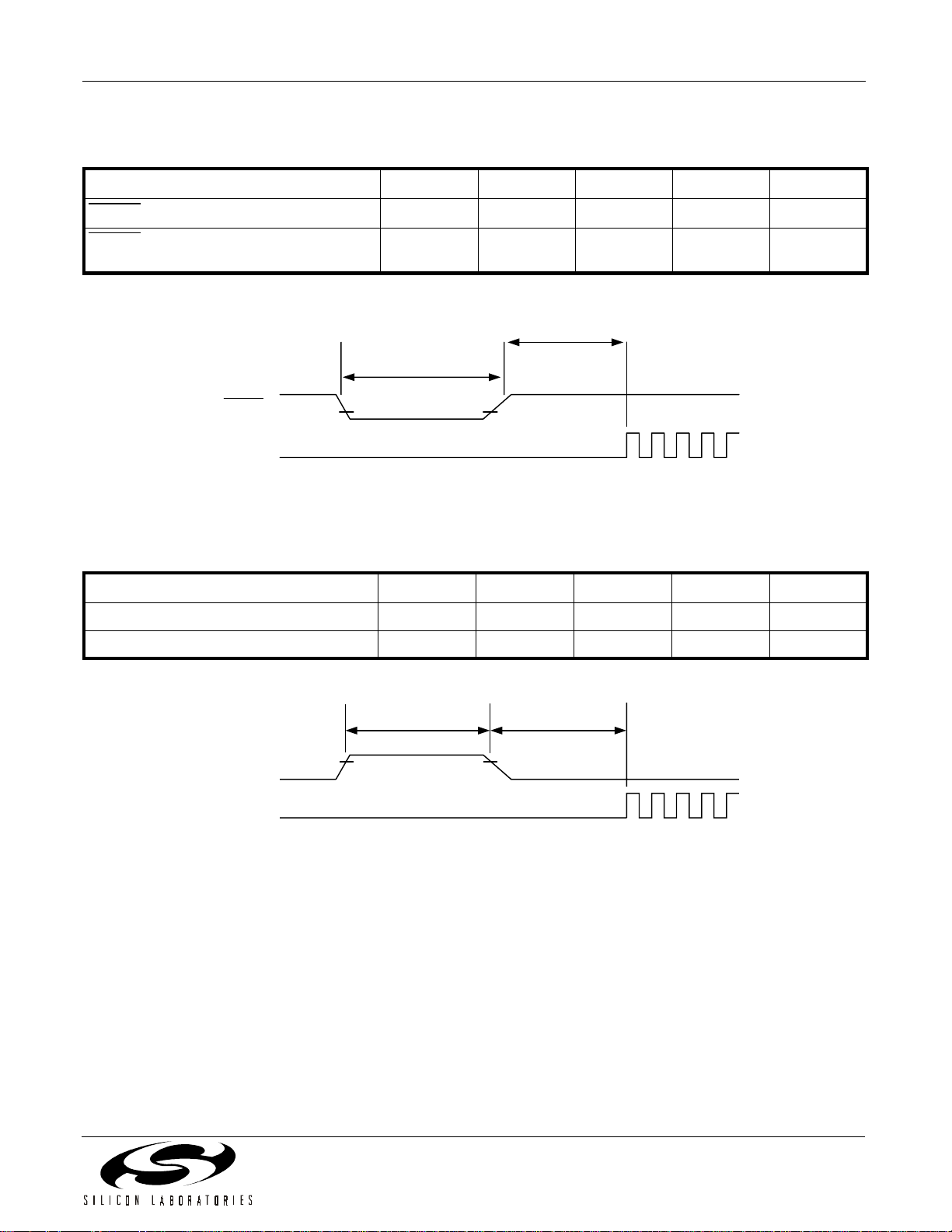

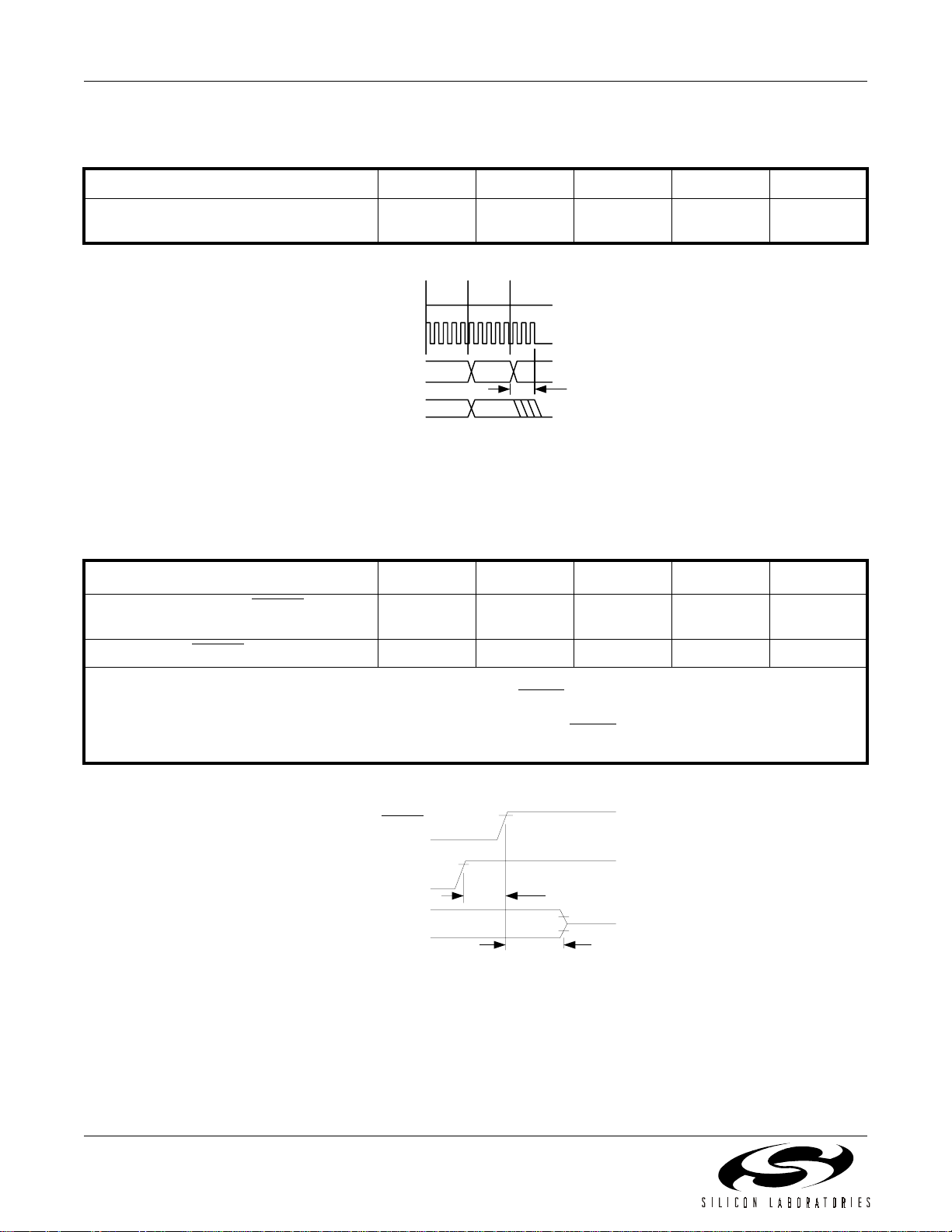

Table 7: AC Link Timing Characteristics—Cold Reset

(VD = 3.0 to 3.6 V, VA = Charge Pump, TA = 25°C, CL = 50 pF)

Parameter Symbol Min Typ Max Unit

RESET

RESET

Active Low Pulse Width T

Inactive to BIT_CLK Startup

rst_low

T

rst2clk

1.0 — — µs

162.8 — — ns

Delay

T

rst2clk

T

rst_low

RESET

BIT_CLK

Figure 2. Cold Reset Timing Diagram

Table 8. AC Link Timing Characteristics—Warm Reset

(VD = 3.0 to 3.6 V, VA = Charge Pump, TA = 25°C, CL = 50 pF)

Parameter Symbol Min Typ Max Unit

SYNC Active High Pulse Width T

SYNC Inactive to BIT_CLK Startup Delay T

sync_high

sync2clk

1.0 — — µs

162.8 — — ns

SYNC

BIT_CLK

T

sync_high

T

sync2clk

Figure 3. Warm Reset Timing Diagram

Rev. 1.2 7

Si3036

Table 9. AC Link Timing Characteristics—Clocks

(VD = 3.0 to 3.6 V, VA = Charge Pump, TA = 25°C, CL = 50 pF)

Parameter Symbol Min Typ Max Unit

BIT_CLK Frequency — 12.288 — MHz

BIT_CLK Period T

clk_period

— 81.4 — ns

BIT_CLK Output Jitter — — 750 ps

BIT_CLK High Pulse Width* T

BIT_CLK low Pulse Width* T

clk_high

clk_low

36 40.7 45 ns

36 40.7 45 ns

SYNC Frequency — 48.0 — kHz

SYNC Period T

SYNC High Pulse Width T

SYNC Low Pulse Width T

*Note: Worst case duty cycle rest ricted to 45/55.

BIT_CLK

sync_period

sync_high

sync_low

— 20.8 — µs

—1.3—µs

— 19.5 — µs

T

clk_low

T

clk_high

T

clk_period

T

sync_low

SYNC

T

sync_high

T

Figure 4. Clocks Timing Diagram

8 Rev. 1.2

sync_period

Si3036

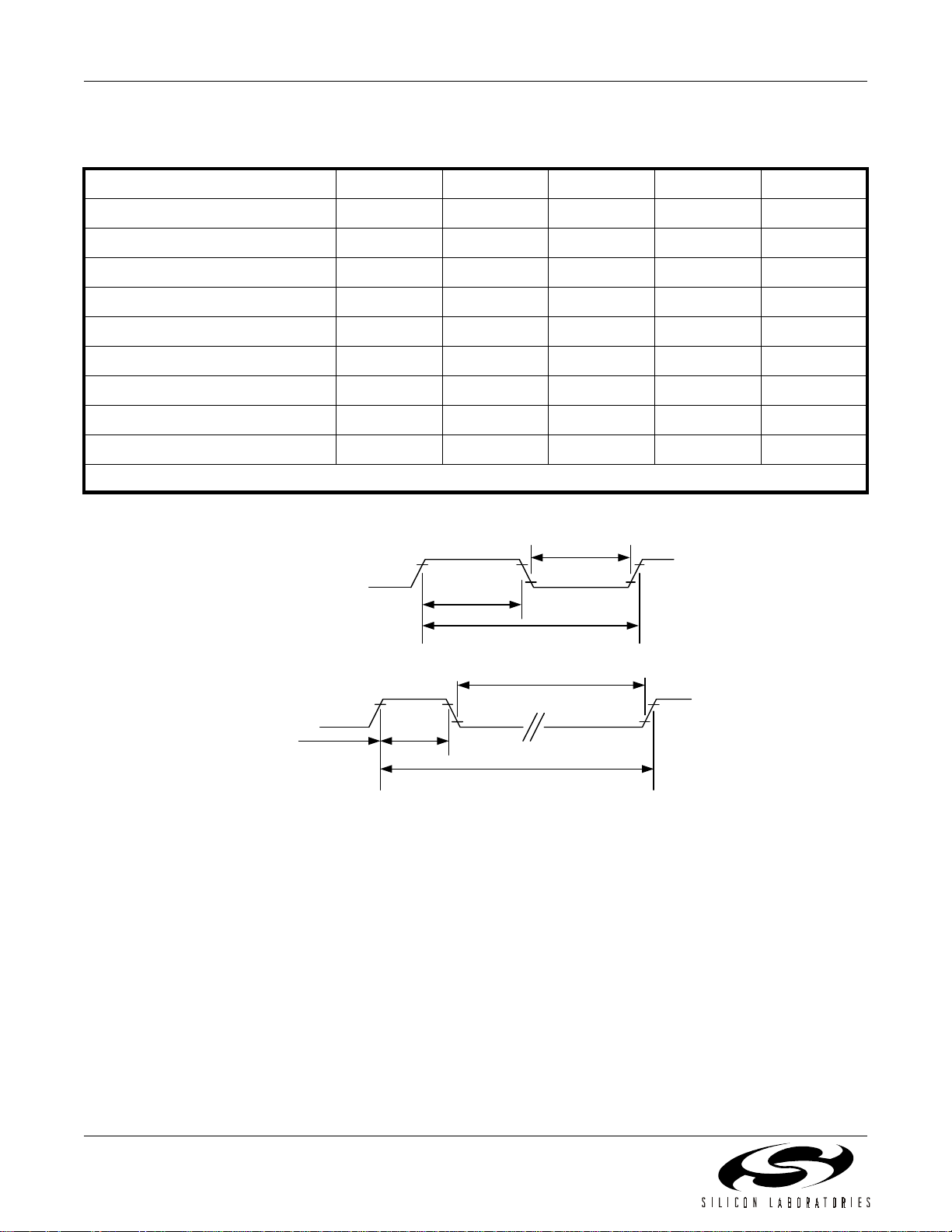

Table 10. AC Link Timing Characteristics—Data Se tup and Hold

(VD = 3.0 to 3.6 V, VA = Charge Pump, TA = 25°C, CL = 50 pF)

Parameter Symbol Min Typ Max Unit

Setup to Falling Edge of BIT_CLK T

Hold from Falling Edge of BIT_CLK T

T

setup

BIT_CLK

SYNC

SDATA_OUT

SDATA_IN

T

hold

setup

hold

15.0 — — ns

5.0 — — ns

Figure 5. Data Setup and Hold Timing Diagram

Table 11. AC Link Rise and Fall Times

(VD = 3.0 to 3.6 V, VA = Charge Pump, TA = 25°C, CL = 50 pF)

Parameter Symbol Min Typ Max Unit

BIT_CLK Rise Time Trise

BIT_CLK Fall Time Tfall

SYNC Rise Time Trise

SYNC Fall Time Tfall

SDATA_IN Rise Time Trise

SDATA_IN Fall Time Tfall

SDATA_OUT Rise Time Trise

SDATA_OUT Fall Time Tfall

clk

clk

sync

sync

din

din

dout

dout

2—6ns

2—6ns

2—6ns

2—6ns

2—6ns

2—6ns

2—6ns

2—6ns

BIT_CLK

SYNC

Trise

Trise

clk

sync

SDATA_IN

Tfall

Tfall

clk

SDATA_OUT

sync

Trise

Trise

din

dout

Figure 6. Signal Rise and Fall Timing Diagram

Rev. 1.2 9

Tfall

Tfall

din

dout

Si3036

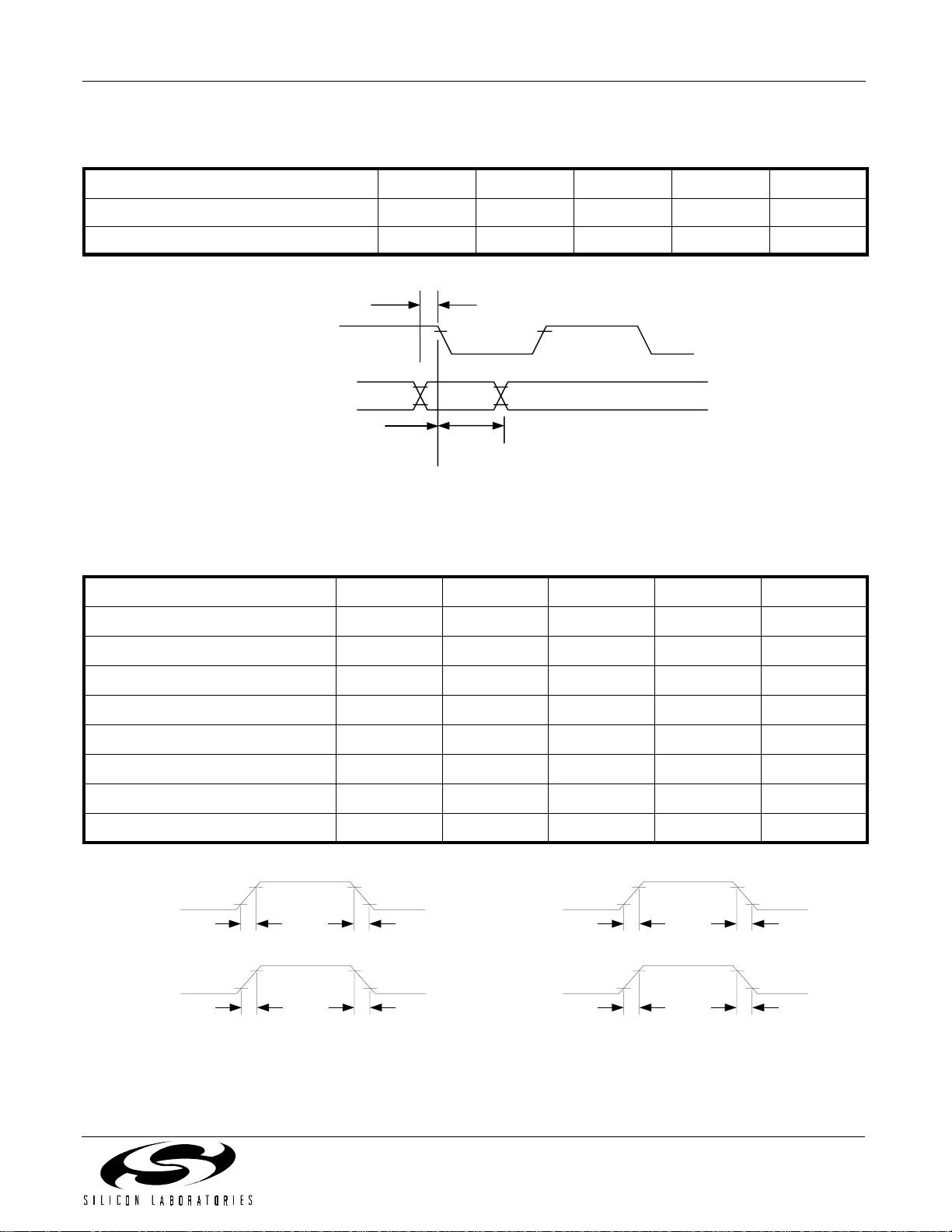

Table 12. AC Link Timing Characteristics— Low Power Mode Timing

(VD = 3.0 to 3.6 V, VA = Charge Pump, TA = 25°C, CL = 50 pF)

Parameter Symbol Min Typ Max Unit

End of Slot 2 to BIT_CLK, SDATA_IN

T

s2_pdown

——1.0µs

Low

SYNC

BIT_CLK

DATA_OUT

SDATA_IN

Slot 1 Slot 2

Write to

Note: B IT_C LK n o t to s c a le

0x56

Data

MLNK

Don't care

Figure 7. AC-Link Low Power Mode Timing Diagram

Table 13. ATE Test Mode

(VD = 3.0 to 3.6 V, VA = Charge Pump, TA = 25°C, CL = 50 pF)

Parameter

Setup to falling edge of RESET

1,2

(also

applies to SYNC)

Rising edge of RESET

Notes:

1. All AC link signals are normal ly low th rough the tra iling edge of RESET

of RESET causes AC’97 AC-link outputs to go high impedance, which is suitable for ATE in circuit testing.

2. When the test mode has been entered, AC’97 must be issued another RESET

the normal operating mode.

to Hi-Z delay T

Symbol Min Typ Max Unit

T

setup2rst

off

15.0 — — ns

— — 25.0 ns

T

s2_pdown

. Bringing SDA TA_OUT high for the trailing edge

with all AC-link signals low to return to

RESET

SDATA_OUT

SDATA_IN, BIT_CLK

T

off

Figure 8. ATE Test Mode Timing Diagram

10 Rev. 1.2

T

setup2rst

Hi-Z

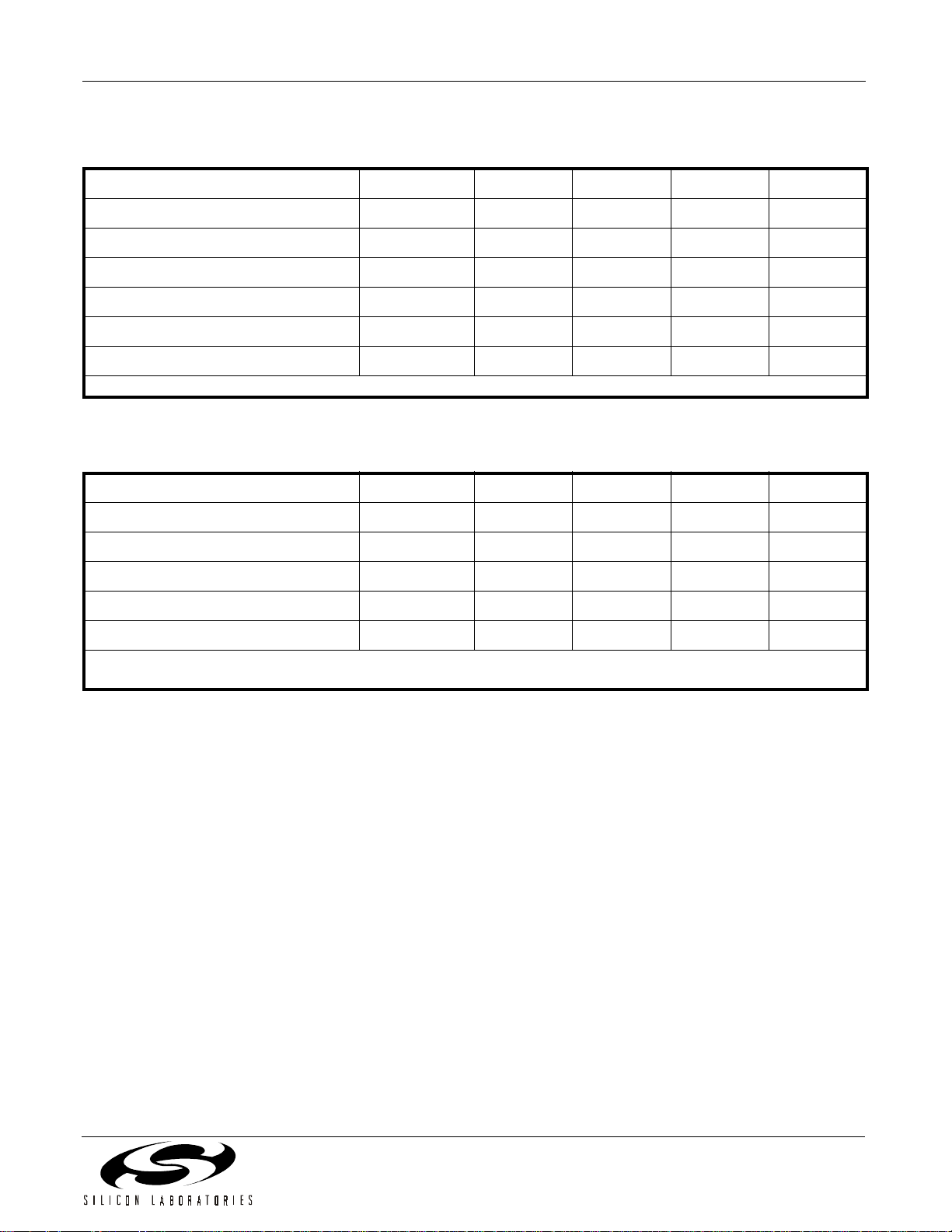

Table 14: Digital FIR Filter Characteristics—Transmit and Receive

(VD = 3.0 to 3.6 V, VA = Charge Pump, Sample Rate = 8 kHz, TA = 70°C)

Parameter Symbol Min Typ Max Unit

Si3036

Passband (0.1 dB) F

Passband (3 dB) F

(0.1 dB)

(3 dB)

0—3.3kHz

0—3.6kHz

Passband Ripple Peak-to-Peak –0.1 — 0.1 dB

Stopband — 4.4 — kHz

Stopband Attenuation –74 — — dB

Group Delay t

Note: Typical FIR filter characteristics for Fs = 8000Hz are shown in Figures 9, 10, 11, and 12.

gd

— 12/Fs — sec

Table 15: Digital IIR Filter Characteri stics—Transmit and Receive

(VD = 3.0 to 3.6 V, VA = Charge Pump, Sample Rate = 8 kHz, TA = 70°C)

Parameter Symbol Min Typ Max Unit

Passband (3 dB) F

(3 dB)

Passband Ripple Peak-to-Peak –0.2 — 0.2 dB

Stopband — 4.4 — kHz

Stopband Attenuation –40 — — dB

Group Delay t

Note:

Typical IIR filter characteristics for Fs = 8000 Hz are shown in Figures 13, 14, 15, and 16. Figures 17 and 18 show

group delay versus input frequency.

gd

0—3.6kHz

— 1.6/Fs — sec

Rev. 1.2 11

Si3036

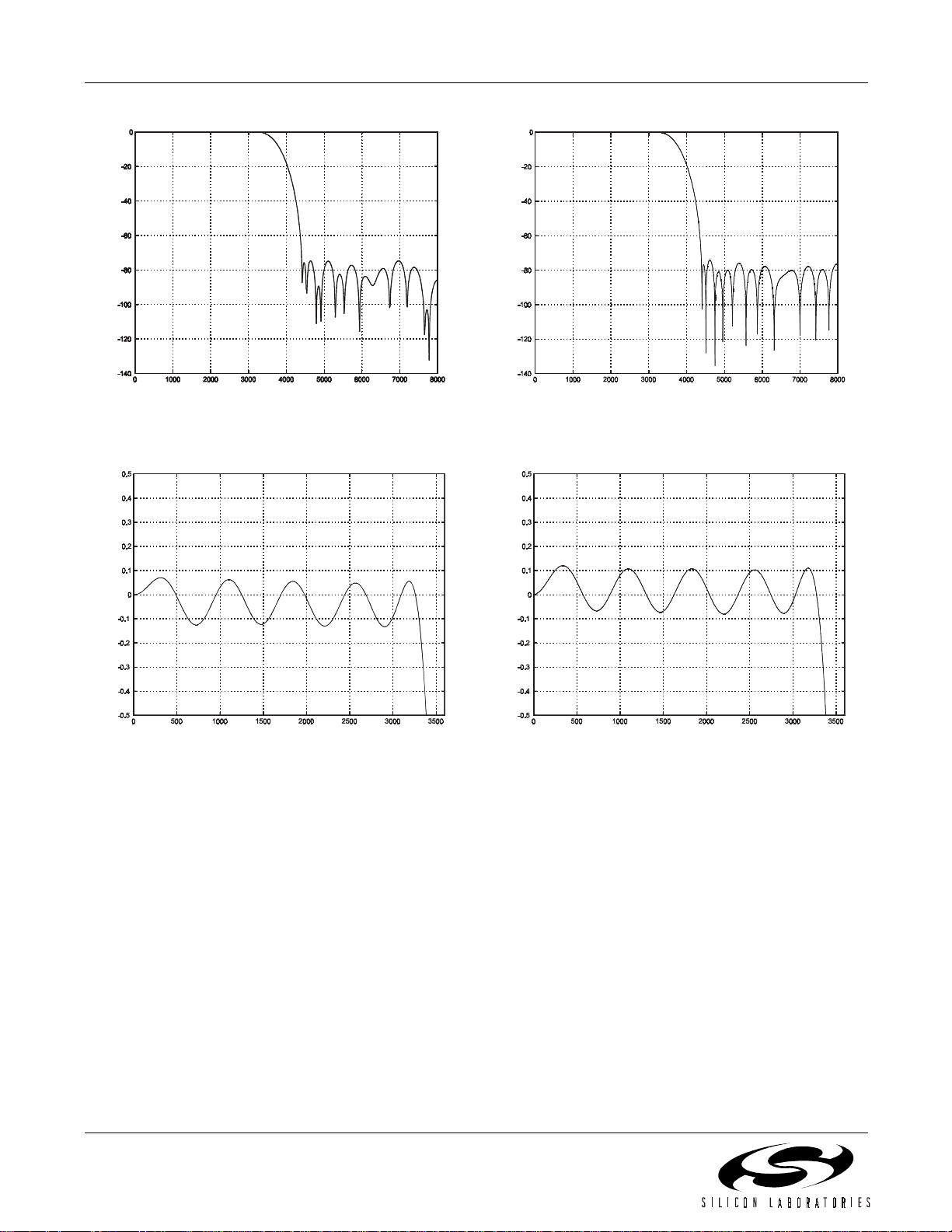

Attenuation—dB

Input Frequency—Hz

Figure 9. FIR Receive Filter Response

Attenuation—dB

Input Frequency—Hz

Figure 10. FIR Receive Filter Passband Ripple

Attenuation—dB

Input Frequency—Hz

Figure 11. FIR Transmit Filter Response

Attenuation—dB

Input Frequency—Hz

Figure 12. FIR Transmit Filter Passband Ripple

For Figures 9–12, all filter plots apply to a sample rate of

Fs = 8 kHz. The filters scale with the sample rate as follows:

F

where Fs is the sample frequency.

12 Rev. 1.2

(0.1 dB)

F

(–3 dB)

= 0.4125 Fs

= 0.45 Fs

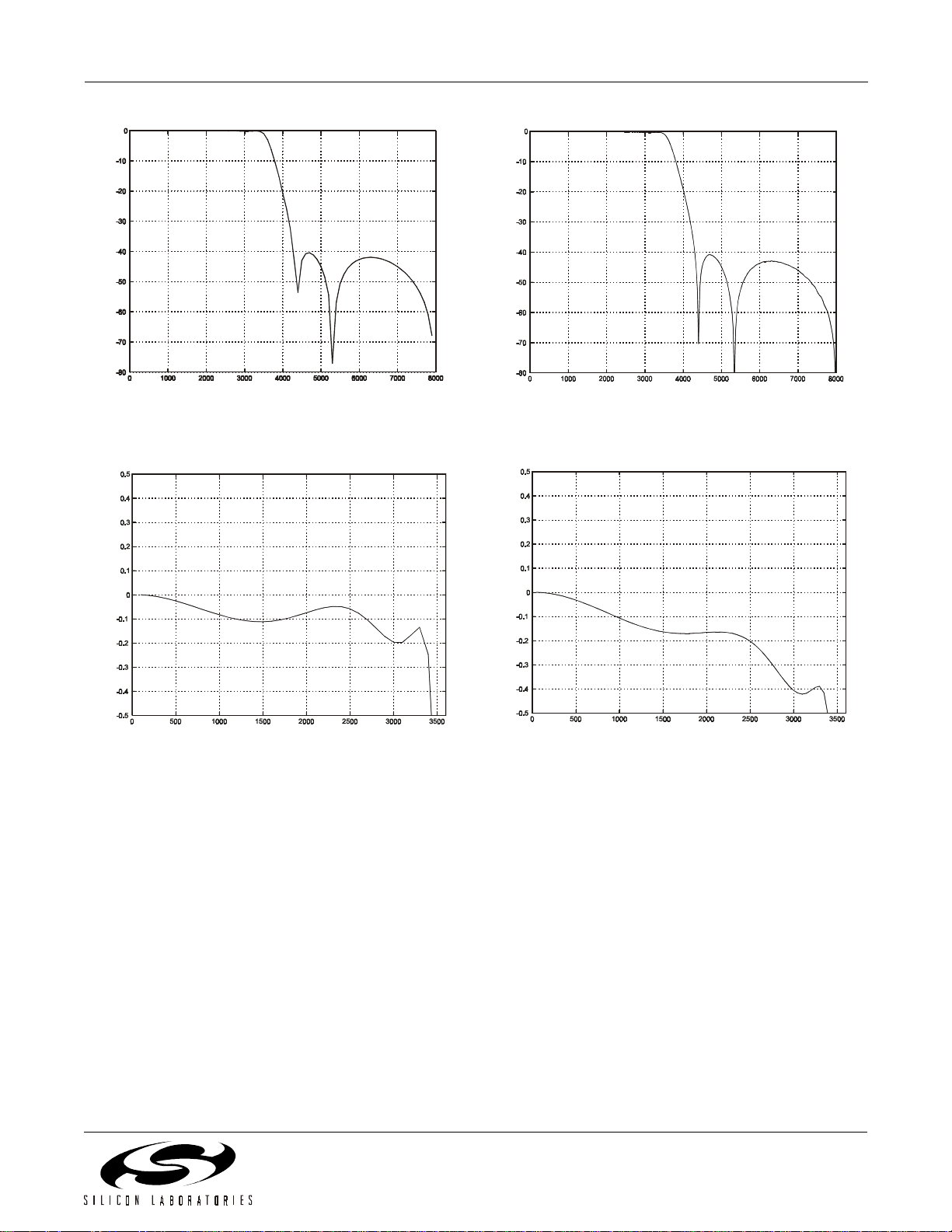

Si3036

Attenuation—dB

Input Frequency—Hz

Figure 13. IIR Receive Filter Response

Attenuation—dB

Input Frequency—Hz

Figure 14. IIR Receive Filter Passband Ripple

Attenuation—dB

Input Frequency—Hz

Figure 15. IIR T ransmit Filter Response

Attenuation—dB

Input Frequency—Hz

Figure 16. IIR Transmit Filter Passband Ripple

For Figures 13–16, all filter plots apply to a sample rate of

Fs = 8 kHz. The filters scale with the sample rate as follows:

F

where Fs is the sample frequency.

= 0.45 Fs

(–3 dB)

Rev. 1.2 13

Si3036

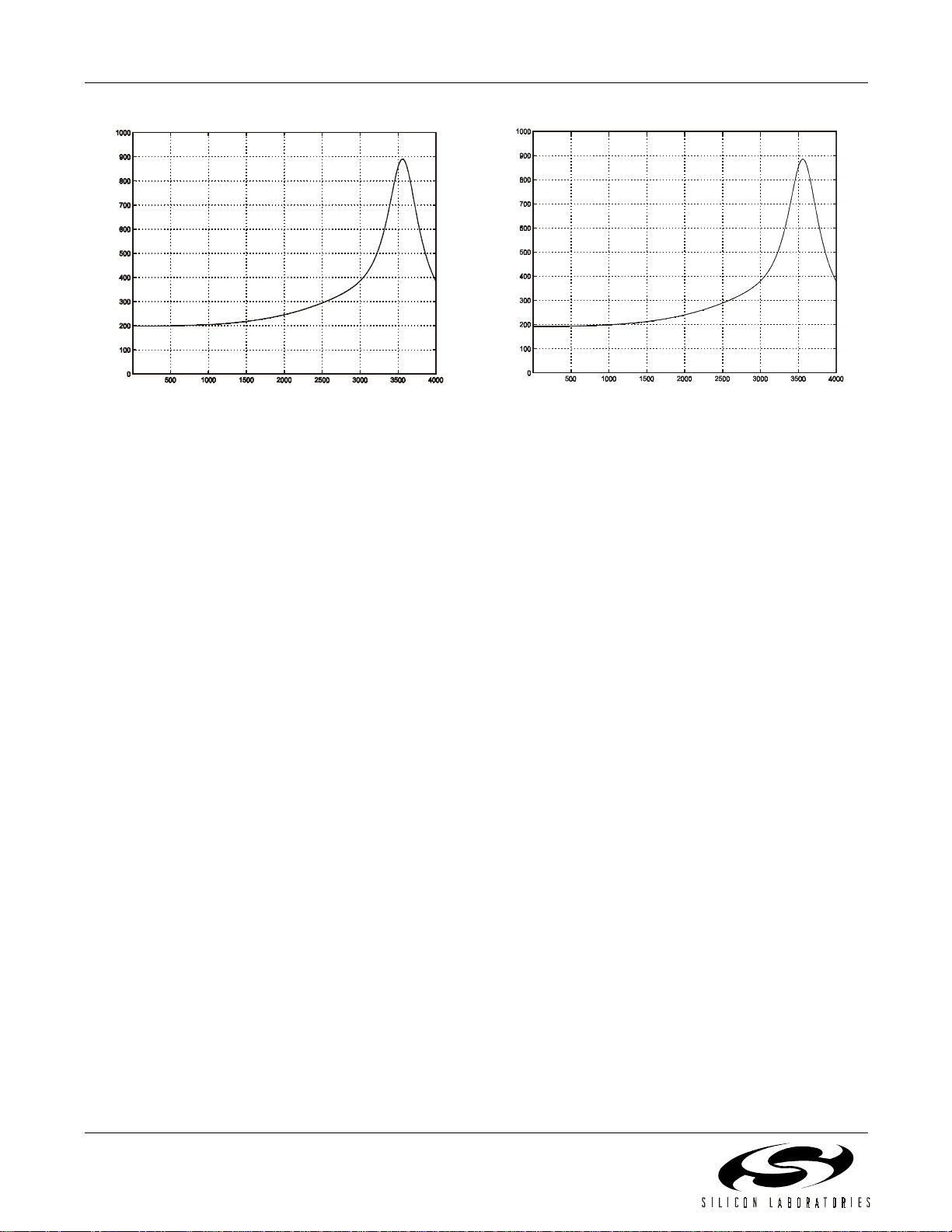

Delay—µs

Input Frequency—Hz

Figure 17. IIR Receive Group Delay

Delay—µs

Input Frequency—Hz

Figure 18. IIR Transmit Group Delay

14 Rev. 1.2

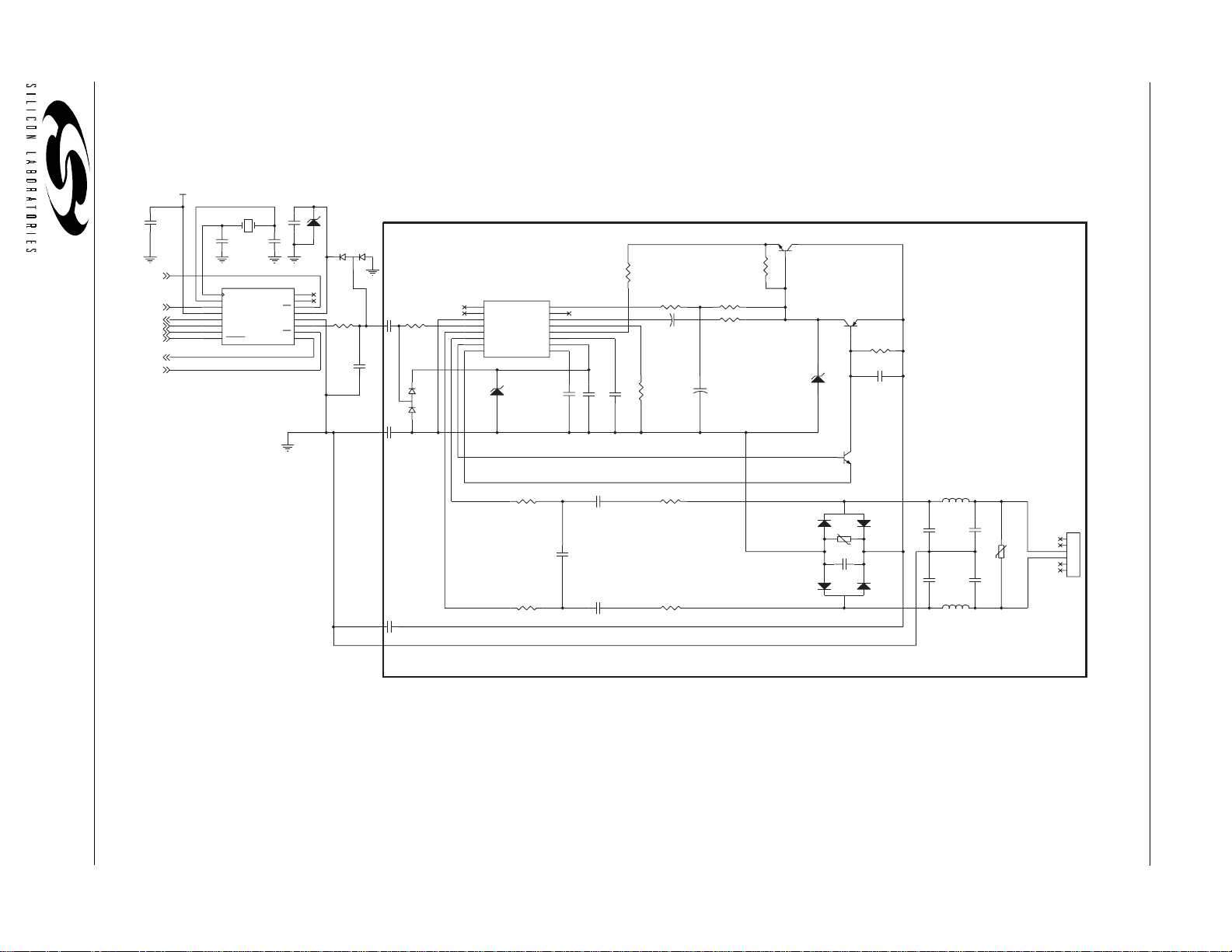

Typical Application Circuit

+3.3VD

C10

ID1#

BITCLK

SDATA_IN

SDATA_OUT

SYNC

RESET#

AOUT

ID0#

Rev. 1.2 15

24.576 MHz

Y1

1

MCLK/XIN

2

XOUT

3

BIT_CLK

4

VD

5

SDATA_IN

6

SDATA_OUT

7

SYNC

89

RESET AOUT

Si3024

C3

GND

Z4

D3

BAV99

16

15

14

ID1

13

VA

12

11

C1A

10

ID0

R27

C30

C35C34

U1

GPIO_A

GPIO_B

No Ground Plane In DAA Section

1

TSTA

2

TSTB

C1

R28

BAV99

C2

3

IGND

4

C1B

5

RNG1

6

RNG2

7

QB

89

QE VREG

Z5D4

Si3012

Q1

R1

U2

16

TX

15

NC

14

RX

13

REXT

12

DCT

11

HYBD

10

VREG2

C6

C12

C16

R4

+

C5

R2

+

R5

R21

R18

C23

Q2

R6

C20

Z1

Q3

Note1: If JATE support is not required, R21,

C12 and C23 may be removed and the

following modifications implemented: R21

should be replaced with a 0 ohm resistor or

shorted, and R4 should be changed to a 604

ohm, 1/ 4 W, +- 1%.

Note 2: See Appendix for applications

requiring UL 1950 3rd Edition compliance.

R23

R22

C4

C8

C11

C7

R10

R9

Figure 19. Typical Application Circuit for the Si3036

FB2

D1

RV2

C9

D2

C32

C25

RV1

C24

C31

FB1

J1

1

2

3

4

5

6

RJ-11

Si3036

Si3036

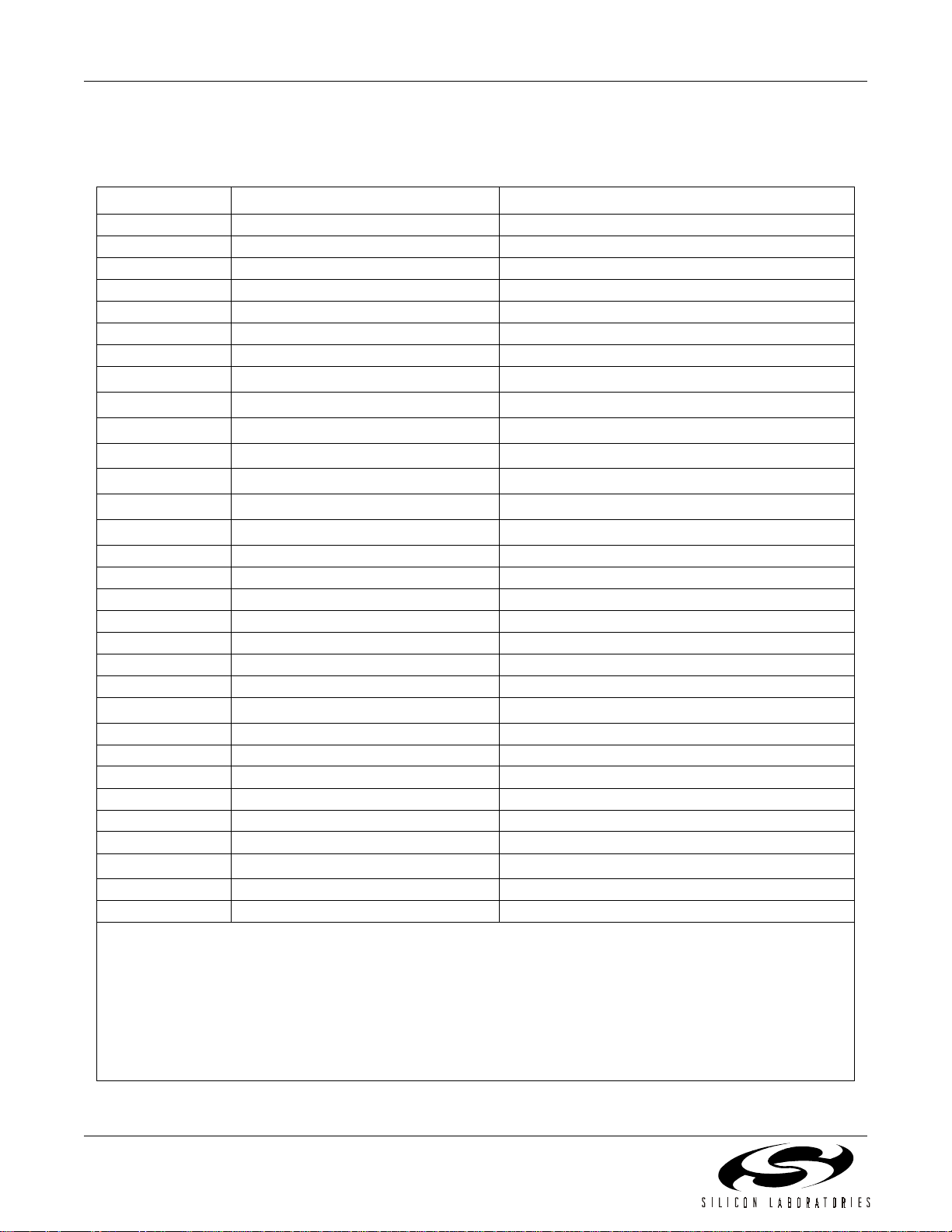

Bill of Materials

Table 16. FCC Component Values—Si3036 Chipset

Component

C1,C4 150 pF, 3 kV, X7R, ±20% Novacap, Venkel, Johanson, Murata, Panasonic

C2 Not Installed

C3 0.22 µF, 16 V, X7R, ±20%

C5 1 µF, 16 V, Tant/Elec, ±20%

C6,C10,C16 0.1 µF, 16 V, X7R, ±20%

C7,C8,C9 15 nF, 250 V, X7R, ±20% Novacap, Johanson, Murata, Panasonic

C11 39 nF, 16 V, X7R, ±20%

C12

C23

C24,C25,C31,C32

C30

C34,C35

D1,D2

D3,D4

FB1,FB2 Ferrite Bead Murata

Q1,Q3 A42, NPN, 300 V OnSemiconductor, Fairchild

Q2 A92, PNP, 300 V OnSemiconductor, Fairchild

RV1 Sidactor, 275 V, 100 A Teccor, ST Microelectronics, Microsemi, TI

RV2 MOV, 240 V Panasonic

R1 51 Ω, 1/2 W ±5%

R2 15 Ω, 1/4 W ±5%

R42,R18,R21

R5,R6 36 kΩ, 1/10 W ±5%

R9,R10 2 kΩ, 1/10 W ±5%

R22,R23 20 kΩ, 1/10 W ±5%

R27,R28 10 Ω, 1/10 W ±5%

U1 Si3024 Silicon Labs

U2 Si3012 Silicon Labs

Y1

Z1 Zener diode, 18 V Vishay, Rohm, OnSemi

Z4,Z5 Zener diode, 5.6 V, 1/2 W Diodes Inc., OnSemiconductor, Fairchild

Notes:

1. The following referenc e des ignato rs were i ntentio nally omitt ed: C 13–C15, C17– C22, C2 6–C29, C 31–C3 3, R3 , R7,

R8, R11–R17, R19, and R20.

2. If JA TE suppo rt is not requi red, R21 , C12, and C2 3 may be remov ed and the fol lowing modific ations imple mented:

R21 should be replaced with a 0 Ω resistor or shorted, and R4 should be changed to a 604 Ω, 1/4 W, ±1%.

3. Alternate population option is C24, C25 (2200 pF, 3 kV, X7R, ±10% and C31, C32 not installed).

4. Install only if needed for improved radiated emissions performance (10 pF, 16 V, NPO, ±10%).

5. Y1, C34, and C35 should be installed if the Si3024 is configured as a primary device.

6. Several diode bridge configurations are acceptable (suppliers include General Semi, Diodes Inc.)

1

2

2

3

4

5

6

2

4

2.7 nF, 16 V, X7R, ±20%

0.1 µF, 16 V, Tant/Elec/X7R, ±20%

1000 pF, 3 kV, X7R, ±10% Novacap, Venkel, Johanson, Murata, Panasonic

33 pF,16 V, NPO, ±5% Novacap, Venkel, Johanson, Murata, Panasonic

Dual Diode, 300 V, 225 mA Central Semiconductor

BAV99 Dual Diode, 70 V, 350 mW Diodes Inc., OnSemiconductor, Fairchild

24.576 MHz, 18 pF, 50 ppm

Value Supplier(s)

Not Installed

301 Ω, 1/10 W, ±1%

16 Rev. 1.2

Si3036

Analog Output

Figure 20 illustrates an option al application circuit to support the analog outp ut capability of the Si3036 for call

progress monitoring purp os es. Th e AO UT le ve l ca n be s et to 0 dB , –6 dB, –12 dB, and mute for both tran sm it and

receive paths through the ATM/ARM bits in Register 5Ch. U1 provides a gain of 26 dB. Additional gain adjustments

may be made by varying the voltage divider created by R1 and R3.

+5 V

AOUT

C2 R3

C6C1

R1

326

+

–

C4

5

U1

4

C3

+

C5

Speaker

R2

Figure 20. Optional Connection to AOUT for a Call Progress Speaker

‘

Table 17. Component Values—Optional Connection to AOUT

Symbol Value

C1 2200 pF, 16 V, ±20%

C2, C3, C5 0.1 µF, 16 V, ±20%

C4 100 µF, 16 V, Elec. ±20%

C6 820 pF, 16 V, ±20%

R1 10 kΩ, 1/10 W, ±5%

R2 10 Ω, 1/10 W, ±5%

R3 47 kΩ, 1/10 W, ±5%

U1 LM386

Rev. 1.2 17

Loading...

Loading...